15

20

Изобретение относится к области ,. передачи дискретной информации по каналам связи, может быть использовано в системах стартстопной передачи сигналов на фоне помех, в част- ности в системах телеуправления и телеконтроля радиовещательного оборудования с передачей кодовых сигналов по занятым вещательным каналам, и является усовершенствованием устрой- Q ства по авт.св. № 1190524.

Цель изобретения - повышение помехоустойчивости путем исправления как ошибок, так и стираний информационных символов.

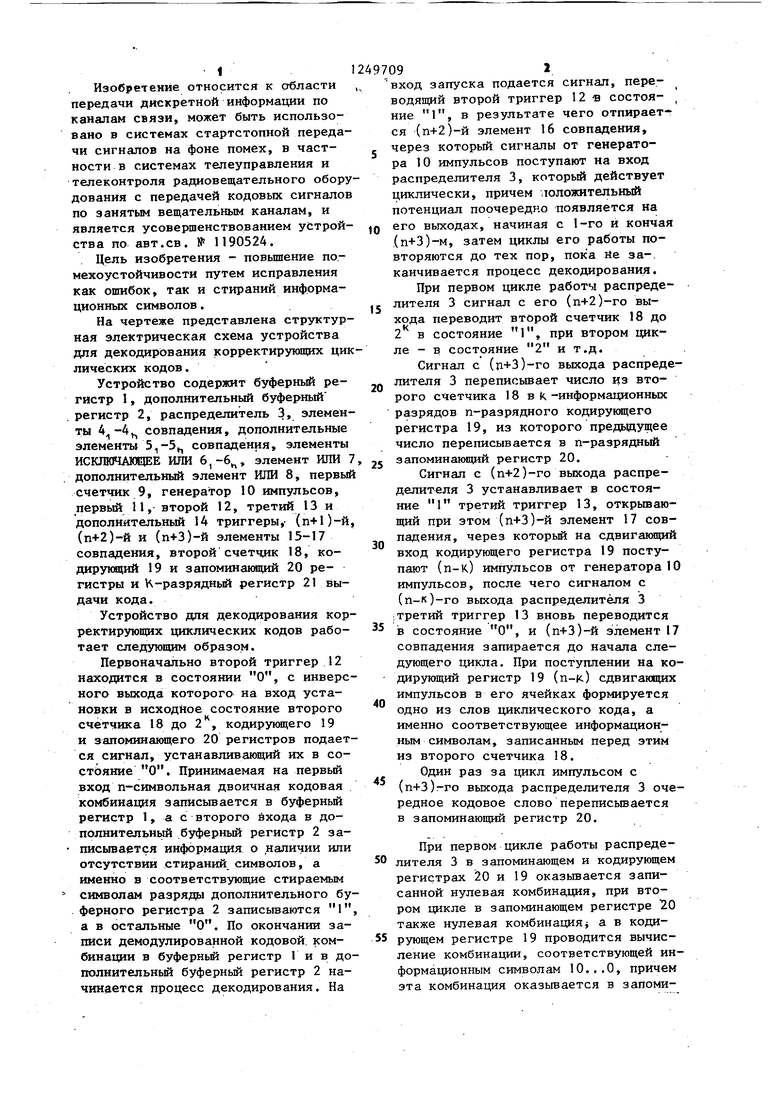

На чертеже представлена структурная электрическая схема устройства для декодирования корректирующих циклических кодов.

Устройство содержит буферный регистр , дополнительный буферный регистр 2, распределитель 3, элементы , совпадения, дополнительные элементы совпадения, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 6,-6, элемент ИЛИ 7, jj дополнительный элемент ИЛИ 8, первьй счетчик 9, генератор 10 импульсов, первьй 11, второй 12, третий 13 и дополнительный 14 триггеры,- (п+1)-й, (п+2)-й и (п+3)-й элементы 15-17 совпадения, второй счетчик 18, кодирующий 19 и запоминающий 20 регистры и К-разрядньй регистр 21 выдачи кода.

Устройство для декодирования корректирующих циклических кодов рабо- 35 тает следующим образом.

Первоначально второй триггер 12 находатся в состоянии О, с инверсного выхода которого на вход установки в исходное состояние второго счетчика 18 до 2, кодирукмцего 19 и запоминающего 20 регистров подается сигнал, устанавливающий их в состояние О. Принимаемая на первьй вход п-символьная двоичная кодовая комбинация записывается в буферньй регистр 1, а с второго входа в дополнительный буферньй регистр 2 за- писывается информация о наличии или отсутствии стираний символов, а именно в соответствующие стираемым символам разряды дополнительного буферного регистра 2 записываются 1, а в остальные О. По окончании записи демодулированной кодовой ком- 55 бинации в буферньй регистр Г и в до- полнительньй буферньй регистр 2 начинается процесс декодирования, На

30

40

45

50

0

j

5

5

0

0

5

0

вход запуска подается сигнал, переводящий второй триггер 12 в состоя- , ние 1, в результате чего отпирается (п+2)-й элемент 16 совпадения, через который сигналы от генератора 10 импульсов поступают на вход распределителя 3, которьй действует циклически, причем лоложительный потенциал поочередно появляется на его выходах, начиная с 1-го и кончая (п+3)-м, затем циклы его работы повторяются до тех пор, пок а Не за-, канчивается процесс декодирования.

При первом цикле работы распределителя 3 сигнал с его (п+2)-го выхода переводит второй счетчик 18 до 2 в состояние 1, при втором цикле - в состояние 2 и т.д.

Сигнал с (п+3)-го выхода распределителя 3 переписьшает число из второго счетчика 18 в К-информационных разрядов п-разрядного кодирующего регистра 19, из которого предьщущее число переписывается в п-разрядньй запоминающий регистр 20.

Сигнал с (п+2)-го выхода распределителя 3 устанавливает в состояние 1 третий триггер 13, открьшаю- щий при этом (п+3)-й элемент 17 совпадения, через которьй на сдвигающий вход кодирующего регистра 19 поступают (п-к) импульсов от генератора 10 импульсов, после чего сигналом с (п-к)-го выхода распределителя 3 третий триггер 13 вновь переводится в состояние О, и (п+3)-й элемент 17 совпадения запирается до начала следующего цикла. При поступлении на кодирующий регистр 19 (п-к) сдвигающих импульсов в его ячейках формируется одно из слов циклического кода, а именно соответствующее информационным символам, записанным перед этим из второго счетчика 18.

Один раз за цикл импульсом с (п+3)-го выхода распределителя 3 очередное кодовое слово переписьшается в запоминающий регистр 20.

При первом цикле работы распределителя 3 в запоминающем и кодирующем регистрах 20 и 19 оказьгоается записанной нулевая комбинация, при втором цикле в запоминающем регистре 120 также нулевая комбинацияj а в кодирующем регистре 19 проводится вычисление комбинации, соответствующей информационным символам 10...О, причем эта комбинация оказьгеается в запоми312

нающем регистре 20 на третьем цикле работы распределителя 3 и т.д.

Таким образом, за () циклов работы распределителя 3 в запоминающем регистре 20 последовательно по- йвляются все слова данного циклического кода, причем каждое слово сохраняется в запоминающем регистре 20 в течение всего цикла. С помощью п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ кодовое слово, записанное в запоминающем регистре 20, сравнивается с принятым словом, записанным в буферном регистре 1. При этом сигнал 1 имеется

на выходах лишь тех элементов ИСКПЮ- ,5 комбинацию, записанную в соЧАЮЩЕЕ ИЛИ 6, которые соответствуют отличающимся разряда в сравниваемых словах. Поэтому при условии отсутствия, стираний соответствующих символов оказываются открытыми те из эле- 2о меитов совпадения, которые соответствуют отличающимся разрядам в принятой и одной из 2 эталонных кодовых комбинаций. Если при демодуляции происходит стирание определенных 25 символов, т б сигналами с соответстответствующий момент в запоминающем регистре 20.

Итак, если в течение одного цикла работы распределителя 3 число импуль сов на входе первого счетчика 9 преd-1

вышает , то на его выходе формируется сигнал, переводящий первый триггер 1 в состояние О, в результате чего оказывается запертым (1 + 1)-й элемент 15 совпадения, чевующих выходов дополнительного буферно- рез который проходит импульс с

(h + l)ro выхода распределителя 3 при этом выдача декодированного нала не происходит, а сигналы с (Ы-1) -го и с (h+2)-ro выходов пределителя 3 устанавливают пер счетчик 9 и первый триггер 11 с ветственно в состояние О и М подготовив устройство к очередн циклу декодирования.

го регистра 2 оказываются заперты соответствующие элементы совпа- , однако открываются соответст- вукядие дополнительные элементы 5,-5 совпадения. За один цикл работы распределителя 3 через открытые элементы 4,-4 совпадения и дополнительные элементы совпадения проходит по одному импульсу с соответствующих выходов распределителя 3.

Импульсы с выходов дополнительных элементов совпадения через дополнительный элемент ИЛИ 8 подаются на счетйый вход дополнительного триггера 14, работающего в режиме деления частоты на два. Импульсы с въко- да дополнительного триггера 14, количество которых вдвое меньше количества стертых импульсов, объединяются в элементе ИЛИ 7 с импульсами с выходов открытых элементов 4; совпадений. Это суммарное количество импульсов, равное t (где t число отличающихся нестертых символов в принятой и соответствующей эталонной кодовой комбинации, записанной в данный момент в запоминающем регистре 20, S - число стертых символов, а квадратные скобки означают округление в меньшую сторону до ближайшего целого числа), подсчитьгоается первым счетчиком 9, предел

Г И

счета которого равен , , где а минимальное расстояние используемого кода.

Корректирующий код, имеющий минимальное расстояние d, исправляет до t ошибок и S стираний в том случае, если 2t 4- S id-l .

Таким образом, если на одном из циклов первый счетчик 9 не досчитывает до своего предела счета, то пораженная опшбками и стираниями кодовая комбинация должна быть декодиро комбинацию, записанную в соответствующий момент в запоминающем регистре 20.

Итак, если в течение одного цикла работы распределителя 3 число импульсов на входе первого счетчика 9 преd-1

вышает , то на его выходе формируется сигнал, переводящий первый триггер 1 в состояние О, в результате чего оказывается запертым (1 + 1)-й элемент 15 совпадения, через который проходит импульс с

(h + l)ro выхода распределителя 3, при этом выдача декодированного сигнала не происходит, а сигналы с (Ы-1) -го и с (h+2)-ro выходов распределителя 3 устанавливают первый счетчик 9 и первый триггер 11 соответственно в состояние О и М, подготовив устройство к очередному циклу декодирования.

Если число импульсов на входе первого счетчика 9 не превышает d -J

.2

то на данном цикле в течение п тактов работы распределителя 3 сигнал на выходе первого счетчика 9 не возникает и первый триггер 1 остается в состоянии 1, в которое он был установлен при предыдущем цикле работы сигналом с (п+2)-го выхода распределителя 3. В результате к моменту появления импульса на (п+1)-м выходе распределителя 3 остается открытым (п+1)-й элемент 15 совпадения, через который проходит указанньй импульс, осуществив перепись сигналов из К информационных разрядов запоминающего регистра 20 в К-разрядный регистр 21 вьщачи кода, на параплельньк выходах которого появляется декодированный К-разрядный информационный код, который сохраняется до декодирования следующего кодового слова. Этот им I

пульс (с выхода (nfO-ro элемента 15 совпадения) переводит второй триггер 12 в состояние О, при этом уст ройство возвращается в исходное состояние и процесс декодирования заканчивается. Процесс декодирования продолжается не более () циклов работы распределителя 3, причем может быть закончен на любом из циклов (в зависимости; от того, какое слово принимается).

Формула изобретения Устройство для декодирования кор- /ректируйщих циклических кодов по авт..св. 9 119052А, отличаю- ц ее с я тем, что, с целью повьше- ния помехоустойчивости путем исправления как ошибок, так и стираний сиМ , в него введены дополнительный буферный регистр, п дополнительных

А97096 элементов совпадения, дополнительный элемент ИЛИ и дополнительньй триггер, при этом прямые выходы дополнительного буферного регистра подключены к 5 первым входам соответствующих п дополнительных элементов совпадения, к вторым входам которых подключены соответствующие выходы распределителя, а выходы п дополнительных элемен10 тов совпадения через дополнительный элемент ШШ подключены к счетному входу дополнительного триггера, выход которого подключен к (п+1)-му входу элемента ИЛИ, причем инверсные

15 выходы дополнительного буферного регистра подключены к Дополнительным входам соответствующих элементов

совпадения а вход дополнительного буферного регистра является допол- нительным входом демодулированного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования корректирующих циклических кодов | 1983 |

|

SU1190524A1 |

| Устройство для декодирования корректирующих кодов | 1987 |

|

SU1441487A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| Устройство для декодирования циклических кодов | 1987 |

|

SU1429325A1 |

| Устройство для исправления стираний | 1989 |

|

SU1633498A1 |

| Устройство для исправления стираний | 1978 |

|

SU786030A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Устройство для исправления стираний | 1989 |

|

SU1647916A2 |

Изобретение м.б. использовано в системах стартстопной передачи сигналов на фоне помех. По отношению к авт.св. № 1190524 повьшается помехоустойчивость путем исправления как ошибок, так и стираний информационных символов. Устройство содер СЕ€ - :;; I i .1 5 W, гзь/- .жит два буферных регистра () 1 и 2, распределитель 3, элементы совпадения (ЭС) 4, 5, 15, 16 и 17, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 6, два элемента ИЛИ 7 и 8, два счетчика 9 и 18, генератор 10 импульсов, триггеры (т) 11-14, кодирующий Р 19, запоминающий Р 20 и К-разрядный Р 21 вьща- чи кода. Если на из циклов работы распределителя 3 счетчик 9 не досчитал до своего предела ,счета, то пораженная ошибками и стираниями ico- довая комбинахщя д.б. декодирована в комбинацию, записанную в соответствующий момент в запоминающем Р 20 Цель достигается введением Р 2, ЭС 5, элемента ИЛИ 8 и Т 14. 1 ил. § (О Сю 1 со ы о ;о к

| Устройство для декодирования корректирующих циклических кодов | 1983 |

|

SU1190524A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-08-07—Публикация

1983-11-05—Подача