11252796Z

Изобретение относится к эЛектриче- В четвертом такте работы перемно- ским вычислительным устройствам и мо- жителя значения коэффициентов передачи второго 4 и третьего 5 модуляторов устанавливаются равными 1, а значения 5 коэсМзициентов передачи первого 3 и четвертого 6 модуляторов и демодулятора 7 устанавливаются равными -1, Выбирая постоянную времени фильтра

жет быть использовано в аналоговых вычислительных машинах.

Цель изобретения - повьт1ение точности перемножения.

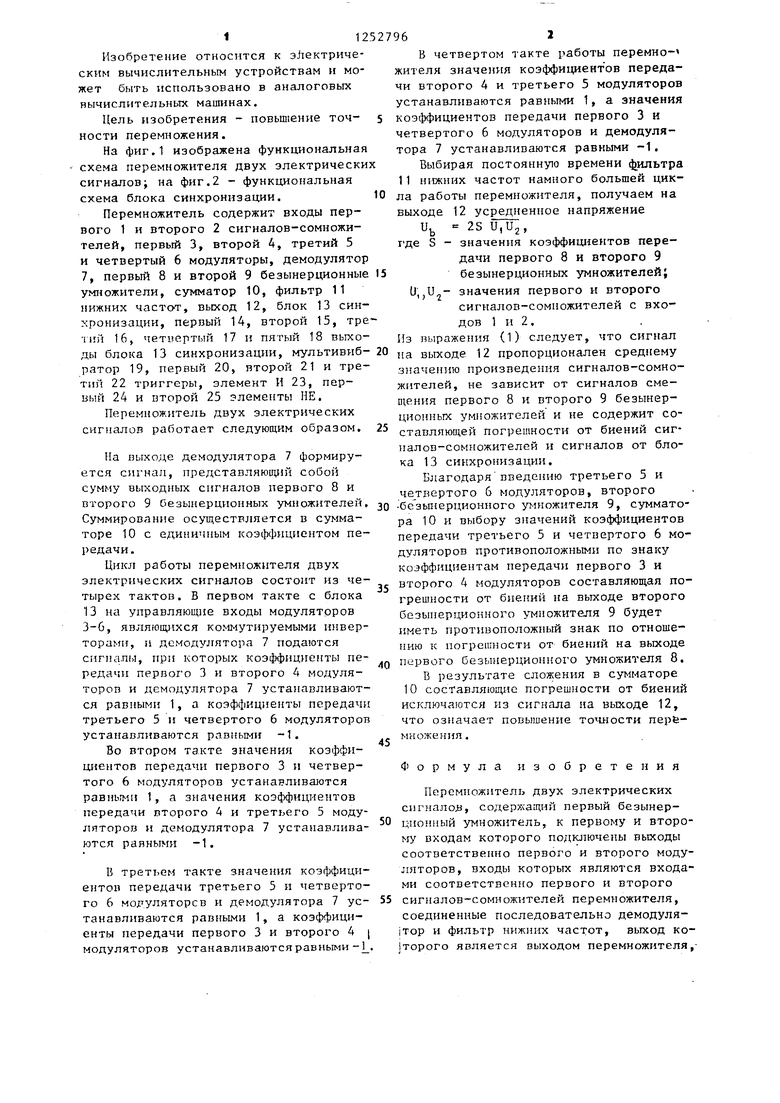

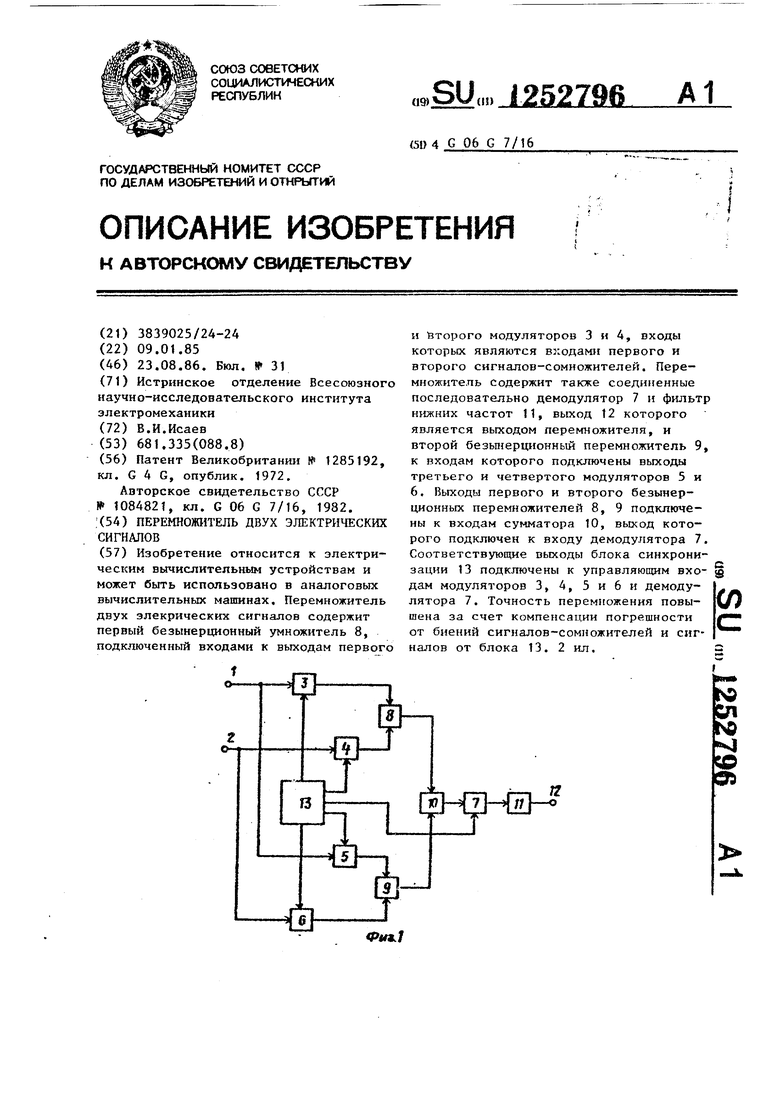

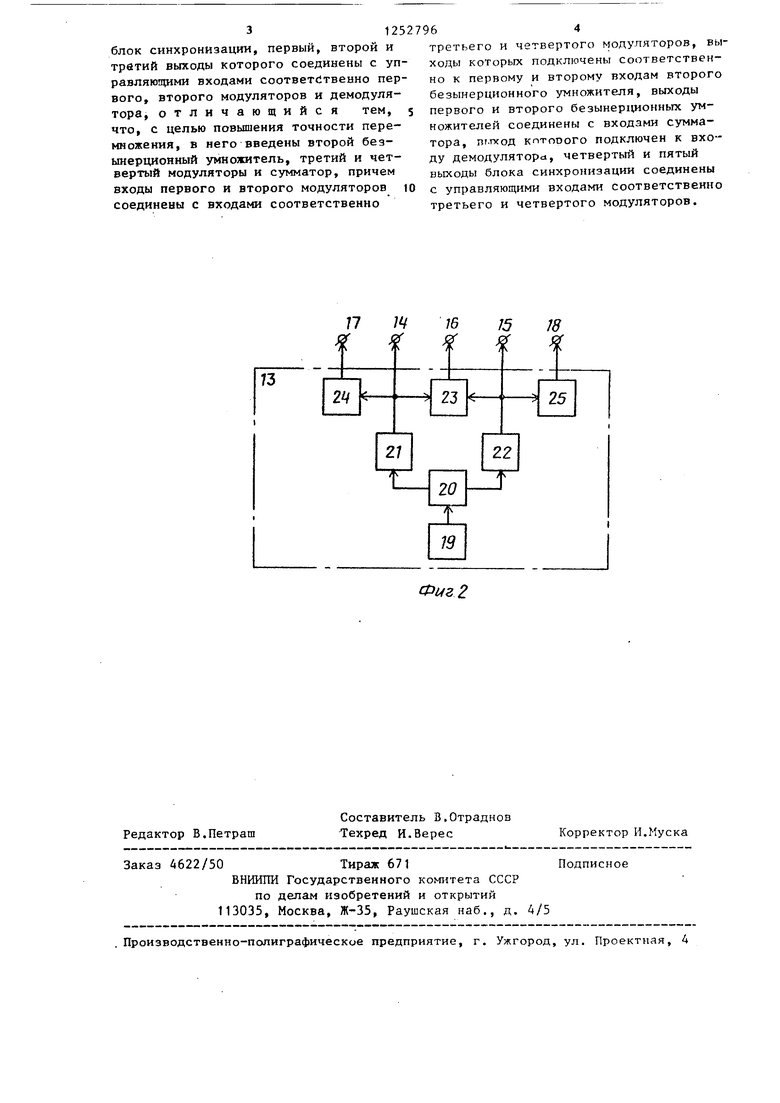

На фиг.1 изображена функциональная схема перемножителя двух электрических

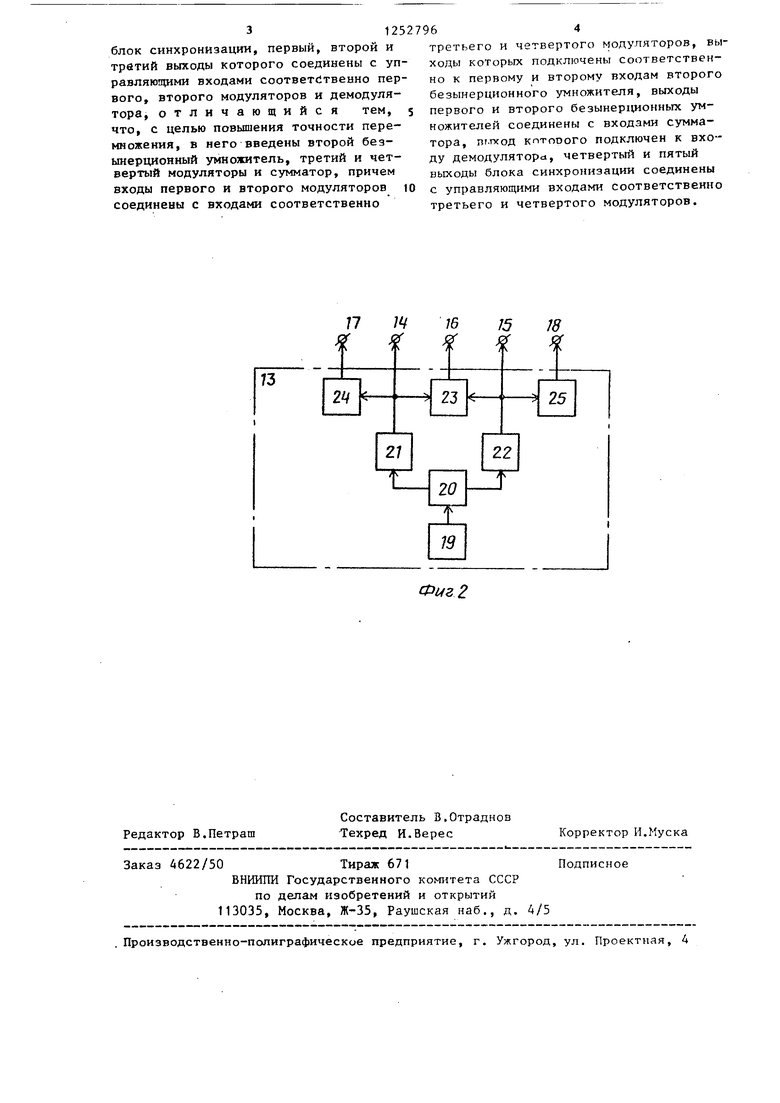

сигналов; на фиг.2 - функциональная схема блока синхронизации.Ю

Перемножитель содержит входы первого 1 и второго 2 сигналов-сомножителей, первый 3, второй 4, третий 5 и четвертый 6 модуляторы, демодулятор 7, первый 8 и второй 9 безынерционные 15 умножители, сумматор 10, фильтр 11 нижних частот, выход 12, блок 13 синхронизации, первый 14, второй 15, тре чий 16, четвертый 17 и пятый 18 выхо11 нижних частот намного большей цикла работы перемножителя, получаем на выходе 12 усредненное напряжение

Uj, 2S иТи,

г де S - значения коэффициентов передачи первого 8 и второго 9 безынерционных умножителей; и, значения первого и второго

сигналов-сомножителей с входов 1 и 2.

Из выражения (1) следует, что сигнал ды блока 13 синхронизации, мультивиб- 20 „ выходе 12 пропорционален среднему ратор 19, первый 20, второй 21 и третий 22 триггеры, элемент И 23, первый 24 и второй 25 элементы НЕ.

Перемножитель двух электрических сигналов работает следуюпу м образом.

з)1ачению произведения сигналов-сомножителей, не зависит от сигналов сме- п;ения первого 8 и второго 9 безынерционных умножителей и не содержит со- ставляюп;ей погрешности от биений сиг- палов-сомножителей и сигналов от блока 13 синхронизации.

На выходе демодулятора 7 формируется сигнал, представляющий собой сумму выходных сигналов первого 8 и

з)1ачению произведения сигналов-сомножителей, не зависит от сигналов сме- п;ения первого 8 и второго 9 безынерционных умножителей и не содержит со- ставляюп;ей погрешности от биений сиг- палов-сомножителей и сигналов от блока 13 синхронизации.

Благодаря введению третьего 5 и

четвертого б модуляторов, второго второго 9 безынерционных умножителей, зо .безынерционного т.1ножителя 9, сумматоСуммирование осуществляется в сумматоре 10 с единичным коэ(})(1)ициентом передачи.

Цикл работы перемножителя двух электрических сигналов состоит из четырех тактов. В первом такте с блока 13 на управляющие входы модуляторов 3-6, являющихся коммутируемыми инверторами, и демодулятора 7 подаются сигналы, при которых коэффициенты передачи первого 3 и второго 4 модуляторов и демодулятора 7 устанавливаются равными 1, а коэффициенты передачи третьего 5 и четвертого 6 модуляторов устанавливаются равными -1.

Во втором такте значения коэффициентов передачи первого 3 и четвертого 6 модуляторов устанавливаются paBHbiMii 1, а значения коэффициентов передачи второго 4 и третьего 5 моду- jTnTopoB и демодулятора 7 устанавливаются равными -1.

В третьем такте значения коэффициентов передачи третьего 5 и четвертого 6 модуляторов и демодулятора 7 устанавливаются равными 1, а коэффициенты передачи первого 3 и второго 4 | модуляторов устанавливаются равными .

35

ра 10 и выбору значений коэффициентов передачи третьего 5 и четвертого 6 модуляторов противоположными по знаку коэффициентам передачи первого 3 и второго 4 модуляторов составляющая погрешности от биений на выходе второго безынерционного умножителя 9 будет иметь противоположный знак по отношению к погрешности от биений на выходе 4Q первого безынерционного умножителя 8. В результате сложения в сумматоре 10 составляю1дие погрешности от биений исключаются из сигнала на выходе 12, что означает повышение точности nepfe- множения.

45

50

55

ормула изобретения

Перемножитель двух электрических сигналов, содержащий первый безынерционный умножитель, к первому и второму входам которого подключены выходы соответственно первого и второго модуляторов, входы которых являются входами соответственно первого и второго сигналов-сомножителей перемножителя, соединенные последовательно демодуля- jTop и фильтр нижних частот, выход ко- JToporo является выходом перемножителя,11 нижних частот намного большей цикла работы перемножителя, получаем на выходе 12 усредненное напряжение

Uj, 2S иТи,

г де S - значения коэффициентов передачи первого 8 и второго 9 безынерционных умножителей; и, значения первого и второго

сигналов-сомножителей с входов 1 и 2.

Из выражения (1) следует, что сигнал „ выходе 12 пропорционален среднему

з)1ачению произведения сигналов-сомножителей, не зависит от сигналов сме- п;ения первого 8 и второго 9 безынерционных умножителей и не содержит со- ставляюп;ей погрешности от биений сиг- палов-сомножителей и сигналов от блока 13 синхронизации.

Благодаря введению третьего 5 и

ра 10 и выбору значений коэффициентов передачи третьего 5 и четвертого 6 модуляторов противоположными по знаку коэффициентам передачи первого 3 и второго 4 модуляторов составляющая погрешности от биений на выходе второго безынерционного умножителя 9 будет иметь противоположный знак по отношению к погрешности от биений на выходе первого безынерционного умножителя 8. В результате сложения в сумматоре 10 составляю1дие погрешности от биений исключаются из сигнала на выходе 12, что означает повышение точности nepfe- множения.

50

55

ормула изобретения

Перемножитель двух электрических сигналов, содержащий первый безынерционный умножитель, к первому и второму входам которого подключены выходы соответственно первого и второго модуляторов, входы которых являются входами соответственно первого и второго сигналов-сомножителей перемножителя, соединенные последовательно демодуля- jTop и фильтр нижних частот, выход ко- JToporo является выходом перемножителя,блок синхронизации, первый, второй и третий выходы которого соединены с управляющими входами соответйтвенно первого, второго модуляторов и демодулятора, отличающийся тем, s что, с целью повышения точности пере- ми ожения, в него введены второй безынерционный умножитель, третий и четвертый модуляторы и сумматор, причем входы первого и второго модуляторов JO соединены с входами соответственно

третьего и четвертого модуляторов, выходы которых подключены соответственно к первому и второму входам второго безынерционного умножителя, выходы первого и второго безынерхрюнных умножителей соединены с входами сумматора, nf-тход кптооого подключен к входу демодулятор, четвертьгй и пятый выходы блока синхронизации соединены с управляющими входами соответственно третьего и четвертого модуляторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Перемножитель электрических сигналов | 1984 |

|

SU1265801A1 |

| Перемножитель электрических сигналов | 1982 |

|

SU1084821A1 |

| Перемножитель электрических сигналов | 1989 |

|

SU1622887A2 |

| Перемножитель электрических сигналов | 1991 |

|

SU1836694A3 |

| Перемножитель сигналов | 1985 |

|

SU1309048A1 |

| Умножитель электрических сигналов | 1982 |

|

SU1030813A1 |

| ДЕМОДУЛЯТОР СИСТЕМЫ СВЯЗИ С ДВУХКРАТНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2009 |

|

RU2427969C1 |

| Перемножитель аналоговых сигналов | 1985 |

|

SU1297082A1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2582331C1 |

| Вычислительное устройство | 1984 |

|

SU1280611A1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Перемножитель двух элекрических сигналов содержит первый безынерционный умножитель 8, подключенный входами к выходам первого и йторого модуляторов 3 и 4, входы которых являются Блюдами первого и второго сигналов-сомножителей. Перемножитель содержит также соединенные последовательно демодулятор 7 и фильтр нижних частот 11, выход 12 которого является вьгходом перемножителя, и второй безьшерционный перемножитель 9, к входам которого подключены выходы третьего и четвертого модуляторов 5 и 6. Выходы первого и второго безынерционных перемножителей 8, 9 подключены к входам сумматора 10, выход которого подключен к входу демодулятора 7. Соответствуюпще выходы блока синхронизации 13 подключены к управляющим вхо- § дам модуляторов 3, 4, 5 и 6 и демоду- лятора 7. Точность перемножения повы- // шена за счет компенсации погрешности от биений сигналов-сомножителей и сигналов от блока 13. 2 ил. .1

Редактор В.Петраш

Составитель В.Отраднов Техред И.Верес

Заказ 4622/50Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

- - ------- - - ----- - --- - ---- - - - - - - .-.-.,

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг 2

Корректор И.Муска

| Устройство для регулирования давления сжатого газа в коллекторе компрессорной станции | 1984 |

|

SU1285192A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Перемножитель электрических сигналов | 1982 |

|

SU1084821A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ,(54) ПЕРЕМНОЖИТЕЛЬ ДВУХ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | |||

Авторы

Даты

1986-08-23—Публикация

1985-01-09—Подача