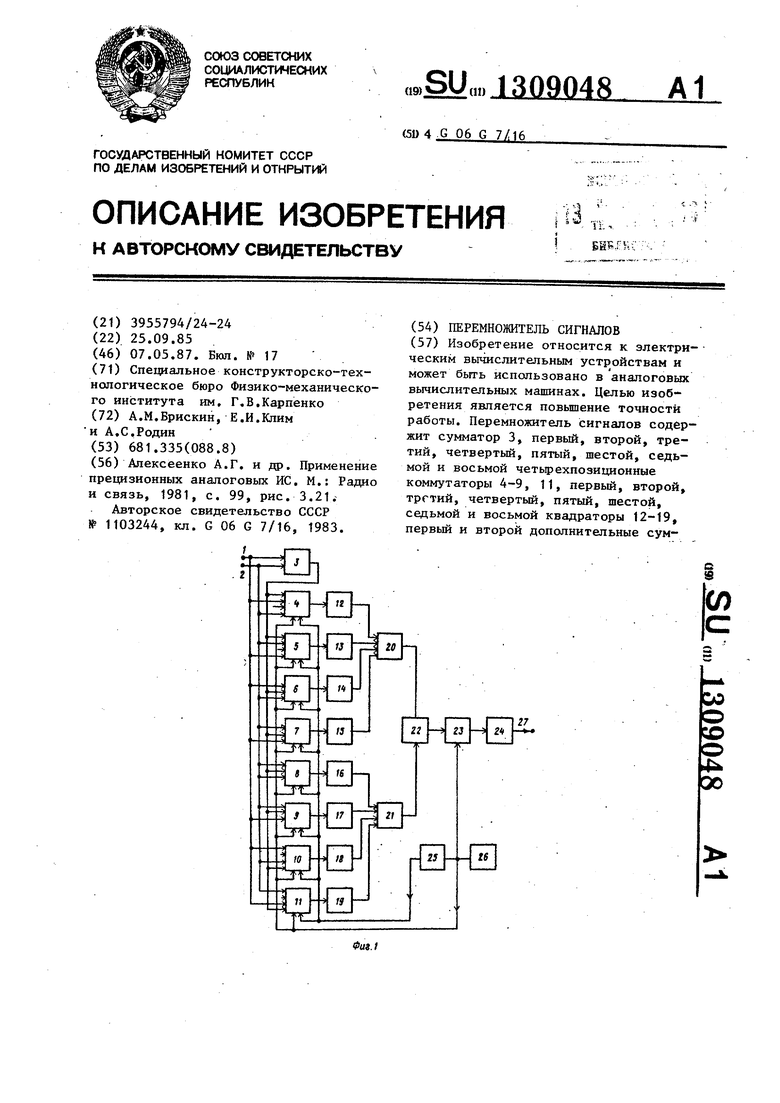

маторы 20 и 21, блок 22 вычитания, синхронный детектор 23, фильтр 24 нижних частот, делитель 25 частоты, генерат ор 26 коммутирующего напряжеИзобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Целью изобретения является повышение точности работы.

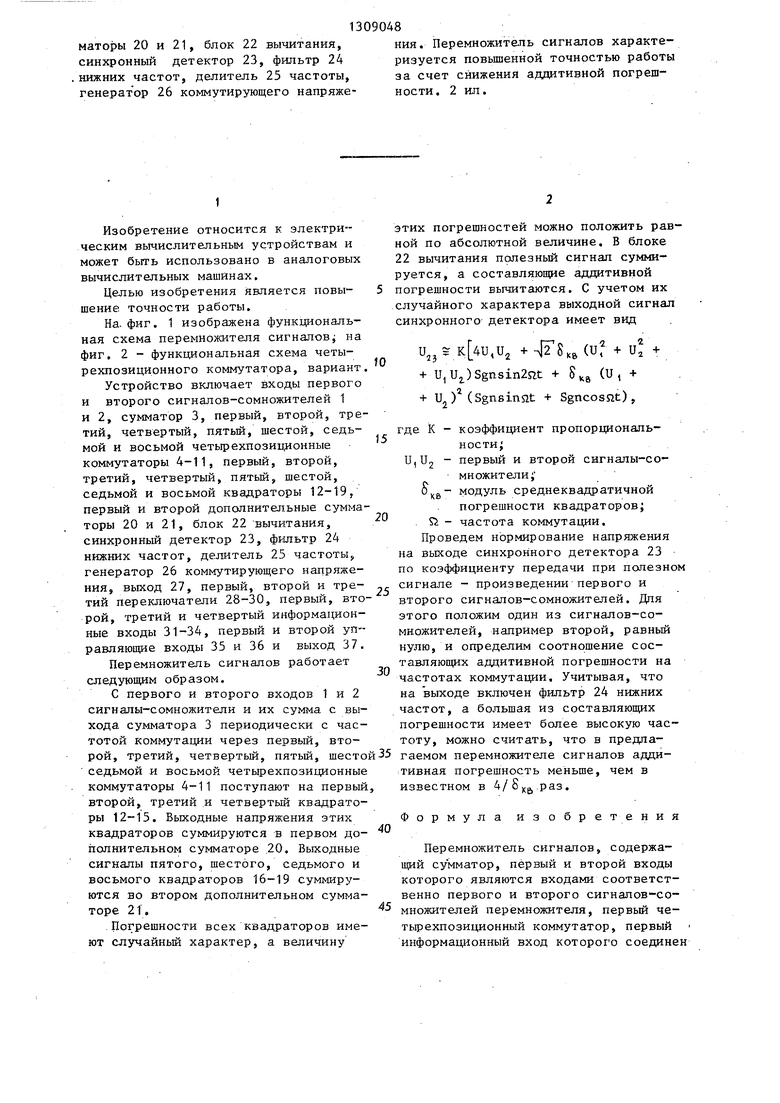

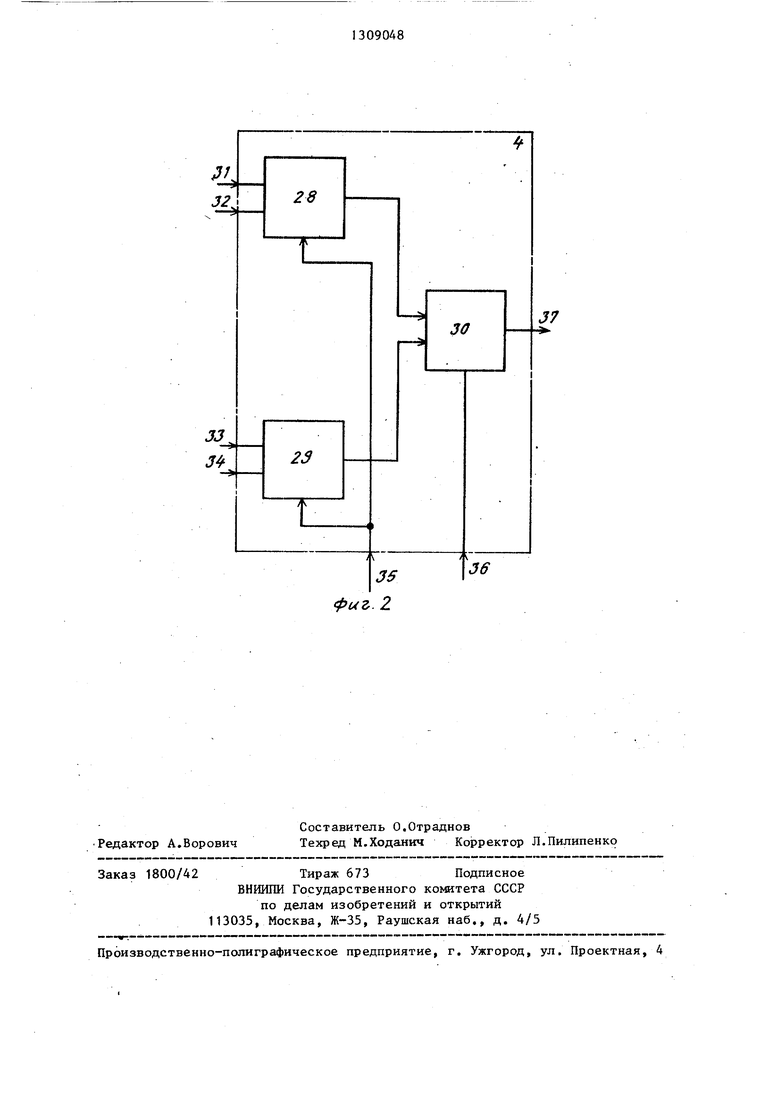

На. фиг. 1 изображена функциональная схема перемножителя сигналовj на фиг. 2 - функциональная схема четы- рехпозиционного коммутатора, вариант Устройство включает входы первого и второго сигналов-сомножителей 1 и 2, сумматор 3, первый, второй, третий, четвертый, пятьй, шестой, седьмой и восьмой четырехпозиционные коммутаторы 4-11, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой квадраторы 12-19, первый и второй дополнительные сумматоры 20 и 21, блок 22 вычитания, синхронный детектор 23, фильтр 24 нижних частот, делитель 25 частоты, генератор 26 коммутирующего напряжения, выход 27, первый, второй и третий переключатели 28-30, первый, второй, третий и четвертый информационные входы 31-34, первый и второй уп- равляюш;ие входы 35 и 36 и выход 37.

Перемножитель сигналов работает следующим образом.

С первого и второго входов 1 и 2 сигналы-сомножители и их сумма с выхода сумматора 3 периодически с частотой коммутации через первый, второй, третий, четвертый, пятый, шесто седьмой и восьмой четырехпозиционные коммутаторы 4-11 поступают на первый второй, третий и четвертый квадраторы 12-15. Выходные напряжения этих квадраторов суммируются в первом дополнительном сумматоре 20. Выходные сигналы пятого, шестого, седьмого и восьмого квадраторов 16-19 суммируются во втором дополнительном сумматоре 21.

Погрешности всех квадраторов имеют случайньй характер, а величину

ния. Перемножитель сигналов характеризуется повышенной точностью работы за счет снижения аддитивной погрешности. 2 ил.

5

0

5

0

5

0

5

этих погрешностей можно положить равной по абсолютной величине. В блоке 22 вычитания полезньй сигнал суммируется, а составляющие аддитивной погрешности вычитаются. С учетом их случайного характера выходной сигнал синхронного детектора имеет вид

,U2 (и + и +

+ U,U.,)Sgnsin2sit + (и, +

л

+ Uj) (Sgnsinsit + Sgncosnt),

где К - коэффициент пропорциональности;

UjUj - первый и второй сигналы-сомножители; модуль среднеквадратичной

погрешности квадраторов; S5 - частота коммутации. Проведем нормирование напряжения на выходе синхронного детектора 23 по коэффициенту передачи при полезном сигнале - произведении первого и второго сигналов-сомножителей. Дпя этого положим один из сигналов-сомножителей, например второй, равный нулю, и определим соотношение составляющих ад :;итивной погрешности на частотах коммутации. Учитывая, что на выходе включен фильтр 24 нижних частот, а большая из составляющих погрешности имеет более высокую частоту, можно считать, что в предлагаемом перемножителе сигналов аддитивная погрешность меньше, чем в известном в 4/8к.раз.

Формула изобретения

Перемножитель сигналов, содержащий сумматор, первый и второй входы которого являются входами соответственно первого и второго сигналов-сомножителей перемножителя, первый че- тырехпозиционный коммутатор, первый информационный вход которого соединен

,с выходом сумматора, первый и второй входы сумматора соединены соответственно с вторым и четвертым информационными входами первого четырехпо- зиционного коммутатора, выход кото- рого подключен к входу первого квадратора, синхронный детектор, выход которого соединен с входом фильтра нижних частот, выход кот орого является выходом перемножителя, генератор коммутирующего напряжения, выход которого подключен к входу делителя частоты, к управляющему входу синхронного детектора и к первому управляющему входу первого четырехпозици- онного коммутатора, второй управляющий вход которого соединен с выходом делителя частоты, отличающий с я тем, что, с целью повьше- ния точности, в него введены второй, третий, четвертый, пятый, шестой, седьмой и восьмой четырехпозиционные коммутаторы, второй, третий, четвертый, пятый, шестой, седьмой и восьмой квадраторы, первый и второй до- полнительные сумматоры и блок вычитания, причем к первому информационному входу первого четырехпозиционно го коммутатора подключены первый информационный вход второго, третьи информационные входы третьего и четвертого, вторые информационные входы пятого и шестого и четвертые информационные входы седьмого и восьмого четырехпозици онных коммутаторов, вто- рой информационный вход первого че- тьфехпозиционного коммутатора соединен с четвертыми информационными входами второго и четвертого, с вто-

рым информационньм входом третьего, с первыми информационными входами пятого и седьмого и с третьими информационными входами шестого и восьмого четырехпозиционных коммутаторов, четвертый информационный вход первого четьфехпозиционного коммутатора соединен с вторыми информационными входами второго, и четвертого, с третьими информационньв-м входами пятого и седьмого, с первыми информационными входами шестого и восьмого и с четвертым информационным входом третьего четырехпозиционных коммутаторов, выходы второго, третьего и четвертого четырехпозиционных коммутаторов подключены к входам второго, третьего и четвертого квадраторов, выходы ко- торых соединены с соответствующими

входами первого дополнительного сумматора, выход которого подключен к i первому входу блока вычитания, выход которого соединен с входом синхрон- . ного детектора, выходы пятого, шестого, седьмого и восьмого четырехпозиционных коммутаторов соответственно через пятый, шестой, седьмой и восьмой квадраторы подключены к входам второго дополнительного сумматора, выход которого соединен с вторым входом блока вычитания, первый и второй управляющие входы первого че- тырехпозиционного коммутатора соединены соответственно с первыми и вторыми управляющими входами второго, , третьего, четвертого, пятого, шестого, седьмого и восьмого четырехпозиционных коммутаторов .,

фиг

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ ВРЕМЕННОЙ ДИСКРЕТИЗАТОР | 2015 |

|

RU2583707C1 |

| Устройство для виброиспытаний | 1986 |

|

SU1366897A1 |

| Приемник четырехпозиционного фазоманипулированного сигнала | 1985 |

|

SU1252963A1 |

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| Устройство для прогнозирования надежности по результатам ускоренных испытаний | 1987 |

|

SU1508238A1 |

| Цифровой измеритель показателей качества электрической энергии трехфазной сети | 1988 |

|

SU1633368A1 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| Устройство для контроля параметров | 1990 |

|

SU1728869A1 |

| ФАЗОВЫЙ СПОСОБ ПЕЛЕНГАЦИИ И ФАЗОВЫЙ ПЕЛЕНГАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2012 |

|

RU2518428C2 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1982 |

|

SU1048581A1 |

Изобретение относится к электрическим вьиислительным устройствам и может быть использовано в аналоговых вьгаислительных машинах. Целью изобретения является повышение точности работы. Перемножитель сигналов содержит сумматор 3, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой четырехпозиционные коммутаторы 4-9, 11, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой квадраторы 12-19, первый и второй дополнительные сум(Л со о со о NU 00

Редактор А.Ворович

Составитель О.Отраднов

Техред М.Ходанич Корректор Л.Пилипенко

1800/42

Тираж 673 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Апексеенко А.Г | |||

| и др | |||

| Применение прецизионных аналоговых ИС | |||

| М.: Радио и связь, 1981, с | |||

| Прибор, замыкающий сигнальную цепь при повышении температуры | 1918 |

|

SU99A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Перемножитель низкочастотных сигналов | 1983 |

|

SU1103244A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-07—Публикация

1985-09-25—Подача