Изобретение относится к импульсной технике, в частности к преобразователям временных интервалов микросекундного диапазона, задаваемых с помощью импульсных сигналов, и является усовершенствованием изобретения по авт. св. № 930217,

Цель изобретения - повьшение точности преобразования за счет уменьшения погрешности преобразования, обусловленной изменением веса хронирующего элемента из-за априорной неизвестности величины задержки.

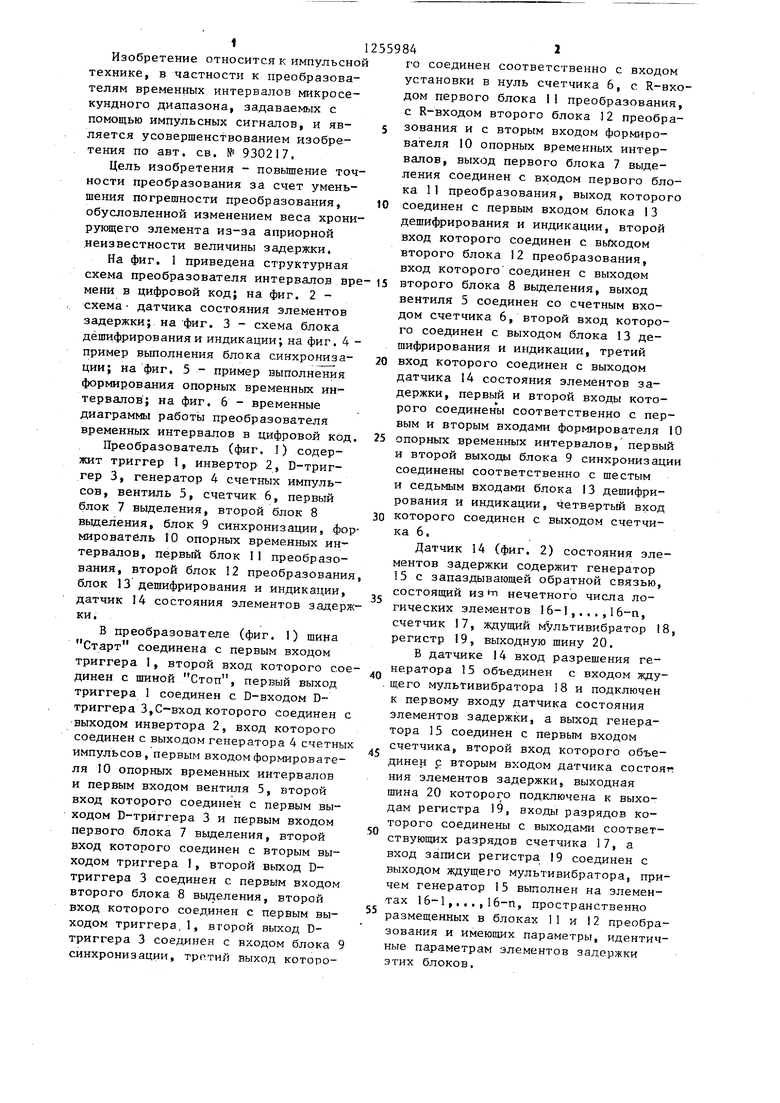

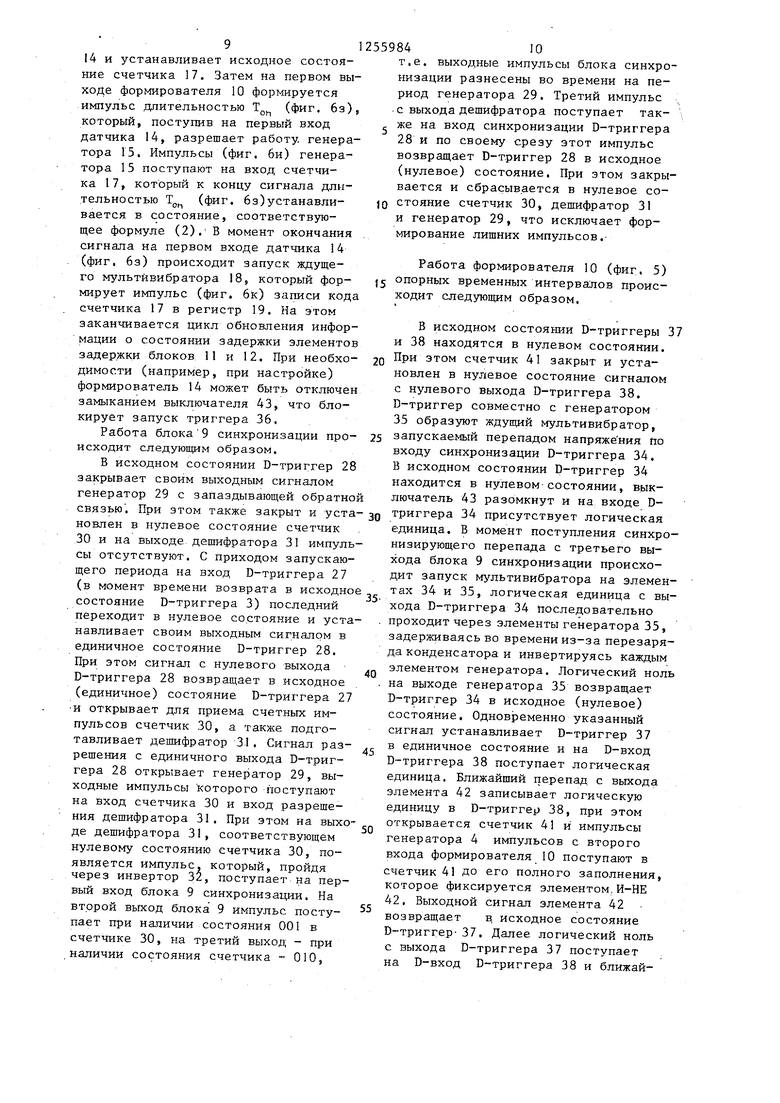

На фиг. 1 приведена структурная

схема преобразователя интервалов вре-is второго блока 8 вьщеления, выход

мени в цифровой код; на фиг. 2 - схема датчика состояния элементов задержки; на фиг. 3 - схема блока дешифрирования и индикации; на фиг, 4 - пример выполнения блока синхронизации; на фиг. 5 - пример выполнения формирования опорных временных интервалов ; на фиг. 6 - временные диаграммы работы преобразователя временных интервалов в цифровой код.

Преобразователь (фиг, 1) содержит триггер 1, инвертор 2, В-триг гер 3, генератор 4 счетных импульсов, вентиль 5, счетчик 6, первый блок 7 вьщеления, второй блок 8 выделения, блок 9 синхронизации, формирователь ГО опорных временных интервалов, первый блок II преобразования, второй блок 12 преобразования блок 13 дешифрирования и индикации, датчик 14 состояния элементов задержки.

В преобразователе (фиг, 1) шина Старт соединена с первым входом триггера 1, второй вход которого соединен с шиной Стоп, первый выход триггера I соединен с D-входом D- триггера 3,С-вход которого соединен с выходом инвертора 2, вход которого соединен с выходом генератора 4 счетных импульсов, первым входом формирователя 10 опорных временных интервалов и первым входом вентиля 5, второй вход которого соединей с первым выходом D-триггера 3 и первым входом первого блока 7 выделения, второй вход которого соединен с вторым выходом триггера 1, второй выход D- триггера 3 соединен с первым входом второго блока 8 выделения, второй вход которого соединен с первым выходом триггера.1, второй выход D- триггера 3 соединен с входом блока 9 синхронизации, третий выход которо

го соединен соответственно с входом установки в нуль счетчика 6, с R-BXO- дом первого блока I1 преобразования, с R-входом второго блока J2 преобразования и с вторым входом формирователя 10 опорных временных интервалов, выход первого блока 7 выделения соединен с входом первого блока 11 преобразования, выход которого соединен с первым входом блока 13 дешифрирования и индикации, второй вход которого соединен с выходом второго блока 12 преобразования, вход которого соединен с выходом

вентиля 5 соединен со счетным входом счетчика 6, второй вход которого соединен с выходом блока 13 дешифрирования и индикации, третий вход которого соединен с выходом датчика 14 состояния элементов задержки, первый и второй входы которого соединены соответственно с первым и вторым входами формирователя 10 опорных временных интервалов, первый и второй выходы блока 9 синхронизации соединены соответственно с шестым и седьмым входами блока 13 дешифрирования и индикации, Четвертый вход которого соединен с выходом счетчика 6.

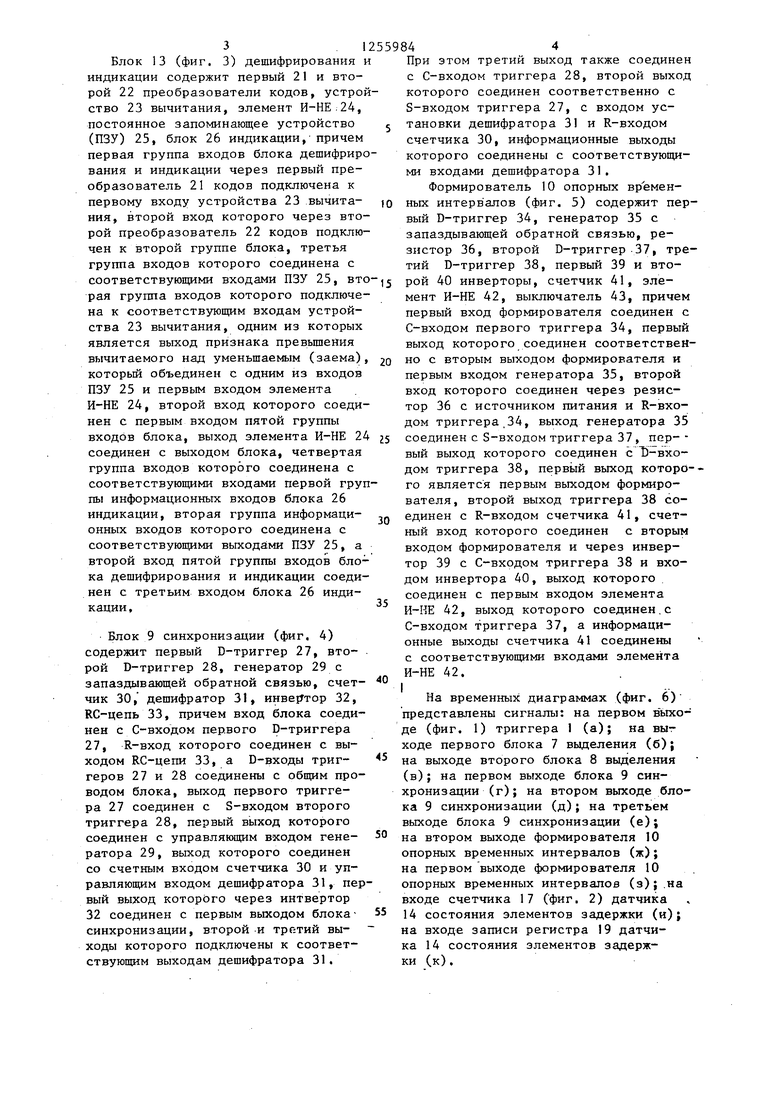

Датчик 14 (фиг. 2) состояния элементов задержки содержит генератор 15 с запаздывающей обратной связью, состоящий из ш нечетного числа логических элементов 16-1,.,,,16-п, счетчик 17, ждущий м льтивибратор 18, регистр 19, выходную шину 20,

В датчике 14 вход разрешения генератора 15 объединен с входом ждущего мультивибратора 18 и подключен к первому входу датчика состояния элементов задержки, а выход генератора 15 соединен с первым входом

45

50

55

счетчика, второй вход которого объединен с вторым входом датчика состоят ния элементов задержки, выходная тина 20 которого подключена к выходам регистра 19, входы разрядов которого соединены с выходами соответствующих разрядов счетчика 17, а вход записи регистра 19 соединен с выходом ждущего мультивибратора, причем генератор 15 выполнен на элементах 16-1,...,16-п, пространственно размещенных в блоках 11 и 12 преобразования и имеющих параметры, идентичные параметрам элементов задержки этих блоков.

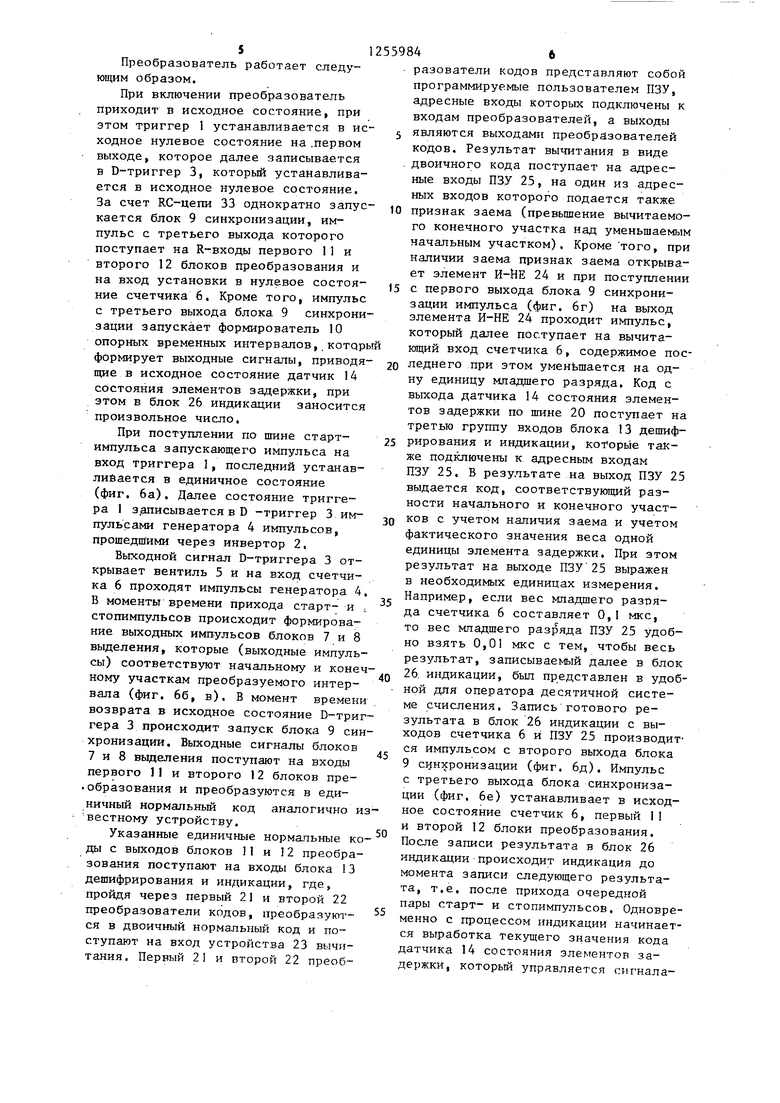

Блок 13 (фиг, 3) дешифрирования и индикации содержит первый 21 и второй 22 преобразователи кодов, устройство 23 вычитания, элемент И-НЕ.24, постоянное запоминающее устройство (ПЗУ) 25, блок 26 индикации,- причем первая группа входов блока дешифрирования и индикации через первый преобразователь 21 кодов подключена к первому входу устройства 23 вычитания, второй вход которого через второй преобразователь 22 кодов подключен к второй группе блока, третья группа входов которого соединена с

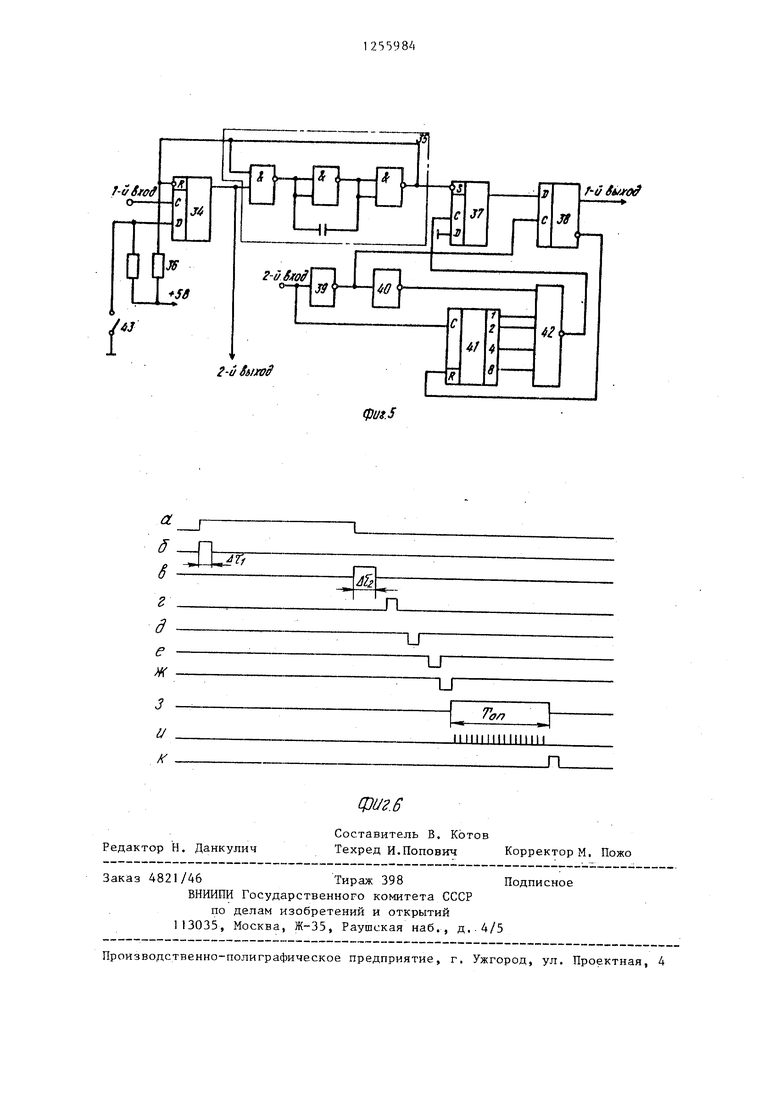

Формирователь 10 опорных временных интерв апов (фиг. 5) содержит пе вый D-триггер 34, генератор 35 с запаздывающей обратной связью, резистор 36, второй D-триггер .37, тр тий D-триггер 38, первый 39 и втосоответствующими входами ПЗУ 25, вто-, рой 40 инверторы, счетчик 41, элерая группа входов которого подключена к соответствующим входам устройства 23 вычитания, одним из которых является выход признака превьщ ения вычитаемого над уменьшаемым (заема), который объединен с одним из входов ПЗУ 25 и первым входом элемента И-НЕ 24, второй вход которого соединен с первым входом пятой группы входов блока, выход элемента И-НЕ 24 соединен с выходом блока, четвертая группа входов которого соединена с соответствующими входами первой группы информационных входов блока 26 индикации, вторая группа информационных входов которого соединена с соответствующими выходами ПЗУ 25t а второй вход пятой группы входов блока дешифрирования и индикации соединен с третьим входом блока 26 индикации ,

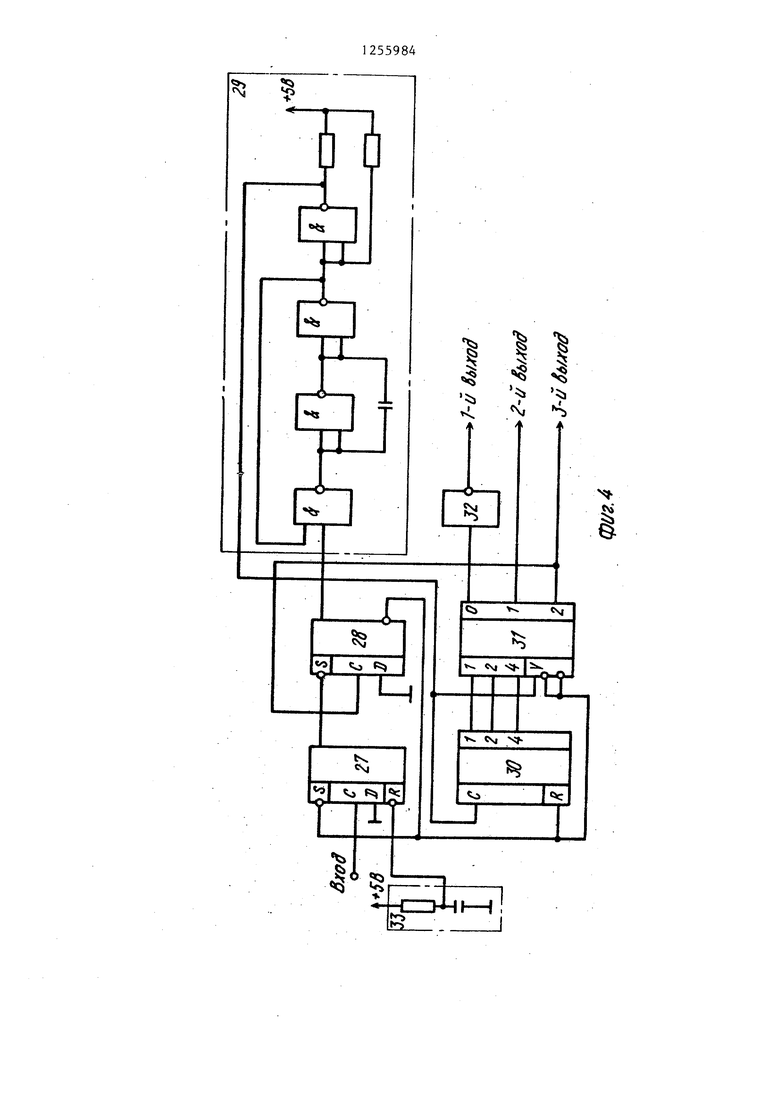

Блок 9 синхронизации (фиг. 4) содержит первый D-триггер 27, второй D-триггер 28, генератор 29 с запаздывающей обратной связью, счет чик 30, дешифратор 31, инве{Утор 32, КС-цепь 33, причем вход блока соединен с С-входом первого р-триггера 27, R-вход которого соединен с выходом RC-цепи 33, а D-входы триггеров 27 и 28 соединены с общим проводом блока, выход первого триггера 27 соединен с S-входом второго триггера 28, первый выход которого соединен с управляющим входом генератора 29, выход которого соединен со счетным входом счетчика 30 и управляющим входом дешифратора 31, певый выход которого через интвертор 32 соединен с первым выходом блока - синхронизации, второй и третий выходы которого подключены к соответствующим выходам дешифратора 31.

При этом третий выход также соединен с С-входом триггера 28, второй выход которого соединен соответственно с S-входом триггера 27, с входом установки дешифратора 31 и R-входом счетчика 30, информационные выходы которого соединены с соответствующими входами дешифратора 31,

Формирователь 10 опорных временных интерв апов (фиг. 5) содержит первый D-триггер 34, генератор 35 с запаздывающей обратной связью, резистор 36, второй D-триггер .37, третий D-триггер 38, первый 39 и второй 40 инверторы, счетчик 41, эле20J5 30

5

мент И-НЕ 42, выключатель 43, причем первый вход формирователя соединен с С-входом первого триггера 34, первый выход которого соединен соответственно с вторым выходом формирователя и первым входом генератора 35, второй вход которого соединен через резистор 36 с источником питания и R-входом триггера.34, выход генератора 35 соединен с S-входом триггера 37 , пер- - вый выход которого соединен с Т)-входом триггера 38, первый выход которо-- го является первым выходом формирователя, второй выход триггера 38 соединен с R-входом счетчика 41, счетный вход которого соединен с вторым входом формирователя и через инвертор 39 с С-входом триггера 38 и входом инвертора 40, выход которого соединен с первым входом элемента И-НЕ 42, выход которого соединен.с С-входом триггера 37, а информационные выходы счетчика 41 соединены с соответствующими элемента И-НЕ 42.

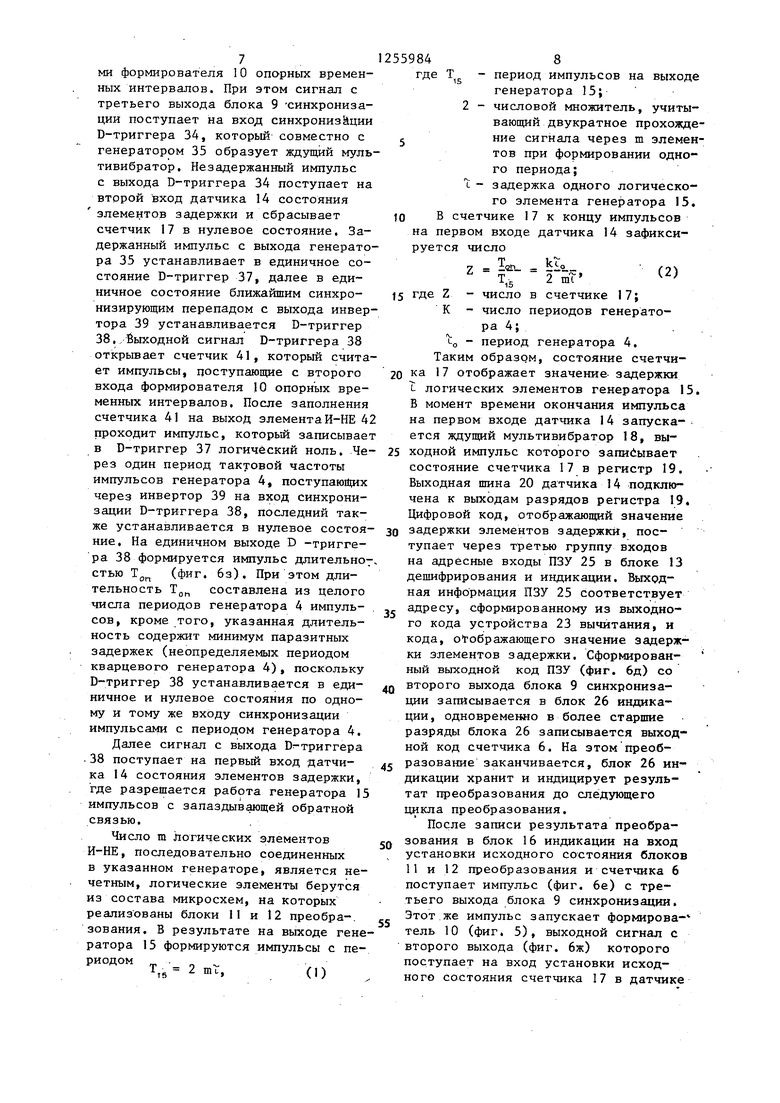

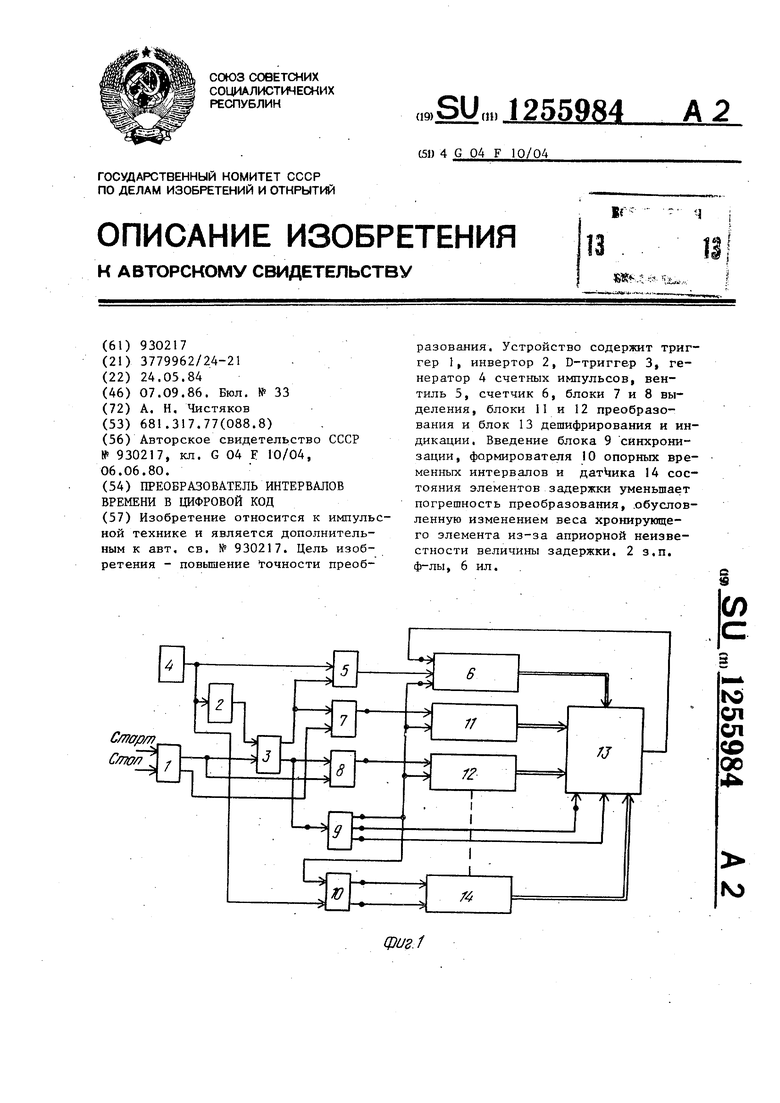

На временных диаграммах (фиг. 6) представлены сигналы: на первом в ыхо- де (фиг. 1) триггера I (а); на выг ходе первого блока 7 выделения (б); на выходе второго блока 8 выделения (в); на первом выходе блока 9 синхронизации (г); на втором выходе блока 9 синхронизации (д); на третьем выходе блока 9 синхронизации (е); на втором выходе формирователя 10 опорных временных интервалов (ж); на первом выходе формирователя 10 опорных временных интервалов (з); .на входе счетчика 17 ( фиг, 2) датчика 14 состояния элементов задержки (и); на входе записи регистра 19 датчика 14 состояния элементов задержки (к) .

Преобразователь работает следующим образом.

При включении преобразователь приходит в исходное состояние, при этом триггер I устанавливается в ис- ходное нулевое состояние на .первом выходе, которое далее записывается в D-триггер 3, который устанавливается в исходное нулевое состояние. За счет КС-цепи 33 однократно запус- кается блок 9 синхронизации, импульс с третьего выхода которого поступает на R-входы первого 1 и второго 12 блоков преобразования и на вход установки в нулевое состоя- ние счетчика 6. Кроме того, импульс с третьего выхода блока 9 синхронизации запускает формирователь 10 опорных временных интервалов,.которы формирует выходные сигналы, приводя- щие в исходное состояние датчик 14 состояния элементов задержки, при этом в блок 26 индикации заносится произвольное число.

При поступлении по шине старт- импульса запускающего импульса на вход триггера 1, последний устанав- лийается в единичное состояние (фиг, 6а), Далее состояние триггера 1 записывается вD -триггер 3 им- пульсами генератора 4 импульсов, прошедшими через инвертор 2,

Выходной сигнал D-триггера 3 открывает вентиль 5 и на вход счетчика 6 проходят импульсы генератора 4 В моменты времени прихода старт- и стопимпульсов происходит формирование выходных импульсов блоков 7 и 8 выделения, которые (выходные импульсы) соответствуют начальному и конечному участкам преобразуемого интервала (фиг, 66, в), В момент времени возврата в исходное состояние D-триггера 3 происходит запуск блока 9 синхронизации. Выходные сигналы блоков 7 и 8 выделения поступают на входы первого 1 и второго 12 блоков пре- .образования и преобразуются в единичный нормальный код аналогично ивестному устройству,

Указанные единичные нормальные коды с выходов блоков 11 и 12 преобразования поступают на входы блока 13 дешифрирования и индикации, где, пройдя через первый 21 и второй 22 преобразователи кодов, преобразуют- ся в двоичный нормальный код и поступают на вход устройства 23 вычитания. Первый 21 и второй 22 преоб

Q ,j о

5

0

5

0

разователи кодов представляют собой программируемые пользователем ПЗУ, адресные входы которых подключены к входам преобразователей, а выходы являются выходами преобразователей кодов. Результат вычитания в виде двоичного кода поступает на адресные входы ПЗУ 25, на один из адресных входов которого подается также признак заема (превышение вычитаемого конечного участка над уменьшаемым начальным участком), Кроме того, при наличии заема признак заема открывает элемент И-НЕ 24 и при поступлении с первого выхода блока 9 синхронизации импульса (фиг, 6г) на выход элемента И-НЕ 24 проходит импульс, который далее поступает на вычитающий вход счетчика 6, содержимое последнего при этом уменьшается на одну единицу младшего разряда. Код с выхода датчика 14 состояния элементов задержки по шине 20 поступает на третью группу входов блока 13 дешифрирования и индикации, которые также подключены к адресным входам ПЗУ 25, В результате на выход ПЗУ 25 выдается код, соответствующий разности начального и конечного участков с учетом наличия заема и учетом фактического значения веса одной единицы элемента задержки. При этом результат на выходе ПЗУ 25 выражен в необходимых единицах измерения. Например, если вес младшего разряда счетчика 6 составляет О,1 мкс, то вес младшего разряда ПЗУ 25 удобно взять 0,01 МКС с тем, чтобы весь результат, записываемый далее в блок 26. индикации, был представлен в удобной для оператора десятичной системе счисления. Запись готового результата в блок 26 индикации с выходов счетчика 6 и ПЗУ 25 производится импульсом с второго выхода блока 9 синхронизации (фиг, 6д), Импульс с третьего выхода блока синхронизации (фиг, бе) устанавливает в исходное состояние счетчик 6, первый 11 и второй 12 блоки преобразования. После записи результата в блок 26 индикации происходит индикация до момента записи следующего результата, т,е, после прихода очередной пары старт- и стопимпульсов. Одновременно с процессом индикации начинается выработка текущего значения кода датчика 14 состояния элементов задержки, который управляется сигнала71

ми формирователя 10 опорных временных интервалов. При этом сигнал с третьего выхода блока 9 -синхронизации поступает на вход синхронизации D-триггера 34, который совместно с генератором 35 образует ждущий мультивибратор. Незадержанный импульс с выхода D-триггера 34 поступает на второй вход датчика 14 состояния

элементов задержки и сбрасывает счетчик 17 в нулевое состояние. Задержанный импульс с выхода генератора 35 устанавливает в единичное состояние D-триггер 37, далее в единичное состояние ближайшим синхронизирующим перепадом с выхода инвертора 39 устанавливается D-триггер 38. Ёыходной сигнал D-триггера 38 открывает счетчик 41, который считает импульсы, поступающие с второго входа формирователя 10 опорных временных интервалов. После заполнения счетчика 41 на выход элементаИ-НЕ 42 проходит импульс, который записывает в D-триггер 37 логический ноль. Через один период тактовой частоты импульсов генератора 4, поступающих через инвертор 39 на вход синхронизации D-триггера 38, последний также устанавливается в нулевое состояние. На единичном выходе D -триггера 38 формируется импульс длительноу стью Tjj (фиг. 6з). При этом длительность Тд„ составлена из целого числа периодов генератора 4 импульсов, кроме того, указанная длительность содержит минимум паразитных задержек (неопределяемых периодом кварцевого генератора 4), поскольку D-триггер 38 устанавливается в единичное и нулевое состояния по одному и тому же входу синхронизации импульсами с периодом генератора 4. Далее сигнал с выхода D-триггера

38 поступает на первый вход датчика 14 состояния элементов задержки, где разрешается работа генератора 15 мпульсов с запаздывающей обратной связью.

Число m Логических элементов -НЕ, последовательно соединенных в указанном генераторе, является неетным, логические элементы берутся з состава микросхем, на которых еализованы блоки II и 12 преобра-. ования. В результате на выходе генеатора 15 формируются импульсы с пеиодом . . - Т,5 2 шь, (1)

559848

где Т - период импульсов на выходе

генератора 15;

2 - числовой множитель, учитывающий двукратное прохожде- с ние сигнала через m элементов при формировании одного периода;

1 - задержка одного логического элемента генератора 15. to В счетчике 17 к концу импульсов на первом входе датчика 14 зафиксируется число

ту UIL. - о

- f,f - Гшт

(2)

15 где Z - число в счетчике 17;

К - число периодов генератора 4;. . tg - период генератора 4. Таким образом, состояние счетчи20 ка 17 отображает значение- задержки t логических элементов генератора 15. В момент времени окончания импульса на первом входе датчика 14 запуска- ется ждущий мультивибратор 18, вы5 ходной импульс которого записывает Состояние счетчика 17 в регистр 19. Выходная шина 20 датчика 14 подключена к выходам разрядов регистра 19. Цифровой код, отображающий значение

0 задержки элементов задержки, поступает через третью группу входов на адресные входы ПЗУ 25 в блоке 13 дешифрирования и индикации. Выходная информация ПЗУ 25 соответствует

, адресу, сформированному из выходного кода устройства 23 вычитания, и кода, о гображающего значение задержки элементов задержки. Сформированный выходной код ПЗУ (фиг. 6д) со

Q второго выхода блока 9 синхронизации записывается в блок 26 индикации, одновременно в более старшие разряды блока 26 записывается выходной код счетчика 6. На этом преоб- г разование заканчивается, блок 26 индикации хранит и индицирует результат преобразования до следующего цикла преобразования.

После записи результата преобразования в блок 16 индикации на вход установки исходного состояния блоков П и 12 Преобразования и счетчика 6 поступает импульс (фиг. бе) с третьего выхода блока 9 синхронизации. Этот же импульс запускает формирова- - тель 10 (фиг. 5), выходной сигнал с второго выхода (фиг. 6ж) которого поступает на вход установки исходного состояния счетчика 17 в датчике

0

5

14 и устанавливает исходное состояние счетчика 17. Затем на первом выходе формирователя 10 формируется импульс длительностью Т, (фиг. бз), который, поступив на первый вход датчика 14, разрешает работу, генератора 15. Импульсы (фиг. 6и) генератора 15 поступают на вход счетчика 17, который к концу сигнала длительностью Тр (фиг. 6э)устанавли- вается в состояние, соответствующее формуле (2). В момент окончания сигнала на первом входе датчика 14 (фиг. 6з) происходит запуск ждущего мультивибратора 18,, который фор- мирует импульс (фиг, 6к) записи кода счетчика 17 в регистр 19. На этом заканчивается цикл обновления информации о состоянии задержки элементов задержки блоков 11 и 12. При необхо- димости (например, при настройке) формирователь 14 может быть отключен замыканием выключателя 43, что блокирует запуск триггера 36.

Работа блока 9 синхронизации про- исходит следующим образом.

В исходном состоянии D-триггер 28 закрывает своим выходным сигналом генератор 29 с запаздывающей обратно связью . При этом также закрыт и уста новлен в нулевое состояние счетчик 30 и на выходе дешифратора 31 импульсы отсутствуют. С приходом запускающего периода на вход D-триггера 27 (в момент времени возврата в исходно состояние D-триггера 3) последний переходит в нулевое состояние и устанавливает своим выходным сигналом в единичное состояние D-триггер 28. При этом сигнал с нулевого выхода D-триггера 28 возвращает в исходное (единичное) состояние D-триггера 27 и открывает для приема счетных импульсов счетчик 30, а также подготавливает дешифратор 31. Сигнал разрешения с единичного выхода D-триггера 28 открывает генератор 29, выходные импульсы которого поступают на вход счетчика 30 и вход разрешения дешифратора 31. При этом на выходе дешифратора 31, соответствующем нулевому состоянию счетчика 30, появляется импульс, который, пройдя через инвертор 32, поступает на первый вход блока 9 синхронизации. На второй блока 9 импульс посту- пает при наличии состояния 001 в счетчике 30, на третий выход - при .наличии состояния счетчика - 010,

5 0

5

о

Q

0

т.е. выходные импульсы блока синхронизации разнесены во времени на период генератора 29. Третий импульс с выхода дешифратора поступает так- же на вход синхронизации D-триггера 28 и по своему срезу этот импульс возвращает D-триггер 28 в исходное (нулевое) состояние. При этом закрывается и сбрасывается в нулевое состояние счетчик 30, дешифратор 31 и генератор 29, что исключает формирование лишних импульсов.Работа формирователя 10 (фиг. 5) опорных временных интервалов происходит следующим образом.

В исходном состоянии D-триггеры 37 и 38 находятся в нулевом состоянии. При этом счетчик 41 закрыт и установлен в нулевое состояние сигналом с нулевого выхода D-триггера 38. D-триггер совместно с генератором 35 образуют ждущий мультивибратор, запускаемый перепадом напряже ния по входу синхронизации D-триггера 34. В исходном состоянии р-триггер 34 находится в нулевом состоянии, выключатель 43 разомкнут и на входе D- триггера 34 присутствует логическая единица. В момент поступления синхронизирующего перепада с третьего выхода блока 9 синхронизации происходит запуск мультивибратора на элементах 34 и 35, логическая единица с выхода D-триггера 34 последовательно проходит через элементы генератора 35, задерживаясь во времени из-за перезаряда конденсатора и инвертируясь каждым элементом генератора. Логический ноль на выходе генератора 35 возвращает D-триггер 34 в исходное (нулевое) состояние. Одновременно указанный сигнал устанавливает D-триггер 37 в единичное состояние и на D-вход D-триггера 38 поступает логическая единица. Ближайший перепад с вьгхода элемента 42 записывает логическую единицу в D-триггер 38, при этом открывается счетчик 4 и импульсы генератора 4 импульсов с второго входа формирователя 10 поступают в счетчик 41 до его полного заполнения, которое фиксируется элементом,И-НЕ 42. Выходной сигнал элемента 42 возвращает в, исходное состояние D-триггер-37. Далее логический ноль с выхода D-триггера 37 поступает на D-вход D-триггера 38 и ближайшим синхронизирующим перепадом записывается в D-триггер 38. Выходной сигнал с нулевого выхода ,D-тригге- ра 38 поступает на R-вход счетчика 41 и устанавливает его в исходное (нулевое) состояние. Таким образом, длительность Т нахождения D-триг- гера 38 в единичном состоянии равна сумме целого числа периодов генератора 4 импульсов, поскольку D-триггер 38 устанавливается как в единичное, так и в нулевое состояние по

первого и второго блоков преобразования, третьим входом счетчика и первым входом формирователя опорных временных интервалов, а вход блока синхронизации подключен к второму выходу D-триггера, второй вход формирователя опорных временных интервалов подключен к выходу генератора импульсов, а первый и второй выходы JQ формирователя опорных временных интервалов соединены соответствнно с первым и вторым входами датчика состояния элементов задержки.

2 Преобразователь по п. 1, о т импульсам с выхода инвертора 39.

Результат преобразования временного интервала ь цифровой код в пред- ли ч ающий с я тем, что датчик лагаемом устройстве определяется сог- состояния элементов задержки содержит регистр, счетчик, ждущий мультивибратор и генератор с запаздывающей обратной связью, вход разрешения ко- 2Q торого объединен с входом ждущего мультивибратора и подключен к первому

ласно формуле

-

- X где t.,

пГ -н (p-q) 2г, - преобразуемый временной интервал; число целых периодов o

п to q уместившихся в t (фиксируется счетчиком 6); период генератора 4; р и q - результаты преобразования соответственно блока 11 и блока 12 (начального и конечного участков несинхронности) ; t - задержка в одном элементе

задержки;

2 - числовой коэффициент, учи-, тывающий использование в блоках 11 и 12 в качестве единицы задержки двух элементов с задержкой.

Формула изобретения

1. Преобразователь интервалов времени в цифровой код по авт. св. № 930217, отличающийся тем, что, с целью повьш1ения точности преобразования, в него введены блок синхронизации, формирователь опорных временных интервалов и датчик состояния элементов задержки, выходные шины которого подключены к соответствующим входам третьей группы входов блока дешифрирования и индикации, выход которого соединен с вторым входом счетчика, выходные шины которого подключены к четвертой группе входов блока дешифрирования и индикации, шестой и седьмой входы которого соединены соответственно с первым и вторым выходами блока сйн- хронйзации, третий выход которого соединен с объединенными R-входами

входу датчика состояния элементов

задержки, а выход

генератора соединен с первым входом счетчика, вто- 25 рой вход которого объединен с вторым входом датчика состояния элементов задержки, выходная шина которого подключена к выходам регистра, входы разрядов которого соединены с выхо- 3Q дами соответствующих разрядов счетчика, а вход записи регистра подключен к выходу ждущего мультивиб-., ратора.

35

40

45

50

55

3. Преобразователь по п. I, о т - личающийся тем, что блок дешифрирования и индикации содержит первый и второй преобразователи кодов, устройство вычитания, элемент И-НЕ, постоянное запоминающее устройство и блок индикации, первая группа информационных входов которого соединена с соответствующими входами четвертой группы входов блока дешифрирования и индикации, а вторая группа информационных входов блока индикации подключена к соответствующим выходам постоянного запоминающего устройства, первая группа адресных входов которого соединена с соответствующими входами третьей группы входов блока дешифрирования и индикации, а вторая группа входов постоянного запоминающего, устройства подключена к соответствующим выходам устройства вычитания, выход признака превышения вычитаемого над уменьшаемым (заема) которого соединен с соответствующим

первого и второго блоков преобразования, третьим входом счетчика и первым входом формирователя опорных временных интервалов, а вход блока синхронизации подключен к второму выходу D-триггера, второй вход формирователя опорных временных интервалов подключен к выходу генератора импульсов, а первый и второй выходы формирователя опорных временных интервалов соединены соответствнно с первым и вторым входами датчика состояния элементов задержки.

2 Преобразователь по п. 1, о т ли ч ающий с я тем, что датчик состояния элементов задержки содержит регистр, счетчик, ждущий мультивибратор и генератор с запаздывающей обратной связью, вход разрешения ко- торого объединен с входом ждущего мультивибратора и подключен к первому

входу датчика состояния элементов

задержки, а выход

генератора соединен с первым входом счетчика, вто- рой вход которого объединен с вторым входом датчика состояния элементов задержки, выходная шина которого подключена к выходам регистра, входы разрядов которого соединены с выхо- дами соответствующих разрядов счетчика, а вход записи регистра подключен к выходу ждущего мультивиб-., ратора.

5

0

5

0

5

3. Преобразователь по п. I, о т - личающийся тем, что блок дешифрирования и индикации содержит первый и второй преобразователи кодов, устройство вычитания, элемент И-НЕ, постоянное запоминающее устройство и блок индикации, первая группа информационных входов которого соединена с соответствующими входами четвертой группы входов блока дешифрирования и индикации, а вторая группа информационных входов блока индикации подключена к соответствующим выходам постоянного запоминающего устройства, первая группа адресных входов которого соединена с соответствующими входами третьей группы входов блока дешифрирования и индикации, а вторая группа входов постоянного запоминающего, устройства подключена к соответствующим выходам устройства вычитания, выход признака превышения вычитаемого над уменьшаемым (заема) которого соединен с соответствующим

13

входом постоянного запоминающего устройства и первым входом элемента И-НЕ, второй.вход которого подключен к шестому входу блока дешифриро вания и индикации, а выход элемента И-НЕ.соединен с выходом блока дешиф рирования и индикации, седьмой вход которого подключен к третьему входу записи блока индикации, первая груп

( 1-й ewd

1-я ept/fmo 2-л tpumxt Wecfnou efodoS Sjraffffff Jfod

25598414

па входов устройства вычитания подключена через первый преобразователь кодов к соответствующим входам первой группы входов блока дешифрирова- J кия и индикации, вторая группа входов которого через второй преобразователь кода соединена с соответствующими входами группы входов устройства вычитания.

Z-й

фиг. 2

eujfoif y-Mtpynf -ffpya/m

fjFSffoffitffSffe

(pifsJ

2-й

f-u

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь интервалов времени в цифровой код | 1980 |

|

SU930217A1 |

| СПОСОБ ПОМОЩИ ВОДИТЕЛЯМ ПРИ ПЕРЕСТРОЕНИЯХ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2016 |

|

RU2646782C2 |

| Устройство для измерения скорости движения моделей | 1986 |

|

SU1448282A1 |

| СПОСОБ АВТОМАТИЧЕСКОГО ГРУППОВОГО ВОЖДЕНИЯ ДОРОЖНЫХ МАШИН И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2017 |

|

RU2664033C1 |

| Устройство для контроля электропотребления | 1988 |

|

SU1566371A1 |

| Устройство для преобразования телеграфного кода в видеокод | 1985 |

|

SU1314461A1 |

| Измеритель временных интервалов | 1967 |

|

SU737915A1 |

| Преобразователь частоты в код | 1990 |

|

SU1751851A1 |

| Устройство задержки импульсов | 1980 |

|

SU917326A1 |

| Устройство для программного счета штучных изделий | 1981 |

|

SU964678A1 |

Изобретение относится к импульсной технике и является дополнительным к авт. св. № 930217. Цель изобретения - повышение точности преобразования. Устройство содержит триггер 1, инвертор 2, D-триггер 3, генератор 4 счетных импульсов, вентиль 5, счетчик 6, блоки 7 и 8 выделения, блоки 11 и 12 преобразования и блок 13 дешифрирования и индикации. Введение блока 9 синхронизации, формирователя 10 опорных временных интервалов и датчика 14 состояния элементов задержки уменьшает погрешность преобразования, .обусловленную изменением веса хронирующего элемента из-за априорной неизвестности величины задержки, 2 з.п. ф-лы, 6 ил. С/пар/п to 01 сд со 00 4 КЗ сриг1

a.

б S г д e ж

3 и

Редактор Н. Данкулич

физ.6

Составитель В. Котов Техред И.Попович

Заказ 4821/46Тираж 398Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Раушская наб., д..4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Тог,

IllliniHIIIIIII

Л

Корректор М, Пожо

| Преобразователь интервалов времени в цифровой код | 1980 |

|

SU930217A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-09-07—Публикация

1984-05-24—Подача