(54) УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Система стабилизации задержки | 1981 |

|

SU957422A1 |

| Устройство задержки | 1978 |

|

SU769722A1 |

| Преобразователь кода в длительность задержки сигнала | 1985 |

|

SU1287292A1 |

| Устройство задержки | 1980 |

|

SU884111A1 |

| Шифратор-дешифратор | 1981 |

|

SU1005295A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2006 |

|

RU2309430C1 |

| Цифровой фазометр-частотомер | 1987 |

|

SU1471148A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

: ., I . .;

Изобретение относится к импуль;Сной технике и может быть использовано Б радионавигационных дальномерных и угломёрно дальномерных системах для повышения точности измерения наклонной дальности.

Сфера использования устройства может распространяться на другие радиотехнические системы, в которых имеется необходимость осуществлять задержку импульсных сигналов с высокой точностью, и которые содержат в своем составе устройства, йз- меняющие свою задержку под воздействием различных факторов. Например, приемное и передающее устройства изменяют время распространения сигнала в зависимости от воздействия внешних условий и др.

Известно устройство, содержащее регистр сдвига, коммутатор, дешиф ратор, .генератор тактовых импульсов, калибратор длительности видеоимпульсов, состоящий из генератора одиночных импульсов и триггера, счетчик импульсов и блок начальной установки емкости счетчика, состоящий из статического регистра коммутатора и формирователя импульса записи кода в счетчик,регистр сдвига подключен к входной шине устройства через упомянутый калибратор длительности видеоимпульсов, а генератор тактовых импульсов подключен к тактовой шине регистра сдвига через последовательно соединенные умножитель частоты тактовых импульсов и упомянутый счетчик, при зтом выход умножителя частоты тактовых импульсов

15 подключен к формирователю одиночных импульсов калибратора к формирователю импульсов записи кода в счетчик.

Недостатком этого устройства

20 является невысокая разрешающая способность.

Известно устройство задержки,которое содержит датчик кода,генератор

подключенный ко,входу счетчика регистр сдвига, блок управления, блок ввода и сумматор, информационные входы- которого поразрядно объединены с выходами разрядов регистра и датчика крда, а выход сумматора присоединен к первому входу блока управления и входу датчика кода, второй и третий входы блока управления подключень соответственно к выходу генератора и дополнител ному выходу регистра, а его вход соединен с вычитающим входом сумматора, вход устройства параллельно подключен к первьом входам ключе

блока ввода, подключенного ко входам

регистра, вторые входы которых црисоединены соответственно к выходам разрядов счетчика, выходом подключенного к входу синхронизации регистра,, а вторая группа выходов датчика кода подключена к соответст- вующим входам регистра.

Однако известное устройство имеет невысокую разрешающую способность и сложность.

Наиболее близким по технической сущности является устройство задержки импульсов, содержащее основную линию задержки, вход которой соединен с источником контрольных импульсов, дополнительную линию задержки с отводами, включенную последовательно с основной , временной дискриминатор, двоичный счетчик, дешифратор чисел, нормирователь импульсов по длительности , элемент ИЛИ, п-триггеров, п + 1 элементов И, при этом отводы дополнительной линии задержки через п элементов И подключены ко входам элемента ИЛИ, выход коч-орого через нормирователь импульсов по длительности соединен с одним из входов П + 1-ГО -элфмента И, выход которого, через временной дискриминатор подключен ко входу двоичного счетчика, к поразрядным выходам счетчика подключены соответствующие входы дешифратора, причем i-и выход дешифратора подключен ко входу установки i-го триггера и к входу установки в 1 i+1-по триггера, выход дешифратора - к входу установки в О п-го триггера и к входу установки в 1 первого триггера, выходы всех триггеров подключены к вто рьп-1 входам п элементов И, а вход осг новчой пинии соединен со вторым входок п+1-го элемента И.

Основньм недостатком известного устройства является сложность и малая надежность задерживающего уст- : ройства за счет применения дополнительной линии задержки и ее схемы управления.

Цель изобретения - упрощение устройства и повышение его надежности

Для достижения указанной цели в устройство для задержки импульсов, содержащее линию задержки, вход которой соединен с источником контрольных сигналов и временной дискриминатор, введены блок привязки, запоминающее .устройство,, преобразователь время-код, сумматор и преобразователь код-время, при этом выходы блока привязки и запоминающего устройства соединены с входами сумматора, выходы которого подсоединены к входам линии задержки, вход синхронизации которой подключен к выходу делителя частоты блока привязки, выход линии задержки через преобразователь код-время подключен к первому входу временного дискриминатора, другой вход которого подключен к выходу источника контрольных импульсов, выход дискриминатора через преобразователь время-код присоединен к входам запоминающего устройства, управляющий вход запоминающего устройства, и блока привязки соединены с входом устройства и выходом источника контрольных импульсов..

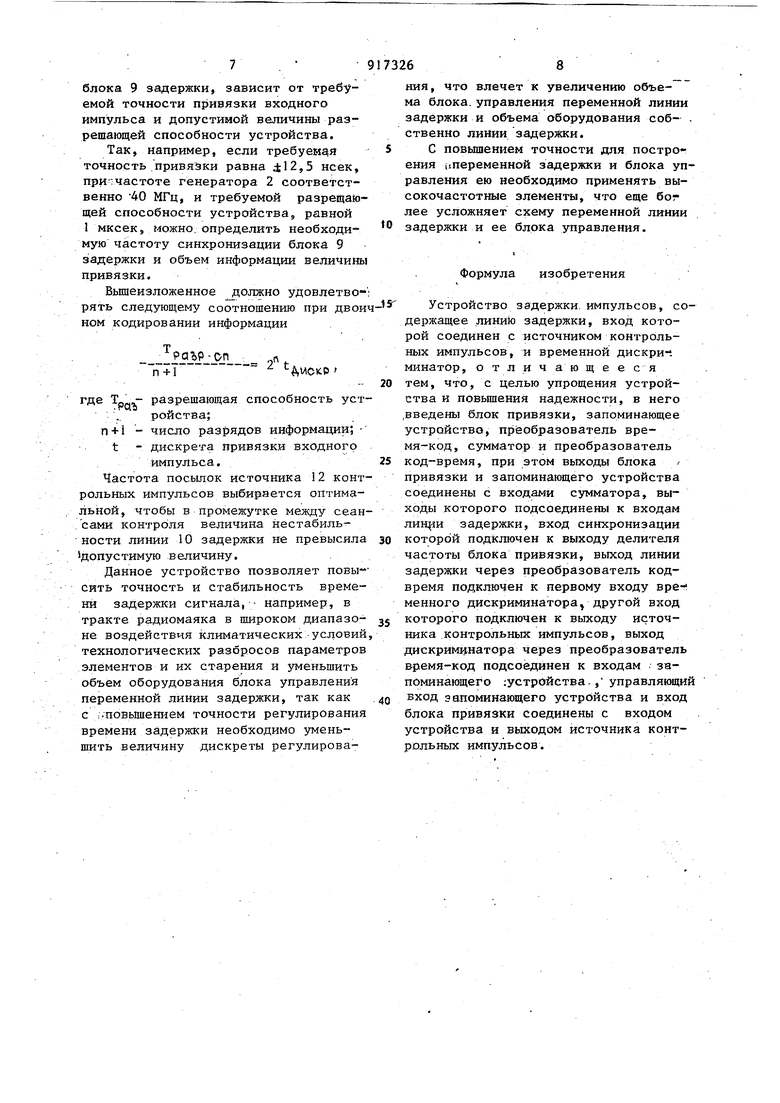

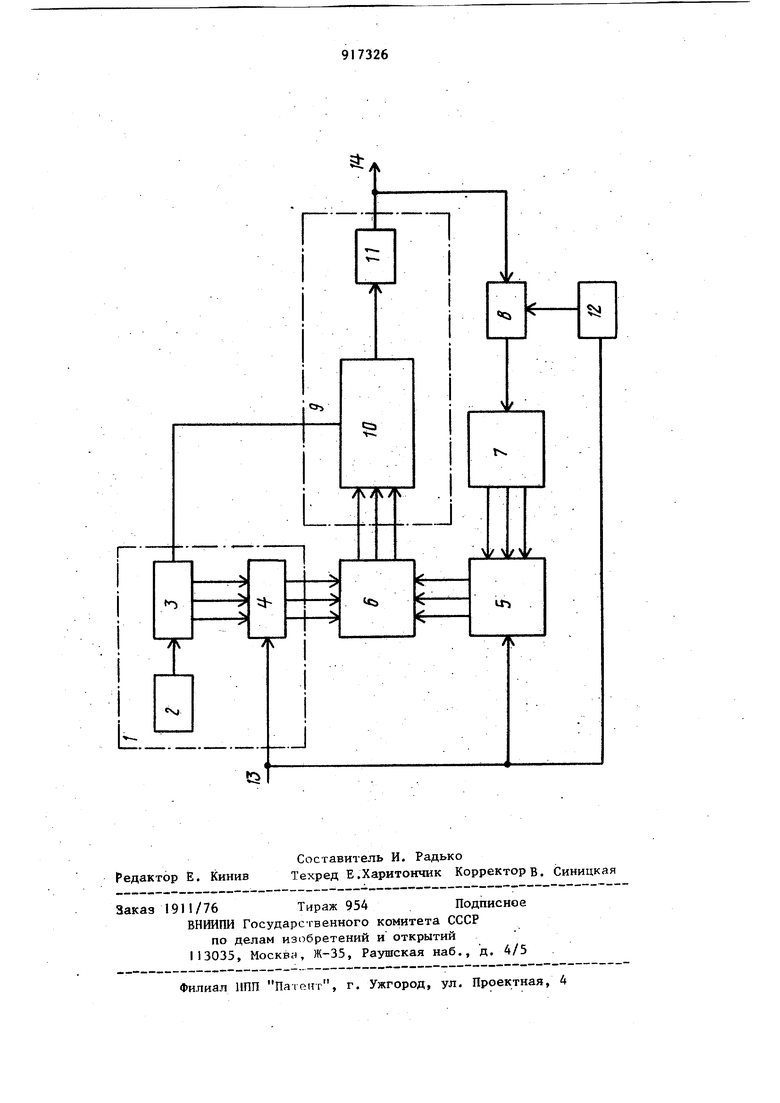

На чертеже приведена функционалЬ ная электрическая схема устройства.

Устройство содержит блок 1 привязки, содержащий генаратор 2 высокой частотыу делитель 3 частоты и блок 4 вывода, запоминающее устройство 5, сумматор 6, преобразователь 7 время-код , временной дискриминатор 8, блок 9 задержки, содержащий последовательно соединенные линию to задержки, и преобразователь 11 код-время, источник 12 контрольных импульсов входную клемму 13 и выходную клемму 14 устройства.

Устройство работает следующим образом.

На Вход блока 1 привязки (блок 4 вывода) и управляющий вход запоминаю щего устройства 5 подаются импульсы с выхода источника 12 контрольных импульсов со стабильным периодом, длительность которого равна величине времени задержки контролируемой линии задержки. Дальнейшее прохождение сигналов по схеме начнем рассматривать с момента, когда устройство находится в неходном состоянии. В ячейках запомин ющего устройства 5 хранится значение величины коррекции времени, равного величине разницы между величиной за держки устройства на данный момент и величиной периода между импульсами источник а 12 контрольных импульсо принятого за эталон. Величина временного рассогласования определяется на временном дискри минаторе 8, на один вход которого по даются импульсы с выхода источника контрольных импульсов, а на другой вход поступают импульсы с выхода бло 9 задержки. Полученный временной интерзал. преобразовывается в код на преобразователе 7 .время-код и затем записывается в ячейки памяти запоминающего устройства 5. При отсутствии импульсов на входной клемме 13 устройства, импульсы синхронизации продолжают поступать с выхода делителя 3 частоты, блока I привязки, на синхронизирующий вход блока 9 задержки, по которому распрротраняется нулевая информация. Входной импульс поступает через входную клемму. 13 на вход блока 1 привязки, управляющий вход блока 4 вывода и управляющий вход запоминающего устройства 5. С помощью этого устройства дости гается высокай точность привязки по времени входного импульса к импульсам синхронизации цифрового блока 9 задержки. Привязки осуществляются посредством блока 4 вывода, который считывает код с выходов делителя 3.частоты в момент воздействия входного им пульса. Код снятый с выходов делителя 3 частоты пропорционален времени рассогласования входного импульса и импульсов синхронизации блока 9 за.держки. :. Известно, что с повьшенйем точности и стабильности времени задержки необходимо увеличивать частоту импульсов генератора 2,что одновременно ведет к увеличению объема линии задержки, при условии отсутствия блока I привязки. Сохранение кода привязки при его распространении в блоке 9 задержки и последую111ее его преобразование во временной интервал , позволяет выполнить привязку на высокой частоте, а так как частота импульсов синхронизации блока задержки в 2 раз ниже частоты генератора 2, что позволяет снизить объем линии задержки в п раз.. Код привязки ,с выхода блока I привязки поступает на вход сумматоpai 6, на вторые входы которого поступает информация, соответствующая величине рассогласования на данный момент с выходов запоминающего устройства 5. . Сумматор 6 осуществляет сложение постпупивших на его входы информации с учетом знака информации с выхода запоминающего устройства 5. Информация (результат) сложения с выхода сумматора 6 поступает на входы блока 9 задержки, где она записывается и распространяется по линии 10 задержки под воздействием импульсов синхронизации. Корректированный код привязки с выхода линии 10 задержки поступает на вход преобразователя 11 код-время. . Таким образом, импульс, поступивщий на вход устройства задержки, считывает посредством блока 4 вьшода блока 1 привязки код привязки, максимальное значение которогосоответствует величине периода импульсов синхронизации блока 9 задержки. И одновременно информацию с запоминающе- го устройства 5, где. записан код величины разности времени задержки устройства и эталонного времени. Сумматор 6 осуществляет корректировку величины кода привязки с учетом информации с выходов запоминающего устройства 5 для каждого входн®го импульса. Так как информация временной привязки (код привязки) входного импульса к импульсам синхронизации и информация кода рассогласования времени задержки устройства и величиной эталонного времени выражены в коде, например, двричном, то на выходе блока 9 задержки установлен преобразователь 11 код-время. Объем информации, соответствующий величине времени привязки входного импульса к импульсу синхронизации блока 9 задержки, зависит от требуемой точности привязки входного импульса и допустимой величины разрешающей способности устройства. Так, например, если требуеиая точность .привязки равна il2,5 нсек, при-;частоте генератора 2 соответственно 40 МГц, и требуемой разрещаю щей способности устройства, равной 1 мксек, можно, определить необходимую частоту синхронизации блока 9 задержки и объем информации величины привязки. Вышеизложенное должно удовлетворять следующему соотношению при двои ном кодировании информации -If оп. п + Г t wcicP где Т--.,- разрешающая способность уст ройства; п + 1 - число раз{)ядов информации; t - дискрета привязки входного импульса. Частота посылок источника 12 конт рольных импульсов выбирается оптимальной, чтобы в промежутке между сеан . сами контрсрля величина нестабильности линии 10 задержки не превысила допустимую величину. Данное устройство позволяет повы сить точность и стабильность времени задержки сигнала, например, в тракте радиомаяка в широком диапазоне воздействия климатических условий технологических разбросов параметров элементов и их старения и уменьшить объем оборудования блока управлений переменной линии задержки, так как с /.повышением точности регулирования времени задержки необходимо уменьшить величину дискреты регулирования , что влечет к увеличению объема блока.управления переменной линии задержки и объема оборудования соб- . ственно линии задержки. С повышением точности для построения (переменной задержки и блока управления ею необходимо применять высокочастотные элементы, что еще бог лее усложняет схему переменной линии задержки и ее блока управления. Формула изобретения Устройство задержки, импульсов, содержащее задержки, вход которой соединен с источником контрольных импульсов, и временной дискриминатор, отличающееся тем, что, с целью упрощения устройства и повьшения надежности, в него .введены блок привязки, запоминающее устройство, преобразователь время-код, сумматор и преобразователь код-время, при этом выходы блока привязки и запоминающего устройства соединены с входами сумматора, выходы которого подсоединены к входам задержки, вход синхронизации которой подключен к выходу делителя частоты блока привязки, выход линии задержки через преобразователь кодвремя подключен к первому входу временного дискриминатора другой вход которого подключен к выходу источника контрольных импульсов, выход дискриминатора через преобразователь время-код подсоединен к входам запоминающего :устройства., управляющий вход запоминающего устройства и вход блока привязки соединены с входом устройства и выходом источника контрольных импульсов.

гт

,L

fn

L.

.J

п

/ЧУГ

I

u

/.

Авторы

Даты

1982-03-30—Публикация

1980-08-15—Подача