Изобретение относится к электро- гехнике и может быть использовано для управления тиристорными выпря- мительно-инверторными преобразователями с фазрвьтм регулированием напряжения.

Цель изобретения - повышение энергетических показателей преобразователей и их устойчивости за счет повышения точности синхронизации и исключения асимметрии импульсов по полупериодам питающего напряжения.

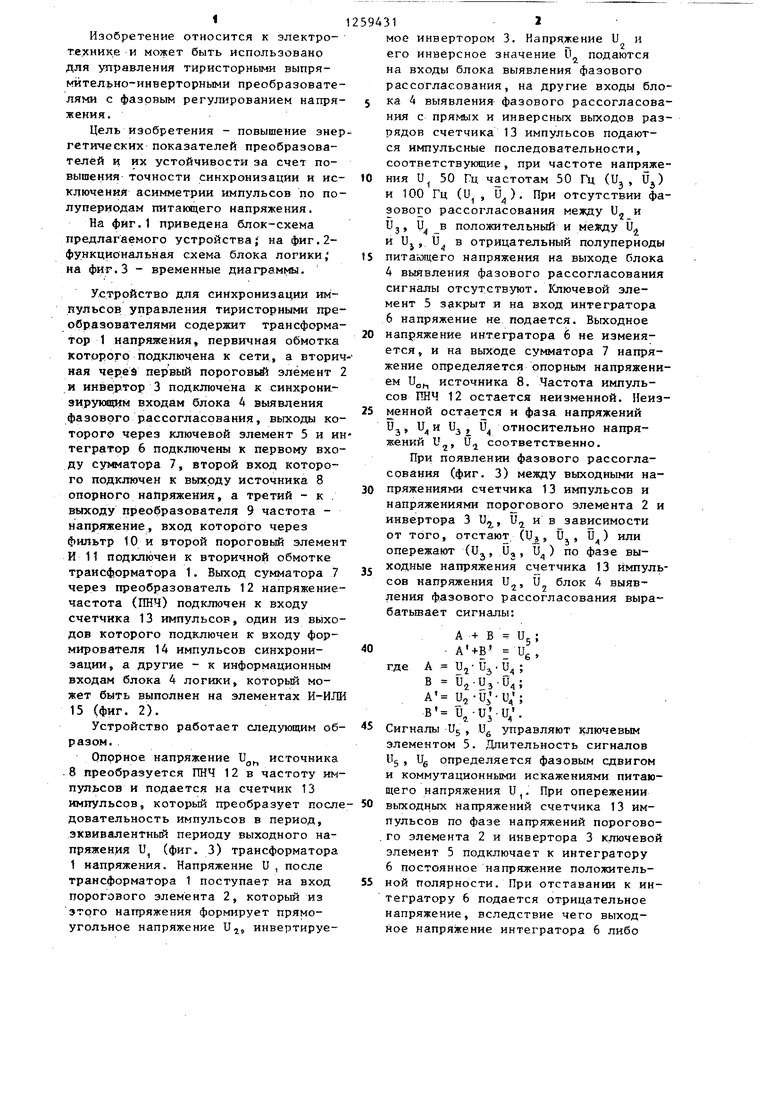

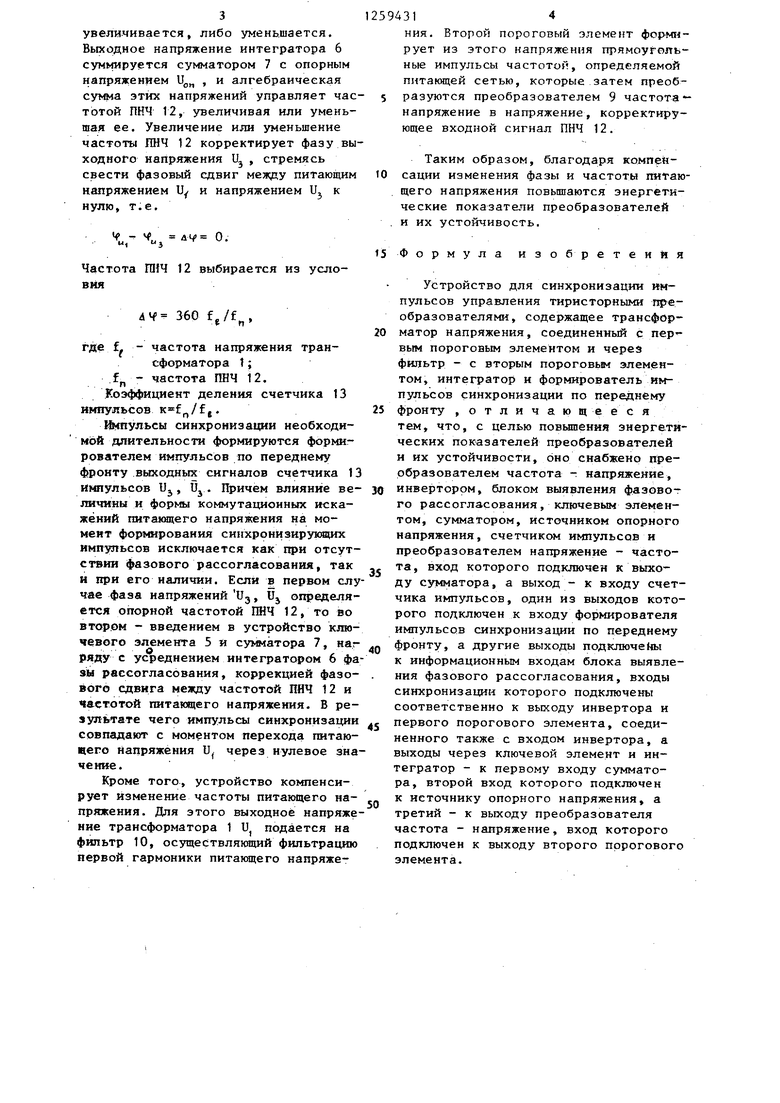

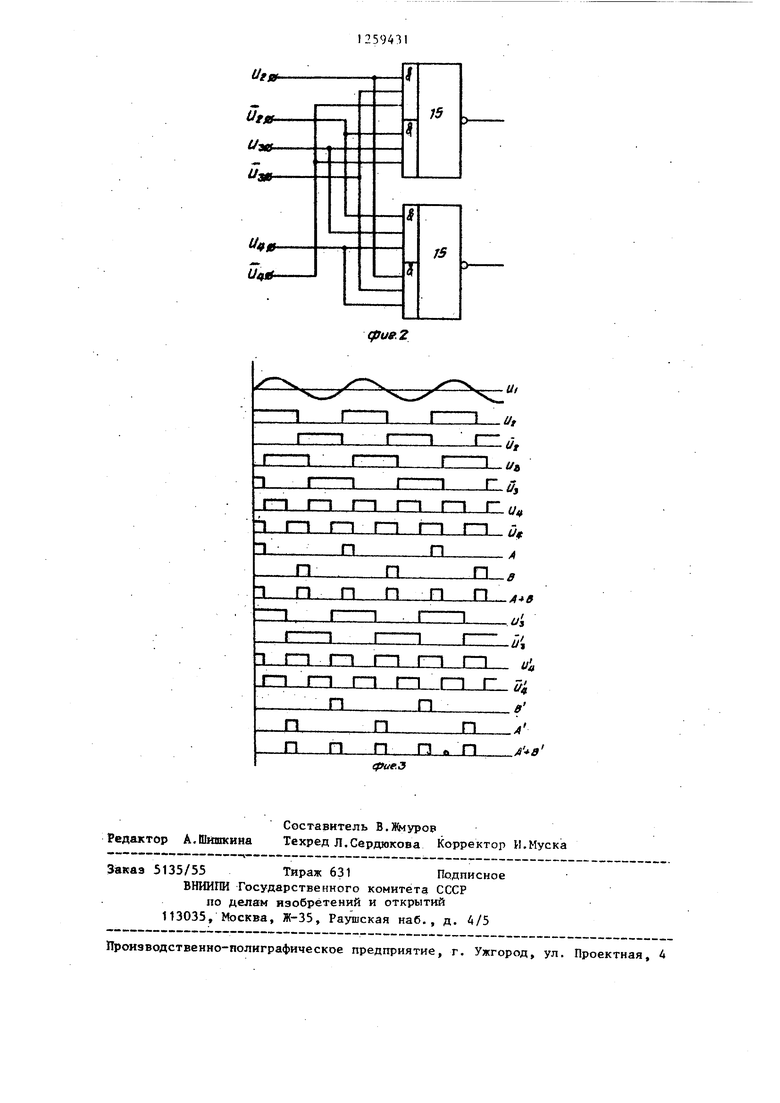

На фиг.1 приведена блок-схема предлагаемого устройства; на фиг.2- функциональная схема блока логики; на фиг.З - временные диаграммы.

Устройство для синхронизации импульсов управления тиpиcтopны и преобразователями содержит трансформатор 1 напряжения, первичная обмотка которого подключена к сети, а вторич ная череЭ первый noporoai элемент 2 и инвертор 3 подключена к синхрони- эирукщим входам блока А выявления фазового рассогласования, выходы которого через ключевой элемент 5 и интегратор 6 подключены к первому входу сумматора 7, второй вход которого подключен к выходу источника 8 опорного напряжения, а третий - к . выходу преобразователя 9 частота - напряжение, вход которого через фильтр 10 и второй пороговый элемент И 11 подкл1бчен к вторичной обмотке трансформатора 1. Выход сумматора 7 через преобразователь 12 напряжение- частота (ПНЧ) подключен к входу счетчика 13 импульсов, один из выходов которого подключен к входу формирователя 14 импульсов синхронизации, а другие - к информационным входам блока 4 логики, который может быть выполнен на элементах И-ИЛИ 15 (фиг. 2).

Устройство работает следующим образом.

Опорное напряжение U источника .8 преобразуется ПНЧ 12 в частоту им- пупьсов и подается на счетчик 13 импульсов, который преобразует последовательность импульсов в период, эквивалентный периоду выходного напряжения и (фиг. 3) трансформатора 1 напряжения. Напряжение U , после трансформатора 1 поступает на вход порогового элемента 2, который из этого напряжения формирует прямоугольное напряжение U-j, инвертируемое инвертором 3. Напряжение U н его инверсное значение U, подаются на входы блока выявления фазового рассогласования, на другие входы блока 4 выявления фазового рассогласования с прямых и инверсных выходов разрядов счетчика 13 импульсов подаются импульсные последовательности, соответствующие, при частоте напряжения и 50 Гц частотам 50 Гц (Uj, Uj) и 100 Гц (и , и). При отсутствии фазового рассогласования между U и Uj, и в положительный и между 0, и Uj, и в отрицательный полупериоды

питакяцего напряжения на выходе блока 4 выявления фазового рассогласования сигналы отсутствуют. Ключевой элемент 5 закрыт и на вход интегратора 6 напряжение не подается. Выходное

напряжение интегратора 6 не изменяется , и на выходе сумматора 7 напряжение определяется опорным напряжением UQ источника 8. Частота импульсов ПНЧ 12 остается неизменной. Неизменной остается и фаза напряжений Uj, и и и , и относительно напряжений U,j, 0/1 соответственно.

При появлении фазового рассогласования (фиг. 3) между выходными напряжениями счетчика 13 импульсов и напряжениями порогового элемента 2 и инвертора 3 U, U и в зависимости от того, отстают, (и, 0 , U) или опережают (U,, U,, U) по фазе выходные напряжения счетчика 13 импульсов напряжения U, U блок 4 выявления фазового рассогласования выра- батьюает сигналы:

А + В Ujj

. А +В Ug , где А - Uj- Uj,- U ;

В и -Уэ-и ;

. А и,-из -и;;

.

Сигналы Uj, Ug управляют ключевым элементом 5. Длительность сигналов Ufi определяется фазовым сдвигом и коммутационными искажениями питающего напряжения U. При опережении

выходных напряжений счетчика 13 импульсов по фазе напряжений порогово- .го элемента 2 и инвертора 3 ключевой элемент 5 подключает к интегратору 6 постоянное напряжение положительной полярности. При отставании к интегратору 6 подается отрицательное напряжение, вследствие чего выходное напряжение интегратора 6 либо

3

увеличивается, либо уменьшается. Выходное напряжение интегратора 6 суммируется сумматором 7 с опорным напряжением U , и алгебраическая cyffl a этих напряжений управляет частотой ПНЧ 12, увеличивая или уменьшая ее. Увеличение или уменьшение частоты ПНЧ 12 корректирует фазу выходного напряжения U , стремясь свести Фазовый сдвиг между питающим напряжением U и напряжением Uj к нулю, т.е.

. V -.

Частота ПНЧ 12 выбирается из условия

44 360 fg/f,

где f, - частота напряжения трансформатора 1; f - частота ПНЧ 12.

Коэффициент деления счетчика 13 импульсов .

№тульсы синхронизации необходимой длительности формируются формирователем импульсов по переднему фронту выходных сигналов счетчика 13 импульсов Uj, Uj. Причем влияние величины и формы коммутационных искажений питанйцего напряжения на момент фор шрования снпхронизирующтс импульсов исключается как при отсутствии фазового рассогласования, так и при его наличии. Если в первом случае фаза напряжений Ug, Uj определяется опорной частотой ПНЧ 12, то во втором - введением в устройство кдао- чевого элемента 5 и сужатора 7, наг ряду с усреднением интегратором 6 фазы рассогласования, коррекцией фазового сдвига между частотой ПИЧ 12 и частотой питающего напряжения. В результате чего импульсы синхронизации совпадают с моментом перехода питаю- цего Напряжения U через нулевое значение.

Кроме того, устройство компенсирует Изменение частоты питающего напряжения. Для этого выходное напряжение трансформатора 1 U, подается на фильтр 10, осуществляющий фильтрацию первой гармоники питанлцего напряже4314

НИН, Второй пороговый элемент формирует из этого напряжения прямоугольные импульсы частотой, определяемой питающей сетью, которые затем преоб- разуются преобразователем 9 частота- напряжение в напряжение, корректирующее входной сигнал ПНЧ 12.

Таким образом, благодаря компен- сации изменения фазы и частоты питающего напряжения повышаются энергетические показатели преобразователей . и их устойчивость.

Формула изобретения

Устройство для синхронизации импульсов управления тиристорными преобразователями, содержащее трансформатор напряжения, соединенный с пер - вым пороговым элементом и череэ фильтр - с вторым пороговьм элементом, интегратор и формирователь импульсов синхронизации по переднему

фронту , отличающееся

тем, что, с целью повышения энергетических показателей преобразователей и их устойчивости, оно снабжено преобразователем частота -: напряжение,

инвертором, блоком выявления фазового рассогласования, ключевым элементом, сумматором, источником опорного напряжения, счетчике импульсов и преобразователем напряжение - частота, вход которого подключен к выходу сумматора, а выход - к входу счетчика импульсов, один из выходов которого подключен к входу формирователя импульсов синхронизации по переднему

фронту, а другие выходы подключены к информационным входам блока выявления фазового рассогласования, входы синхронизации которого подключены соответственно к выходу инвертора и

первого порогового элемента, соединенного также с входом инвертора, а выходы через ключевой элемент и интегратор - к первому входу сумматора, второй вход которого подключен к источнику опорного напряжения, а третий - к выходу преобразователя частота - напряжение, вход которого подключен к выходу второго порогового элемента.

(ftuff.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухотсчетный преобразователь угла поворота вала в код | 1985 |

|

SU1269265A1 |

| Следящая система | 1985 |

|

SU1290251A1 |

| Устройство для управления ведомым сетью инвертором | 1988 |

|

SU1603510A1 |

| Преобразователь мощности в частоту | 1983 |

|

SU1150568A1 |

| Преобразователь постоянного напряжения в постоянный ток | 1983 |

|

SU1117793A1 |

| Преобразователь кода в угловое положение вала | 1983 |

|

SU1088048A1 |

| Преобразователь угловых перемещений в код | 1985 |

|

SU1311024A1 |

| Электропривод | 1988 |

|

SU1656652A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1425832A1 |

| Грозопеленгатор-дальномер | 1984 |

|

SU1201790A1 |

Изобретение относится к электротехнике и может быть использовано для управления тиристорными вы- прямительно-инверторными преобразователями с фазовым регулированием напряжения. Целью изобретения является повышение энергетических показателей преобразователей и их устой- - чивости за счет повышения точности синхронизации и исключения асимметрии импульсов по полупериодам питающего напряжения. При опережении выходных напряжений счетчика импульсов 13 по фазе напряжений порогового элемента 2 и инвертора 3 блок выявления фазового рассогласования 4 через ключевой элемент 5 подключает к интегратору 6 постоянное напряжение положительной полярности, а при отставании - напряжение отрицательной полярности. Выходное напряжение интегратора 6 либо увеличивается, либо уменьшается. Это напряжение суммируется сумматором 7 с опорным напряжением и полученный сигнал , управляет частотой преобразователя . 12 напряжение - частота, увеличивая или уменьшая ее. Это изменение корр.ек- тирует фазу выходного ьапряжения.З ил. (Л ю СП со СО

| Веркович Е.И | |||

| и др | |||

| Полупроводниковые выпрямители | |||

| - М.: Энергия, 1976, с | |||

| Приспособление для градации давления в воздухопроводе воздушных тормозов | 1921 |

|

SU193A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ИМПУЛЬСОВ УПРАВЛЕНИЯ ТИРИСТОРНЫМ ПРЕОБРАЗОВАТЕЛЕМ | 1981 |

|

SU1001838A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-09-23—Публикация

1985-01-04—Подача