Изобретение относится к электросвязи и может быть использовано для контроля качества каналов в системах передачи дискретной информации.

Цель изобретения - сокращение времени измерения.

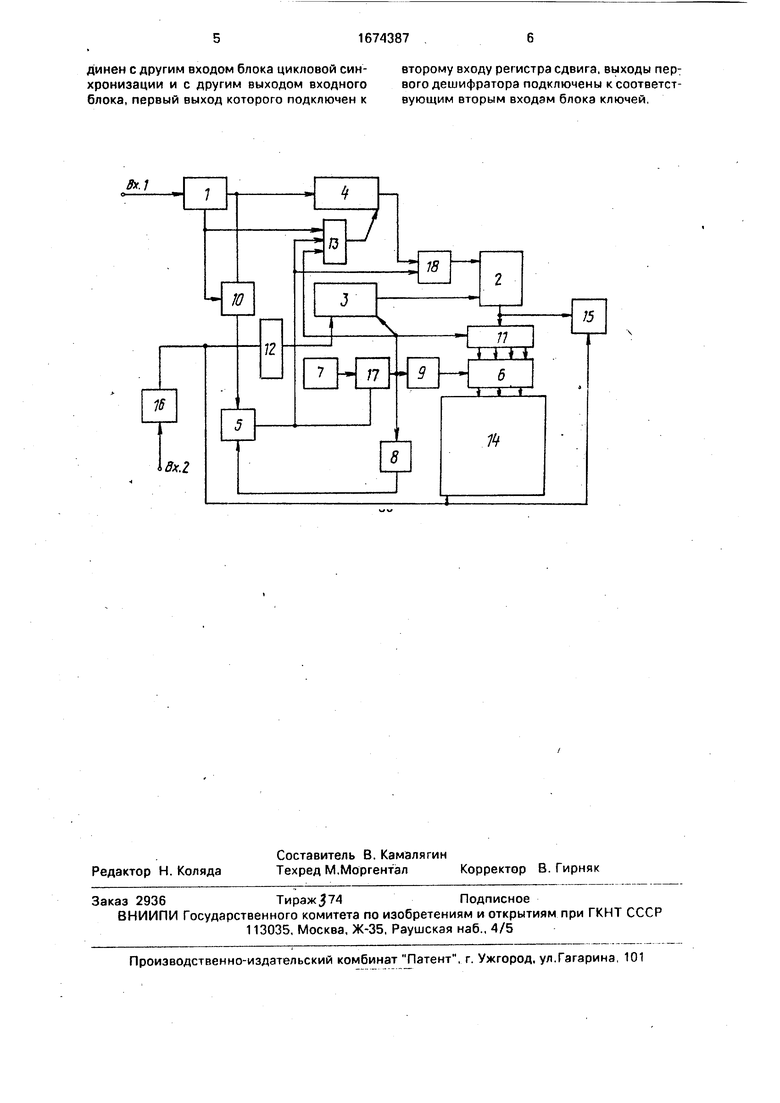

На чертеже представлена структурная схема устройства для определения достоверности передачи дискретной информации.

Устройство содержит входной блок 1, блок 2 сравнения, датчик 3 кодовых комбинаций, регистр 4 сдвига, триггер 5, блок 6 ключей, генератор 7 импульсов, делители 8 и 9 счета, блок 10 цикловой синхронизации, дешифраторы 11 и 12, элемент И-ИЛИ 13, блок 14 счетчиков, счетчики 15 и 16 и элементы И 17 и 18.

Устройство работает следующим образом.

Перед началом работы счетчик 16 устанавливается в исходное состояние.

В режиме приема из канала связи через входной блок 1 поступает тестовая последовательность и записывается в регистр 4 сдвига в соответствии с тактами, вырабатываемыми входным блоком 1. Тактовые импульсы от входного блока 1 проходят на вход регистра 4 сдвига через элемент И-ИЛИ 13, который при о сутствии потенциала с триггера 5 на персом входе разрешает прохождение сигналов, поступающих на третий вход.

Одновременно тестовая последовательность поступает на вход блока 10 цикловой синхронизации, который предназначен для приема последовательности той же структуры, что и тестовая. При приеме К неискаженных посылок подряд блок 10 формирует на выходе сигнал в момент окончания приема тестовой последовательности. Этим сигналом блок 14 счетчика 15 устанавливается в состояние О, а датчик 3 устанавливается в исходное положение. Одновременно триггер 5 устанавливается в состояние 1 и на его выходе появляется потенциал

Дешифратор 12 предназначен для формирования начальной комбинации и записи ее в датчик 3.

С появлением потенциала на втором входе элемент И 17 разрешает прохождение

сл

С

о VJ

CJ 00

XI

тактирующих импульсов от генератора 7 на тактовые входы датчика 3 кодовых комбинаций, регистра 4 сдвига через элемент И- ИЛИ 13 и дешифратор 11. Одновременно элемент И-ИЛИ 13 запрещает прохождение тактовых импульсов на регистр 4 от входного блока 1. Этим же потенциалом триггера 5 отпирается элемент И 18, разрешая прохождение импульсов принятой последовательности на блок 2 сравнения (режим сравнения).

Частота последовательности генератора 7 импульсов значительно больше частоты тактирования входным блоком 1. При выдаче генератора 7 N-ro импульса на выходе делителя 8 появится сигнал, устанавливающий триггер 5 в состояние О, запирая при огом элементы И 17 и 18 и разрешая запись в регистр А следующей тестовой последовательности из канала связи. В течение режима сравнений в блоке 2 сравнивается ровно N пар элементов последовательности, примятой из канала связи и эталонной.

В режиме сравнения в устройстве производятся две основные операции контроля качества канала: подсчет количества искаженных посылок во всей передающей последовательности счетчиком 15 сбоев: подсчет количества комбинаций, содержа- одну, две, ... п ошибок блоком 14 счетчиков искажения комбинаций.

При сравнении принятой эталонной последовательностей на выходе блока 2 формируется двоичная последовательность, соответствующая наличию и отсутствию искажений посылок в принятой по каналу связи тестовой последовательности (1 соответствует искажению посылки). Количе- CiBO искажений подсчитывается счетчиком 15 сбоев Одновременно последовательность поступает на вход дешифратора 11. Длина анализируемой комбинации задается первым делителем 9. коэффициент счета (деления) которого равен количеству разря- доз дешифратора 11. При появлении на входе дешифратора 11 сигнала блок 6 ключей отпирается и разрешает прохождение с одного из выходов дешифратора 11 импульса на тот счегчик, который в блоке 14 подсчитывает число комбинаций (блоков) с количествомискаженныхпосылок, соответствующее в данный момент состоянию дешифратора 11. В итоге к моменту окончания режима сравнения счетчик 15 находится в состоянии, соответствующем общему количеству сбоевв последовательности длиной N, а СИК-1, СИК-2, , СИК-п (16-1, ... 16-2, ... 16-п) - в состояниях, соответствующих количеству блоков длиной L, содержащих соответственно, одну, две... п ошибок. Увеличение показаний счетчика 16 на единицу показывает, что сеанс контроля состоялся.

Для обеспечения циклового фазирования и определения начала приема из канала тестовой последовательности с точностью, достигаемой в устройстве, как с точки зрения обеспечения заданной вероятности проведения сеанса, так и с точки зрения

0 защиты от ложного пуска и тем самым от проведения ложного сеанса, при цикловом фазировании традиционными способами необходимо предварить тестовую последовательность аналогичной синхронизирую5 щей последовательностью. Сеанс контроля канала в этом случае потребует примерно в два раза больше времени, чем сеанс контроля, проводимый с помощью данного устройства.

0 Значение К может быть выбрано из условия, что вероятность ложной синхронизации не превышает заданную величину. Формула изобретения Устройство для определения достовер5 ности передачи дискретной информации, содержащее блок счетчиков, первый счетчик, последовательно соединенные входной блок, вход которого является первым входом устройства и блок цикловой синхрони0 зации, последовательно соединенные датчик кодовых комбинаций, блок сравнения и первый дешифратор, выход блока сравнения подключен к первому входу первого счетчика, отличающееся тем, что,

5 с целью сокращения времени измерения, в него введены второй счетчик, первый вход которого является вторым входом устройства, второй дешифратор и последовательно соединенные генератор импульсов, первый

0 элемент И, первый делитель счета, триггер, элемент И-ИЛИ. регистр сдвига и второй элемент И, выход которого подключен к другому входу блока сравнения, последовательно соединенные второй делитель счета

5 и блок ключей, выходы которых подключены к соответствующим информационным входам блока счетчиков, установочный входко- торого соединен с вторыми входами первого и второго счетчиков, с выходом бло0 ка цикловой синхронизации, с другим входом триггера, с входом второго дешифратора, выход которого подключен к первому входу датчика кодовых комбинаций, второй вход которого соединен с вто5 рым входом первого дешифратора, с выходом первого элемента И, с входом второго делителя счета и с вторым входом элемента И-ИЛИ, первый вход которого соединен с другими входами первого и второго элемента И, третий вход которого соединен с другим входом блока цикловой синхронизации и с другим выходом входного блока, первый выход которого подключен к

второму входу регистра сдвига, выходы первого дешифратора подключены к соответствующим вторым входам блока ключей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Двухканальное устройство для сопряжения ЭВМ | 1989 |

|

SU1735860A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Устройство для адаптивного мажоритарного декодирования фазирующих сигналов | 1984 |

|

SU1213492A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| Устройство избирательного вызова и передачи кодограмм | 1983 |

|

SU1136326A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2009 |

|

RU2450465C2 |

| Стартстопное приемное устройство | 1985 |

|

SU1259506A1 |

| Устройство цикловой синхронизации блочных кодов | 1989 |

|

SU1688434A1 |

Изобретение относится к электросвязи. Цель изобретения - сокращение времени измерения. Устройство содержит входной блок 1, блок 2 сравнения, датчик 3 кодовых комбинаций, регистр 4 сдвига, триггер 5, блок 6 ключей, генератор 7 импульсов, делители 8 и 9 счета, блок 10 цикловой синхронизации, дешифраторы 11 и 12, элемент И - ИЛИ 13, блок 14 счетчиков, счетчики 15 и 16 и элементы И 17 и 18. В блоке 2 сравниваются последовательности, принятые из канала связи, и эталонная. 1 ил.

| 1972 |

|

SU422111A1 | |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-08-30—Публикация

1989-12-08—Подача