12

элемента И соединен с объединенными вторыми входами второго элемента ИЛИ и регистра приема, третий вход рого соединен с выходом блока свёртки по модулю три, один из выходов дешифратора счетчика длины слова соединен с вторым входом первого элемента ИЛИ к с другим входом элемента И-НЕ, выход которого является первым выходом последовательно-парахс- лельного преобразователя, второй выход триггера окончания передачи соединен с вторым входом первого элемента И, третий вход которого является первым входом последовательно-параллельного преобразователя, первым, ВТО1ДЫМ, третьим входами последова1

Изобретение относится к радиотехнике и может быть использовано в телеграфной аппаратуре Передачи данных.

Цель изобретения - повышение помехозащищенности.

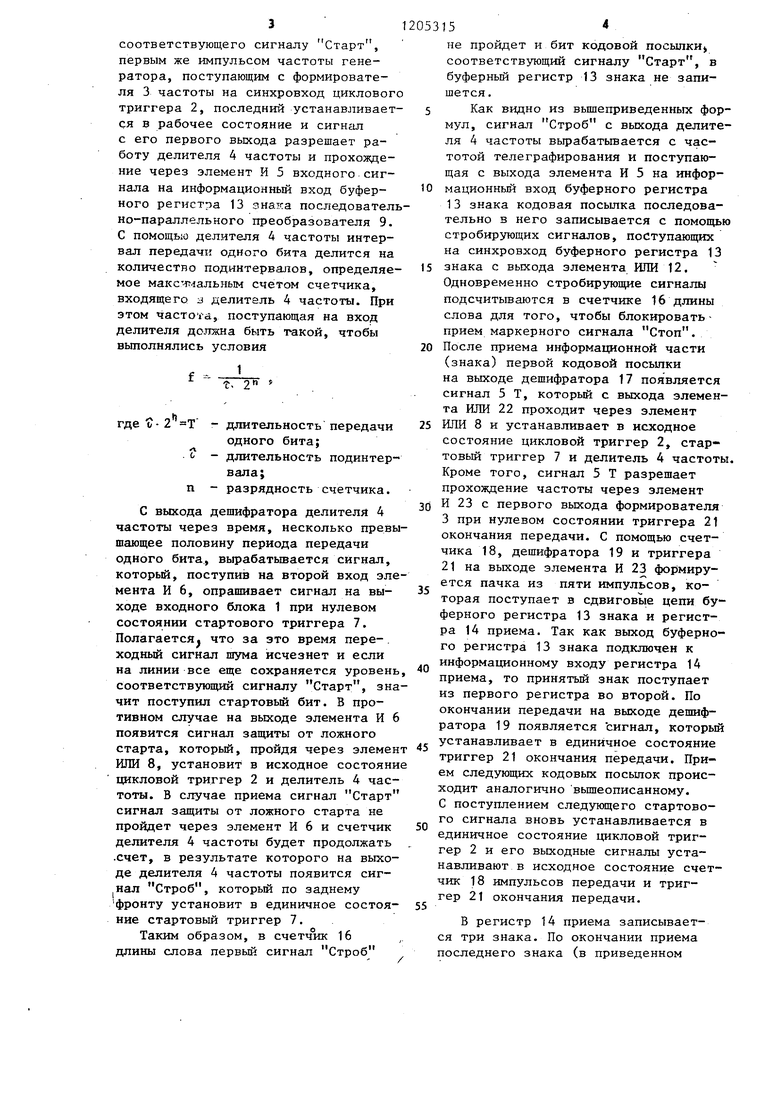

На фиг. 1 изображена структурная электрическая схема предлагаемого стартстопного приемного устройства на фиг. 2 - структурная схема последовательно-параллельного преобразовтеля .

Стартстопное приемное устройство содержит входной блок 1, цикловой триггер 2, формирователь 3 частоты, делитель 4 частоты, первый и второй элементы И 5 и 6, стартовый триггер 7, элемент ИЛИ 8, последовательно-параллельный преобразователь 9 и формирователь 10 тактов.

Последовательно-параллельный преобразователь 9 состоит из элемента И 11, элемента ИЛИ 12, буферного регистра 13 знака, регистра 14 приема, блока 15 свертки по модулю три, счетчика 16 длины слова, дешифратора 17 счетчика длинЬ слова счетчика 18 импульсов передачи, дешифратора 19 счетчика импульсов передачи, элемента И-НЕ 20 триггера 21 окончания передачи, элемента ИЛИ 22 и элемента И 23,

Стартстопное приемное устройство работает следующим образом.

15

тельно-параллельного преобразовател являются соответственно второй вход счетчика импульсов передачи, первый вход второго элемента И и второй вход счетчика длины слова, четвертым, седьмым, пятым и восьмым входами последовательно-параллельного преобразователя являются соответственно четвертый вход регистра приема, второй вход второго элемента И, второй вход триггера окончания передачи и второй вход буферного регистра знака, вторым и третьим выходами последовательно- параллельного преобразователя являются выход первого элемента ИЛИ и выход регистра приема.

Перед началом приема телеграфного сообщения цикловой триггер 2 находится в нерабочем состоянии и сигнал с его первого выхода запрещает работу делителя 4 частоты и не пропускает сигнал с выхода входного блока 1 через элемент И 5 в последовательно-параллельный преобразователь 9. Входной канал приема находится в состоянии, соответствующем уровню сигнала Стоп, и постоянно опрашивается частотой генератора, поступающей на синхровход циклового триггера. Цикл передачи каждой кодовой посьшки всегда начинается с маркерного сигнала Старт, который (в отличие от сигнала Стоп) имеет противоположный логический уровень. Хотя между передающей и приемной

стороной отсутствует синхронизация и для каждой из них имеются две отдельные последовательности тактовых импульсов, но предполагается, что эти последовательности калиброваны. В связи с этим в предлагаемом стартстопном устройстве применен метод стробирования, т.е. считывание сигнала с линии осуществляется в середине интервала времени

поступления каждого бита информации. При поступлении из входного блока 1 перехода от Стопа к Старту, т.е. при появлении на информационном входе циклового триггера 2 уровня.

3

соответствующего сигналу Старт, первым же импульсом частоты генератора, поступающим с формирователя 3 частоты на синхровход циклового триггера 2, последний устанавливает- ся в рабочее состояние и сигнал с его первого выхода разрешает работу делителя 4 частоты и прохождение через элемент И 5 входного сигнала на информационный вход буфер- ного регистра 13 знака последовательно-параллельного преобразователя 9. С помощькз делителя 4 частоты интервал передачи одного бита делится на количество подинтервалов, определяе- мое мак с -тральным счетом счетчика, входящего 3 делитель 4 частоты. При этом частота, поступающая на вход делителя должна быть такой, чтобы вьтолнялись условия

где 2 Т - длительность передачи

одного бита; t- - длительность подинтервала;п - разрядность счетчика.

С выхода дешифратора делителя 4 частоты через время, несколько превышающее половину периода передачи одного бита, вырабатьшается сигнал, которьй, поступив на второй вход элемента И 6, опрашивает сигнал на вы- ходе входного блока 1 при нулевом состоянии стартового триггера 7. Полагается, что за это время переходный сигнал шума исчезнет и если

на линии все еще сохраняется уровень.

соответствующий сигналу Старт, значит поступил стартовый бит. В противном случае на выходе элемента И 6 появится сигнал защиты от ложного старта, который, пройдя через элемент ИЛИ 8, установит в исходное состояние цикловой триггер 2 и делитель 4 частоты. В случае приема сигнал Старт сигнал защиты от ложного старта не пройдет через элемент И 6 и счетчик делителя 4 частоты будет продолжать .счет, в результате которого на выходе делителя 4 частоты появится сигнал Строб, который по заднему фронту установит в единичное состоя- ние стартовьй триггер 7.

Таким образом, в счетч ик 16 длины слова первый сигнал Строб

5 О 5 0

5

5

0

5 0 5

154

не пройдет и бит кодовой посьшкИ) соответствующий сигналу Старт, в буферный регистр 13 знака не запишется.

Как видно из вьшеприведенных формул, сигнал Строб с выхода делителя 4 частоты вьфабатывается с частотой телеграфирования и поступающая с выхода элемента И 5 на информационный вход буферного регистра 13 знака кодовая посылка последовательно в него записывается с помощью стробирующих сигналов, поступающих на синхровход буферного регистра 13 знака с выхода элемента ИЛИ 12. Одновременно стробирующие сигналы подсчитываются в счетчике 16 длины слова для того, чтобы блокировать- прием маркерного сигнала Стоп. После приема информационной части (знака) первой кодовой посыпки на выходе дешифратора 17 появляется сигнал 5 Т, который с выхода элемента ИЛИ 22 проходит через элемент ИЛИ 8 и устанавливает в исходное состояние цикловой триггер 2, стар- товьй триггер 7 и делитель 4 частоты. Кроме того, сигнал 5 Т разрешает прохождение частоты через элемент И 23 с первого выхода формирователя 3 при нулевом состоянии триггера 21 окончания передачи. С помощью счетчика 18, дешифратора 19 и триггера 21 на выходе элемента И 23 формируется пачка из пяти импульсов, которая поступает в сдвиговые цепи буферного регистра 13 знака и регистра 14 приема. Так как выход буферного регистра 13 знака подключен к информационному входу регистра 14 приема, то принятый знак поступает из первого регистра во второй. По окончании передачи на выходе депшф- ратора 19 появляется сигнал, который устанавливает в единичное состояние триггер 21 окончания передачи. Прием следующих кодовых посыпок происходит аналогично вьштеописанному. С поступлением следующего стартового сигнала вновь устанавливается в единичное состояние цикловой триггер 2 и его выходные сигналы устанавливают в исходное состояние счетчик 18 импульсов передачи и триггер 21 окончания передачи.

В регистр 14 приема записывается три знака. По окончании приема последнего знака (в приведенном

51

примере - третьего) на выходе дешифратора 17 появляется сигнал, который, пройдя через элемент И -НЕ 20 при единичном состоянии триггер 21, включает формирователь 10 тактов. Последний работает следующим образом. Когда элемент И-НЕ 20 закрыт, т.в; на его выходе присутствует потенциал, соответствующий уровню логической единицы, то формирователь 10 тактов работает в режиме параллельной записи единицы в его первый разряд. После того, как на его входе появляется сигнал, соответствукиций уровню логического нуля, он переходит в режим последовательного сдвига. Записанная в него единица начинает последовательно сдвигаться по регистру

0

5

156

на частоте генератора импульсов, формируя на его выходах серию сигналов, одним из которых записывается контрольный код с блока 15 в контрольные разряды регистра 1А приема, другим - выдается сигнал прерывания в, вычислительную машину, а следзто- щим импульсом устанавливается в исходное состояние счетчик 16 длины слова. Таким образом, устройство готово к приему следующих кодовых посьшок телеграфного сообщения.

Благодаря наличию в предлагаемом устройстве буферного регистра 13 знака совмещается по времени прием следующей кодовой посылки л передача предыдущей упакованной информации в устройство связи с вычислительной машиной.

Составитель Н. Лазарева Редактор А. Ревин Техред 3.Палий Корректор:И. Муска

Заказ 8541/59 Тираж 658 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Филиал ПИП Патент, г. Ужгород, ул. Проектная, 4

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Стартстопное приемное устройство | 1985 |

|

SU1259506A1 |

| Стартстопное приемное устройство | 1979 |

|

SU843283A2 |

| Устройство для сопряжения ЭВМ с каналом связи | 1989 |

|

SU1656546A1 |

| Система передачи дискретной информации | 1987 |

|

SU1518886A1 |

| Многоканальное приемное устройство стартстопных телеграфных сигналов | 1984 |

|

SU1264367A1 |

| Система передачи дискретной информации с решающей обратной связью | 1983 |

|

SU1111258A1 |

| УСТРОЙСТВО ТЕЛЕМЕХАНИКИ | 1995 |

|

RU2111546C1 |

| Приемное устройство дополнительной цифровой информации, передаваемой в составе кадрового гасящего импульса полного телевизионного сигнала | 1988 |

|

SU1653179A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

| Устройство для настройки стартстопного приемника на скорость передачи | 1976 |

|

SU620026A1 |

| Стартстопное приемное устройство | 1979 |

|

SU843283A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-01-15—Публикация

1984-01-26—Подача