1

Изобретение -относится к автоматическому управлению и вычислительной технике и может быть использовано при построении систем автоматического управления и регулирования, например, для управления малогабаритным компасом.

Цель изобретения - повышений точности системы автоматического управления.

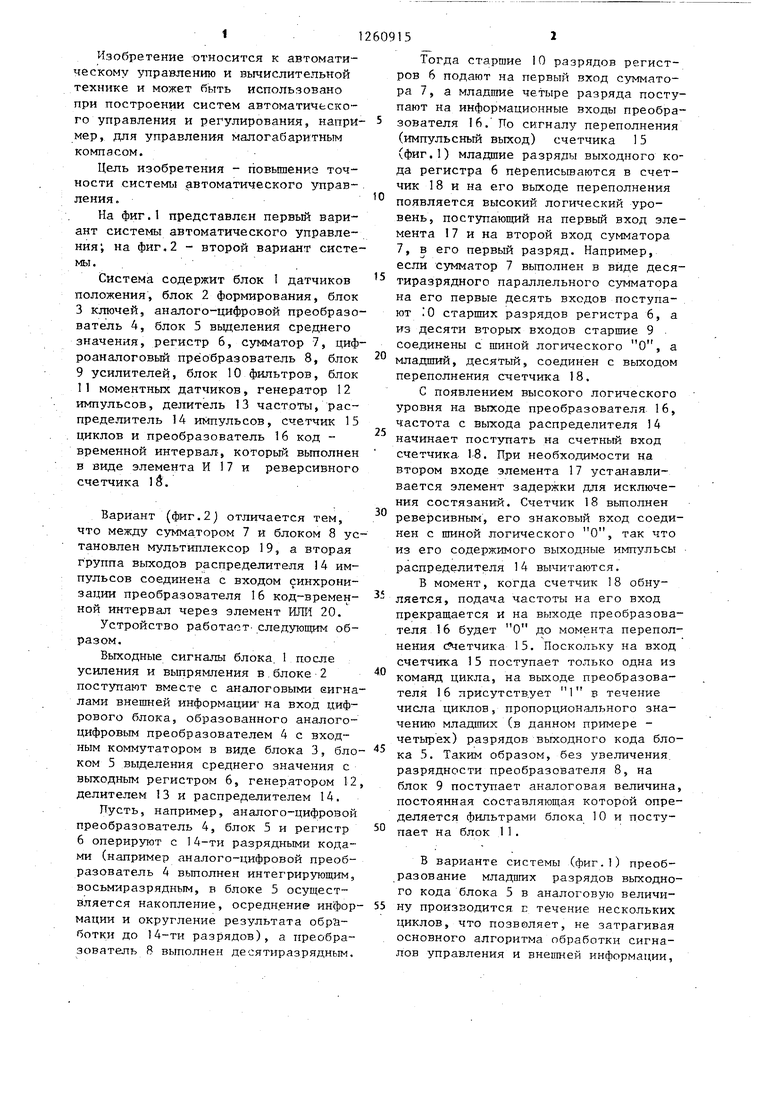

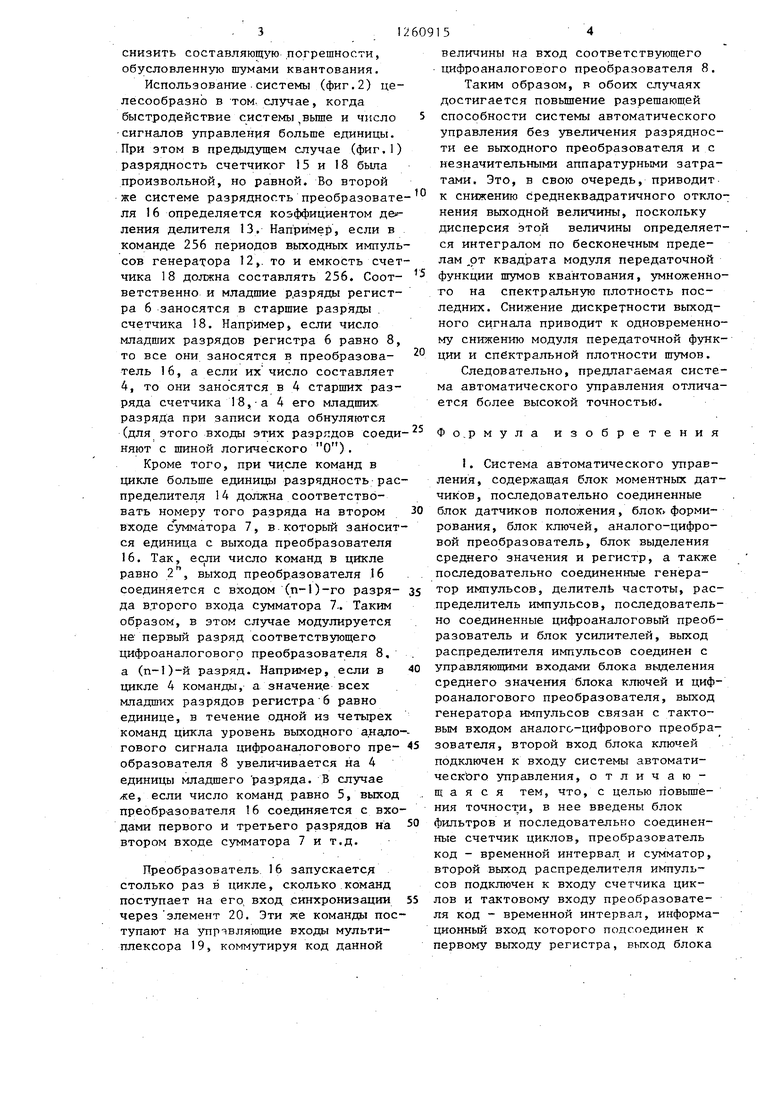

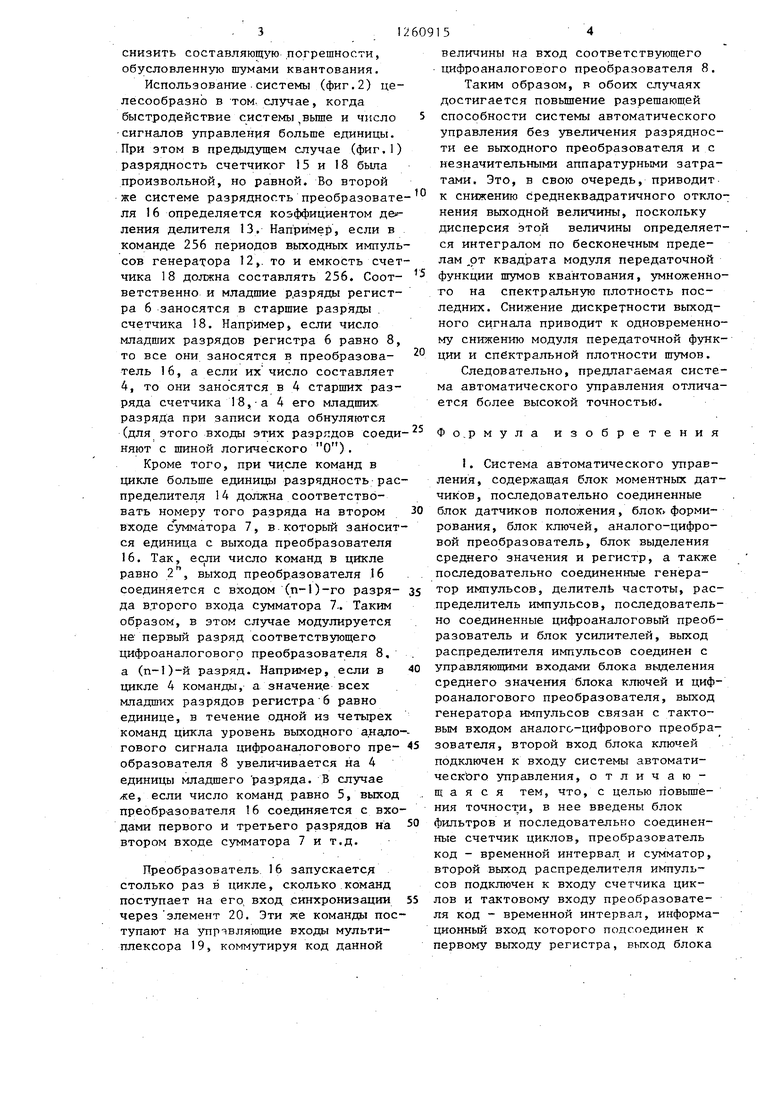

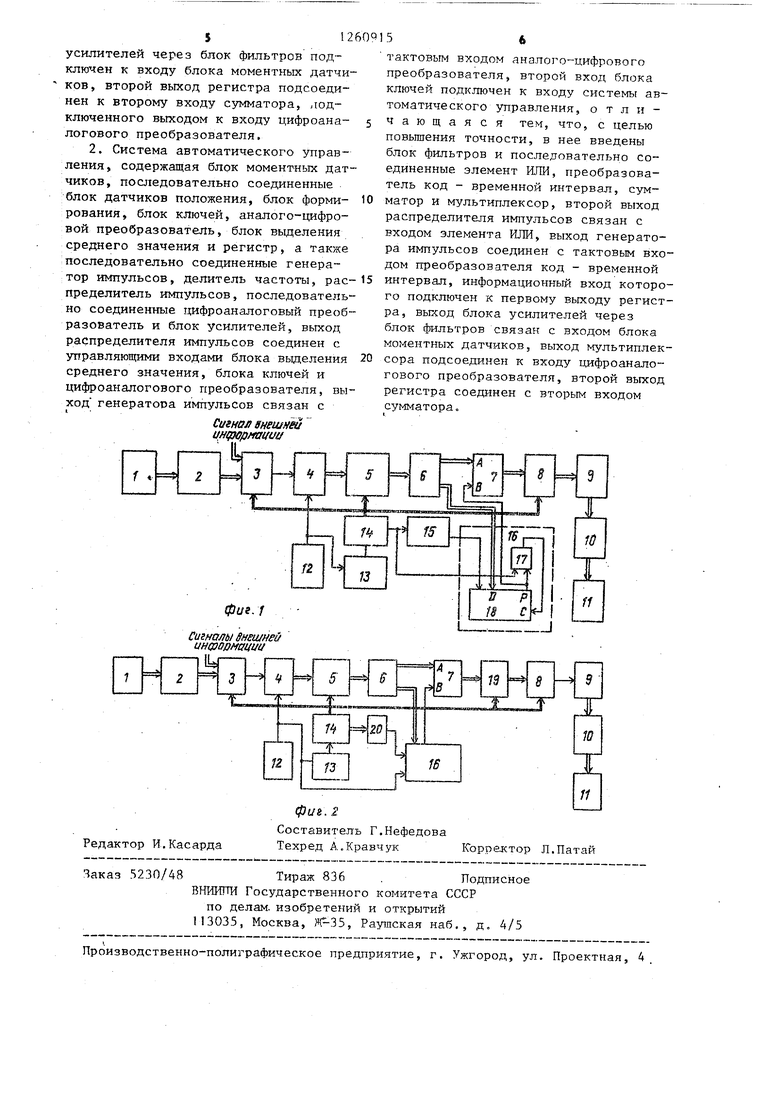

На фиг.1 представлен первый вариант системы автоматического управления; на фиг.2 - второй вариант системы. .

Система содержит блок 1 датчиков положения, блок 2 формирования, блок 3 ключей, аналого-цифровой преобразователь 4, блок 5 выделения среднего значения, регистр 6, сумматор 7, циф роаналоговый преобразователь 8, блок 9 усилителей, блок 10 фильтров, блок 11 моментных датчиков, генератор 12 импульсов, делитель 13 частоты, распределитель 14 импульсов, счетчик 15 циклов и преобразователь 16 код - временной интервал, который вьтолнен в виде элемента И 17 и реверсивного счетчика 1Й.

Вариант (фиг.2) отличается тем, что между сумматором 7 и блоком 8 установлен мультиплексор 19, а вторая группа выходов распределителя 4 импульсов соединена с входом синхронизации преобразователя 16 код-временной интервал через элемент ИЛИ 20.

Устройство работает- следующим образом.

Выходные сигналы блока. 1 после усипения и выпрямления в. блоке 2 поступают вместе с аналоговыми еигна лами внешней информации на вход цифрового блока, образованного аналого- цифровым преобразователем 4 с входВ момент, когда счетчик 18 обнуляется, подача частоты на его вход прекращается и на врлходе преобразова теля 16 будет О до момента перепол нения с четчика 15. Поскольку на вход счетчика 15 поступает только одна и команд цикла, на выходе преобразователя 16 присутствует 1 в течение числа циклов, пропорционального зна чению младших (в данном примере - четырех) разрядов выходного кода бл

ным коммутатором в виде блока 3, бло- з. Таким образом, без увеличения

ком 5 выделения среднего значения с выходным регистром 6, генератором 12, делителем 13 и распределителем 14.

Пусть, например, аналого-цифровой преобразователь 4, блок 5 и регистр 6 оперируют с 14-ти разрядными кодами (например аналого-цифровой преобразователь 4 вьтолнен интегрир-ующ1-1М5 восьмиразрядным, в блоке 5 осуществляется накопление, осреднение информации и округление результата обрй- ботки до 14-ти разрядов), а преобразователь 8 выполнен десятиразрядным.

разрядности преобразователя 8, на блок 9 поступает аналоговая величин постоянная составляющая которой опр деляется фильтрами блока 10 и посту пает на блок 11.

В варианте системы (фиг.1) преоб разование младших разрядов выходн го кода блока 5 в аналоговую величи 55 ну производится п течение нескольки циклов, что позвеляет, не затрагива основного алгоритма обработки сигна лов управления и внешней информации

0

5

20

25

30

3

40

Тогда старшие 10 разрядов регистров 6 подают на первый вход с-уммато- ра 7, а младшие четыре разряда поступают на информационные входы преобразователя 16. По сигналу переполнения (импульсный выход) счетчика 15 (фиг.1) младшие разряды выходного кода регистра 6 переписьгоаготся в счетчик 18 и на его выходе переполнения появляется высокий логический уровень, поступающий на первый вход элемента 17 и на второй вход сумматора 7, в его первый разряд. Например, если сумматор 7 вьтолнен в виде десятиразрядного параллельного сумматора на его первые десять входов поступают ;0 старших разрядов регистра 6, а из десяти вторых входов старшие 9 соединены с шиной логического О, а младший, десятый, соединен с вьпсодом переполнения счетчика 18.

С появлением высокого логического уровня на выходе преобразователя 16, частота с выхода распределителя 14 начинает пост-упать на счетный вход счетчика 18. При необходимости на втором входе элемента 17 устанавливается элемент задержки для исключения состязаний. Счетчик 18 вьтолнен реверсивным, его знаковый вход соединен с шиной логического О, так что из его содержимого выходные импульсы - распределителя 14 вычитаются.

В момент, когда счетчик 18 обнуляется, подача частоты на его вход прекращается и на врлходе преобразователя 16 будет О до момента переполнения с четчика 15. Поскольку на вход счетчика 15 поступает только одна из команд цикла, на выходе преобразователя 16 присутствует 1 в течение числа циклов, пропорционального значению младших (в данном примере - четырех) разрядов выходного кода бло з. Таким образом, без увеличения

разрядности преобразователя 8, на блок 9 поступает аналоговая величина, постоянная составляющая которой определяется фильтрами блока 10 и посту- пает на блок 11.

В варианте системы (фиг.1) преобразование младших разрядов выходного кода блока 5 в аналоговую величи- ну производится п течение нескольких циклов, что позвеляет, не затрагивая основного алгоритма обработки сигналов управления и внешней информации,

снизить составляющую погрешности, обусловленную шумами квантования.

Использование.системы (фиг.2) целесообразно в том. случае, когда быстродействие системы ,вьппе и число сигналов управления больше единицы. При этом в предыдущем случае (фиг,1) разрядность счетчиког 15 и I8 бьша произвольной, но равной. Во второй же системе разрядность преобразователя 6 определяется коэффициентом ления делителя 13, Например, если в команде 256 периодов выходных импульсов генератора 12,. то и емкость счетчика 18 должна составлять 256. Соот- ветственно и младшие разряды регистра 6 заносятся в старшие разряды счетчика 18. Например, если число младших разрядов регистра 6 равно 8, то все они заносятся в преобразова- тель 16, а если их число составляет 4, то они заносятся в 4 старших разряда счетчика 18,а 4 его младших разряда при записи кода обнуляются (для этого входы этих разрггдов соеди няют с шиной логического О).

Кроме того, при числе команд в цикле больше единицы разрядность распределителя 14 должна соответствовать номеру того разряда на втором входе сумматора 7, в.который заносится единица с выхода преобразователя 16. Так, если число команд в цикле равно 2, выход преобразователя 16 соединяется с входом (п-1)-го разря- да второго входа сумматора 7.. Таким образом, в этом случае модулируется не первый разряд соответствующего цифроаналоговогр преобразователя 8, а (п-1)-й разряд. Например, если в цикле 4 команды, а значение всех младших разрядов регистра 6 равно единице, в течение одной из четьфех команд цикла уровень выходного анало гового сигнала цифроаналогового пре- образователя 8 увеличивается на 4 единицы младшего разряда. В случае же, если число команд равно 5, вьпсод преобр-азователя 16 соединяется с входами первого и третьего разрядов на втором входе сумматора 7 и т.д.

Преобразователь 16 запускаете столько раз в цикле, сколько команд поступает на его, вход, синхронизации через элемент 20. Эти же команды поступают на управляющие входы мультиплексора 19, коммутируя код данной

величины на вход соответствующего цифроаналогового преобразователя 8.

Таким образом, в обоих случаях достигается повьшгение разрешающей способности системы автоматического управления без увеличения разрядности ее выходного преобразователя и с незначительными аппаратурными затратами. Это, в свою очередь, приводит к снижению среднеквадратичного отклонения выходной величины, поскольку дисперсия этой величины определяется интегралом по бесконечным пределам ,от квадрата модуля передаточной функции шумов квантования, умноженного на спектральную плотность последних. Снижение дискретности выходного сигнала приводит к одновременному снижению модуля передаточной функции и спектральной плотности шумов.

Следовательно, предлагаемая система автоматического управления отличается более высокой точностью.

Ф о,р мула изобретения

I. Система автоматического управления, содержащая блок моментных датчиков, последовательно соединенные блок датчиков положения, блок формирования, блок ключей, аналого-цифровой преобразователь, блок выделения среднего значения и регистр, а также последовательно соединенные генератор импульсов, делитель частоты, распределитель импульсов, последовательно соединенные цифроаналоговый преобразователь и блок усилителей, выход распределителя импульсов соединен с управляющими входами блока выделения среднего значения блока ключей и цифроаналогового преобразователя, выход генератора импульсов связан с тактовым входом аналого-цифрового преобразователя, второй вход блока ключей подключен к входу системы автоматического управления, отличающаяся тем, что, с целью повьшхе- ния точностей, в нее введены блок фильтров и последовательно соединенные счетчик циклов, преобразователь код - временной интервал и сумматор, второй выход распределителя импульсов подключен к входу счетчика циклов и тактовому входу преобразователя код - временной интервал, информационный вход которого подсоединен к первому выходу регистра, выход блока

512

усилителей через блок фильтров подключен к входу блока моментных датчиков , второй выход регистра подсоединен к второму входу сумматора, лод- ключенного выходом к входу цифроана- логового преобразователя,

2. Система автоматического управления, содержащая блок моментных датчиков, последовательно соединенные блок датчиков положения, блок форми- рования, блок ключей, аналого-цифровой преобразователь, блок выделения среднего значения и регистр, а также последовательно соединенные генератор импульсов, делитель частоты, распределитель импульсов, последовательно соединенные цифроаналоговый преобразователь и блок усилителей, выход распределителя импульсов соединен с управляющими входами блока вьщеления среднего значения, блока ключей и цифроаналогового преобразователя, выход генератора импульсов связан с

Сигнал ffHeufffM UHipopmiwu

Сигналы внешней uHcpBOHawtt

Редактор И.Касарда

фа. I Составитель Г.Нефедова Техред А.Кравчук Корректор Л.Патай

Заказ 5230/48Тираж 836 . Подписное

ВНИИПИ Государственного комитета СССР

по делам, изобретений и открытий 113035, Москва, , Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4.

56

тактовым входом аналого-цифрового преобразователя, второй вход блока ключей подключен к входу системы автоматического зтравления, отличающаяся тем, что, с целью повьшения точности, в нее введены блок фильтров и последовательно соединенные элемент И.ПИ, преобразователь код - временной интервал, сумматор и мультиплексор, второй выход распределителя импульсов связан с входом элемента ИЛИ, выход генератора импульсов соединен с тактовым входом преобразователя код - временной интервал, информационный вход которого подключен к первому выходу регистра, выход блока усилителей через блок фильтров связан с входом блока моментных датчиков, выход мультиплексора подсоединен к входу цифроаналогового преобразователя, второй выход регистра соединен с вторым входом сумматорас

| название | год | авторы | номер документа |

|---|---|---|---|

| Регулятор | 1984 |

|

SU1260913A1 |

| Цифровой измеритель сопротивления | 1977 |

|

SU737867A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1378061A1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Многоканальная электроразведочная станция | 1980 |

|

SU934414A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| Устройство для преобразования координат | 1980 |

|

SU898426A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Устройство для воспроизведения периодических сигналов | 1983 |

|

SU1130881A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1251326A1 |

Изобретение относится к автоматическому управлению и вычислительной технике и может быть использовано для з равления положением подвижных объектов. Цель изобретения - по- вышение точности управления за счет повьшения запаса устойчивости и снижения составляющей погрепгаости, обусловленной шумами квантования. Поставленная цель достигается тем, что за счет изменения разрешающей способности цифроаналогового преобразователя изменено соотношение разрешающих способностей аналого-цифрового и цифро- аналогового преобразователей, что приводит к повьш1ению точности коррекции, осуществляемой по каналу управления системы. 2 с. п.ф-лы, 2 ил. о S

| Гироскопические системы | |||

| Под ред | |||

| Полонора Д.С | |||

| ч | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| М.: Высшая школа, 1977, с | |||

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-09-30—Публикация

1985-05-17—Подача