Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования.аналоговых величин в цифровые,

Цель изобретения - повышение точности преобразования-.

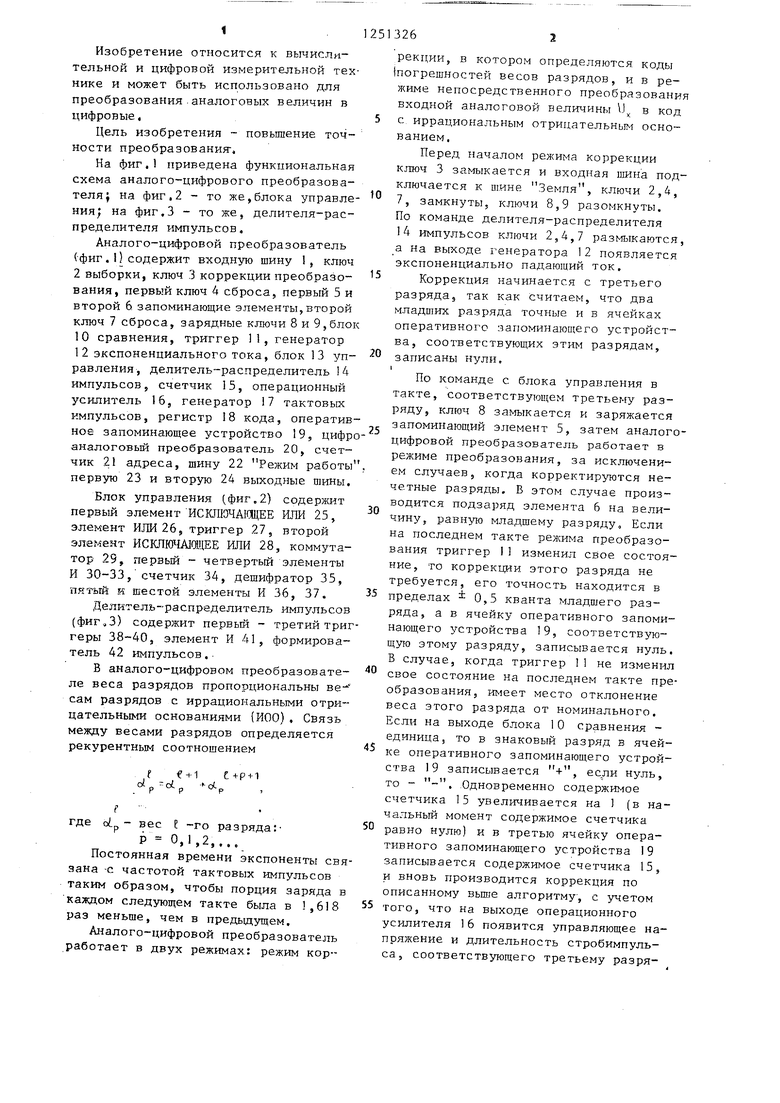

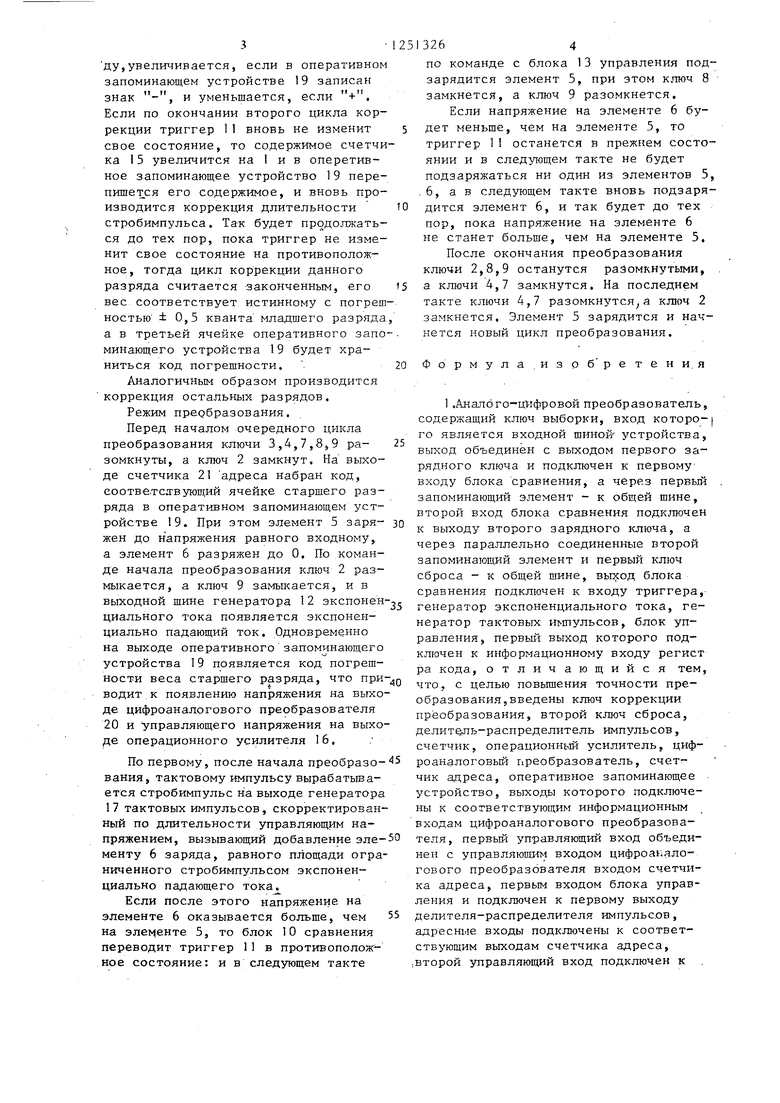

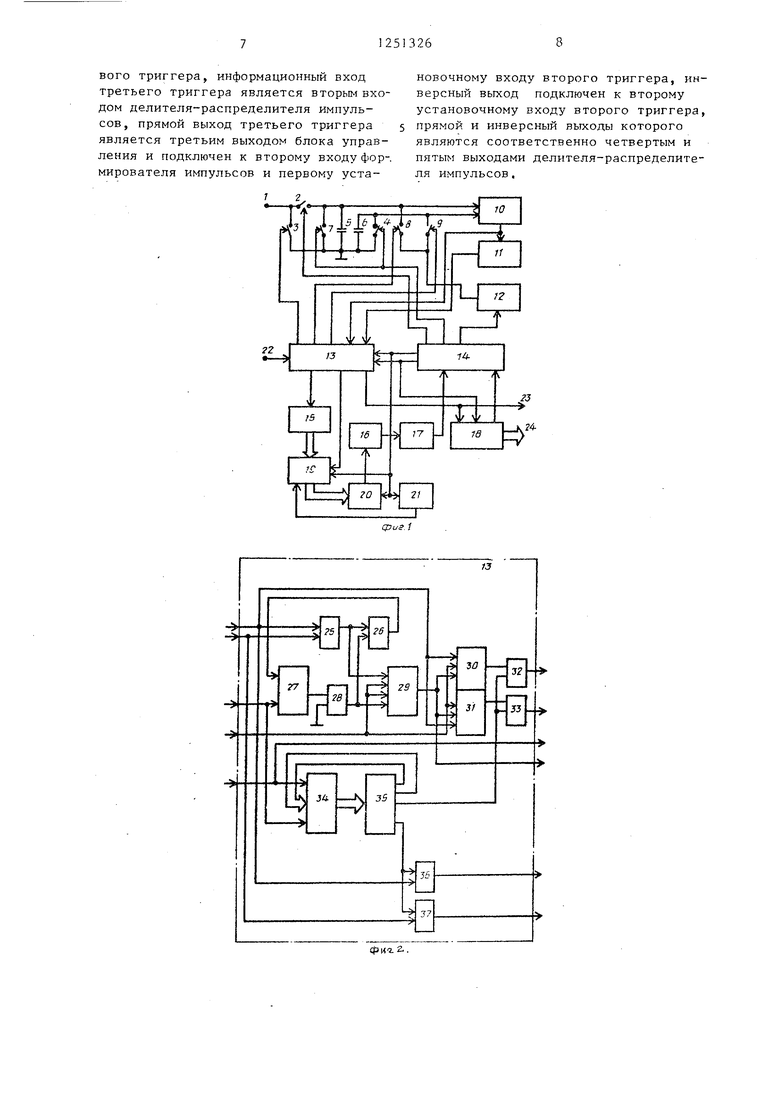

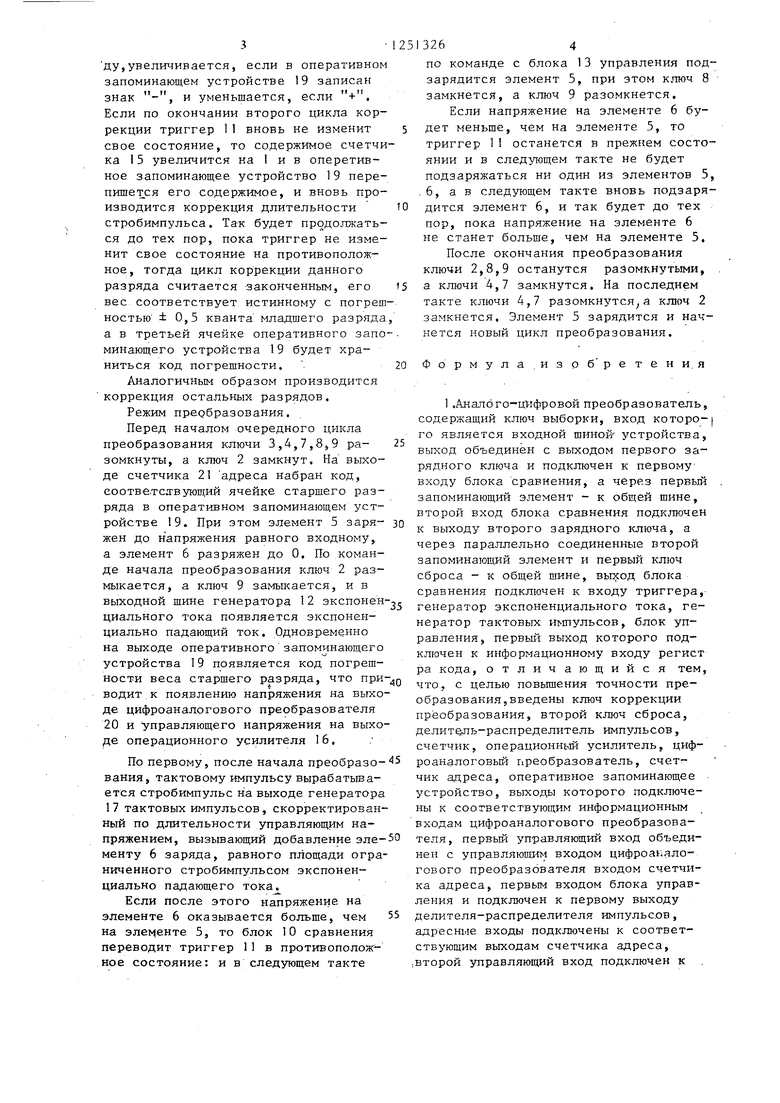

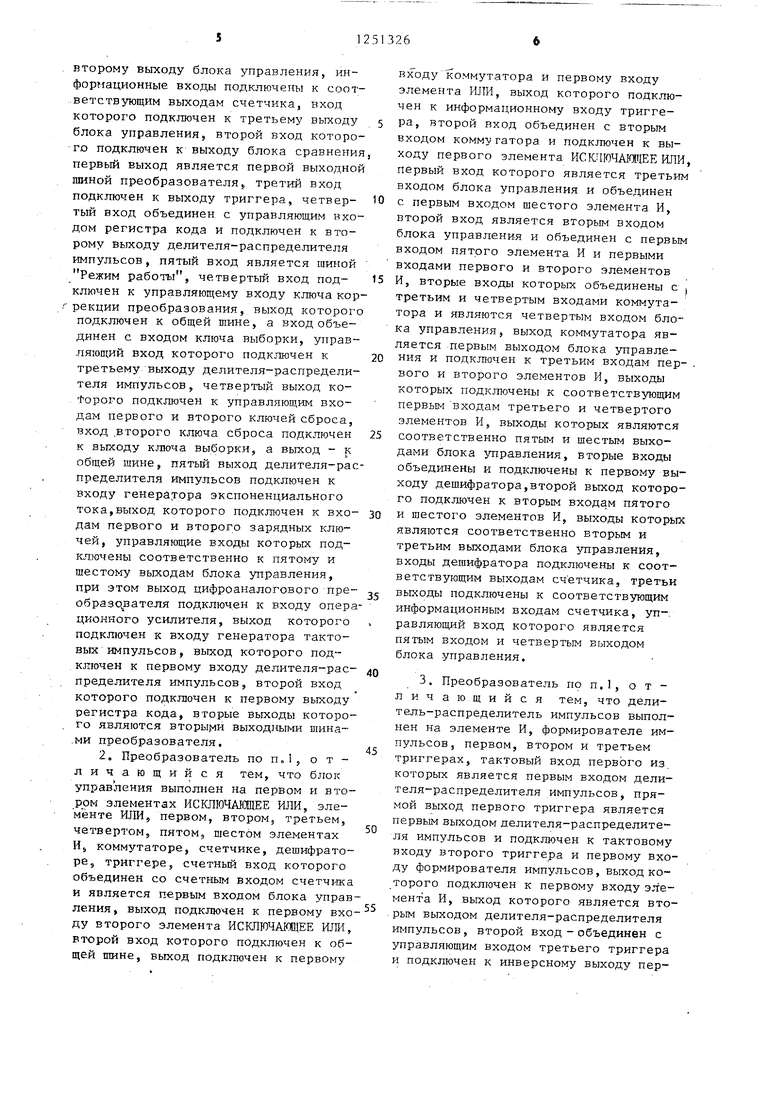

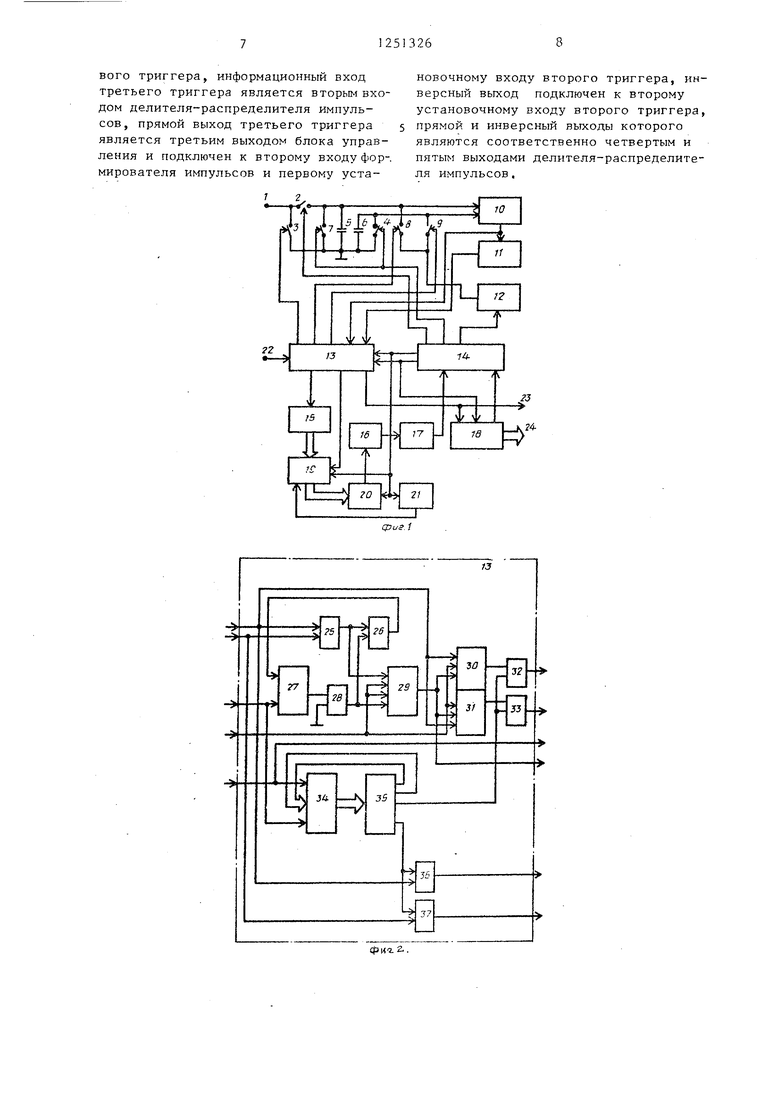

На фиг.1 приведена функциональная схема аналого-цифрового преобразователя; на фиг,2 - то же,блока управления; на фиг.З - то же, делителя-распределителя импульсов.

Аналого-цифровой преобразователь (-фиг. I) содержит входную шину 1, ключ 2 выборки, ключ 3 коррекции преобразования, первый ключ 4 сброса, первый 5 и второй 6 запоминающие элементы, второй ключ 7 сброса, зарядные ключи 8 и 9,блок 10 сравнения, триггер 1 1 , генератор 12 экспоненциального тока, блок 13 управления, делитель-распределитель 14 импульсов, счетчик 15, операционный усилитель 16, генератор 7 тактовых импульсов, регистр 18 кода, оперативное запоминающее устройство 19, цифр аналоговьй преобразователь 20, счетчик 21 адреса, шину 22 Режим работы первую 23 и вторую 24 выходные шины.

Блок управления (фиг,2) содержит первый элемент ИСКПЮЧАЩЕЕ ИЛИ 25, элемент ИЛИ 26, триггер 27, второй элемент ИСКЛЮЧАИЦЕЕ ИЛИ 28, коммутатор 29, первый - четвертый элементы И 30-33, счетчик 34, дешифратор 35, пятый к шестой элементы И 36, 37.

Делитель-распределитель импульсов () содержит первый - третий тригеры 38-40, элемент И 41, формирователь 42 импульсов..

В аналого-цифровом преобразователе веса разрядов пропорциональны ве- сам разрядов с иррациональными отрицательными основаниями (ИОО), Связь между весами разрядов определяется рекурентным соотношением

f f + 1 е+р-и ., где - вес Е -го разряда:Р 0,1,2,...

Постоянная времени экспоненты связана -с частотой тактовых импульсов таким образом, чтобы порция заряда в каждом следующем такте была в , раз меньше, чем в предыдущем.

Аналого-цифровой преобразователь работает в двух режимах: режим кор-

5

0

5

0

5

0

5

0

55

рекции, в котором определяются коды 1погрешностей весов разрядов, и в режиме непосредственного преобразования входной аналоговой величины J в код с иррациональным отрицательньтм основанием.

Перед началом режима коррекции ключ 3 замыкается и входная шина подключается к шине Земля, ключи 2,4, 7, замкнуты, ключи 8,9 разомкнуты. По команде делителя-распределителя 14 импульсов ключи 2,4,7 размыкаются, а на выходе генератора 12 появляется экспоненциально падающий ток.

Коррекция начинается с третьего разряда, так как считаем, что два младп1их разряда точные и в ячейках оперативного запоминающего устройства, соответствующих этим разрядам, записаны нули.

По команде с блока управления в такте, соответствующем третьему разряду, ключ 8 замыкается и заряжается запоминающий элемент 5, затем аналого- цифровой преобразователь работает в режиме преобразования, за исключением случаев, когда корректир- тотся нечетные разряды. В этом случае производится -подзаряд элемента 6 на величину, равную младшему разряду. Если на последнем такте релотма преобразования триггер I1 изменил свое состояние, то коррекции этого разряда не требуется, его точность находится в пределах 0,5 кванта младшего разряда, а в ячейку оперативного запоминающего устройства 19, соответствующую этому разряду, записывается нуль. В случае, когда триггер 11 не изменил свое состояние на последнем такте преобразования, имеет место отклонение веса этого разряда от номинального. Если на выходе блока 10 сравнения - единица, то в знаковый разряд в ячейке оперативного запоминающего устройства 19 записывается +, если нуль, то - -. .Одновременно содержимое счетчика 15 увеличивается на 1 (в начальный момент содержимое счетчика равно нулю) и в третью ячейку оперативного запоминающего устройства 19 записывается содержимое счетчика 15, и вновь производится коррекция по описанному вьш1е алгоритму-, с учетом того, что на выходе операционного усилителя 16 появится управляющее напряжение и длительность стробимпуль- са, соответствующего третьему разря

ду,увеличивается, если в оперативном запоминающем устройстве 19 записан знак -, и уменьшается, если +. Если по окончании второго цикла коррекции триггер 11 вновь не изменит свое состояние, то содержимое счетчика 15 увеличится на I и в оперетив- ное запоминающее устройство 19 перепишется его содержимое, и вновь производится коррекция длительности стробимпульса. Так будет продолжаться до тех пор, пока триггер не изменит свое состояние на противоположное, тогда цикл коррекции данного разряда считается законченным, его вес соответствует истинному с погрешностью ±0,5 кванта младшего разряда а в третьей ячейке оперативного запо минающего устройства 19 будет храниться код погрешности.

Аналогичным образом производится коррекция остальных разрядов.

Режим преобразования.

Перед началом очередного цикла преобразования ключи 3,4,7,8,9 разомкнуты, а ключ 2 замкнут. На выходе счетчика 21 адреса набран код, еоответсд-вующий ячейке старшего разряда в оперативном запоминающем устройстве 19. При этом элемент 5 заряжен до напряжения равного входному, а элемент 6 разряжен до 0. По команде начала преобразования ключ 2 размыкается, а ключ 9 замыкается, и в вьпсодной шине генератора 12 экспонен циального тока появляется экспоненциально падающий ток. Одновременно на выходе оперативного запоминающего устройства 19 появляется код погрешности веса старшего разряда, что при водит к появлению напряжения на выходе цифроаналогового преобразователя 20 и управляющего напряжения на выходе операционного усилителя 16.

По первому, после начала преобразования, тактовому импульсу вырабатывается стробимпульс в:а выходе генератора 17 тактовых импульсов, скорректированный по длительности управляющим напряжением, вызывающий добавление элементу 6 заряда, равного площади ограниченного стробимпульсом экспоненциально падающего тока.

Если после этого напряжение на элементе 6 оказывается больше, чем на элеиенте 5, то блок 10 сравнения переводит триггер 11 в противоположное состояние: и в следующем такте

13264

по команде с блока 13 управления подзарядится элемент 5, при этом ключ 8 замкнется, а ключ 9 разомкнется.

Если напряжение на элементе 6 бу- дет меньше, чем на элементе 5, то

триггер I I останется в состоянии и в следующем такте не будет подзаряжаться ни один из элементов 5, .6, а в следующем такте вновь подзарядится элемент 6, и так будет до тех пор, пока напряжение на элементе 6 не станет больше, чем на элементе 5.

После окончания преобразования ключи 2,8,9 останутся разомкнутыми, а ключи 4,7 замкнутся. На последнем такте ключи 4,7 разомкнутся а ключ 2 замкнется. Элемент 5 зарядится и начнется новый цикл преобразования.

.

20 Формула изо б ре тени.я

1 .Аналого-цифровой преобразователь, содержащий ключ выборки, вход которо-j го является входной шиной устройства, выход объединен с выходом первого зарядного ключа и подключен к первому

входу блока сравнения, а через первый запоминающий элемент - к общей шине, второй вход блока сравнения подключен к выходу второго зарядного ютюча, а через параллельно соединенные второй запоминающий элемент и первый ключ сброса - к общей шине, выход блока сравнения подключен к входу триггера,- генератор экспоненциального тока, генератор тактовых иьтульсов, блок управления, первьш выход которого подключен к информационному входу регист ра кода, отличающийся тем, что, с целью повьшзения точности преобразования, введены ключ коррекции преобразования, второй ключ сброса, делитель-распределитель импульсов, счетчик, операционньш усилитель, циф- роаналоговый гфеобразователь, счетчик адреса, оперативное запоминающее устройство, выходы которого подключены к соответствующим информационным входам цифроаналогового преобразователя , первый управляющий вход объединен с управляющим входом цифроа1;ало- гового преобразователя входом счетчика адреса, первым входом блока управления и подключен к первому выходу делителя-распределителя импульсов, адресные входы подключены к соответствующим выходам счетчика адреса, .второй управляющий вход подключен к

торому выходу блока управления, инормационные входы подключены к соот- етствзпощим выходам счетчика, вход оторого подключен к третьему выходу 5 лока управления, второй вход которо- го подключен к выходу блока сравнения, ервый выход является первой выходной иной преобразователя, третий вход подключен к выходу триггера, четвер- Ю тый вход объединен с управляющим входом регистра кода и подключен к второму выходу делителя-распределителя импульсов, пятый вход является шиной Режим работы, четвертый вход под- 15 ключен к управляющему входу ключа кор- рекдии преобразования, выход которого подключен к общей щине, а вход объединен с входом ключа выборки, управ- ляюпщй вход которого подключен к 20 третьему выходу делителя-распределителя импульсов четвертый выход ко- toporo подключен к управляющим входам первого и второго ключей сброса, вход .второго ключа сброса подключен 25 к выходу ключа выборки, а выход - к общей шине, пятый выход делителя-распределителя импульсов подключен к входу генератора экспоненциального тока,выход которого подключен к вхо- зо дам первого и второго зарядных ключей, управляющие входы которых подключены соответственно к пятому и шестому выходам блока управления, при этом выход цифроаналогового пре- 5 образо вателя подключен к входу опера- цконного усилителя, выход которого подключен к входу генератора тактовых импульсов , выход которого под- .кяючен к первому входу делителя-рас- 40 пределителя импульсов, второй вход которого подключен к первому выходу регистра кода, вторые выходы которого являются вторы;у1И выходными шина- ,ми преобразователя.

2. Преобразователь по п.1 , отличающийся тем, что блок управления выполнен на первом и втором элементах ИСКЛЮЧАШЕЕ ИЛИ, элементе ИЛИ, первом, втором, третьем, четвертом, пятом, шестом элементах Us коммутаторе, счетчике, дешифраторе, триггере, счетный вход которого объединен со счетным входом счетчика и является первым входом блока управления, выход подключен к первому входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к общей шине, выход подключен к пepвo fy

50

55

5 0 5 о 5 0

0

5

входу коммутатора и первому входу элемента ИЛИ, выход которого подключен к информационному входу триггера, второй вход объединен с вторьпм входом комму гатора и подключен к выходу первого элемента ИСКЧЮЧМСЩЕЕ ИЛИ, первый вход которого является третьим входом блока управления и объединен с первым входом шестого элемента И, второй вход является вторым входом блока управления и объединен с первым входом пятого элемента И и первыми входами первого и второго элементов И, вторые входы которых объединены с , третьим и четвертым входами коммутатора и являются четвертым входом блока управления, выход коммутатора является первым выходом блока управления и подключен к третьим входам первого и второго элементов И, выходы которых подключены к соответствующим первым входам третьего и четвертого элементов И, выходы которых являются соответственно пятым и шестым выходами блока управления, вторые входы объединены и подключены к первому выходу дешифратора,второй выход которого подключен к вторым входам пятого и шестого элементов И, выходы которых являются соответственно вторым и третьим выходами блока управления, входы дешифратора подключены к соответствующим выходам счетчика, третьи выходы подключены к соответствующим информационным входам счетчика, уп-: равляющнй вход которого является пятым входом и четвертым выходом блока управления,

3. Преобразователь по п,1, отличающийся тем, что делитель-распределитель импульсов выполнен на элементе И, формирователе импульсов, первом, втором и третьем триггерах, тактовый вход первого из. которых является первым входом делителя-распределителя импульсов, прямой выход первого триггера является первым выходом делителя-распределителя импульсов и подключен к тактовому входу второго триггера и первому входу формирователя импульсов, выход которого подключен к первому входу элемента И, выход которого является вторым выходом делителя-распределителя импульсов, второй вход - объединен с управляющим входом третьего триггера и подключен к инверсному выходу первого триггера, информационный вход третьего триггера является вторым входом делителя-распределителя импульсов, прямой выход третьего триггера является третьим выходом блока управления и подключен к второму входу формирователя импульсов и первому установочному входу второго триггера, инверсный выход подключен к второму установочному входу второго триггера, прямой и инверсный выходы которого являются соответственно четвертым и пятым выходами делителя-распределителя импульсов,

38

Редактор Н.Слабодяник

Составитель В.Першиков

Техред Л.Сердюкова Корректор Е. Рошко

Заказ 4426/58Тираж Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная,4

39

LJфиё.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1985 |

|

SU1297224A1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| ЧАСТОТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ ЕРМАКОВА-ФЕДОРОВА (ВАРИАНТЫ) | 2007 |

|

RU2362175C2 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| Цифровой регистратор | 1984 |

|

SU1164549A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Синхронный фильтр | 1988 |

|

SU1644366A1 |

| Устройство для считывания графической информации | 1981 |

|

SU964674A1 |

| Устройство для зарядки емкостного накопителя | 1989 |

|

SU1780150A1 |

Изобретение позволяет повысить точность аналого-цифрового преобразования за счет введения дополнительного режима самокоррекции. Возможность эффективной самокоррекции обеспечивается тем, что веса разрядов аналого-цифрового преобразователя пропорциональны весам разрядов с иррациональными отрицательньГми основаниями. В режиме коррекции определяются коды погрешностей весов разрядов, которые записываются в оперативное запоминающее устройства. Перед началом режима коррекции ключ коррекции преобразования замыкается, ключ выборки и два ключа сброса замкнуты, а зарядные ключи разомкнуты. По команде делителя-распределителя импульсов KJnb4 выборки и два ключа сброса размыкаются, а на выходе генератора появляется экспоненцильный ток, который по команде блока управления через первый зарядньга ключ в течение определенного времени поступает на вход запоминающего элемента, затем аналого-цифровой преобразователь работает в режиме преобразования, за исключением случаев, когда корректируются нечетные разряды. В этом случае производится подзаряд запоминающего элемен-. та на величину, равную весу младшего разряда, если в конце последнего такта преобразования блок сравнения и триггер изменят свое состояние, то коррекции данного разряда не требуется и в соответствующую ячейку оперативного запоминающего устройства записывается О, в противном случае обеспечивается определение- и запись в соответствующую ячейку оперативного запоминающего устройства кода погрешности соответствующего разряда, который затем используется в режиме преобразования для соответствующего изменения длительности тактовых импульсов на выходе генератора. Результат преобразования в виде параллельного код а снимается по первьм выходным шинам, а в виде последовательного кода j- по i вторым выходньм шинам. Сигнал на вход- ной шине определяет режим работы преобразователя. 2 з.п. ф-лы, 3 ил. С sэ ел ОР ю О5

| Аналого-цифровой преобразователь | 1980 |

|

SU911720A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU799130A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-08-15—Публикация

1984-11-06—Подача