1

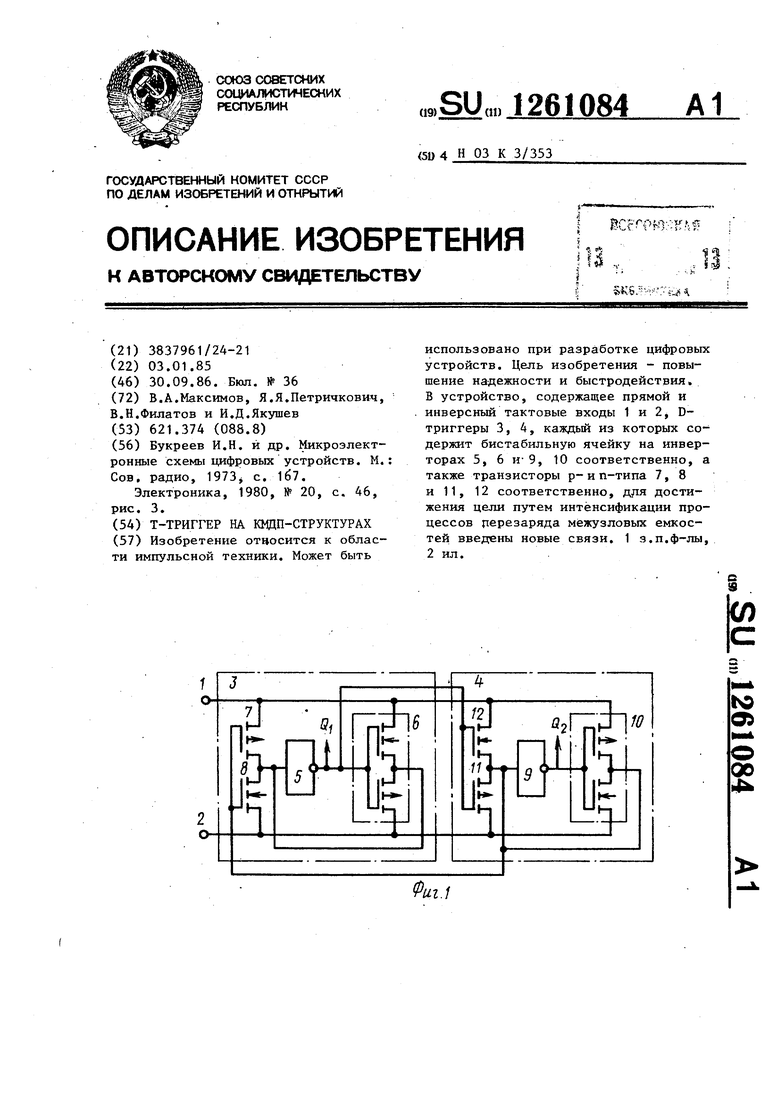

Изобретение относится к импульсной технике и может быть использовано при разработке различных цифровых устройств.

Цель изобретения - повьшение надежности и быстродействия путем интенсификации процессов перезаряда . межузловых емкостей.

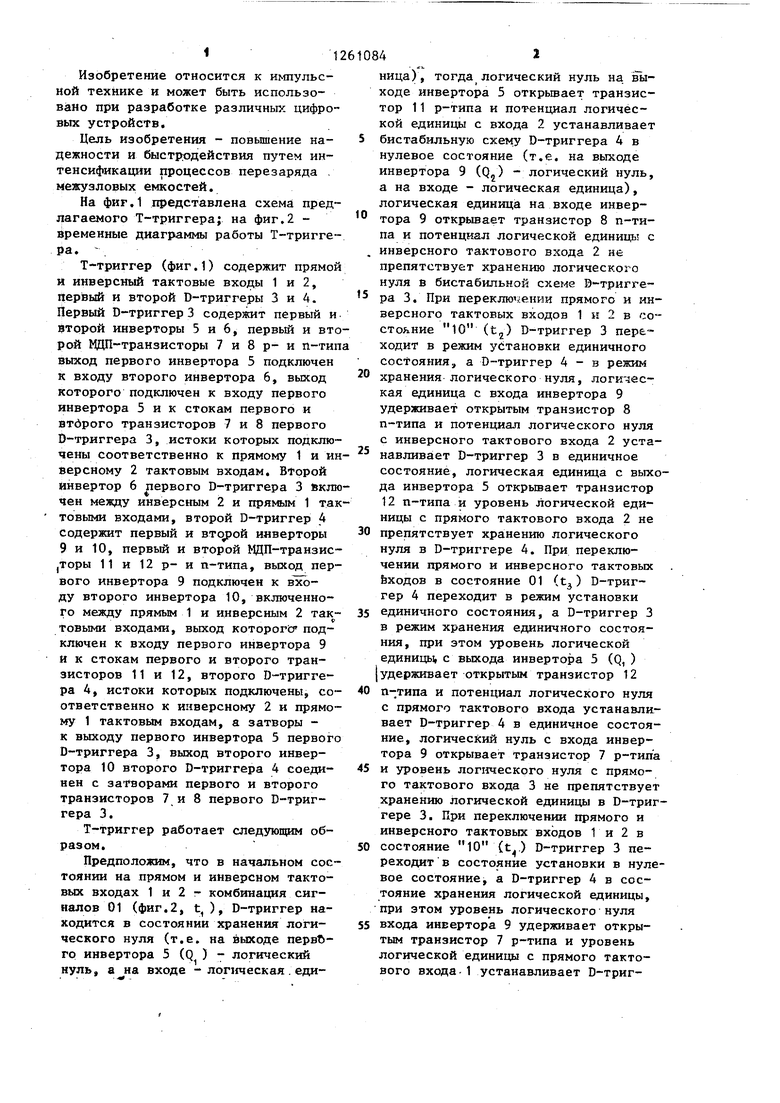

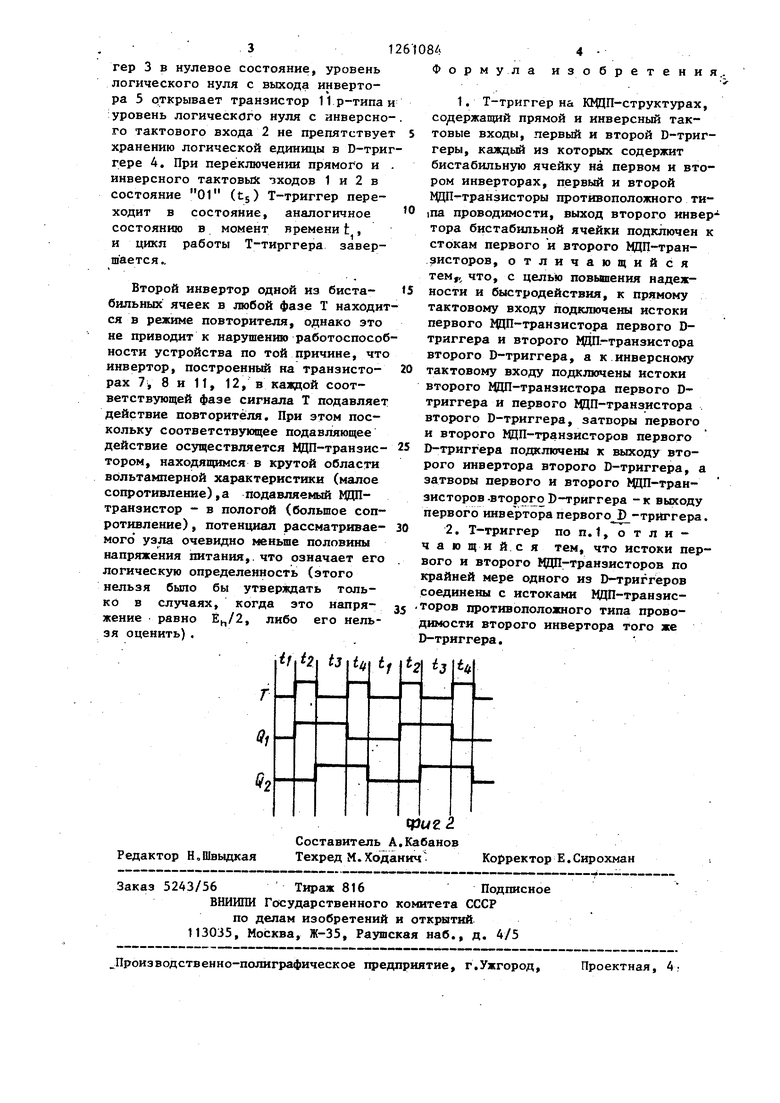

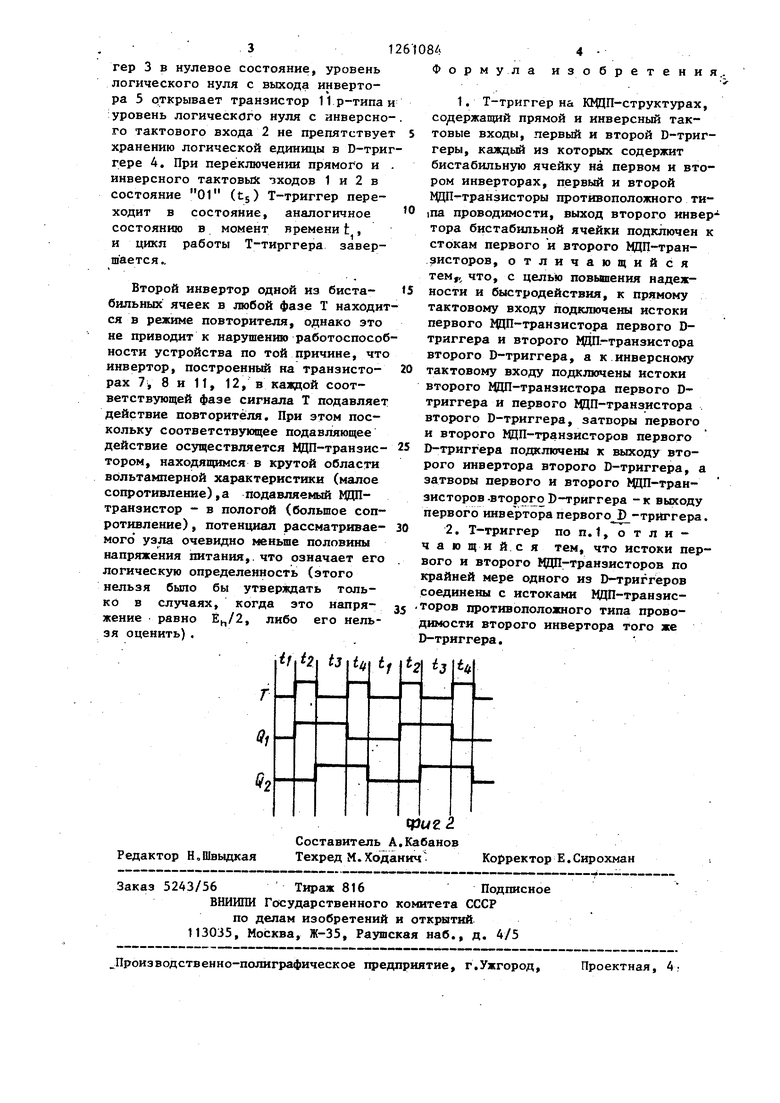

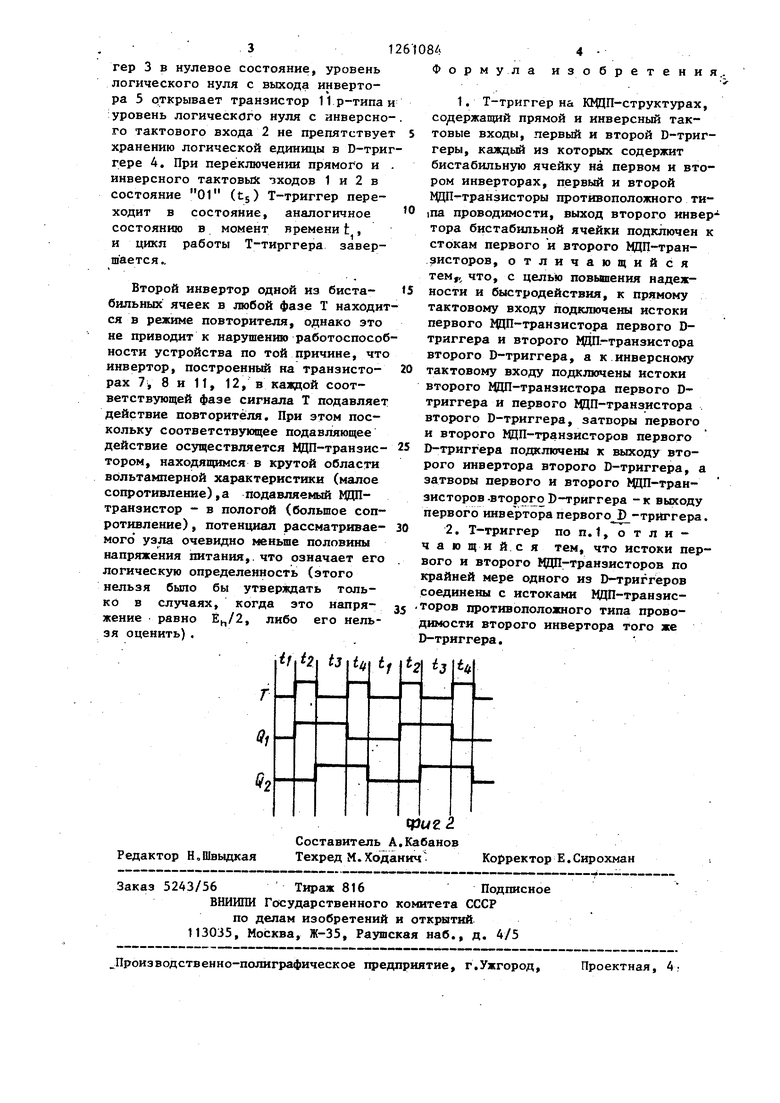

На фиг.1 представлена схема предлагаемого Т-триггера; на фиг.2 - временные диаграммы работы Т-триггера. Т-триггер (фиг.1) содержит прямой и инверсный тактовые входы 1 и 2, пер;вый и второй D-триггеры 3 и 4. Первый D-триггер3 содержит первый и аторой инверторы 5 и 6, первый и второй МДП-транзисторы 7 и 8 р- и п-типа выход первого инвертора 5 подключен к входу второго инвертора 6, выход которого подключен к входу первого инвертора 5 и к стокам первого и втброго транзисторов 7 и 8 первого D-триггера 3, истоки которых подключены соответственно к прямому 1 и инверсному 2 тактовым входам. Второй инвертор 6 первого D-триггера 3 включен между инверсным 2 и прямым 1 тактовыми входами, второй D-триггер 4 содержит первый и второй инверторы 9 и 10, первый и второй МДП-транзис- |Торы 11 и 12 р- и п-типа, выход первого инвертора 9 подключен к входу второго инвертора 10, включенного между прямым 1 и инверсным 2 тактовыми входами, выход которогсг подключен к входу первого инвертора 9 и к стокам первого и второго транзисторов 11 и 12, второго D-триггера А, истоки которых подключены, соответственно к инверсному 2 и прямому 1 тактовым входам, а затворы - к выходу первого инвертора 5 первого D-триггера 3, выход второго инвертора 10 второго D-триггера 4 соединен с затворами первого и второго транзисторов 7 и 8 первого D-триггера 3.

Т-триггер работает следующим образом.

Предположим, что в начальном состоянии на прямом и инверсном тактовых входах 1 и 2 - комбинация сигналов 01 (фиг.2, ц), D-триггер находится в состоянии хранения логического нуля (т.е. на йыходе первТ - гр инвертора 5 (Q ) - логический нуль, а на входе - логическая еди12610842

ница), тогда логический нуль на. выходе инвертора 5 открывает транзистор 11 р-типа и потенциал логической единицы с входа 2 устанавливает бистабильную схему D-триггера 4 в нулевое состояние (т.е. на выходе инвертора 9 (Q,) - логический нуль, а на входе - логическая единица), логическая единица на входе инвертора 9 открывает транзистор 8 п-типа и потенциал логической единицы с инверсного тактового входа 2 не препятствует хранению логического нуля в бистабильной схеме В-тригге- 5 ра 3. При переключении прямого и ин10

20

версного тактовых входов 1 и 2 в со- столние 10 (tj) D-триггер 3 переходит в режим установки единичного состояния, а В-триггер 4 - в режим хранения логического нуля, логическая единица с входа инвертора 9 удерживает открытым транзистор 8 п-типа и потенциал логического нуля с инверсного тактового входа 2 уста навливает D-триггер 3 в единичное состояние, логическая единица с выхода инвертора 5 открьтает транзистор 12 п-типа и уровень логической единицы с прямого тактового входа 2 не

30 препятствует хранению логического нуля в D-триггере 4. При переключении прямого и инверсного тактовых входов в состояние 01 (t) D-триггер 4 переходит в режим установки

35 единичного состояния, а D-триггер 3 в режим хранения единичного состояния, при этом уровень логической единицы, с выхода инвертора 5 (Q, ) jудерживает открытым транзистор 12

40 п-типа и потенциал логического нуля с прямого тактового входа устанавливает D-триггер 4 в единичное состояние, логический нуль с входа инвертора 9 открывает транзистор 7 р-типа

45 и уровень логического нуля с прямого тактового входа 3 не препятствует хранению логической единицы в D-триггере 3. При переключении прямого и инверсного тактовых входов 1 и 2 в

50 состояние 10 (t.) D-триггер 3 переходит в состояние установки в нулевое состояние, а D-триггер 4 в состояние хранения логической единицы, при этом уровень логического нуля

55 входа инвертора 9 удерживает открытым транзистор 7 р-типа и уровень логической единицы с прямого тактового входа-1 устанавливает D-триг

версного тактовых входов 1 и 2 в со- столние 10 (tj) D-триггер 3 переходит в режим установки единичного состояния, а В-триггер 4 - в режим хранения логического нуля, логическая единица с входа инвертора 9 удерживает открытым транзистор 8 п-типа и потенциал логического нуля с инверсного тактового входа 2 устанавливает D-триггер 3 в единичное состояние, логическая единица с выхода инвертора 5 открьтает транзистор 12 п-типа и уровень логической единицы с прямого тактового входа 2 не

препятствует хранению логического нуля в D-триггере 4. При переключении прямого и инверсного тактовых входов в состояние 01 (t) D-триггер 4 переходит в режим установки

единичного состояния, а D-триггер 3 в режим хранения единичного состояния, при этом уровень логической единицы, с выхода инвертора 5 (Q, ) удерживает открытым транзистор 12

п-типа и потенциал логического нуля с прямого тактового входа устанавливает D-триггер 4 в единичное состояние, логический нуль с входа инвертора 9 открывает транзистор 7 р-типа

и уровень логического нуля с прямого тактового входа 3 не препятствует хранению логической единицы в D-триггере 3. При переключении прямого и инверсного тактовых входов 1 и 2 в

состояние 10 (t.) D-триггер 3 переходит в состояние установки в нулевое состояние, а D-триггер 4 в состояние хранения логической единицы, при этом уровень логического нуля

входа инвертора 9 удерживает открытым транзистор 7 р-типа и уровень логической единицы с прямого тактового входа-1 устанавливает D-тригrep 3 в нулевое состояние, уровень логического нуля с выхода инвертора 5 открывает транзистор 11 р-типаи уровень логического нуля с инверсного тактового входа 2 не препятствует хранению логической единицы в D-триг гере 4. При переключении прямого и . инверсного тактовых зходов 1 и 2 в состояние 01 (tj) Т-триггер переходит в состояние, аналогичное состоянию в момент времени t,

и цикл ш ается..

работы Т-тирггера завер

Второй инвертор одной из биста- бильных ячеек в любой фазе Т находится в режиме повторителя, однако это не приводит к нарушению работоспособности устройства по той причине, что инвертор, построенный на транзисторах 7у 8 и И, 12, в каящой соответствующей фазе сигнала Т подавляет действие повторителя. При этом поскольку соответствующее подавляющее действие осуществляется ВДП-транзис- тором, находящимся в крутой области вольтамперной характеристики (малое сопротивление), а подавляемый ЩП- транзистор - в пологой (большое сопротивление) , потенциал рассматривае- мого узла очевидно меньше половины напряжения питания,, что означает его логическую определенность (этого нельзя быпо бы утверзкдать только в случаях, когда это напряжение равно зя оценить).

, либо его нель

Редактор Н„Швыдкая

tpwe

Составитель А.Кабанов

Техред М.Ходанич Корректор Е.Сирохман

Заказ 5243/56 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

.Производственно-полиграфическое предприятие, г.Ужгород,

4

рмула изо

бретения.

5

10

f5

20

25 0

5

1. Т-триггер на КОДП-структурах, соучержащий прямой и инверсный тактовые входы, первый и второй D-триг- геры, каждый из которых содержит бистабильную ячейку на первом и втором инверторах, первый и второй ЩП транзисторы противоположного ти- 1па проводимости, выход второго инвер- тора бистабильной ячейки подключен к стокам первого и второго ЦЦП-тран- зисторов, отличающийся тему/, что, с целью повышения надежности и быстродействия, к прямому тактовому входу подключены истоки первого ОДП-транзистора первого D- триггера и второго ЩП-транзистора второго D-триггера, а к инверсному тактовому входу подключены истоки второго ЩП-транзистора первого D- триггера и первого ЦДП-транзистора . второго D-триггера, затворы первого и второго ВДП-транзисторов первого D-триггера подалючены к выходу второго инвертора второго D-триггера, а затворы первого и второго ЩП-тран- зисторов-второг оD-триггера -к вьосоду первого инвертора первого Р -триггера.

2. Т-триггер ПОП.1, отличающий.ся тем, что истоки первого и второго ВДП-транзисторов по крайней мере одного из D-триггеров соединены с истоками МДП-транзис- .торов противоположного типа проводимости второго инвертора того же D-триггера.

Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер на МПД-транзисторах | 1984 |

|

SU1223349A2 |

| @ -Триггер с предпочтительной установкой в @ -состояние | 1982 |

|

SU1075380A1 |

| Д-триггер | 1985 |

|

SU1261085A1 |

| @ -Триггер на МДП-транзисторах | 1983 |

|

SU1238204A2 |

| @ @ -Триггер | 1983 |

|

SU1091315A1 |

| Д-триггер | 1985 |

|

SU1309267A1 |

| @ -Триггер | 1983 |

|

SU1164867A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1287147A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1291969A1 |

| @ - @ -Триггер на МДП-транзисторах | 1985 |

|

SU1262697A1 |

Изобретение относится к области импульсной техники. Может быть 1 П и 1 8 J f использовано при разработке цифровых устройств. Цель изобретения - повышение надежности и быстродействия. В устройство, содержащее прямой и инверсный тактовые входы 1 и 2j D- триггеры 3, 4, каждый из которых содержит бистабильную ячейку на инверторах 5, 6 и-9, 10 соответственно, а также транзисторы р-ип-типа 7, 8 и 11, 12 соответственно, ддя достижения цели путем интенсификации процессов перезаряда мёжузловых емкостей введены новые связи. 1 з.п.ф-лы, 2 ил. (Л С 1 L§ 1 Q Ш U nJl ь т tsD Од 00 4а

| Букреев И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| М | |||

| : Сов | |||

| радио, 1973j с | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электроника, 1980, № 20, с | |||

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-30—Публикация

1985-01-03—Подача