Ияобретение относится к электросвязи я может быть использовако в системах передачи информации.

Целъв изобретения является повьг- шеиие быстродействия при увеличении дпииы кодовых конбииахщй.

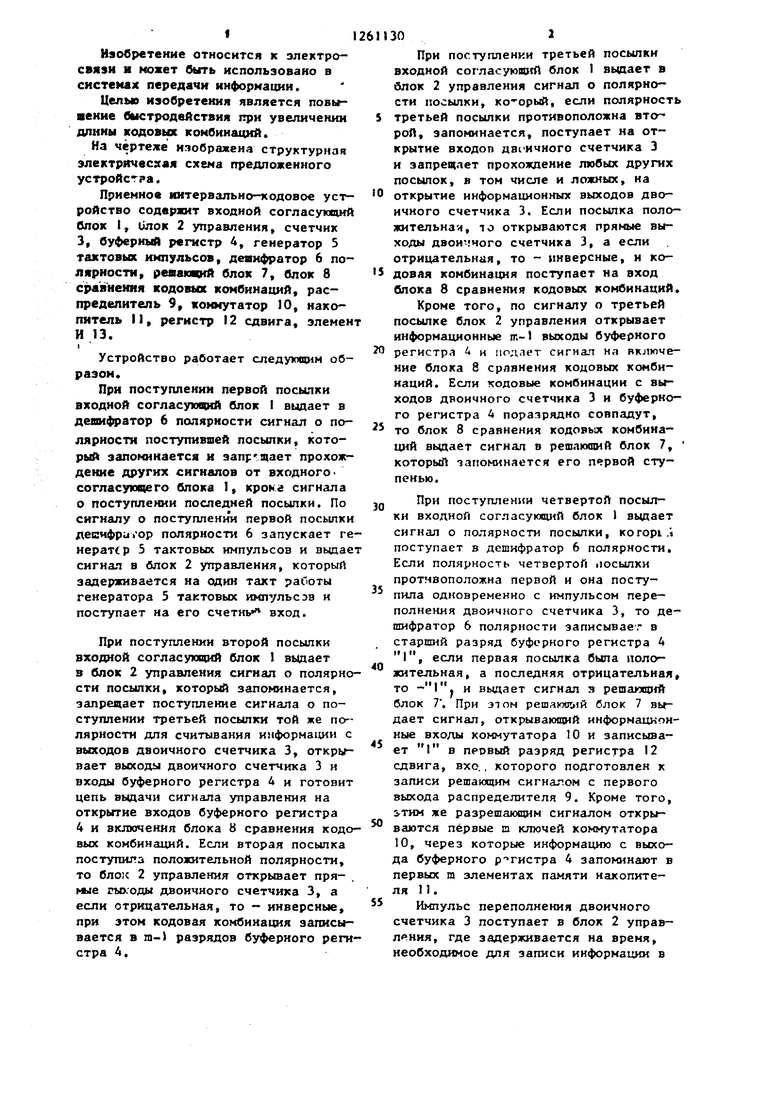

На чертеже изображена структурная элехтричесяая схема предложенного устройства.

Приемное нитервально-кодовое уст- ройство содержит входной согласуюсшй блок I, Олок 2 управления, счетчик 3, буферный регистр 4, генератор 5 тактовьа импульсов, дешифратор 6 полярности рашакщий блох 7, блох 8 сравнения ходовых хомбииаций, распределитель 9, хоммутатор 10, накопитель II, регистр 12 сдвига, элемен И 13.

Устройство работает следующим образом.

При поступлении первой посылки входной согласующий блох I выдает в дешифратор 6 полярности сигнал о по- ляриости поступившей посылки, который запоминается и запрещает прохождение других сигналов от входного- согласующего блока 1, крок.г сигнала о поступлении последней посылки. По сигналу о поступленш первой посылки деснфриуор полярности 6 запускает ге иератср 5 тактовых импульсов и выдае сигнал в блок 2 управления, который задерживается на один тахт раСоты генератора 5 тактовых импульсэв и поступает на его счетны вход.

При поступлении второй посылки входной согласующий блох I выдает в блох 2 управления сигнал о полярности посылки, который запоминается, запрещает поступление сигнала о поступлении третьей посылки той же полярности для считывания информа1щи с выходов двоичного счетчика 3, открывает выходы двоичного счетчика 3 и входы буферного регистра 4 и готовит цепь выдачи сигнала управления на открытие входов буферного регистра 4 и включения блока 8 сравнения кодо вых комбинаций. Если вторая посылка поступила положительной полярности, то бло)с 2 управления открывает пря- «це гы. оды двоичного счетчика 3, а если отрицательная, то - инверсные, при этом ходовая комбинация записывается в т-) разрядов буферного регистра 4.

о

j о

5

5

302

При поступлении третьей посылки входной согласуюпой блок 1 выдает в блок 2 управления сигнал о полярности посылки, который, если полярность третьей посылки противоположна вто рой, запоминается, поступает на открытие входоп двоичного счетчика 3 и запрещает прохождение любых других посылок, в том числе и ложных, на открытие информационных выходов двоичного счетчика 3. Если посыпка положительная, 10 открываются прямые выходы двоичного счетчика 3, а если отрицательная, то - инверсные, и кодовая комбинация поступает на вход блока 8 сравнения кодовых комбинаций.

Кроме того, по сигналу о третьей посылке блок 2 управления открывает информационные т-1 выходы буферного регистра А и подлет сигнал на включение блока 8 сравнения кодовых комбинаций. Если кодовые комбинации с выходов двоичного счетчика 3 и буферного регистра 4 поразрядно совпадут, то блок 8 сравнения кодовья комбинаций выдает сигнал в решаюпшй блок 7, который запоминается его первой ступенью.

При поступлении четвертой посылки входной согласуюотй блок 1 выдает сигнал о полярности посылки, Koropi .i поступает в дешифратор 6 полярности. Если полярность четвертой посылки противоположна первой и она поступила одновременно с импульсом переполнения двоичного счетчика 3, то дешифратор 6 полярности записывает в старший разряд буферного регистра А 1, если первая посылка была положительная, а последняя отрицательная, то . и выдает сигнал з решапщий блок 7. При этом решакяь й блок 7 выдает сигнал, открывающий информационные входы коммутатора 10 и записывает в первый разряд регистра 12 сдвига, вхо.. которого подготовлен к записи решающим сигналом с первого выхода распределителя 9. Кроме того, ьтим же разрешаюощм сигналом открываются первые ш ключей коммутатора 10, через которые информацию с выхода буферного регистра 4 запоминают в первых m элементах памяти накопителя 11.

Импульс переполнения двоичного счетчика 3 поступает в блок 2 управ- , где задерживается на время, необходимое для записи информации в

312

накопитель 11. Задержанный сигнал сбрасывает в исходное состояние элементы памяти блока 2 управления, дешифратора 6 полярности, репаюцего блока 7, буферного регистра н дао- ичный счетчик 3 и, кроме того, поступает на вход распределителя 9, сигнал с которого поступает на вход регистра 12 сдвига и открывает вторые гг. ключей коммутатора 10, цикл приема второго и последующих знаков повторяет цикл приема первого. При этом распределитель 9 делает m последовательных переключений, подключая очередные ю входов накопителя Ii через комкутатор 10 к выходам буферного регистра 4,и регистр 12 сдвига считает правильно принятые знаки. Прием информации осуществляется ло тех пор, пока не будут приняты и записаны в накопитель П все знаки кодогр,, при этом яо всех разрядах регистра 12 сдвига должны быть записа еы I. Тогда элемент И I3 выдает в накопитель М сигнал, речрешаюо1ий считыва- иуе информации на исполнеш1е, сбросы- вает регистр I2 сдвига и распределитель 9 в исходное состоялне.л нл исродл щу сторону перРЛ Тит снгнлл Книт.чниня

Формула изобретения

Приемное интервально-кодовое устройство, содержащее входной согласую- щнй блок, первый и втгрой вьосоды ко- 35 торого со лшнены соответственно с пер- BbW и вторым входами блока управления и соответственно с первым и вторым входами дешифратора полярности, первый выход которого соединен с пер- 40 вым входом решающего блока, второй вход которого подключен к первому выходу счетчика, к третьему входу дешифратора полярности и к третьему вх )ду ;1ока управления, четвертый 45 вход которого подключен к второму выходу дешифратора полярности и к входу

Составитель О. Геллер Редактор М. Недолу,г.с::ко Техред М.Ходаннч Корректор А. Зимокосов

5247/59

Тираж 624 Подписное, BffHUHH Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

. 4

генератора тактовых импульсов, единичный выход котор го соединен с пяг тым входом блока управления, первый выход которого соединен с четвертью входом дешифратора полярности, третий выход которого соедииен с первым входом бу 1 ерного регистра, второй j вход которого подключен к второму выходу блока управления, третий выход которого соединен с первым входом счетчика, вторые выходы которого подключены к третьим входам буферного регистра и к первьм входам блока сравнения кодовых комбинаций, вторые входы которого подключены к первым выходам буферного регистра, при чтом выход блока сравнения кодовых комбинаций соеллнен с третьим входом решающего блока, отличающееся тем, что, с целью повьши ния быстродействия при увеличении длины кодовых комбинаций, в него введены регистр сдвига, элемент И, коммутатор, накопитель и распределитель, выходы которого соединены с первыми входами кок- мутатора и с первыми входами регистра сдвига, выходы которого подключены к входам элемент И, выход которого соединен с первым входом накопителя, с вторьм входом регистра сдпига и с первым входом рлспредепителя, второй нход которого подключен к четвертому выходу бЛ1)кл v-правления, к пятому входу дешифратора полярности, к второму входу счетчнка, к четвертому входу буферного регистра и к четвертому вхо;;7 решающего блока, иькод которого соединен с третьим входом регистра сдвига и с BTopbw входом коммутатора, выходы которого соединены с вторыми входами накопителя, причем первые и второй выходы буферного регистра подключены соответственно к третьим и четвертому входам коммутатора, а инверсный выход reH jpaTopa тактовых пульсов соединен с шестым входом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемное интервально-кодовое устройство | 1981 |

|

SU1029422A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| Передающее интервально-кодовое устройство | 1986 |

|

SU1358106A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Адаптивное устройство для приема информации с групп рассредоточенных объектов | 1990 |

|

SU1837346A1 |

| Устройство для анализа распределения ошибок в кодовой комбинации | 1983 |

|

SU1128401A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

Изобретение относится к электросвязи. Повьшается быстродействие при увеличении длины кодовых комбинаций. Устройство содержит входной согласу- вцкй блок I, блок управления 2, счетчик 3, буферный регистр 4, г-р тактовых импульсов 5, дешифратор полярности 6, решашвий блок 7, блок сравнения кодовых комбинаций 8, распределитель (Р) 9, коммутатор 10, накопитель (Н) И, регистр сдвига (РС) 12, и элемент И 13. Прием информации осуществляется до тех пор, пока не будут приняты Н записаны через кo fyтaтop 10 в Н И все знаки кодограммы, при этом во всех разрядах PC 12, д.б. записаны I. Тогда элемент И 13 выдает сигнал, сбрасывающий PC 12 и Р 9 исходное состояние и разрешающей в .«. 1 считывание информации на исполнение. Т, обр., на передахжую сторону передается сигнал Квитаицкл. Цель достигается введеиием Р 9, коммутатора 10, Н П, PC 12 и злемента И J3. I кл. г (Л ф со

| Приемное стартстопное устройство | 1972 |

|

SU469217A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приемное интервально-кодовое устройство | 1981 |

|

SU1029422A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-09-30—Публикация

1985-05-27—Подача