1С

о N:

4

;о ;о

Изобретение относится к вычислительной технике.

Цель изобретения - упрощение устройства.

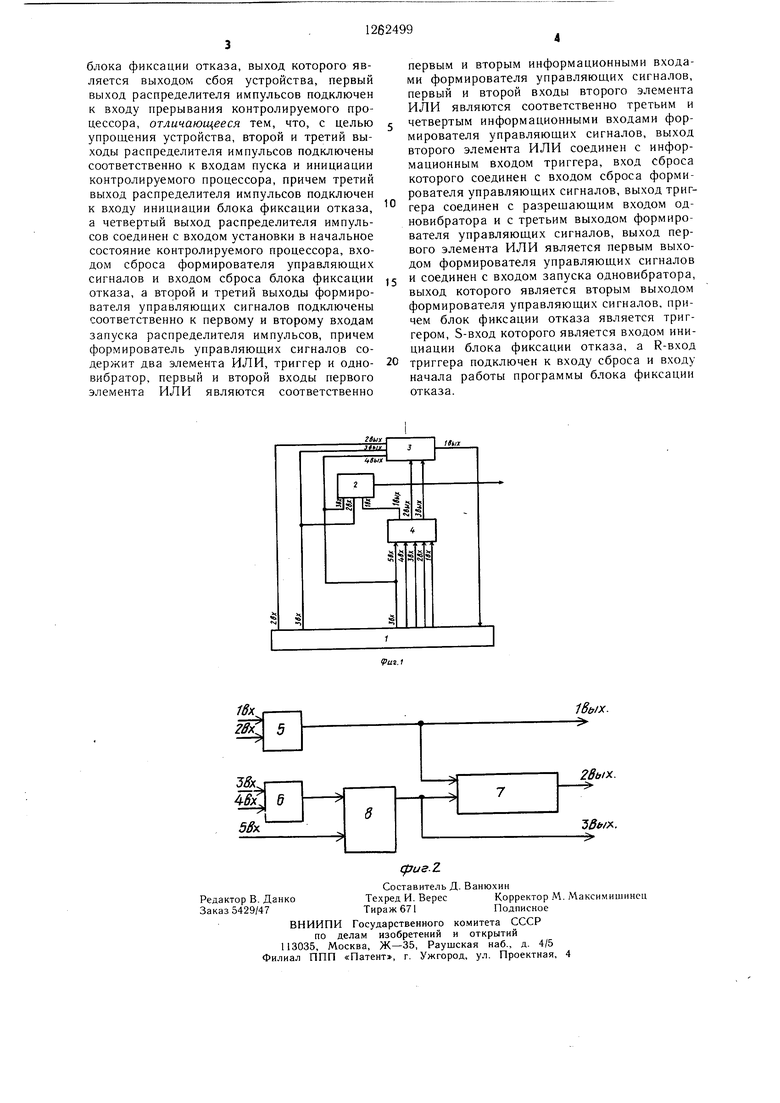

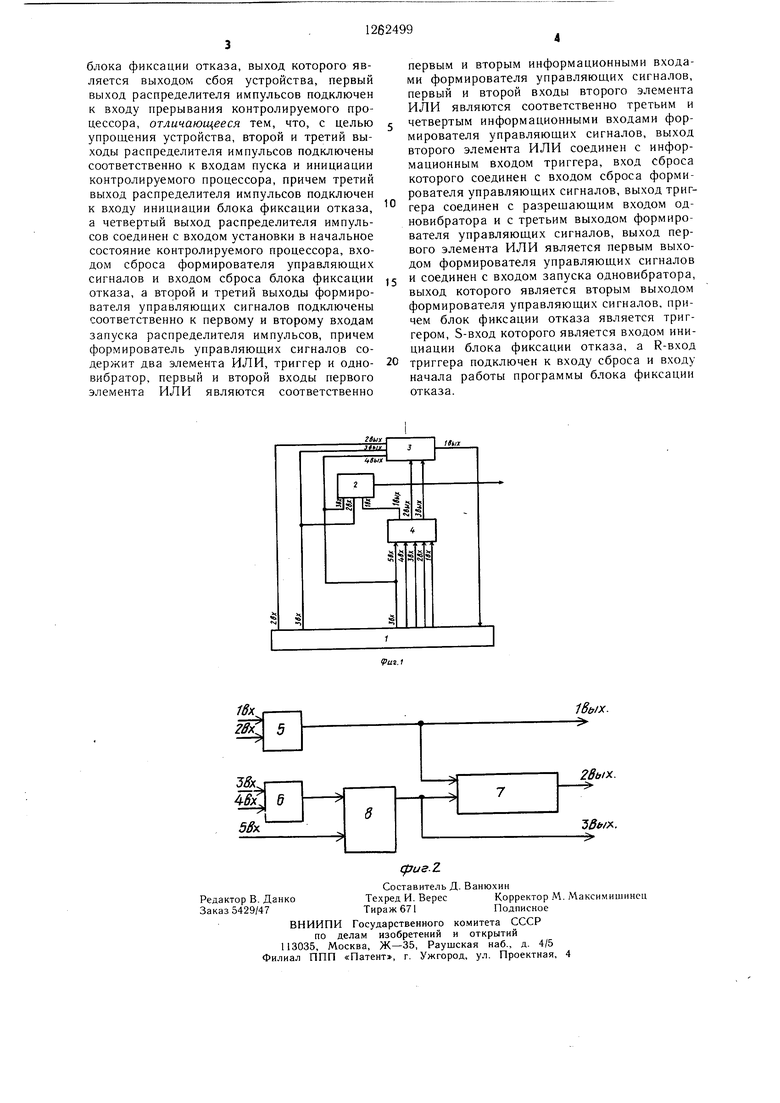

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - структурная схе.ма формирователя управляющих сигналов.

Устройство для перезапуска процессора при сбое (фиг. 1) содержит контролируемый процессор 1, блок 2 фиксации отказа, представляющий собой триггер с одним выходом, распределитель 3 импульсов, формирователь 4 управляющих сигналов.

Формирователь 4 управляющих сигналов (фиг. 2) состоит из первого 5 и второго 6 элементов ИЛИ, одновибратора 7, триггера 8.

Устройство работает следующим образом.

В случае аппаратного или программного сбоя, вызывающего прекращение выполнения программы и зависание системы, формирователь 4 управляющих сигналов генерирует сигнал, который подается с второго выхода формирователя 4 на первый вход запуска распределителя 3 импульсов, вырабатывающего серию из трех последователь)1ых сигналов, имитирующих сигналы пульта: «Сброс, «Инициация, «Пуск. Сигнал «Сброс с четвертого выхода распределителя 3 импульсов подается одновременно на вход сброса блока 2 фиксации отказа, вход установки в начальное состояние операционного блока контролируемого процессора 1 и вход сброса формирователя 4 управляющих сигналов. При появлении сигнала «Сброс на установочном входе операционного блока контролируемого процессора 1 последний вырабатывает сигнал, который переводит контролируемый процессор в исходное состояние. Сигналы «Инициация и «Пуск с выходов распределителя 3 импульсов поступают на соответствующие входы блока сопряжения с пультом контролируемого процессора 1, вызывая перезагрузку операционной системы в оперативную память из внещнего запоминающего устройctBa, т.е. осуществляется процесс, аналогичный действиям человека (оператора) при работе с известным устройством. После загрузки в операционном блоке контролируемого процессора 1 генерируются сигналы, которые подаются на соответствующие входы элемента ИЛИ 6 формирователя 4 (фиг. 2). Сигнал с выхода элемента ИЛИ 6 подается на первый вход триггера 8, устанавливая его в рабочее состояние. Сигнал с выхода триггера 8 вызывает появление на первом выходе распределителя 3 импульсов сигнала прерывания, который поступает на вход прерывания контролируемого процессора, вводя в действие программу, обеспечивающую продолжение выполнения задачи.

Одновременно сигнал с выхода триггера 8 подается на вход одновибратора 7, разрещая его работу по слежению за выполнением программы.

Сигнал «Сброс, поступающий на вход

сброса блока 2 фиксации отказа, переводит последний в исходное состояние.

Сигнал «Инициация, поступающий на вход инициации блока 2, вызывает срабатывание этого блока и появление на его выходе сигнала об отказе в работе процессора. В случае нормального перезапуска программы сигнал о начале работы программы с первого выхода формирователя 4 сигнала ощибки поступает на вход начала работы

5 программы блока 2 фиксации отказа и сбрасывает сигнал об отказе, который может поступать на систему сигнализации для обслуживающего персонала либо на резервную ЭВМ (не показаны).

Периодические контрольные сигналы

0 о прохождении контрольной команды в программе либо об адресе используемого программной внешнего устройства поступают с контрольного разряда выходной адресной шины процессора на соответствующий вход

5 элемента ИЛИ 5. Период обращения программы к этому адресу меньше длительности и.мпульса, вырабатываемого oднoвибpafoром 7, поэтому последний постоянно находится в состоянии запуска. При прекращении выполнения программы одновибратор 7

0 возвращается в исходное состояние, что сопровождается появлением на втором выходе формирователя 4 управляющих сигналов. Четыре контролируемых разряда выходной адресной тины процессора, поступающие на соответствующие входы формирова5 теля сигнала ошибки (блок 4) снимаются с выбранных четырех из 28 адресных линий, которыми процессор адресует устройства сопряжения внешних устройств. Выбранные линии адресуют внешнее устройство, к которому происходит периодическое обращение задачи, выполняемой на ЭВМ.

Периодичес ;ие сигналы, поступающие на информационные входы 16 -46л блока 4, сигнализируют о нормальном выполнении задачи на ЭВМ.

Формула изобретения

Устройство для перезапуска процессора при сбое, содержащее формирователь управляющих сигналов, блок фиксации отказа, распределитель импульсов, причем первый - четвертый разряды выходной адресной шины контролируемого процессора подключены к первому - четвертому соответственно информационным входам формирователя управляющих сигналов, первый выход формирователя управляющих сигналов соединен с входом начала работы программы

блока фиксации отказа, выход которого является выходом сбоя устройства, первый выход распределителя импульсов подключен к входу прерывания контролируемого процессора, отличающееся тем, что, с целью упрощения устройства, второй и третий выходы распределителя импульсов подключены соответственно к входам пуска и инициации контролируемого процессора, причем третий выход распределителя импульсов подключен к входу инициации блока фиксации отказа, а четвертый выход распределителя импульсов соединен с входом установки в начальное состояние контролируемого процессора, входом сброса формирователя управляющих сигналов и входом сброса блока фиксации отказа, а второй и третий выходы формирователя управляющих сигналов подключены соответственно к первому и второму входам запуска распределителя импульсов, причем формирователь управляющих сигналов содержит два элемента ИЛИ, триггер и одновибратор, первый и второй входы первого элемента ИЛИ являются соответственно

первым и вторым информационными входами формирователя управляющих сигналов, первый и второй входы второго элемента ИЛИ являются соответственно третьим и четвертым информационными входами формирователя управляющих сигналов, выход второго элемента ИЛИ соединен с информационным входом триггера, вход сброса которого соединен с входом сброса формирователя управляющих сигналов, выход триггера соединен с разрещающим входом одновибратора и с третьим выходом формирователя управляющих сигналов, выход первого элемента ИЛИ является первым выходом формирователя управляющих сигналов

и соединен с входом запуска одновибратора, выход которого является вторым выходом формирователя управляющих сигналов, причем блок фиксации отказа является триггером, S-вход которого является входом инициации блока фиксации отказа, а R-вход

триггера подключен к входу сброса и входу начала работы программы блока фиксации отказа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

| Устройство для контроля процессора | 1979 |

|

SU881753A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| Устройство для перезапуска ЭВМ | 1984 |

|

SU1205146A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Устройство для контроля хода программы и перезапуска ЭВМ | 1987 |

|

SU1501066A2 |

| Устройство для блокировки и перезапуска ЭВМ при сбоях питания | 1981 |

|

SU993267A1 |

| Устройство для перезапуска вычислительного комплекса при обнаружении сбоя | 1988 |

|

SU1541608A1 |

| МОДУЛЬ СИСТЕМНОГО КОНТРОЛЯ | 2003 |

|

RU2265240C2 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

Авторы

Даты

1986-10-07—Публикация

1984-07-24—Подача