1

Изобретение относится к цисЬровой вычислительной технике и может быть использовано при проектировании процессоров отказоустойчивых вычислительных систем с микропрограммным управлением.

Известно двухканальное устройство микропрограммного управления дублированной вычислительной системы, в котором осуществляется потактное срав- ю нение микрокоманд. Устройство содержит формирователь адреса, блок памяти, формирователь микроопераций, коммутатор, триггер 1 .

Недостатком указанного аналога является низкая функциональная надежность, обусловленная отсутствием средств восстановления при выходе из строя блоков одного из каналов. 20

Известны микропрограммные процессоры с самодиагностикой, содержащие задублированные блоки обработки.

блоки локальной памяти и блок основ ной памяти 2,3j.

Недостатками указанных процессоров являются большой объем дополнительного резервного оборудования и необходимость разработки сложного программного обеспечения для осуществления реконфигурации процессоров.

Известен также микропрограммный процессор с самодиагностикой, содержащий первый и второй блоки обработки информации, коммутатор, схему сравнения , триггер, блоки основной памяти, регистры адреса и данных, блок . микропрограммной памяти, йюрмирователи адреса и микроопераций .

Heдocтaткaмvl указанного аналога являются большой объем средств контроля и сло)хность восстановления работоспособности при возникновении отказа .

Наиболее близким к предлагаемому по технической сущности и достигаемо39му эффекту является процессор, содер жащий блок основной памяти, регистр адреса, регистр данных, блок буферно памяти, два блока локальной памяти, два операционных блока, первый комму татор, первый б/юк элементов И, схему сравнения, первый формирователь адреса микрокоманд, блок памяти микро команд, триггер управления, формиров тель микроопераций, причем первый выход блока основной памяти соединен с входом регистра данных, первый выход которого соединен р первыми вход ми первого и второго блоков локальной памяти соответственно, второй вы ход - с первым входом первого формирователя адреса микрокоманд, третий через регистр адреса - с первым входом блока основной памяти, второй вх которого соединен с первым входом блока буферной памяти и первым выходом формирователя микроопераций, вто рой выход - со вторым входом блока буферной памяти и первым входом формирователя микроопераций, третий вход - с выходом первого блока элементов И, первый вход которого соеди нен с выходом первого коммутатора, второй вход - с первым выходом перво го формирователя адреса микрокоманд, второй вход которого соединен с выходом схемы сравнения, третий вход является входом синхронизации устройства, четвертый вход соединен со вторым выходом формирователя микроопераций, второй вход которого соеди нен с выходом блока памяти микрокоманд, третий выход - с управляющими входами первого коммутатора, первый информационный вход которого соединен с первым входом схемы сравнения и первым выходом первого операционно го блока, второй выход которого соединен со вторым входом первого блока локальной памяти, первый выход ко торого соединен с первым входом первого операционного блока, второй вхо схемы сравнения соединен со вторым информационным входом первого коммутатора и первым выходом второго операционного блока, второй выход которого соединен со вторым входом второ го блока локальной памяти, выход которого соединен с первым входом второго операционного блока 51« Недостатками указанного процессор являются низкая отказоустойчивость и низкая достоверность функционирования 5 8 прототипе реализуется следующая дисциплина функционирования. Результаты работы двух параллельно функционирующих каналов обработки информации сравниваются. При их совпадении осуществляется обмен данными с основной памятью процессора, причем один из каналов определяется как основной, а второй как резервный. В случае несовпадения результатов на. выходе каналов формируется управляющий сигнал, по которому работа процессора блокируется, содержимое каналов передается в буферную память, а затем с использованием специального диагностического оборудования определяется отказавший канал. По результатам диагностики восстанавливается содержимое работоспособного канала и процессор продолжает работу в одноканальном режиме. Низкая отказоустойчивость обусловлена тем, что при наличии второго отказа (первого отказа в другом канале J процессор теряет работоспособность Указанный недостаток ограничивает возможность использования процессора в системах с накоплением отказов. Низкая достоверность функционирования обусловлена тем, что при наличии одного отказа процессор переходит в одноканальный режим и паритетный контроль правильности обработки информации не. производится. Кроме того, прототип имеет большое время диагностики, которое обусловлено тем, что в режиме диагности- ки определяется отказавший или элемент, а не отказавшие микрокоманды и для диагностики не используется информация при передаче ее в буферную память. Большое время диагностики обуславливается также необходимостью передачи содержимого каналов в буферную память и последующей перезагрузки работоспособного канала Низкая отказоустойчивость, низкая достоверность функционирования и большое время диагностики.микропрограммного процессора существенно ограничивает область его применения, снижает эффективность решаемых им задач. Цель изобретения - повышение отказоустойчивости и достоверности функционирования микропрограммного процессора. Поставленная цель достигается тем мто в микропрограммный процессор, содержащий блок основной памяти, регистр адреса, регистр данных, блок бу ферной памяти, первый и второй блоки локальной памяти, первый и второй опе рационные блоки, первый коммутатор, первый блок элементов И, схему сравнения, первый формирователь адреса микрокоманд, триггер управления, блок памяти микрокоманд и первый формирователь микроопер аций, причем первый информационный выход блока основной памяти соединен с входом регистра дан ных, первый выход которого соединен с первыми входами первого и второго бло ков локальной памяти, второй выход регистра данных соединен с входом кода операции первого формирователя мик рокоманд, управляющий выход которого соединен с инверсными входами первого блока элементов И, третий .выход регистра данных соединен с входом рег истра адреса, выход которого соединен с первым адресным входом блока основной памяти, второй информационный выход блока основной памяти соединен с первым информационным входом блока буферной памяти и первым входом формирователя микроопераций, выход микроопераций которого соединен с управляющим входом блока основной памяти и управляющим входом блока буферной памяти, выход первого коммутатора соединен с входом первого блока элементов И, выход которого соединен с информационным входом блока основной памяти, выход блока памяти микрокоманд соединен со вторым входом формирователя микроопераций, адресный выход которого соединен с адресным входом первого формирователя адреса микрокоманд, выход первого операционного блока соединен с первым информационным входом первого коммутатора . и первым входом схемы сравнения, выход которой соединен с управляющим входом формирователя адреса микрокоманд, выход второго операционного блока соединен со вторым входом схемы сравнения, и вторым информационным входом первого коммутатора, прямой и инверсный управляющие входы которого соединены с первым управляющим выходом формирователя микроопераций, второй выход первого операционного блока соединен со вторым входом первого блока локальной памяти, выход оторого соединен с первым информационным входом первого операционного блока, второй выход второго операционного блока соединен со вторым входом второго блока локальной памяти, выход которого соединен с первым информационным входом второго oпepaциoVlнoго блока, вход синхронизации формирователя адреса микрокоманд соединен с входом тактовых импульсов устройства , введены второй и третий коммутаторы, второй, третий и четвертый блоки элементов И, триггер режима, второй формирователь адреса микрокоманд, счетчик адреса, первый, второй и третий элементы ИЛИ, первый и второй одновибраторы, элемент ИЛИ-НЕ,причем информационный выход блока буферной памяти соединен с первыми информационными входами второго и третьего коммутаторов, выход которого соединен ,со вторыми входами первого и второго операционных блоков, выход микроопераций формирователя микроопераций соединен со вторыми информационными входами третьего и второго коммутаторов, выход которого соединен с третьими входами первого и второго блоков локальной памяти, выход первого элемента ИЛИ соединен с входом первого одновибратора, выход которого соединен с первым входом второго элемента ИЛИ, единичный выход триггера управления соединен со вторым входом второго элемента ИЛИ, выход которого соединен с прямыми и инверсными управляющими входами второго и третьего коммутаторов, второй управляющий выход формирователя микроопераций соединен с единичным входом триггера режима, единичный выход которого соединен с первым входом второго блока элементов И, выход микроопераций формирователя соединен со вторым входом второго блока элементов И, выход которого соединен с входами первого элемента ИЛИ и входами второго формирователя адреса микрокоманд, выход второго формирователя адреса микрокоманд соединен с первым входом третьего блока элементов И, выход которого соединен с информационными входами счетчика адреса, первый управляющий выход блока буферной памяти соединен с единичным входом триггера управления, нулевой выход которого соединен со вторым входом- третьего блока элементов И, второй управляющий выход блока буферной памяти соединен с первым входом третьего эле7 980 мента ИЛИ, выход которого соединен с установочным входом счетчика адреса и нулевым входом триггера управления , третий управляющий выход блока j буферной памяти соединен с входом второго одновибратора и счетным входом счетчика адреса, выходы которого соединены со вторым информационным входом блока буферной памяти и входами элементаИЛИ-НЕ, адресный выход пер-О

вого формирователя адреса микрокоманд и выход элемента ИЛИ-НЕ соединены соответственно с первым и вторым входами четиертого блока элементов И, выход которого соединен с входом блока 5 памяти микрокоманд, выход кода отказавших микрокоманд формирователя микроопераций соединен со вторым адресным входом блока основной памяти, выход схемы сравнения и выход второго одновибратора соединены соотвеуственно со вторым и третьим входами третьего элемента ИЛИ, установочный вход устройства соединен с нулевым входом триггера режима, Сущность изобретения состоит в повышении отказоустойчивости и достовер ности функционирования микропрограммного процессора путем использования функциональной избыточности микрокоманд и замены микрокоманд, управляющих отказавшими Функциональными блоками каналов, соответствующими эквивалентными последовательностями микро команд.. Мн6 : ество микрокоманд, образующих Микрооперационный базис Мд вычислительной системы, как правило обладает функциональной избыточностью. Множест во микрокоманд Мд может быть представ лено объединением подмножества микрокоманд МЛ,, без которых не могут быть реализованы все требуемые операции и подмножества микрокоманд М.2, вводи мых дополнительно для обеспечения заданного уровня производительности сис темы. Поэтому часть микрокоманд подмножества М.1 может быть выполнена пу тем реализации эквивалентной последовательности других микрокоманд из подмнох еств .М.1 и М.2. Например, микрокоманды операции умножения могут быть заменены последовательностью мик рокоманд сложения и сдвига. Это позволяет для большинства микрокоманд формировать эквивалентные заменяющие последовательности и использовать их при соответствующих отказах с целью восстановления работоспособности.

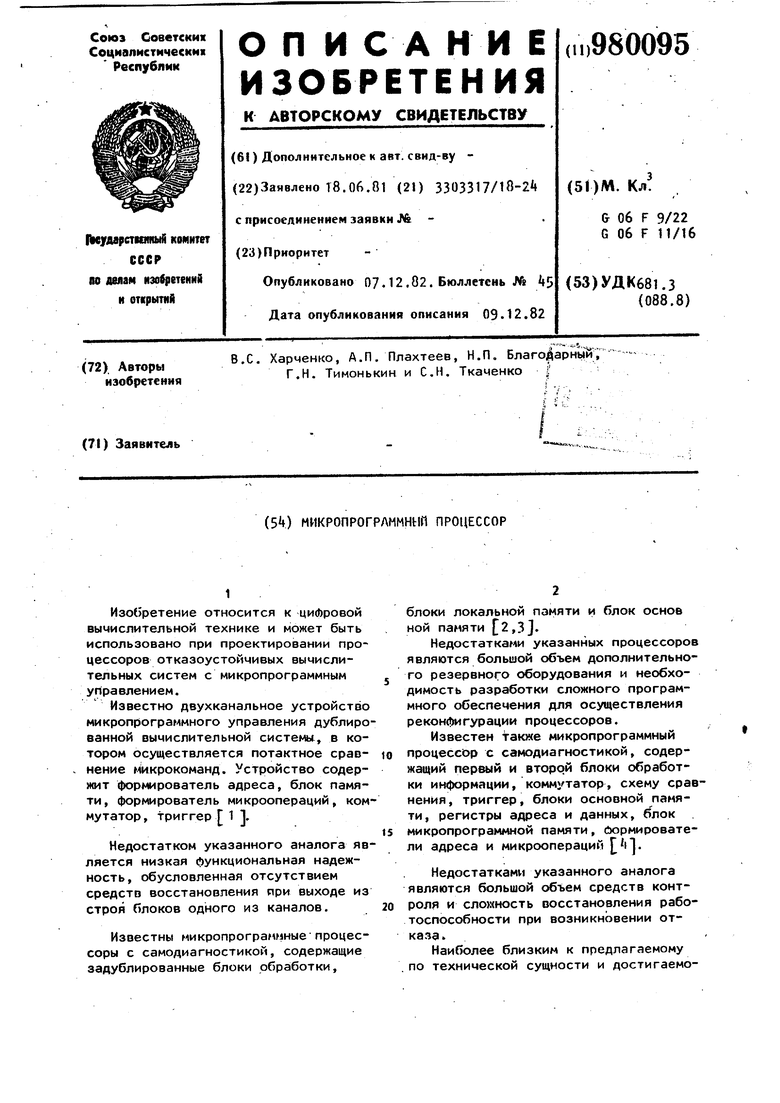

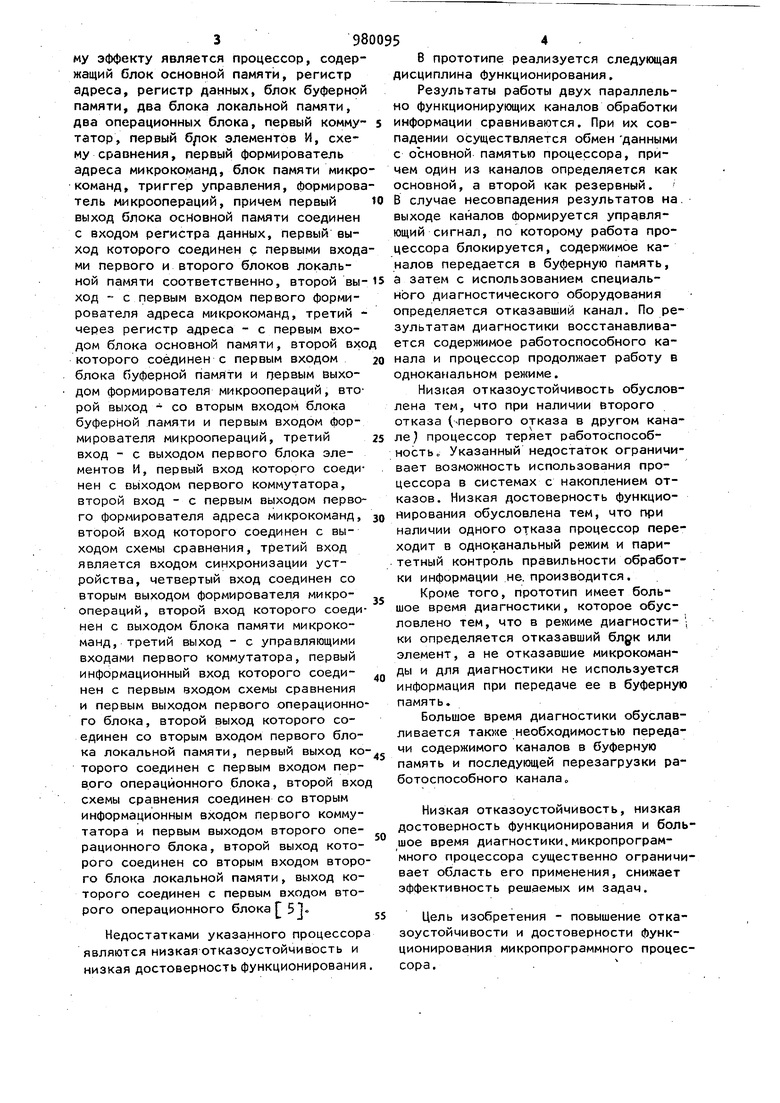

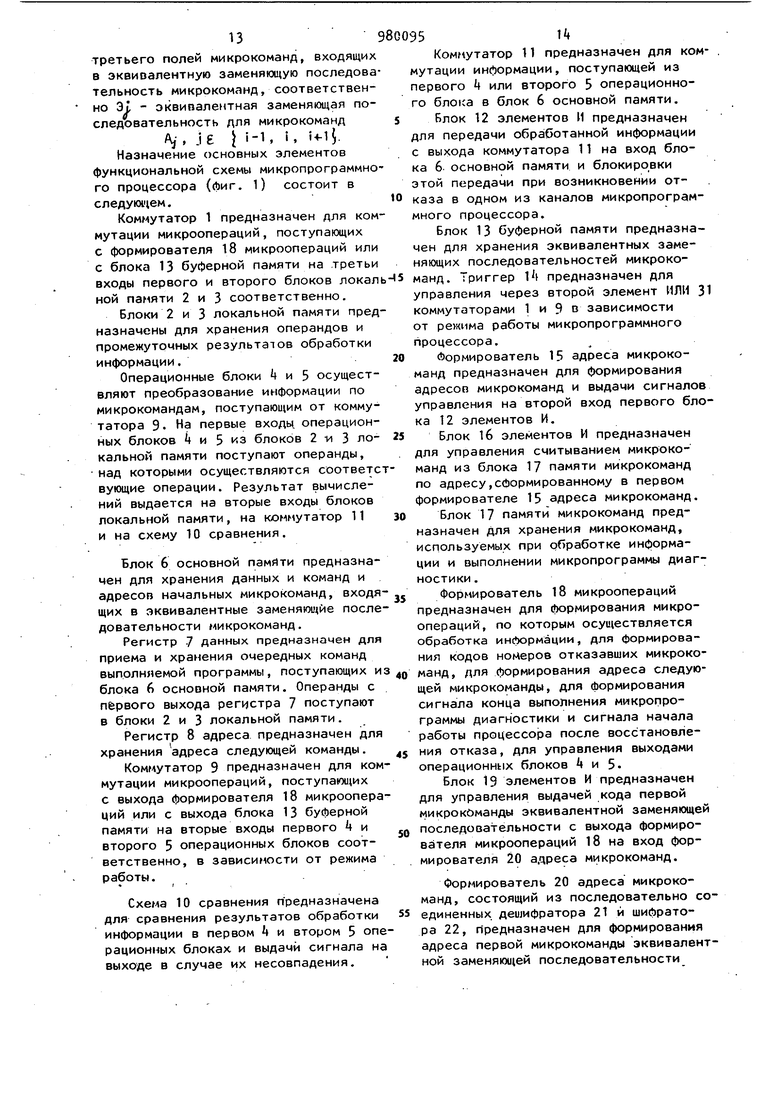

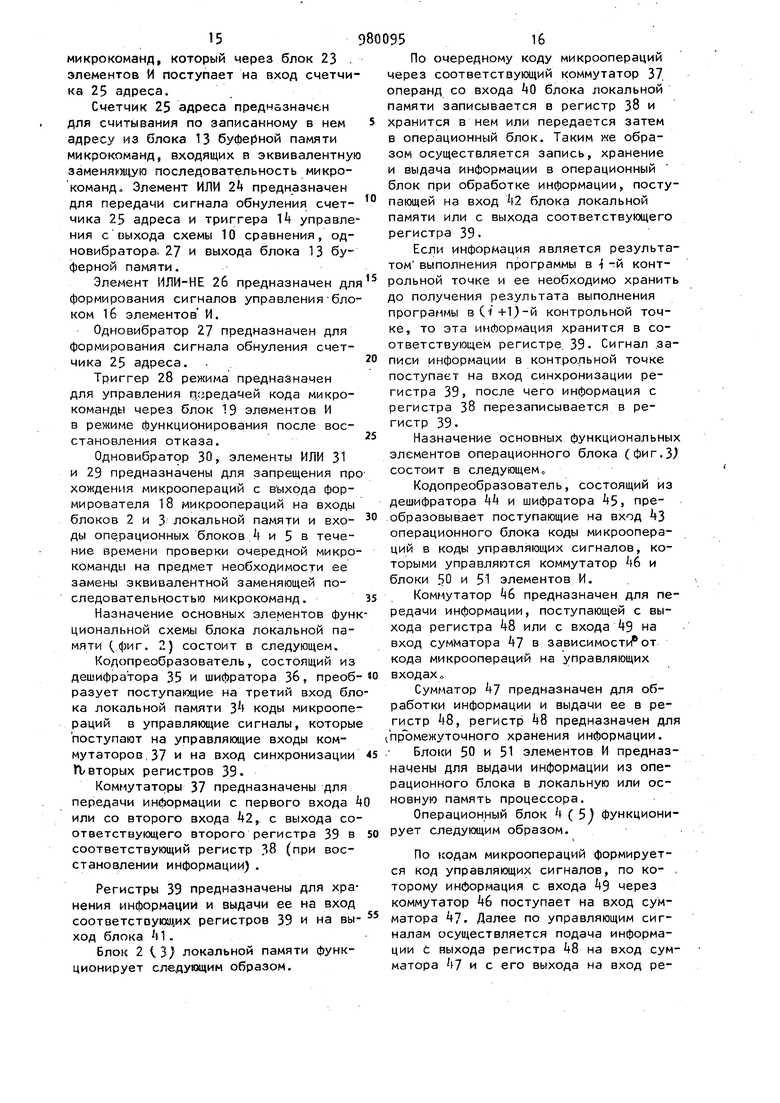

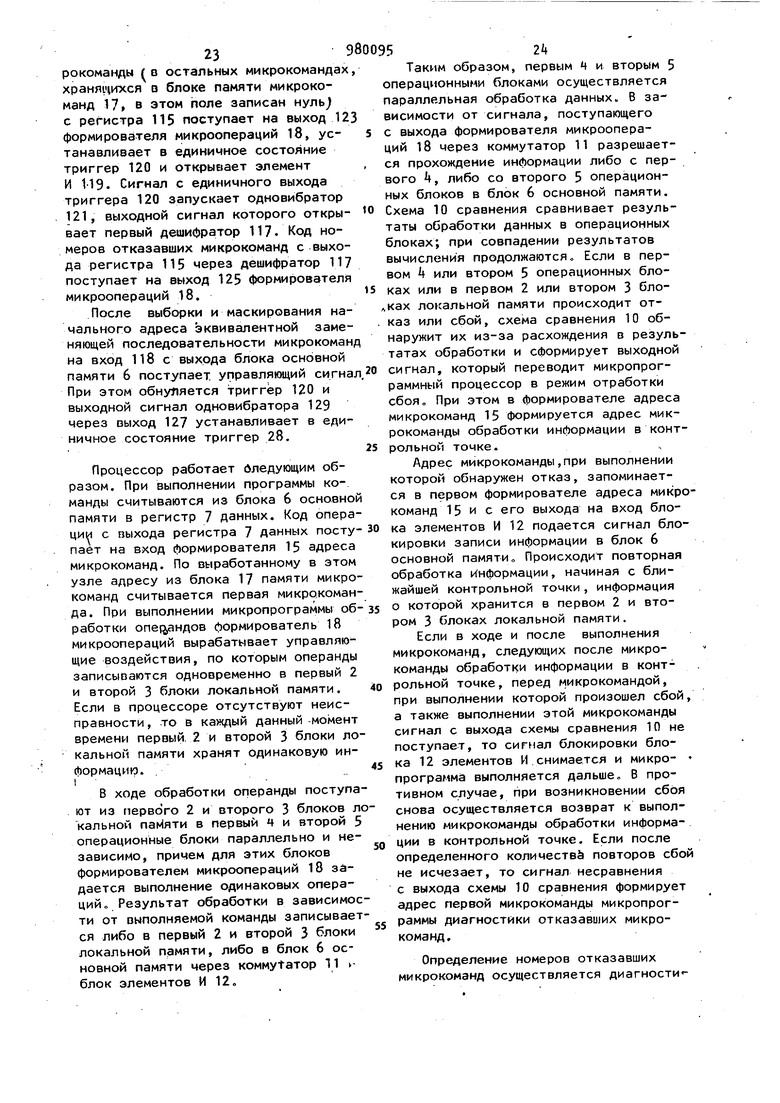

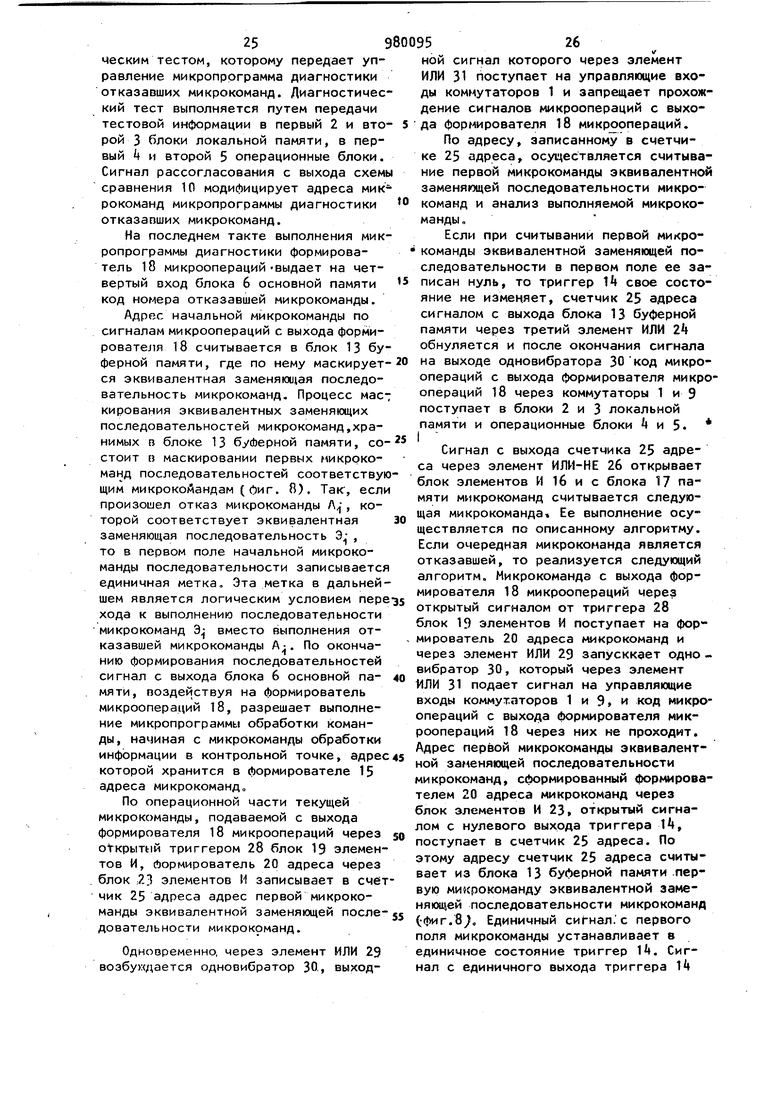

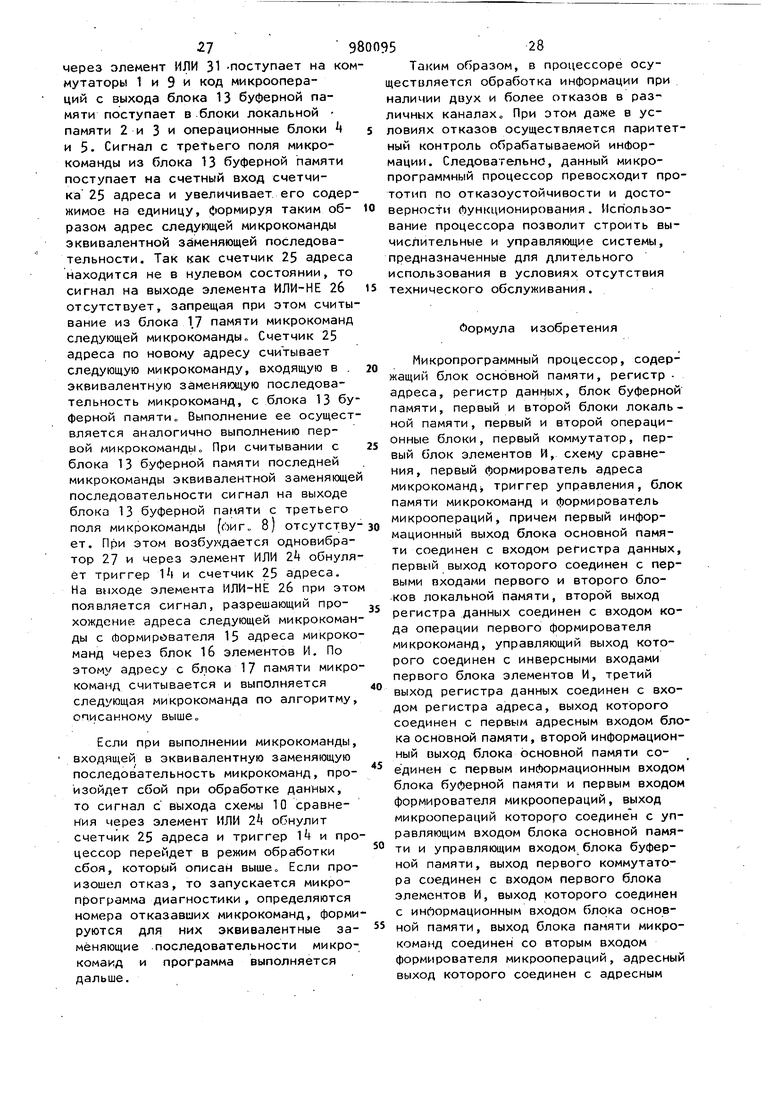

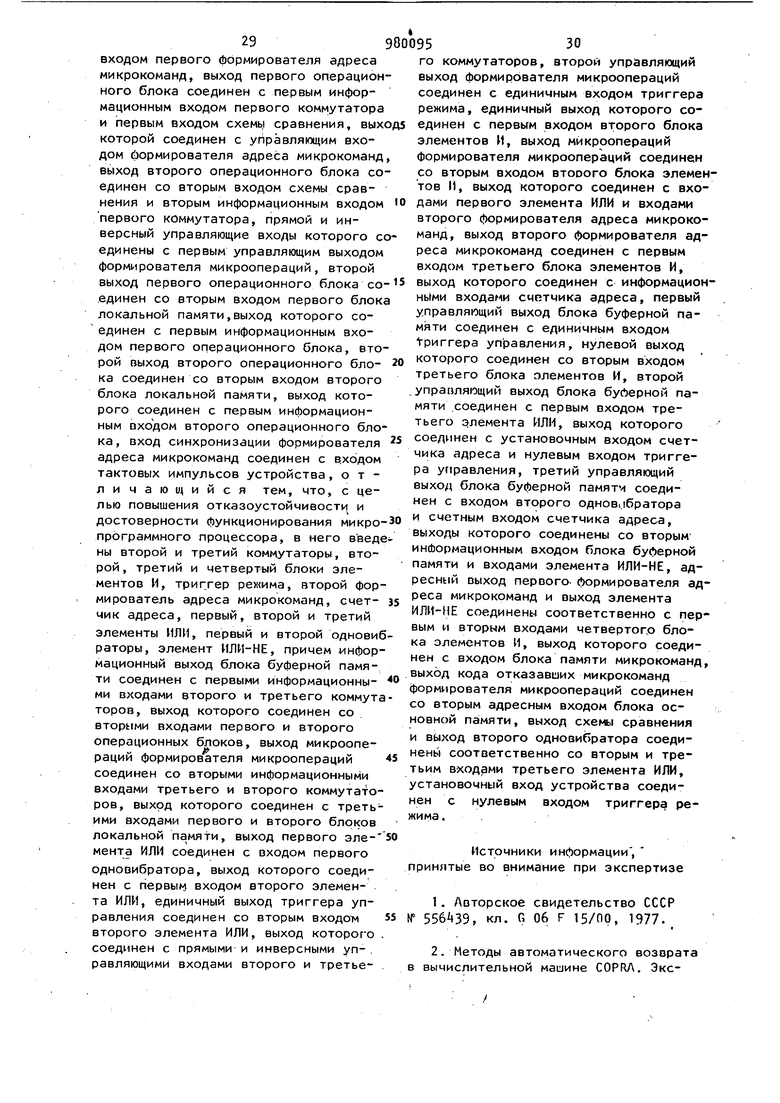

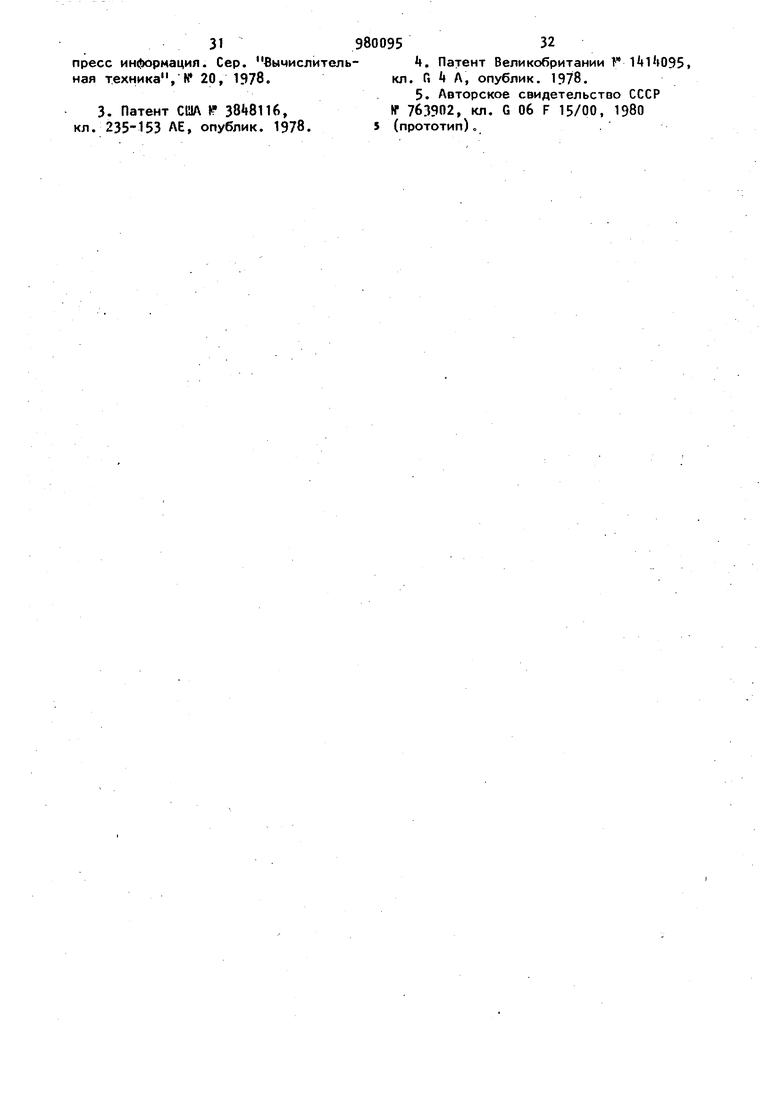

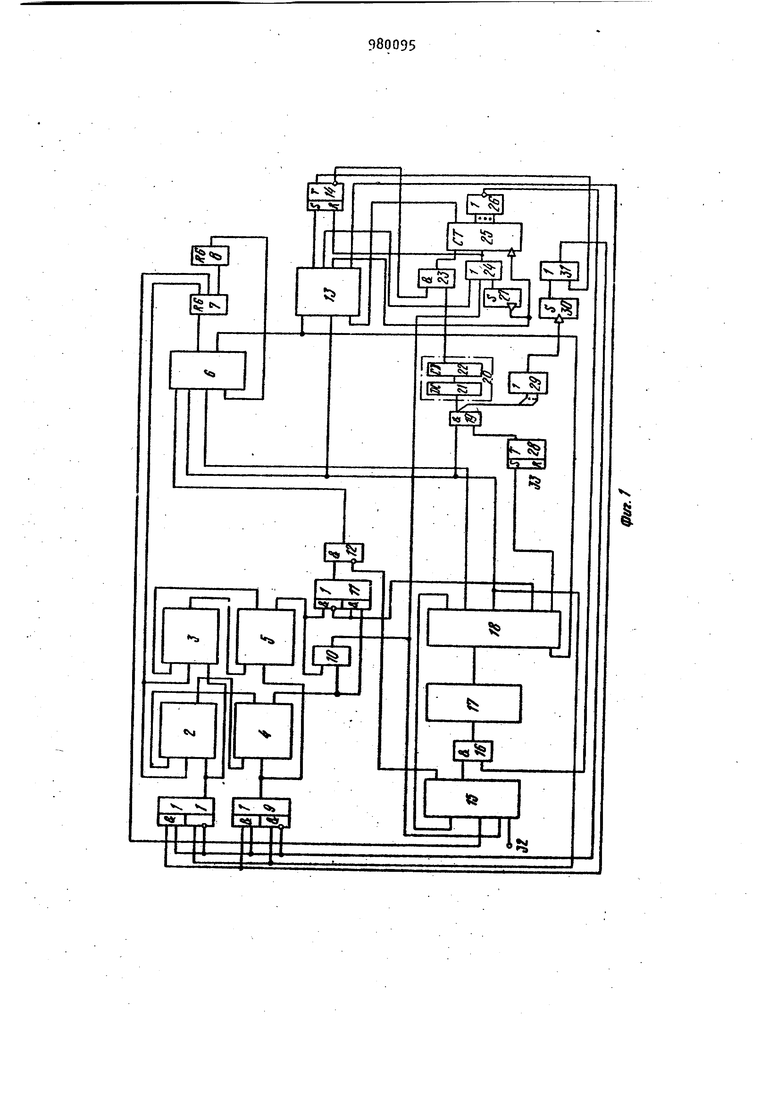

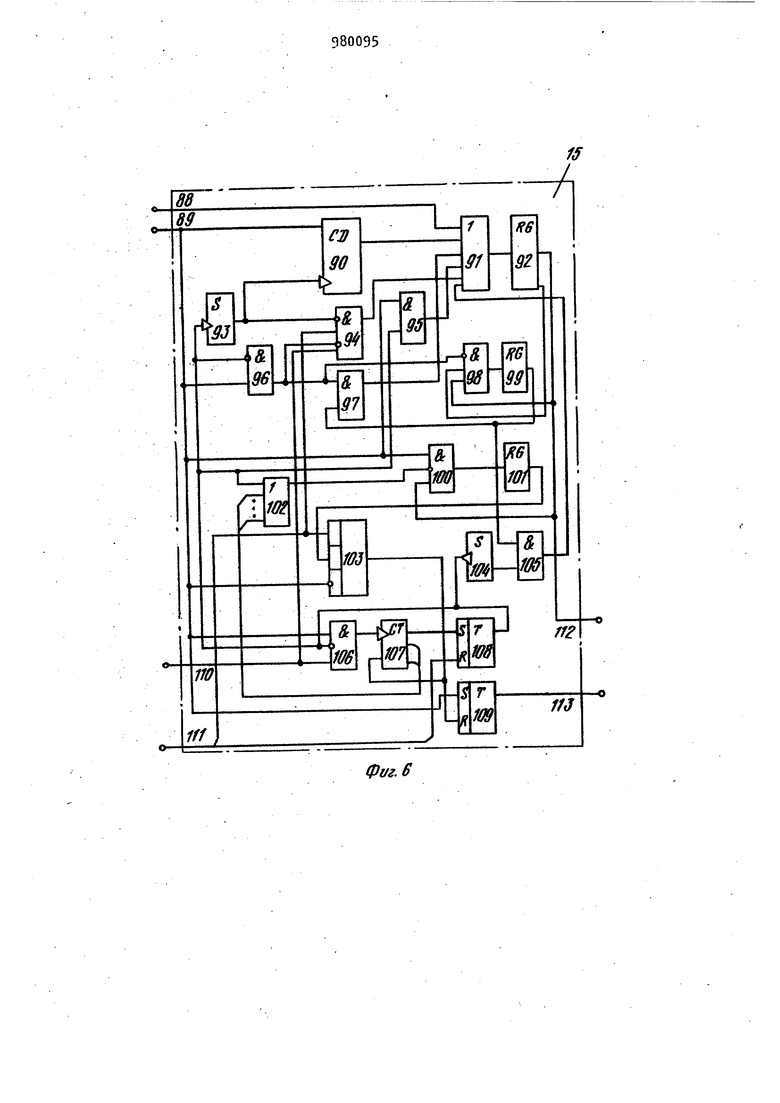

составляется список отказавших микрокоманд; в блоке буферной памяти хранятся эквивалентные заменяющие последовательности микрокоманд, которые могут пополняться по мере накопления отказов; при появлении в одном из каналов отказа, определении отказавших микрокоманд и маскирования соответствующих эквивалентных заменяющих по95Основные отличительные особенности реализованной в процессоре дисциплины функционирования состоят в следуг ющем: при отказе одного из каналов микродиагностика проводится с целью определения микрокоманд, которые не выполняются вследствие отказа соответствующего функционального блока( а не самих функциональных блоков ; на основе результатов микродиагностики следовательностей в блоке буферной памяти, микропрограммный процессор переходит во второй режим нормального функционирования, который характеризуется потактным обращением к блоку буферной памяти с целью проверки необходимости выполнения эквивалентной заменяющей последовательности микрокоманд. Для реализации сущности изобретения в микропрограммный процессор дополнительно введены второй и третий коммутаторы, три блока элементов И, три элемента ИЛИ, элемент ИЛИ-НЕ, второй триггер, второй формирователь адреса микрокоманд, состоящий из дешифратора и шифратора, два одновибратора, счетчик адреса. I.в Код микрокоманды, считываемой из блока памяти микрокоманд в формирователь микроопераций, разбит на пять полей: поле метки конца выполнения микропрограммы диагностики; поле кода выполняемых микроопераций; поле метки управления выдачей обработанной информации с первого или второго канала е блок основной памяти; поле кода адреса следующеймикрокоманды; по-; ле кода отказавших микрокоманд. Код микрокоманд, вводящих в эквивалентную заменяюи ую последовательность микрокоманд, состоит из трех полей: поле метки., определяющей необходимость выполнения данной эквивалентной заменякдцей последовательности микрокоманд; поле кода микроопераций; поле метки считывания информации. 9 Введение второго и третьего комму таторов и обусловленных ими связей позволяет управлять обработкой информации в обоих каналах либо по мик рокомандам, поступающим с формирователя микроопераций, либо по микрокомандам, входящим в эквивалентную заменяющую последовательность микрокоманд и считываемым из блока буферной памяти. Введение четвертого блока элементов И, элемента ИЛИ-НЕ и обусловленных ими связей необходимо для управления выдачей адреса следующей.микро команды в блок памяти микрокоманд только после выполнения эквивалентно заменя эщей последовательности микрокоманд, выполняемых вместо отказавшей микрокоманды. Введение триггера режима, второго формирователя адреса микрокоманд, второго блока элементов И и обусловленных ими связей позволяет записывать в счетчик адреса адрес первой микрокоманды эквивалентной заменяющей последовательности для отказавшей микрокоманды. Второй формирователь адреса микро команд может быть выполнен в виде пр граммируемой логической матрицы. Поскольку список микрокоманд, которые могут быть заменены эквивалентными последовательностями, известен, то оп рационным частям этих микрокоманд ст новится в соответствие адрес начальной микрокоманды эквивалентной заменя ющей последовательности. Например, если полное множество заменяемых микрокоманд состоит из ми рокоманд R, R, ...,RK дешифрато второго формирователя адреса имеет К вь1ходов и Ч входов ( if - разрядность операционной части Ш-микрокоманд R, i е 1,к). На каждом из выходов дешифратора di реализуется функция г; где двоичная переменная j-того разряда операционной части . Шифратор второго формирователя адрес имеет в этом случае входов и Ё. выходов, где g--}eog-2 Z W, 95 число микрокоманд, образуюгде f4| щих эквивалентную заменяющую последовательность для i-той микрокоманды. Шифратор формирует на своих выходах двоичные коды разрядностью , . которые соответствуют единичным сигналам, поступающим с выхода дешифратора. Эти коды задают начальные адреса эквивалентных заменяющих последовательностей. Введение счетчика адресов обусловь лено необходимостью формирования адресов микрокоманд, входящих в эквивалентную заменяющую последовательность микрокоманд, и считывания по этим адресам микрокоманд из блока буферной памяти. Соединение третьего управляющего выхода блока буйерной памяти со счетным входом счетчика адреса и введение третьего элемента ИЛИ, второго одновибратора и обусловленных ими связей необходимо для увеличения содержимого счетчика адреса в рроцессе считывания микрокоманд, входящих в эквивалентную заменяющую последовательность микрокоманд, и его обнуления по окончании выполнения последовательности или при сбое в процессе ее выполнеВведение первого и второго элементов ИЛИ, первого одновибратора и обусловленных ими,связей позволяет блокировать выполнение очередной микрокоманды, считываемой с выхода формирователя микроопераций, на время проверки принадлежности ее к числу отказавших микрокоманд. На фиг. 1 приведена функциональная схема микропрограммного процессора; на фиг. 2 - функциональная схема блоков локальной памяти, выполненных идентично; на фиг. 3 - функциональная схема операционных блоков, выполненных идентично; на фиг. - Функциональная схема блока основной памятй; на Лиг. 5 функциональная схема блока буферной памяти; на фиг. 6 функциональная схема первого йюрмирователя адреса микрокоманд; на фиг. 7 функциональная схема формирователя микроопераций. Пример кодирования полей эквивалентных заменяющих последовательностей микрокоманд для отказавих и неотказавших микрокоманд показан на фиг. 8. 119 На фиг. 1 используются следующие обозначения: второй коммутатор 1, первый блок 2 локальной памяти, второй блок 3 локальной памяти, первый операционный блок k и второй операционный блок 5 блок 6 основной памя ти, регистр 7 данных, регистр 8 адре са, третий коммутатор 9, схема 10 сравнения, первый коммутатор 11, первый блок 12 элементов И, блок 13 буферной памяти, триггер 1 управления, первый формирователь 15 адреса микрокоманд, четвертый блок 16 элеме тов И, блок 17 памяти микрокоманд, формирователь 18 микроопераций, второй блок 19 элe)eнтoв И, второй формирователь 20 адреса микрокоманд, состоя1 ий из дешифратора 21 и шифратора 22, третий блок 23 элементов И, третий элемент ИЛИ 2, счетчик 25 ад реса элемент ИЛИ-НЕ 2б, второй одно вибратор 27, триггер 28 режима, первый элемент ИЛИ 29, первый одновибра тор 30, второй элемент ИЛИ 31, вход синхронизации, вход 33 установки триггера 28 в нуль. На фиг. 2 используются следующие обозначения: третий вход 3 блока ло кальной памяти, дешифратор 35, шифра тор 36, и коммутаторов 37,V первых регистров 38, Y) вторых регистров 39, первый вход АО блоков локальной памяти, выход 1 блока локальной памяти, второй вход 2 блока локальной памяти. На фиг. 3 используются следующие обозначения: второй вход k3 операционного блока, дешифратор kk, шифратор ,коммутатор 46, сумматор 7, регистр 8, второй вход 9 операцион ного блока, первый 50 и второй 51 бл ки элементов И, первый 52 и второй 5 выходы операционного блока соответст венно. На фиг. используются следующие обозначения: информационный вход 5l блока основной памяти, регистр 55, первый накопитель 5б информации , пер вый адресный вход 57 блока основной памяти,управляющий вход 58 блока основной памяти,первый элемент И 59, вход 60 импульсов записи ,вход 61 импуль сов считывания,второй элемент И 62,тре тий элемент И 63, второй накопитель 6Ц информации,второй 65 адресный вход, первый 66 и второй 67 информационные выходы блока основной памяти соответственно. 5 На фиг, 5 используются следующие обозначения: управляющий вход 68 блока буферной памяти, первый блок 69 элементов И, блок 70 элементов ИЛИ, накопитель 71 информации,, первый 72 и второй 73 информационные входы блока буферной памяти, второй блок 7 элементов И, первый элемент ИЛИ 75, вход 76 импульсов записи, первый 77 и второй 78 элементы И соответственно, вход 79 генератора константы единицы (пход постоянного уровня логической единицы, второй элемент ИЛИ 80, третий элемент И 81, вход 82 импульсов считывания, четвертый элемент И 83, первый управляющий, информационный 85, третий 86 и второй 87 управляющие выходы блока буферной памяти соответственно. На фиГо 6 используются следующие обозначения: вход 88 кода операции и управляющий вход 89 первого формирователя адреса микрокоманд соответственно, шифратор 90, блок 91 элементов ИЛИ, регистр 92 адреса, первый одновибратор 93, первый блок 9 элементов И, третий элемент И 95, первый элемент И 9б, второй блок 97 элементов И, пятый.блок 98 элементов И, второй буферный регистр 99, третий блок 100 элементов И, первый буферный регистр 101, элемент ИЛИ 102, схема 103 сравнения, второй одновибратор 104, четвертый блок 105 элементов И, второй элемент И 106, счетчик 107 сбоев, первый 108 и второй 199 триггеры, синхронизирующий и адресный ВХО.ДЫ 110 и 111 первого формирователя адреса микрокоманд соответственно, адресный и управляющий выходы 112 и 113 первого .формирователя адреса микрокоманд соответственно. На Лиг. 7 используются следующие обозначения: второй вход 114 формирователя микроопераций, регистр 115 микрокоманд, группа первых дешифраторов 116, дешифратор 117, первый вход 118 формирователя lикpooпepaций, элемент И 119, триггер 120, первый 121 и второй 122 о дновибраторы соответственно, выход адреса, первый управляющий выход, выходы кодаотказавших микрокоманд, микроопераций и второй управляющий выход формирователя микроопераций 123-127 соответственно„На Лиг. 8 Используются следующие обозначения: 1-3 - столбцы первоготретьего полей микрокоманд, входящих в эквивалентную заменяющую последова тельность микрокоманд, соответственно Э1 - эквивалентная заменяющая последовательность для микрокоманд Ai,- , j I i-1, i, i+-lj. Назначение основных элементов функциональной схемы микропрограммно го процессора (фиг. 1) состоит в следую1чем. Коммутатор 1 предназначен для ком мутации микроопераций, поступающих с формирователя 18 микроопераций или с блока 13 буферной памяти на третьи входы первого и второго блоков локал ной памяти 2 и 3 соответственно. БЛОКИ 2 и 3 локальной памяти пред назначены для хранения операндов и промежуточных результатов обработки информации. Операционные блоки k и осуществляют преобразование информации по микрокомандам, поступающим от коммутатора 9. На первые входы, операционных блоков и 5 из блоков 2 VI 3 ЛОкальной памяти поступают операнды, над которыми осуществляются соответс вующие операции. Результат вычислений выдается на вторые входы блоков локальной памяти, на коммутатор 11 и на схему 10 сравнения. Блок 6 основной памйти предназначен для хранения данных и команд и адресов начальных микрокоманд, входя щих в эквивалентные заменяюи йе после довательности микрокоманд. Регистр 7 данных предназначен для приема и хранения очередных команд выполняемой программы, поступающих и блока 6 основной памяти. Операнды с первого выхода регистра 7 поступают в блоки 2 и 3 локальной памяти. Регистр В адреса предназначен для хранения адреса следующей команды. Коммутатор 9 предназначен для ком мутации микроопераций, поступающих с выхода формирователя 18 микроопера ций или с выхода блока 13 буферной памяти на вторые входы первого t и второго 5 операционных блоков соответственно, в зависимости от режима работы. / Схема 10 сравнения предназначена для сравнения результатов обработки информации в первом t и втором 5 опе рационных блоках и выдачи сигнала на выходе в случае их несовпадения. 95U Коммутатор 11 предназначен для коммутации информации, поступающей из первого k или второго 5 операционного блока в блок 6 основной памяти, Влок 12 элементов И предназначен для передачи обработанной информации с выхода коммутатора 11 на вход блока 6 основной памяти и блокировки этой передачи при возникновении отказа в одном из каналов микропрограммного процессора. Блок 13 буферной памяти предназначен для хранения эквивалентных заменяющих последовательностей микрокоманд. Триггер k предназначен для управления через второй элемент ИЛИ 31 коммутаторами 1 и 9 в зависимости от режима работы микропрограммного процессора. Формирователь 15 адреса микрокоманд предназначен для формирования адресов микрокоманд и выдачи сигналов управления на второй вход первого блока 12 элементов И. Блок 1б элементов И предназначен для управления считыванием микрокоманд из блока 17 памяти микрокоманд по адресу,сформированному в первом формирователе 15 адреса микрокоманд. Блок 17 памяти микрокоманд предназначен Для хранения микрокоманд, используемых при обработке информации и выполнении микропрограммы диагностики . Формирователь 18 микроопераций предназначен для формирования микроопераций, по которым осуществляется обработка информации, для формирования кодов номеров отказавших микрокоманд, для формирования адреса следующей микрокоманды, для формирования сигнала конца выполнения микропрограммы диагностики и сигнала начала работы процессора после восстановления отказа, для управления выходами операционных блоков А и 5. Блок 19 элементов И предназначен для управления выдачей кода первой микрокоманды эквивалентной заменяющей последовательности с выхода формирователя микроопераций 18 на вход формирователя 20 адреса микрокоманд. Формирователь 20 адреса микрокоманд, состоящий из последовательно соединенных дешифратора 21 и шифратора 22, предназначен для формирования адреса первой микрокоманды эквивалентной заменяющей последовательности микрокоманд, который через блок 23 . элементов И поступает на вход счетчи ка 25 адреса. Счетчик 25 адреса предназначен для считывания по записанному в нем адресу из блока 13 буферной памяти микрокоманд, входящих R эквивалентну заменящую последовательность микрокоманд. Элемент ИЛИ предназначен для передачи сигнала обнуления счетчика 25 адреса и триггера 14 управле ния с выхода схемы 10 сравнения, одновибратора. 27 и выхода блока 13 буферной памяти. Элемент ИЛИ-НЕ 2б предназначен дл формирования сигналов управлениябло ком 16 элементов И. Одновибратор 27 предназначен для формирования сигнала обнуления счетчика 25 адреса. . Триггер 28 режима предназначен для управления пгфедачей кода микрокоманды через блок 19 элементов И в режиме функционирования после восстановления отказа. Одновибратор 30, элементы ИЛИ 31 и 29 предназначены для запрещения пр хождения микроопераций с выхода формирователя 18 микроопераций на входы блоков 2 и 3 локальной памяти и входы операционных блоков 4 и 5 в течение времени проверки очередной микро команды на предмет необходимости ее замены эквивалентной заменяющей последовательностью микрокоманд. Назначение основных элементов фун циональной схемы блока локальной памяти (.фиг, 2) состоит в следующем. Кодопреобразователь, состоящий из дешифратора 35 и шифратора 36, преоб разует поступающие на третий вход бл ка локальной памяти 3f коды микроопе раций в управляющие сигналы, которы поступают на управляющие входы коммутаторов, 37 и на вход синхронизации fl/вторых регистров 39 Коммутаторы 37 предназначены для передачи информации с первого входа или со второго входа 2, с выхода со ответствующего второго регистра 39 в соответствующий регистр 38 (при восстановлении информации) . Регистры 39 предназначены для хра нения информации и выдачи ее на вход соответствущих регистров 39 и на вы ход блока hi, Блок 2(3) локальной памяти функционирует следующим образом. По очередному коду микроопераций через соответствующий коммутатор 37 операнд со входа АО блока локальной памяти записывается в регистр ЗВ и хранится в нем или передается затем в операционный блок. Таким we образом осуществляется запись, хранение и выдача информации в операционный блок при обработке информации, поступающей на вход k2 блока локальной памяти или с выхода соответствующего регистра 39. Если информация является результатом выполнения программы в -j -;й контрольной точке и ее необходимо хранить до получения результата выполнения программы вС1+1)-й контрольной точке, то эта информация хранится в соответствующем регистре. 39- Сигнал .записи информации в контрольной точке поступает на вход синхронизации регистра 39, после чего информация с регистра 38 перезаписывается в регистр 39. Назначение основных функциональных элементов операционного блока (фиг.З) состоит в следующем. Кодопреобразователь, состоящий из дешифратора А и шифратора 5, преобразовыв.ает поступающие на вход 43 операционного блока коды микроопераций в коды управляющих сигналов, которыми управляются коммутатор 46 и блоки 50 и 51 элементов И. Коммутатор 46 предназначен для передачи информации, поступающей с выхода регистра 48 или с входа 49 на вход сумматора 47 в зависимости от кода микроопераций на управляющих входах о Сумматор 47 предназначен для обработки информации и выдачи ее в регистр 48, регистр 48 предназначен для пpЪмeжyтoчнoгo хранения информации. Блоки 50 и 51 элементов И предназначены для выдачи информации из операционного блока в локальную или основную память процессора. Операционный блок 4(5) функционирует следующим образом. По кодам микроопераций формируется код управляющих сигналов, по ко- . торому информация с входа 49 через коммутатор 46 поступает на вход сумматора 47. Далее по управляющим сигналам осуществляется подача информации С выхода регистра 48 на вход сумматора 47 и с его выхода на вход регистра . После окончания обработки, информации открываются блоки 50 или 51 элементов И и информация с выхода регистра kB поступает на первый 52 или второй 53 выходы операционного блока.

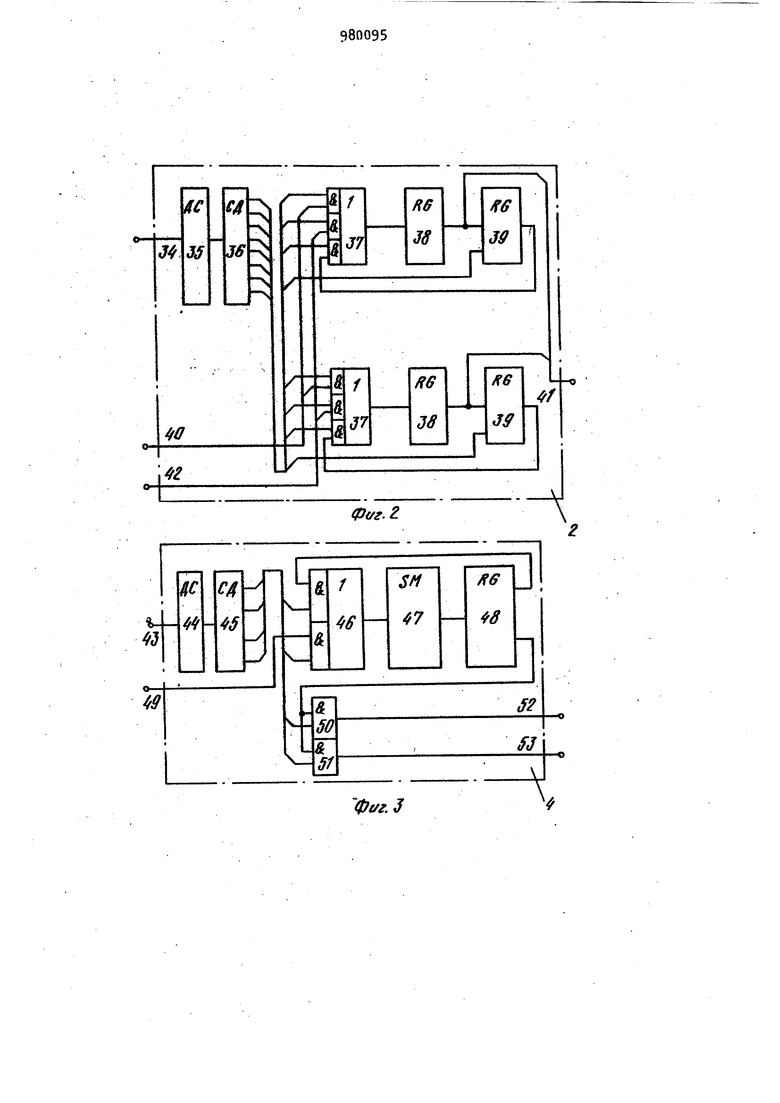

Назначение основных функциональных элементов блока основной памяти (Лиг. состоит в следующем.

Регистр 55 предназначен для приема обработанной информации с входа и последующей ее записи в накопитель 5б

Накопитель 56 предназначен для хранения данных и команд. Первый 59 и второй 62 элементы И по сигналам микроопераций, поступающим на вход 58 формируют сигналы записи и считывания , по которым осуществляется запись в накопитель 5б содержимого регистра 55 и считывание очередной команды по адресу, поступающему на вход 57

Накопитель 6 предназначен для хранения адресов первых микрокоманд эквивалентных заменяющих последовательностей микрокоманд. Элемент И 63 предназначен для формирования сигнала считывания информации по адресу, который поступает на четвертый вход 65.

Блок основной памяти функционирует в трех режимах.

1.Режим записи информации, поступаюи4ей на вход S Информация с первого 4 или второго 5 операционного блока поступает на вход блока 6 основной памяти и записывается в регистр 55.

Код микроопераций открывает элемент И 59 Импульсы записи через элемент И 59 поступают на вход накопителя 5б и записывают в него содержимое регистра 55

2,Режим считывания следующей команды.

Код микроопераций считывания поступает на вход элемента И 62. Импуль сы считывания через элемент И 62 поступают на вход накопителя 56 и по адресу, поступаюи ему на адресный вход 57 накопителя, производят считывание следующей команды и подают ее на первый выход 66,

3 Режим считывания адресов начальных микрокоманд эквивалентных заменяющих последовательностей микрокоманд. Код микроопераций считывания поступает на вход элемента И 63. Импульсы считывания через элемент И 63

поступают на вход второго накопителя б и по адресу, поступающему с входа 65 считывают на выход 67 адрес начальной микрокоманды эквивалентной последовательности отказавшей микрокоманды ,

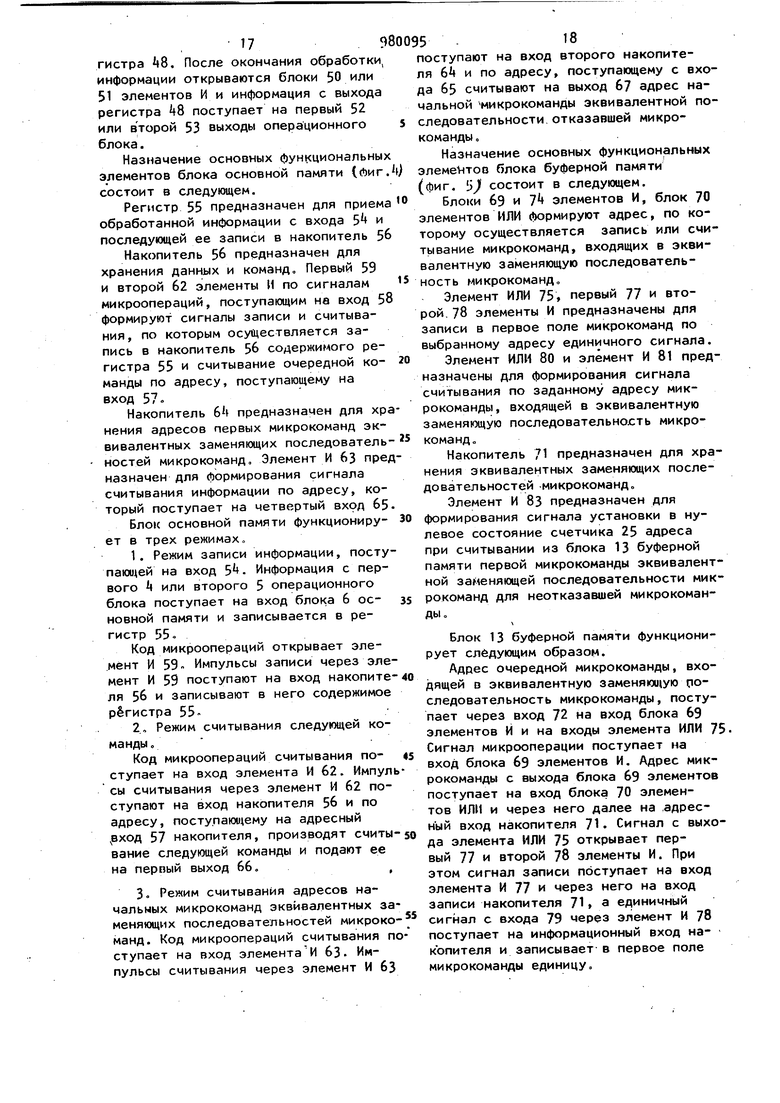

Назначение основных функциональных элеме |тов блока буферной памяти (фиг. j) состоит в следующем.

Блоки б9 и 7 элементов И, блок 70 элементов ИЛИ формируют адрес, по которому осуществляется запись или считывание микрокоманд, входящих в эквивалентную заменяющую последовательность микрокоманд.

Элемент ИЛИ 75 первый 77 и второй. 78 элементы И предназначены для записи в первое поле микрокоманд по выбранному адресу единичного сигнала.

Элемент ИЛИ 80 и элемент И 81 предназначены для формирования сигнала считывания по заданному адресу микрокоманды , входящей в эквивалентную заменяющую последовательность микрокоманд.

Накопитель 71 предназначен для хранения эквивалентных заменяющих последовательностей микрокоманд.

Элемент И 83 предназначен для формирования сигнала установки в нулевое состояние счетчика 25 адреса при считывании из блока 13 буферной памяти первой микрокоманды эквивалентной заменяющей последовательности микрокоманд для неотказавшей микрокомандыБлок 13 буферной памяти функционирует следующим образом.

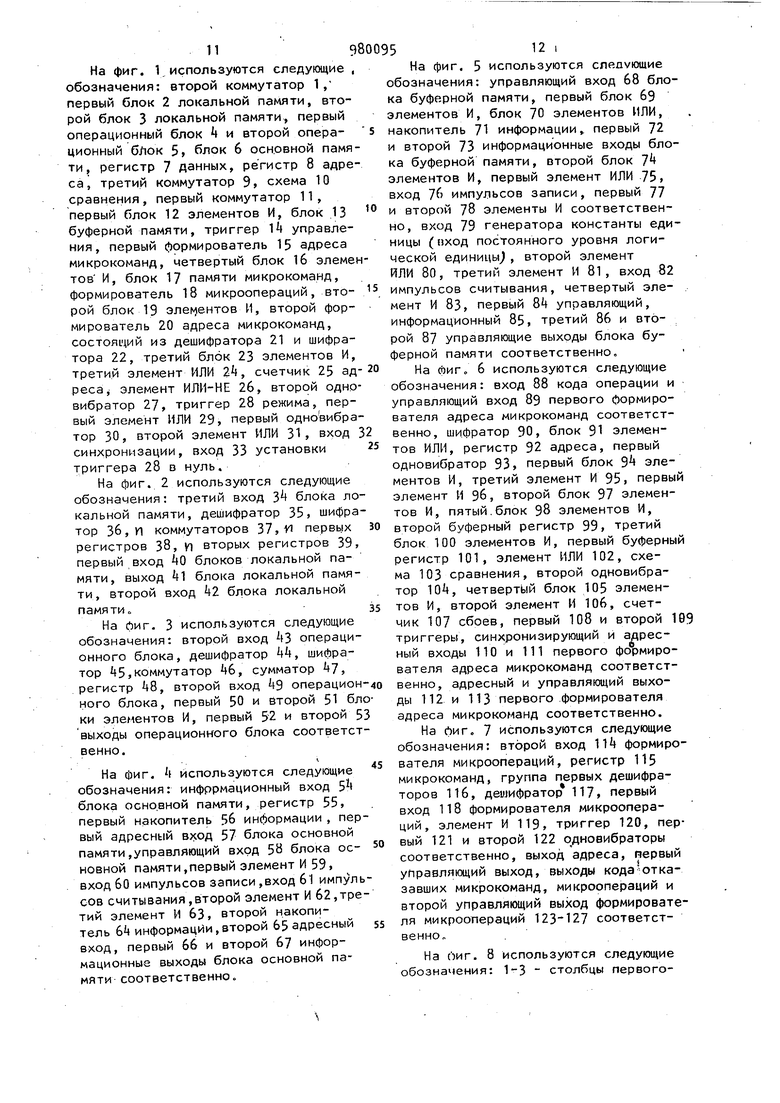

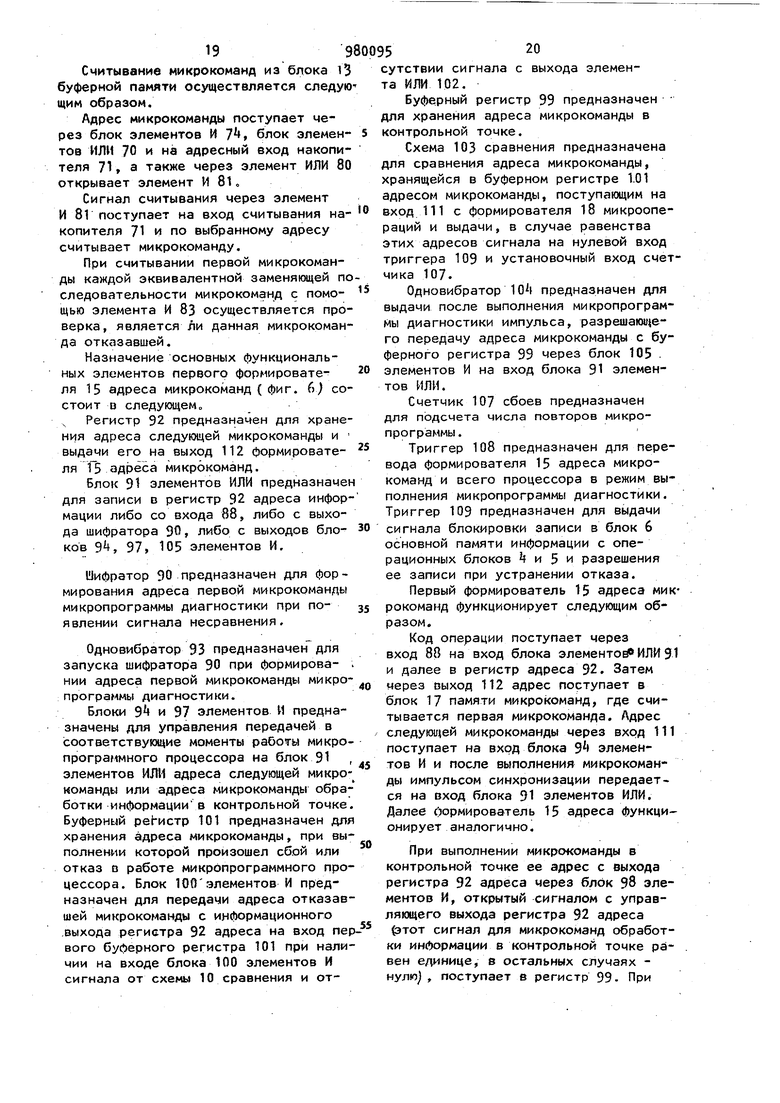

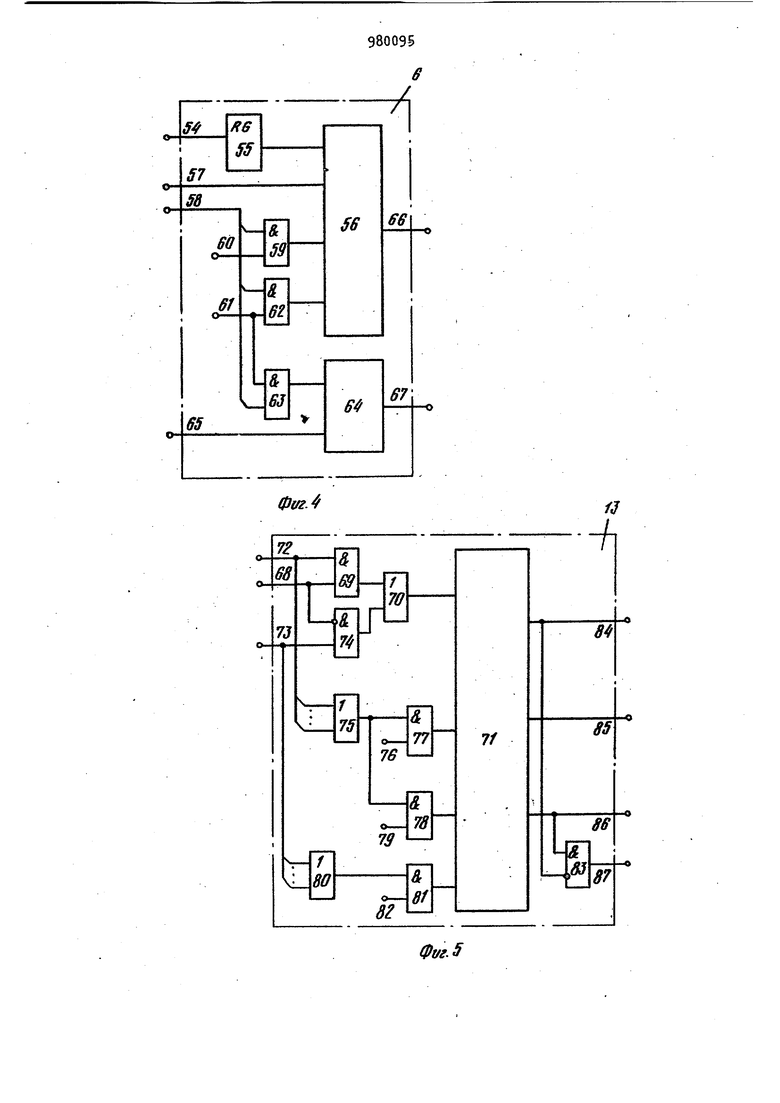

Адрес очередной микрокоманды, входящей в эквивалентную заменяющую последовательность микрокоманды, поступает через вход 72 на вход блока 69 элементов И и на входы элемента ИЛИ 75Сигнал микрооперации поступает на вход блока б9 элементов И. Адрес микрокоманды с выхода блока б9 элементов поступает на вход блока 70 элементов ИЛИ и через него далее на .адресный вход накопителя 71. Сигнал с выхода элемента ИЛИ 75 открывает первый 77 и второй 78 элементы И. При этом сигнал записи поступает на вход элемента И 77 и через него на вход записи накопителя 71 а единичный сигнал с входа 79 через элемент И 78 поступает на информационный вход накопителя и записывает в первое поле микрокоманды единицу. Считывание микрокоманд из блока i3 буферной памяти осуществляется следую щим образом. Адрес микрокоманды поступает через блок элементов И 7 блок элемен тов ИЛИ 70 и на адресный вход накопителя 71, а также через элемент ИЛИ 80 открывает элемент И 8K Сигнал считывания через элемент И 81 поступает на вход считывания накопителя 71 и по выбранному адресу считывает микрокоманду. При считывании первой микрокоманды каждой эквивалентной заменяющей по следовательности микрокоманд с помощью элемента И 83 осуществляется проверка, является ли данная микрокоманда отказавшей. Назначение основных функциональных элементов первого формирователя 15 адреса микрокоманд ( фиг. (у) состоит D следующемо Регистр 92 предназначен для хранения адреса следующей микрокоманды и выдачи его на выход 112 формирователя ТВ адреса микрокоманд. Блок 9t элементов ИЛИ предназначен для записи в регистр 92 адреса информации либо со входа 88, либо с выхода шифратора 90, либо с выходов блоков 9, 97, 105 элементов И. Шифратор 90 предназначен для формирования адреса первой микрокоманды микропрограммы диагностики при появлении сигнала несравнения. Одновибратор 93 предназначен для запуска шифратора 90 при формирова- . НИИ адреса первой микрокоманды микропрограммы диагностики. Блоки 9 и 97 элементов И предназначены для управления передачей в соответствующие моменты работы микропрограммного процессора на блок 91 элементов ИЛИ адреса следующей микрокоманды или адреса микрокоманды обработки информациив контрольной точке. Буферный 101 предназначен для хранения адреса микрокоманды, при выполнении которой произошел сбой или отказ в работе микропрограммного процессора. Блок 100элементов И предназначен для передачи адреса отказавшей микрокоманды с информационного .выхода регистра 92 адреса на вход пер вого буферного регистра 101 при наличии на входе блока 100 элементов И сигнала от схемы 10 сравнения и отсутствии сигнала с выхода элемента ИЛИ 102. Буферный регистр 99 предназначен для хранения адреса микрокоманды в контрольной точке. Схема 103 сравнения предназначена для сравнения адреса микрокоманды, хранящейся в буферном регистре 1.01 адресом микрокоманды, поступающим на вход 111 с формирователя 18 микроопераций и выдачи, в случае равенства этих адресов сигнала на нулевой вход триггера 109 и установочный вход счетчика 107. Одновибратор 10 предназначен для выдачи после выполнения микропрограммы диагностики импульса, разрешаюи его передачу адреса микрокоманды с буферного регистра 99 через блок 105 . элементов И на вход блока 91 элементов ИЛИ. Счетчик 107 сбоев предназначен для подсчета числа повторов микропрограммы . Триггер 108 предназначен для перевода формирователя 15 адреса микрокоманд и всего процессора в режим выполнения микропрограммы диагностики. Триггер 109 предназначен для выдачи сигнала блокировки записи в блок 6 основной памяти информации с операционных блоков и 5 и разрешения ее записи при устранении отказа. Первый формирователь 15 адреса микрокоманд функционирует следующим образом. Код операции поступает через вход 88 на вход блока элементовР ИЛИ 91 и далее в регистр адреса 92. Затем через выход 112 адрес поступает в блок 17 памяти микрокоманд, где считывается первая микрокоманда. Адрес следукйцей микрокоманды через вход 111 поступает на вход блока 9 элементов И и после выполнения микрокоманды импульсом синхронизации передается на вход блока 91 элементов ИЛИ. Далее формирователь 15 адреса функционирует аналогично. При выполнении микрокоманды в контрольной точке ее адрес с выхода регистра 92 адреса через блок 98 элементов И, открытый сигналом с управляющего выхода регистра 92 адреса тот сигнал для микрокоманд обработки информации в контрольной точке равен единице, в остальных случаях нулю), поступает в регистр 99. При

возникновении сбоя в работе микропрограммного процессора на входе 89 появляется сигнал со 10 сравнения . В этом случае адрес микрокоманды, при выполнении которой произошел s сбой, с выхода регистра 92 адреса через блок 100 элементов И открыт сигналом от схемы 10 сравнения, записывается в буферный регистр 101. , Блок 9 элементов И сигналом от схе- 10 мы 10 сравнения через элемент И 9б закрывается и адрес следующей микрокоманды на вход блока 91 элементов ИЛИ не передается. Одновременно сигнал от схемы 10 сравнения черезг 15 элемент И 96 открывает блок элементов И 97, через который адрес микрокоманды обработки информации в контрольной точке с буферного регистра 99 поступает на вход блока .элемен- 20 тов ИЛИ 91 и через элемент И 106 записывает единицу в счетчик 107- Этим сигналом устанавливается в единичное состояние триггер 109.

Микропрограмма начинает выполнять- 25 ся повторно с контрольной точки по алгоритму, описанному выше. Если адрес следующей микрокоманды и адрес микрокоманды, при выполнении которой произо1 ел сбой совпадают и на управ- зо ляющем входе схемы 103 сравнения отсутствует сигнал сбоя с входа 89, сигнал со схемы 103 сравнения обнуляет сметчик 107 и триггер 109 и выполнение микропрограммы продолжается, jj Если при выполнении очередной микрокоманды , адрес которой расположен между адресами микрокоманды в контрольной точке и микрокоманды, при выполнении которой произошел сбой, поступает сигнал сбоя от схемы 10 сравнения, то этот сигнал увеличивает содержимое счетчика 107 на единицу и в регистр адреса 92 снова запишется адрес микрокоманды в контроль- .. ной точке и обработка информации продолжается , как и после возникновения первого сбоя.

Если число сбоев превысит критическое, то счетчик 107 переполнится 50 и выходным сигналом установит 6 единичное состояние триггер 108, сигнал с единичного выхода которого закроет элементы И 9б и 106, откроет элемент И 95 и запустит одновибратор 96. 55 Выходной сигнал одновибратора 93 запускает шифратор 90, закрывая при этом блок 9 элементов И. С выхода

шифратора 90 «од адреса первой микрокоманды микропрограммы диагностики поступает через блок 91 элементов ИЛИ на регистр 92 адреса. Далее выполняется микропрюграмма диагностики с целью определения отказавших микрокоманд. Сигналы, поступающие со схемы 10 сравнн 1Я на второй вход 89 мерез элемент И 95 на вход блока 91 элементов ИЛИ модифицируют адрес следующей микрокоманды .

После выполнения микропрограммы диагностики сигналом, поступающим на вход 111, происходит установка в нулевое состояние триггера 108. При этом запускается одновибратор 10, выходной сигнал которого открывает 1блок 105 элементов И и адоес ми1фокоманды обработки информации в контрольной точке из буферного регистра 99 через блок 10 элементов И поступает на ёлок 91 элементов ИЛИ. Далее формирователь адреса микрокоманд работает в режиме обработки информации после восстановления отказа. Алгоритм работы в этом режиме аналогичен алгоритму работы до возникновения отказа в микропрограммном процессоре.

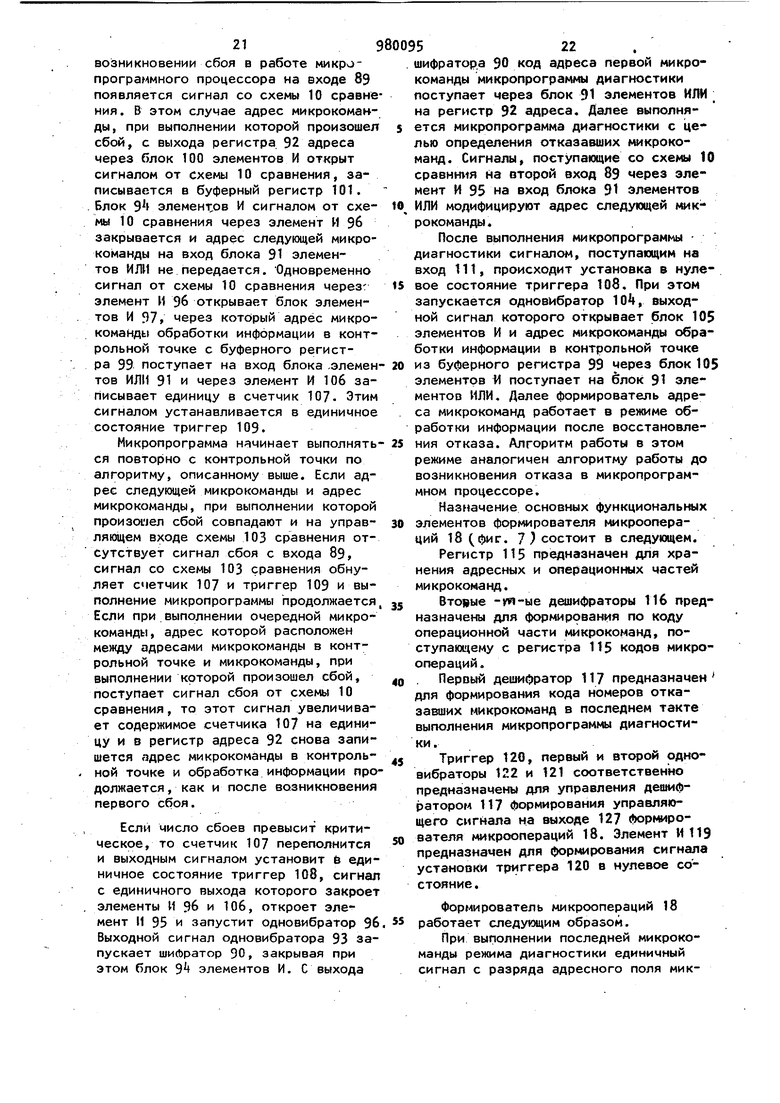

Назначение основных фyнкциoнaль « lx элементов формирователя микроопераций 18 (фиг. 7 ) состоит в следующем.

Регистр 115 предназначен для хранения адресных и операционных частей микрокоманд.

Втовые -уя-ые дешифраторы 116 предназначены для формирования по коду операционной части микрокоманд, поступаю11ему с ркегистра 115 кодов микроопераций .

Первый дешифратор 117 предназначен для формирования кода номеров отказавших микрокоманд в последнем такте выполнения микропрограмм диагностики.

Триггер 120, первый и второй одновибраторы 122 и 121 соответственно предназначены для управления дешифратором 117 формирования управляющего сигнала на выходе 127 формирователя микроопераций 18. Элемент И 119 предназначен для формирования сигнала установки триггера 120 в нулевое состояние ,

Формирователь микроопераций 18 работает следующим образом.

При выполнении последней микрокоманды режима диагностики единичный сигнал с разряда адресного поля микрокоманды о остальных микрокомандах храня1чихся Q блоке памяти микрокоманд 17 в этом поле записан нуль с регистра 115 поступает на выход 123 формирователя микроопераций 18, устанавливает в единичное состояние триггер 120 и открывает элемент И 1-19. Сигнал с единичного выхода триггера 120 запускает одновибратор 121, выходной сигнал которого открывает первый дешифратор 117. Код номеров отказавших микрокоманд с выхода регистра 115 через дешифратор 117 поступает на выход 125 формирователя микроопераций 18. После выборки и маскирования начального адреса эквивалентной заменяющей последовательности микрокоманд на вход 118 с выхода блока основной памяти 6 поступает управляющий сигнал При этом обнуляется триггер 120 и выходной сигнал одновибратора 129 через выход 127 устанавливает в единичное состояние триггер 28. Процессор работает бледующим образом. При выполнении программы команды считываются из блока 6 основной памяти в регистр 7 данных. Код операции с выхода регистра 7 данных поступаёт на вход формирователя 15 адреса микрокоманд. По выработанному в этом узле адресу из блока 17 памяти микрокоманд считывается первая микрс:),команда. При выполнении микропрограммы обработки опе(ндов формирователь 18 микроопераций вырабатывает управляющие воздействия, по которым операнды записываются одновременно в первый 2 и второй 3 блоки локальной памяти. Если в процессоре отсутствуют неисправности, то в каждый данный-момент времени первый. 2 и второй 3 блоки локальной памяти хранят одинаковую информацию. I В ходе обработки операнды поступа ют из первого 2 и второго 3 блоков ло кальной паМяти в первый Ч и второй 5 операционные блоки параллельно и независимо, причем для этих блоков формирователем микроопераций 18 зйдается выполнение одинаковых операций Результат обработки в зависимос ти от выполняемой команды записывает ся либо в первый 2 и второй 3 блоки локальной памяти, либо в блок 6 основной памяти через коммутатор 11 блок элементов И 12. Таким образом, первым Ч и вторым 5 операционными блоками осуществляется параллельная обработка данных. В зависимости от сигнала, поступающего с выхода формирователя микроопераций 18 через коммутатор 11 разрешается прохождение информации либо с первого k, либо со второго 5 операционных блоков в блок 6 основной памяти. Схема 10 сравнения сравнивает результаты обработки данных в операционных блоках; при совпадении результатов вычисления продолжаются Если в первом k или втором 5 операционных блоках или в первом 2 или втором 3 блоКах локальной памяти происходит отказ или сбой, схема сравнения 10 обнаружит их из-за расхождения в результатах обработки и сформирует выходной сигнал, который переводит микропрограммный процессор в режим отработки сбоя. При этом в формирователе адреса микрокоманд 15 формируется адрес микрокоманды обработки информации в контрольной точке. Адрес микрокоманды,при выполнении которой обнаружен отказ, запоминается в первом формирователе адреса микрокоманд 15 и с его выхода на вход блоэлементов И 12 подается сигнал блокакировки записи информации в блок 6 основной памяти. Происходит повторная обработка Информации, начиная с ближайшей контрольной точки , информация о которой хранится в первом 2 и втором 3 блоках локальной памяти. Если в ходе и после выполнения микрокоманд, следующих после микрокоманды обработки информации в контрольной точке, перед микрокомандой, при выполнении которой произошел сбой, а также выполнении этой микрокоманды сигнал с выхода схемы сравнения 10 не поступает, то сигнал блокировки блока 12 элементов И снимается и микро- программа выполняется дальше о В противном случае, при возникновении сбоя снова осуществляется возврат к выполнению микрокоманды обработки информации в контрольной точке. Если после определенного количестве повторов сбой не исчезает, то сигнал несравнения с выхода схемы 10 сравнения формирует адрес первой микрокоманды микропрограммы диагностики отказавших микрокоманд. Определение номеров отказавших микрокоманд осуществляется диагностимеским тестом, которому передает управление микропрограмма диагностики отказавших микрокоманд. Диагностичес кий тест выполняется путем передачи тестовой информации в первый 2 и вто рой 3 блоки локальной памяти, в первый k и второй 5 операционные блоки, Сигнал рассогласования с выхода схем сравнения 10 модифицирует адреса мик рокоманд микропрограммы диагностики отказавших микрокоманд. На последнем такте выполнения мик ропрограммы диагностики формирователь 18 микроопераций-выдает на четвертый вход блока 6 основной памяти код номера отказавшей микрокоманды. Адрес начальной микрокоманды по сигналам микроопераций с выхода формирователя 18 считывается в блок 13 бу ферной памяти, где по нему маскирует ся эквивалентная заменяющая последовательность микрокоманд. Процесс мас кирования эквивалентных заменяющих последовательностей микрокоманд,хранимых в блоке 13 буферной памяти, состоит в маскировании первых микрокоманд последовательностей соответствую щим микрокоДандам (фиг. 8). Так, если произошел отказ микрокоманды , которой соответствует эквивалентная заменяющая последовательность , то в первом поле начальной микрокоманды последовательности записывается единичная метка. Эта метка в дальнейшем является логическим условием пере хода к выполнению последовательности микрокоманд Э вместо выполнения отказавшей микрокоманды А. По окончанию формирования последовательностей сигнал с выхода блока 6 основной памяти, воздействуя на формирователь микроопераций 18, разрешает выполнение микропрограммы обработки команды, начиная с микрокоманды обработки информации в контрольной точке, адрес которой хранится в формирователе 15 адреса микрокоманд. По операционной части текущей микрокоманды, подаваемой с выхода формирователя 18 микроопераций через otкpытtlй триггером 28 блок 19 элементов И, формирователь 20 адреса через блок 23 элементов И записывает в счет чик 25 адреса адрес первой микрокоманды эквивалентной заменяющей последовательности микрокоманд. Одновременно, через элемент ИЛИ 29 возбух дается одновибратор 30,, выходНОЙ сигнал которого через элемент ИЛИ 31 поступает на упраоляющие входы коммутаторов 1 и запрещает прохождение сигналов микроопераций с выхода формирователя 18 микроопераций. По адресу, записанному в счетчике 25 адреса, осуществляется считывание первой микрокоманды эквивалентной заменяющей последовательности микрокоманд и анализ выполняемой микрокомандыЕсли при считывании первой микрокоманды эквивалентной заменяющей последовательности в первом поле ее записан нуль, то триггер 1 свое состояние не изменяет, счетчик 25 адреса сигналом с выхода блока 13 буферной памяти через третий элемент ИЛИ 2 обнуляется и после окончания сигнала на выходе одновибратора микроопераций с выхода формирователя микроопераций 18 через коммутаторы 1 и 9 поступает в блоки 2 и 3 локальной памяти и операционные блоки и 5. Сигнал с выхода счетчика 25 адреса через элемент ИЛИ-НЕ 26 открывает блок элементов И 1б и с блока 17 памяти микрокоманд считывается следующая микрокоманда Ее выполнение осуществляется по описанному алгоритму. Если очередная микрокоманда является отказавшей, то реализуется следующий алгоритм. Микрокоманда с выхода формирователя 18 микроопераций через открытый сигналом от триггера 28 блок 19 элементов И поступает на формирователь 20 адреса микрокоманд и через элемент ИЛИ 29 запусккает одно вибратор 30, который через элемент ИЛИ 31 подает сигнал на управляющие входы коммутаторов 1 и 9, и код микроопераций с выхода формирователя микроопераций 18 через них не проходит. Адрес первой микрокоманды эквивалентной заменяющей последовательности микрокоманд, сформированный формирователем 20 адреса микрокоманд через блок элементов И 23, открытый сигналом с нулевого выхода триггера И, поступает в счетчик 25 адреса. По ЭТОМУ адресу счетчик 25 адреса считывает из блока 13 буферной памяти .первую микрокоманду эквивалентной заменяющей последовательности микрокоманд , о . (.фиг.8, Единичный сигнал, с первого поля микрокоманды устанавливает в единичное состояние триггер I. Сигнал с единичного выхода триггера lA через элемент ИЛИ 31 -поступает на ком мутаторы 1 и 9 и код микроопераций с выхода блока 13 буферной памяти поступает в блоки локальной памяти 2 и 3 и операционные блоки k и 5. Сигнал с Tpetbero поля микрокоманды из блока 13 буферной памяти поступает на счетный вход счетчика 25 адреса и увеличивает его содер жимое на единицу, формируя таким образом адрес следующей микрокоманды эквивалентной заменяющей последовательности. Так как счетчик 25 адреса находится не в нулевом состоянии, то сигнал на выходе элемента ИЛИ-НЕ 26 отсутствует, запрещая при этом считы вание из блока 1.7 памяти микрокоманд следующей микрокоманды„ Счетчик 25 адреса по новому адресу считывает следующую микрокоманду, входящую в . эквивалентную заменяющую последовательность микрокоманд, с блока 13 бу ферной памяти„ Выполнение ее осущест вляется аналогично выполнению первой микрокоманды. При считывании с блока 13 буферной памяти последней микрокоманды эквивалентной заменяюще последовательности сигнал на выходе блока 13 буферной памяти с третьего поля микрокоманды (с )иг„ 8) отсутству ет. При этом возбуждается одновибратор 27 и через элемент ИЛИ 2k обнуля ет триггер и счетчик 25 адреса. На выходе элемента ИЛИ-НЕ 2б при это появляется сигнал, разрешающий прохождение адреса следующей микрокоман ды с (йормир 5вателя 15 адреса микроко манд через блок 16 элементов И, По этому адресу с блока 17 памяти микро команд считывается и выполняется следующая микрокоманда по алгоритму, описанному выше„ Если при выполнении микрокоманды, входящей в эквивалентную заменяющую последовательность микрокоманд, произойдет сбой при обработке данных, то сигнал с выхода схемы 10 сравнения через элемент ИЛИ 2k обнулит счетчик 25 адреса и триггер It и про цессор перейдет в режим обработки сбоя, который описан выше„ Если произошел отказ, то запускается микропрограмма диагностики , определяются номера отказавших микрокоманд, форми руются для них эквивалентные за меняющие .последовательности микрокомаид и программа выполняется дальше. Таким образом, в процессоре осуществляется обработка информации при наличии двух и более отказов в различных каналах. При этом даже в условиях отказов осуществляется паритетный контроль обрабатываемой информации. Следовательно, данный микропрограммный процессор превосходит прототип по отказоустойчивости и достоBepHoctM функционирования. Использование процессора позволит строить вычислительные и управляющие системы, предназначенные для длительного использования в условиях отсутствия технического обслуживания, Оормула изобретения Микропрограммный процессор, содержащий блок основной памяти, регистр адреса, регистр данных, блок буферной памяти, первый и второй блоки локальной памяти, первый и второй операционные блоки, первый коммутатор, первый блок элементов И, схему сравнения, первый формирователь адреса микрокоманд триггер управления, блок памяти микрокоманд и формирователь микроопераций, причем первый информационный выход блока основной памяти соединен с входом регистра данных, первый выход которого соединен с первыми входами первого и второго блоков локальной памяти, второй выход регистра данных соединен с входом кода операции первого формирователя микрокоманд, управляющий выход которого соединен с инверсными входами первого блока элементов И, третий выход регистра данных соединен с входом регистра адреса, выход которого соединен с первым адресным входом блока основной памяти, второй информационный выход блока основной памяти соединен с первым информационным входом блока буферной памяти и первым входом формирователя микроопераций, выход микроопераций которого соединен с управляющим входом блока основной памяти и управляющим входом блока буферной памяти, выход первого коммутатора соединен с входом первого блока элементов И, выход которого соединен с инЛормационным входом блока основной памяти, выход блока памяти микрокоманд соединен со вторым входом формирователя микроопераций, адресный выход которого соединен с адресным 299 входом первого формирователя адреса микрокоманд, выход первого операционного блока соединен с первым информационным входом первого коммутатора и первым входом схемы сравнения, выхо которой соединен с управляющим входом формирователя адреса Микрокоманд выход второго операционного блока соединен со вторым входом схемы сравнения и вторым информационным входом первого коммутатора, прямой и инверсныи управляющие входы которого со единены с первым управляющим выходом формирователя микроопераций, второй выход первого операционного блока соединен со вторым входом первого блока локальной памяти,выход которого соединен с первым информационным входом первого операционного блока, второй выход второго операционного блока соединен со вторым входом второго блока локальной памяти, выход которого соединен с первым информационным входом второго операционного блока, вход синхронизации формирователя адреса микрокоманд соединен с входом тактовых импульсов устройства, о т личающийся тем, что, с целью повышения отказоустойчивости и достоверности функционирования микропрограммного процессора, в него введе ны второй и третий коммутаторы, второй , третий и четвертый блоки элементов И, триггер режима, второй формирователь адреса микрокоманд, счетчик адреса, первый, второй и третий элементы ИЛИ, первый и второй одновиб раторы, элемент ИЛИ-НЕ, причем информационный выход блока буферной памяти соединен с первыми информационными входами второго и третьего коммута торов, выход которого соединен со вторыми входами первого и второго операционных блоков, выход микроопераций формирователя микроопераций соединен со вторыми информационными входами третьего и второго коммутаторов, выход которого соединен с третьими входами первого и второго блоков локальной памя™, выход первого элемента ИЛИ соединен с входом первого одновибратора, выход которого соединен с первым входом второго элемента ИЛИ, единичный выход триггера управления соединен со вторым входом второго элемента ИЛИ, выход которого соединен с прямыми и инверсными уп-. равляющимИ входами второго и третье9530го коммутаторов, второи управляющий выход формирователя микроопераций соединен с единичным входом триггера режима, единичный выход которого соединен с первым входом второго блока элементов И, выход микроопераций формирователя микроопераций соединен со вторым входом второго блока элементов И, выход которого соединен с входами первого элемента ИЛИ и входами второго формирователя адреса микрокоманд, выход второго формирователя адреса микрокоманд соединен с первым входом третьего блока элементов И, выход которого соединен с информационными входами счптчика адреса, первый управляющий выход блока буферной памяти соединен с единичным входом tpиггepa управления, нулевой выход которого соединен со вторым входом третьего блока элементов И, второй управляющий выход блока буферной памяти соединен с первым входом третьего элемента ИЛИ, выход которого соединен с установочным входом сметчика адреса и нулевым входом триггера управления, третий управляющий выход блока буферной памятм соединен с входом второго одновобратора И счетным входом счетчика адреса. выходы которого соединены со вторым информационным входом блока буферной памяти и входами элемента ИЛИ-НЕ, адресный выход первого, формирователя адреса микрокоманд и выход элемента ИЛИ-НЕ соединены соответственно с первым и вторым входами четвертого блока элементов И, выход которого соединен с входом блока памяти микрокоманд, выход кода отказавших микрокоманд формирователя микроопераций соединен со вторым адресным входом блока основной памяти, выход схемы сравнения и выход второго одновибратора соединены соответственно со вторым и третьим входами третьего элемента ИЛИ, установочный вход устройства соединен с нулевым входом триггеру режима , . Источники информации , принятые во внимание при экспертизе 1.Авторское свидетельство СССР fp , кл. G 06 F 15/ПО, 1977. 2.Методы автоматического возврата в вычислительной машине COPRA. Экс3198009532

пресс информация. Сер. вычислитель- U. Патент Великобритании Г 141j095, ная техника, К 20, 1978.кл. fi Ц Л, опублик. 1978,

3. Патент США Р , 763902, кл. G Об F 15/00, 1980

кл. 235-153 ЛЕ, опублик. 1978. 5 (прототип)«

5. Авторское свидетельство СССР

ф{/г.г

Ф1КЛ

Л7

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100625A1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

| Адаптивный модуль микропрограммного устройства управления | 1984 |

|

SU1273926A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Микропрограммный процессор с контролем | 1981 |

|

SU985791A1 |

Фиг. 5

Iff

L

фиг. 6

фуг. 7

фуг, 8

Авторы

Даты

1982-12-07—Публикация

1981-06-18—Подача