1

Изобретение относится к вычислительной технике.

Известно устройство для фиксации, анализа и исправления сбоев, содержащее блок контроля, блок прерывания, блок переключения, блок индикации, г элементы И и элементы ИЛИ, триггеры, в котором после обнаружения сбоя при выполнении программы происходит повторное выполнение участка программы от точки, начальный адрес которой хранится в определенной области МОЗУ l .

Недостатком этого устройства является то, что оно не позволяет ликвидировать последствия целого ряда сбоев. Например, если команда испортилась при хранении в МОЗУ и при считывании ее перед выполнением произошел сбой по четности, тогда любое количество повторений выполнения Части программы, включающей данную команду, не приведет к нормальному продолжению вычислительного процесса без вмешательства оператора или снятия данной программы контрольными программными средствами. Или, например, аналогичная ситуация возникает, когда адресована несуществующая ячейка памяти по вине программиста. В ряде случаев сбой может привести к порче системных таблиц и данных или ошибочно установить уровень прерывания внешнего устройства. Тогда только с помощью человека-оператора, который произведет установку процессора в рабочее состояние и восстановление операционной системы в МОЗУ, можно продолжить вычислительный процесс,

10 что не приемлемо в оперативном режиме управления.

Наиболее близким к предложенному является устройство для контроля процессора, которое содержит пульт уп15равления, блок сопряжения с пультом, первый выход которого подключен к первому входу блока прерываний микропрограммы, выход блока прерываний микропрограммы подключен к входу па20мяти микропрограмм, соединенной своим выходом с первым входом блока операций, второй вход которого подключен ко ко второму выходу блока сопряжения с пультом, третий выход которого со25единен с первым входом блока прерываний программы, который имеет тридцать два входа (по числу прерываний), второй вход блока прерываний программы является одним из свободных входов 30 незадействованного прерывания и предназначен для подключения какого-либо внешнего элемента, первый выход блока прерываний программы соединен с третьим входом блока операций, первый выход которого подключен к пятому входу блока сопряжения с пультом, а второй выход - к входу формирователя сигнала ошибки, выход которого соединен со вторым входом блока прерываний микропрограммы, третий вход которого подключен ко второму выходу блока прерываний программы 2 Однако для восстановления работоспособности процессора после сбоя и для обеспечения продолжения функционирования требуется вмешательство человека-оператора, а это влечет за собой потери машинного времени, особенно недопустимые при управлении в режиме реального времени.

Цель изобретения - повышение быстродействия.

Для достижения поставленной цели в устройство для контроля процессора, содержащее блок прерывания микропрограммы, формирователь, сигнала ошибки, операционный блок, блок пре рываний программы, память микропрограмм, блок сопряжения с пультом и пульт управления, при этом первый управляющий выход блока сопряжения с пультом соединен с первым входом блока прерывания микропрограммы, выход которого подключен к памяти микропрограмм, выход которой соединен с первым входом операционного блока, первый выход которого соединен с первым входом блока сопряжения с пультом, информационный выхбд которого соединен со вторым входом операционного блока, второй выход которого подключен ко входу формирователя сигнала ошибки, выход которого соединен со вторым входом блока прерываний микропрограммы, третий вход которого соединен с первым выходом блока прерываний программы, второй выход которого соединен с третьим входом операционного блока, первый вход блока прерываний программы подключен к второму управляющему выходу блока сопряжения с пультом, введены блок фиксации отказа, распределитель импульсов, элемент задержки и элементы ИЛИ, при этом выход формирователя сигнала ошибки соединен со входом элемента задержки и входом блока фиксации отказа, вых4л которого является выходом устройства, выход элемента задержки подключен ко входу распределителя импульсов, первый выход которого подключен ко второму входу блока прерываний программы, группа выходов распределителя импульсов подключена к первому входу соответствующего элемента ИЛИ, второй вход каждого элемента ИЛИ подключен к группе выходов пульта управления, группа выходов элементов ИЛИ подключена к группе входов блока сопряжения с пультом.

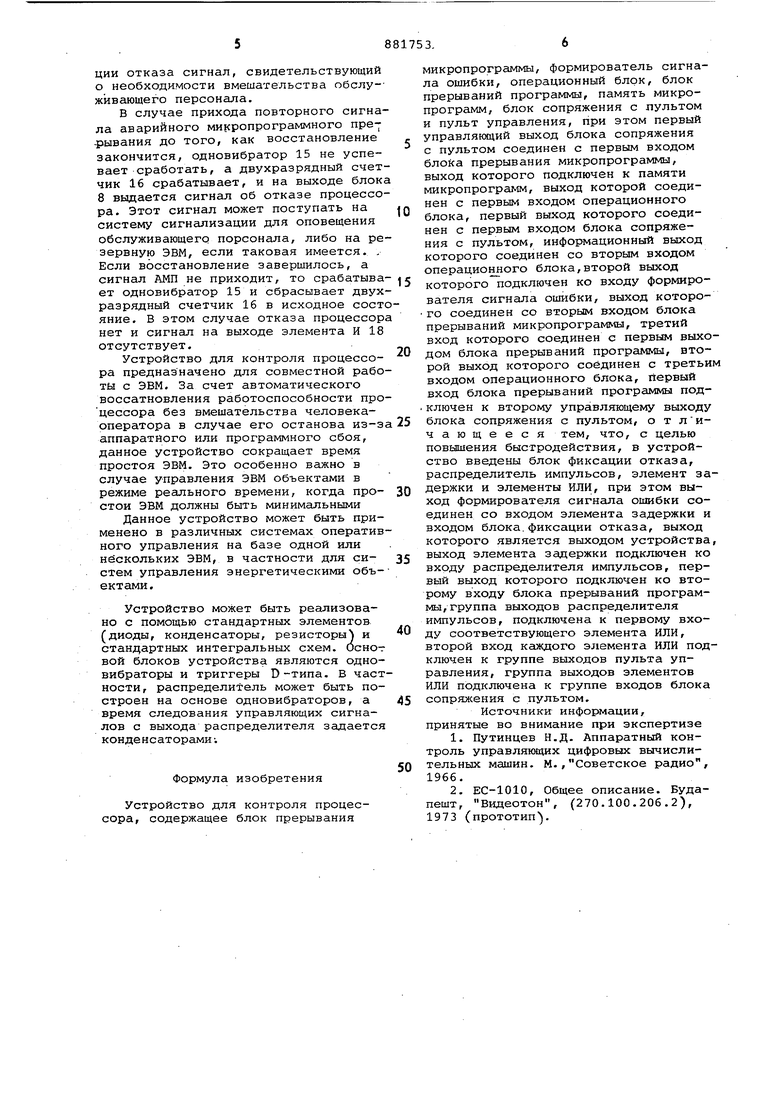

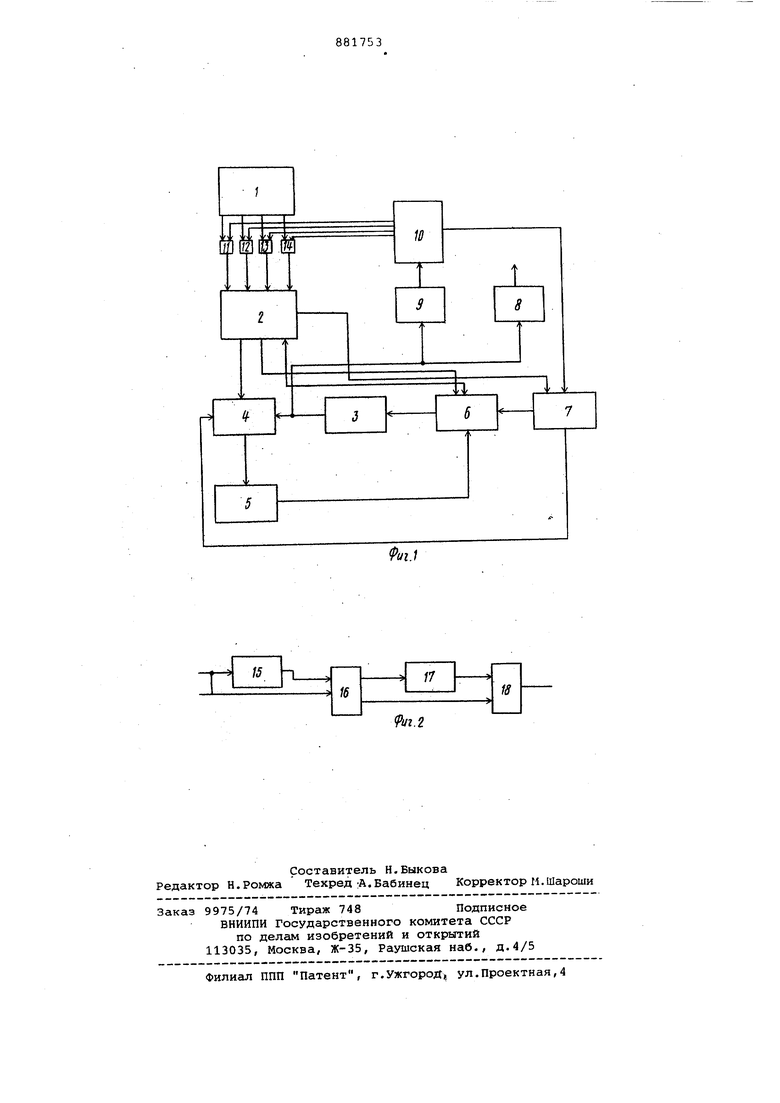

На фиг.1 представлена структурная схема предлагаемого устройства, на фиг.2 - структурная схема блока фиксации отказа.

Устройство содержит пульт 1 управления, блок 2 сопряжения с пультом, формирователь 3 сигнала ошибки, блок 4 прерываний микропрограммы, память 5 микропрограмм, операционный блок 6, блок 7 прерываний программы, блок 8 фиксации отказа, имеющий один вход и один выход , элемент 9 задержки, имеющий один вход и один выход, распределитель 10 импульсов, имеющий один вход и пять выходов, четыре логических элемента ИЛИ 11-14. Блок 8 фиксации отказа содержит одновибрато 15, двухразрядный счетчик 16, инвертор 17, элемент И 18.

Устройство работает следующим образом.

. В случае аппаратного или программного сбоя, который приводит к останову вычислительного процесса и зависанию системы, формирователь 3 сигнала ошибки вырабатывает сигнал аварийного микропрограммного прерывания, который поступает на второй вход блока 4 прерываний микропрограммы и запускает микропрограмму обработки аварийного микропрограммного прерывания, хранящуюся в памяти 5 микропрограмм. Кроме того, сигнал с выхода формирователя 3 сигнала ошибки поступает на вход элемента 9 задержки и на вход блока 8 фиксации отказа изапускает их. Элемент,9 задержки срабатывает, когда закончится действие микропрограммы обработки АМП и выдает сигнал на вход распределителя 10 импульсов, который вырабатывает серию из пяти последовательных сигналов. Четыре сигнала имитируют сигналы пульта: останов, сброс, инициация, пуск. Эти сигналы через элементы 11-14 ИЛИ подаются на входы блока 2 сопряжения с пультом. При этом процессор устанавливается в исходное состояние и происходит перезагрузка операционной системы в оперативную память из внешнего запоминающего устройства. Эти действия аналогичны действиям при манипуляции человека-оператора с пульта.

Пятый сигнал с распределителя 10 импульсов выдается с пятого выхода и поступает на второй вход блока 7 прерываний программы, вызывая прерывание. По данному прерыванию вызывается управляющая программа обработки сбоев, которая обеспечивает продолжение выполнения задачи. При случайном сбое предлагаемое устройство автоматически ликвидирует его последствия, а в случае отказа процессора устройство выдает с выхода блока 8 фиксации отказа сигнал, свидетельствующий о необходимости вмешательства обслуживающего персонала. В случае прихода повторного сигна ла аварийного микропрограммного пре-;-рывания до того, как восстановление закончится, одновибратор 15 не успевает сработать, а двухразрядный счет чик 16 срабатывает, и на выходе блок 8 вьвдается сигнал об отказе процессо ра. Этот сигнал может поступать на систему сигнализации для оповещения обслуживающего порсонала, либо на ре зервную ЭВМ, если таковая имеется. . Если восстановление завершилось, а сигнал АМП не приходит, то срабатыва ет одновибратор 15 и сбрасывает двух разрядный счетчик 16 в исходное сост яние. В этом случае отказа процессор нет и сигнал на выходе элемента И 18 отсутствует. Устройство для контроля процессора предназначено для совместной рабо ты с ЭВМ. За счет автоматического воссатновления работоспособности про цессора без вмешательства человекаоператора в случае его останова из-з аппаратного или программного сбоя, данное устройство сокращает время простоя ЭВМ. Это особенно важно в случае управления ЭВМ объектами в режиме реального времени, когда простой ЭВМ должны быть минимальными Данное устройство может быть применено в различных системах оператив ного управления на базе одной или нескольких ЭВМ, в частности для систем управления энергетическими объектами. Устройство может быть реализовано с помощью стандартных элементов (диоды, конденсаторы, резисторы ) и стандартных интегральных схем. Основой блоков устройства являются одновибраторы и триггеры D-типа. В част ности, распределитель может быть построен на основе одновибраторов, а время следования управляющих сигналов с выхода распределителя задается конденсаторами-. Формула изобретения Устройство для контроля процессора, содержащее блок прерывания микропрограммы, формирователь сигнала ошибки, операционный блок, блок прерываний программы, память микропрограмм, блок сопряжения с лультом и пульт управления, при этом первый управляющий выход блока сопряжения с пультом соединен с первым входом блока прерывания микропрограммы, выход которого подключен к памяти микропрограмм, выход которой соединен с первым входом операционного блока, первый выход которого соединен с первым входом блока сопряжения с пультом, информационный выход которого соединен со вторым входом операционного блока,второй выход которого подключен ко входу формирователя сигнала ошибки, выход которого соединен со вторым входом блока прерываний микропрограммы, третий вход которого соединен с первым выходом блока прерываний программы, второй выход которого соединен с третьим входом операционного блока, первый вход блока прерываний программы подключен к второму управляющему выходу блока сопряжения с пультом, о т личающееся тем, что, с целью повышения быстродействия, в устройство введены блок фиксации отказа, распределитель импульсов, элемент задержки и элементы ИЛИ, при этом выход формирователя сигнала ошибки соединен со входом элемента задержки и входом блока.фиксации отказа, выход которого является выходом устройства, выход элемента задержки подключен ко входу распределителя импульсов, первый выход которого подключен ко второму входу блока прерываний программы, группа выходов распределителя импульсов, подключена к первому входу соответствующего элемента ИЛИ, второй вход каждого элемента ИЛИ подключен к группе выходов пульта управления, группа выходов элементов ИЛИ подключена к группе входов блока сопряжения с пультом. Источники информации, принятые во внимание при экспертизе 1.Путинцев Н.Д. Аппаратный контроль управляющих цифровых вычислительных машин. М.,Советское радио, 1966. 2.ЕС-1010, Общее описание. Будапешт, Видеотон, (270.100.206.2), 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для перезапуска процессора при сбое | 1984 |

|

SU1262499A1 |

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Устройство для диагностики ошибок ЭВМ | 1980 |

|

SU1012260A1 |

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

| Двухканальное устройство для контроля и восстановления процессорных систем | 1986 |

|

SU1397917A1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1984 |

|

SU1180911A1 |

| Устройство для контроля вычислительного процесса ЭВМ | 1988 |

|

SU1596332A1 |

| Устройство для перезапуска ЭВМ | 1984 |

|

SU1205146A1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1982 |

|

SU1132282A1 |

| Процессор | 1979 |

|

SU783795A2 |

Авторы

Даты

1981-11-15—Публикация

1979-09-17—Подача