31

2, дешифратор 3, шифратор 4, мультиплексоры 6 и 14, триггеры 8, 11, 12 и 13, регистры 15, 16 и 17 сдвига, счетчики J8, 19 и 20, элементы 2И-ИЛИ 24, 25 и 26. Устройство обеспечивает достоверный и гибкий контроль микропроцессорных систем с тремя тинами в процессе их функционирования. Гибкость контроля обеспечивается путем избирательной фильтрации потока ошибок по типам, связанным с устройствами контролируемой микропроцессорной системы, при обращении к которым они возникают. Оценка частных потоков ошибок с целью формирования сигнала общей ошибки осуществляется по двум

порогам: порогу плотности распределения и интегральному порогу потока ошибок каждого типа. Сигнал общей ошибки формируется лишь при достижении в некотором канале контроля пороговых значений. Это обеспечивает прерывание выполнения основной программы в существенно более редких случаях и только в ситуациях, заранее назначаемых разработчиком и представляющих реальную опасность для выполнения основной задачи. В результате существенно повышается устойчивость вычислительного процесса в контролируемой системе к воздействию помехи расширяется область ее применения. 2 ил. , 3 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1559347A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для сопряжения цифровой вычислительной машины с внешними устройствами | 1987 |

|

SU1413635A2 |

| Устройство для отладки микропроцессорной системы | 1987 |

|

SU1453408A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем. Целью изобретения является повышение диагностических возможностей устройства за счет разделения возникающих ошибок на ошибки, требующие перезапуска и не требующие перезапуска. Устройство содержит блок 1 постоянной памяти, регистр 2, дешифратор 3, шифратор 4, мультиплексоры 6 и 14, триггеры 8, 11, 12 и 13, регистры 15, 16 и 17 сдвига, счетчики 18, 19 и 20, элементы 2И-ИЛИ 24, 25 и 26. Устройство обеспечивает достоверный и гибкий контроль микропроцессорных систем с тремя шинами в процессе их функционирования. Гибкость контроля обеспечивается путем избирательной фильтрации потока ошибок по типам, связанным с устройствами контролируемой микропроцессорной системы, при обращении к которым они возникают. Оценка частных потоков ошибок с целью формирования сигнала общей ошибки осуществляется по двум порогам: порогу плотности распределения и интегральному порогу потока ошибок каждого типа. Сигнал общей ошибки формируется лишь при достижении в некотором канале контроля пороговых значений. Это обеспечивает прерывание выполнения основной программы в существенно более редких случаях и только в ситуациях, заранее назначаемых разработчиком и представляющих реальную опасность для выполнения основной задачи. В результа3.062образце 2 установлены электротензодатчики 7. При работе устройства опорные плиты 1 поворачиваются вокруг шарниров шарнирно опертой жесткой стенки 3, таки

Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем.

Целью изобретения является повышение диагностических возможностей устройства за счет разделения возникающих ошибок на ошибки, требующие и не требующие перезапуска.

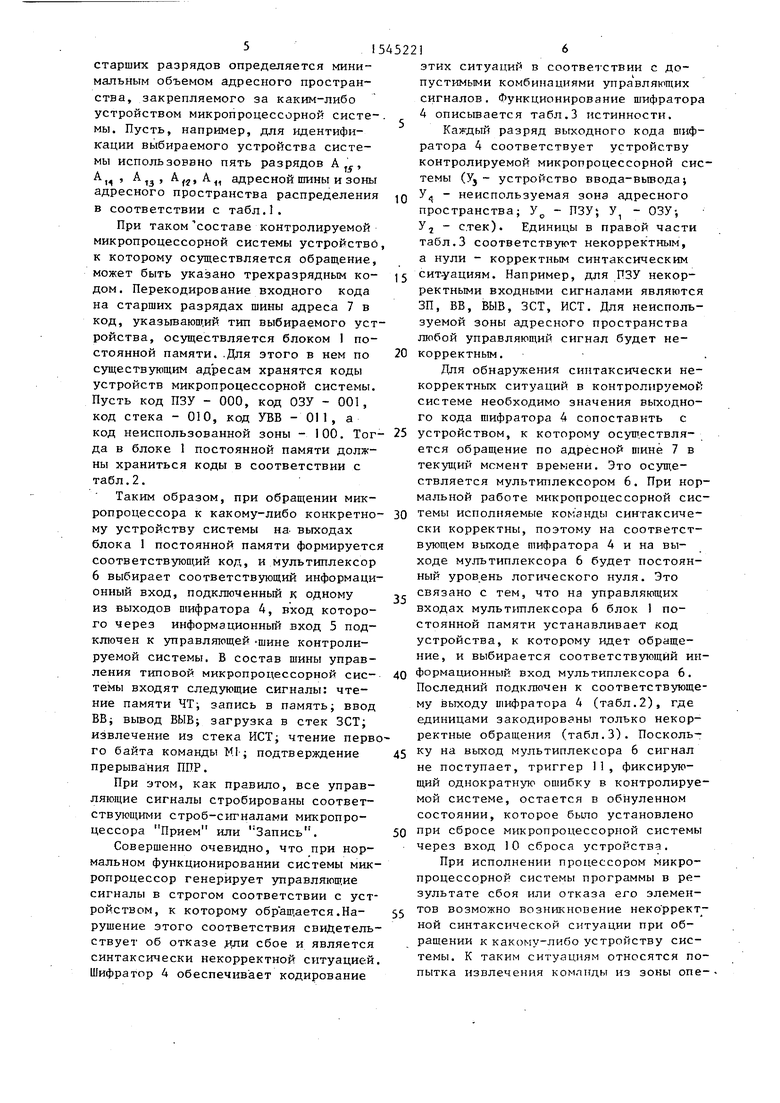

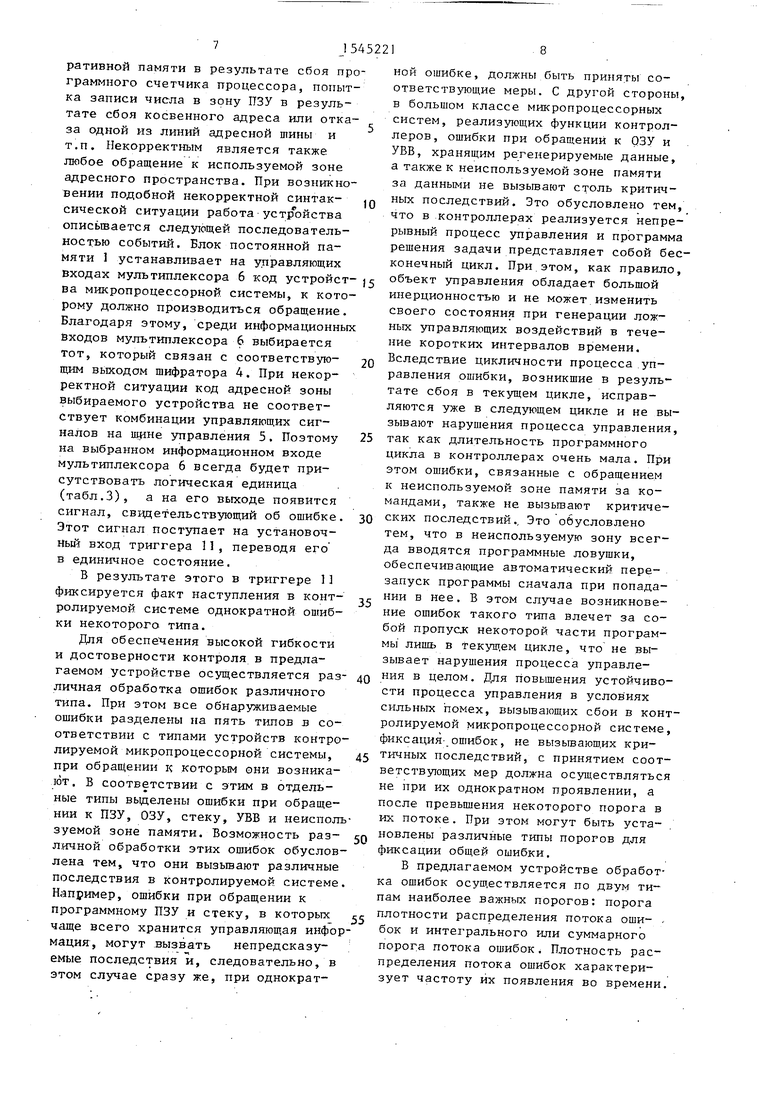

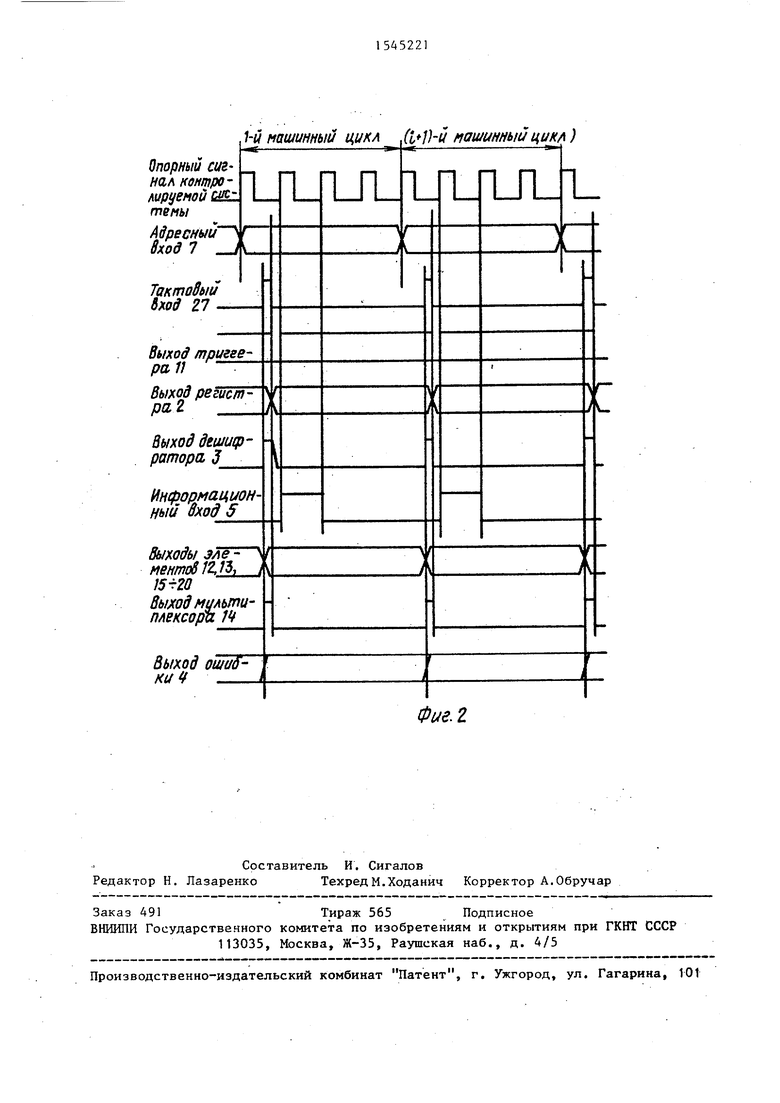

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - вре- менные диаграммы его работы.

Устройство для контроля микропроцессорной системы содержит (фиг.1) последовательно соединенные блок 1 постоянной памяти, регистр 2 и дешифратор 3, последовательно соединенные шифратор 4, информационный вход которого является информационным входом 5 устройства, и первый мультиплексор 6, управляющий вход которого соединен с выходом блока 1 постоянной памяти, адресный вход которого являетс адресным входом 7 устройства, первый триггер 8, выход которого является выходом 9 сигнала ошибки, а вход сбрса соединен с входом 10 сброса устройства, второй 11, третий 12 и четвертый 13 триггеры, второй мультиплексор 14, три регистра 15-17 сдвига, три счетчика 18-20, три элемента И 21-23, и три элемента 2И-ИЛИ 24-26.

Устройство для контроля микропроцессорной системы работает следующим образом.

Оно обеспечивает контроль наиболее распространенной микропроцессор5

0

5

0

5

0

5

ной системы с тремя шинами: шиной адреса, шиной данных и шиной управления.

Для обеспечения контроля микропроцессорной системы вход 5 предлагаемого устройства подключается к управляющей шине контролируемой системы, вход 7 - к ее адресной шине, вход 10 сброса - к цепи сброса микропроцессора, вход 27 - к линии сигнала Синхронизация контролируемой системы, а выход 9 сигнала ошибки - к входу запроса прерывания микропроцессора или может использоваться другим образом.

В общем случае контролируемая микропроцессорная система содержит постоянную память (ПЗУ), оперативную память (ОЗУ), в которой организуется стек, и устройства ввода-вывода (УВВ). На стадии программирования программист должен распределить зону адресного пространства микропроцессора и закрепить за каждым из устройств системы определенную адресную зону. При этом, как правило, часть адресного пространства остается неиспользованной.

Для обращения к конкретному устройству микропроцессор формирует на шине адреса соответствующий код, обеспечивающий активацию выбранного устройства. Для упрошения селекции вы- бираемого устройства распределение адресов осуществляется таким образом, чтобы по старшим разрядам адреса можно было бы определить устройство, к которому осуществляется обращение. Количество используемых для этого

515

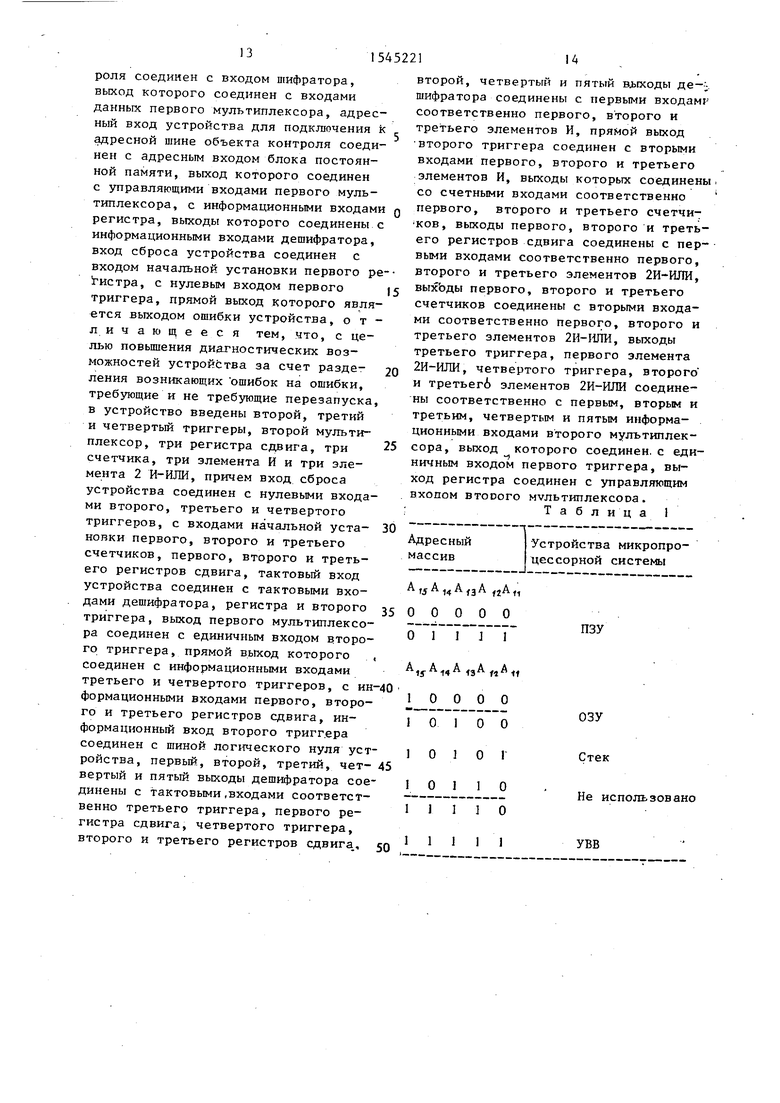

старших разрядов определяется минимальным объемом адресного пространства, закрепляемого за каким-либо устройством микропроцессорной систе-. мы. Пусть, например, для идентификации выбираемого устройства системы ИСПОЛЬЗОРВНО пять разрядов А ,5 ,

и и адресной шины и зоны адресного пространства распределения в соответствии с табл.1.

При таком составе контролируемой микропроцессорной системы устройство, к которому осуществляется обращение, может быть указано трехразрядным ко- дом. Перекодирование входного кода на старших разрядах шины адреса 7 в код, указывающий тип выбираемого устройства, осуществляется блоком I постоянной памяти. .Для этого в нем по существующим адресам хранятся коды устройств микропроцессорной системы. Пусть код ПЗУ - 000, код ОЗУ - 001, код стека - 010, код УВВ -Oil, a код неиспользованной зоны - 100. Тог- да в блоке 1 постоянной памяти должны храниться коды в соответствии с табл.2.

Таким образом, при обращении микропроцессора к какому-либо конкретно- му устройству системы на выходах блока 1 постоянной памяти формируется соответствующий код, и мультиплексор 6 выбирает соответствующий информационный вход, подключенный к одному из выходов шифратора 4, вход которого через информационный вход 5 подключен к управляющей -шине контролируемой системы. В состав шины управления типовой микропроцессорной сие- темы входят следующие сигналы: чтение памяти ЧТ; запись в память; ввод ВВ; вывод ВЫВ; загрузка в стек ЗСТ; извлечение из стека ИСТ; чтение первого байта команды Ml; подтверждение прерывания ППР.

При этом, как правило, все управляющие сигналы стробированы соответствующими строб-сигналами микропроцессора Прием или Запись.

Совершенно очевидно, что при нормальном функционировании системы микропроцессор генерирует управляющие сигналы в строгом соответствии с устройством, к которому обращается.На- рушение этого соответствия свидетельствует об отказе или сбое и является синтаксически некорректной ситуацией. Шифратор 4 обеспечивает кодирование

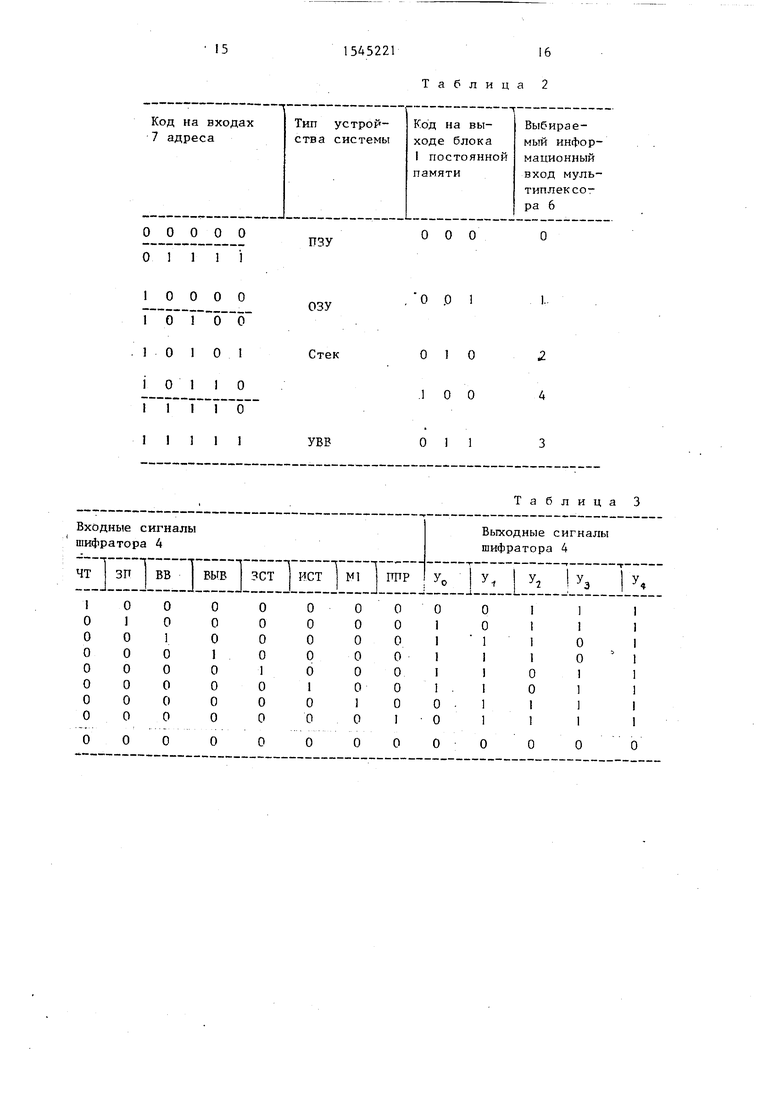

этих ситуаций в соответствии с допустимыми комбинациями управляющих сигналов. Функционирование пшфратора 4 описывается табл.3 истинности.

Каждый разряд выходного кода шифратора 4 соответствует устройству контролируемой микропроцессорной системы (У} устройство ввода-вывода ; У - неиспользуемая зона адресного пространства; У0 - ПЗУ; У, - ОЗУ; У7 - стек). Единицы в правой части таОл.З соответствуют некорректным, а нули - корректным синтаксическим ситуациям. Например, для ПЗУ некорректными входными сигналами являются ЗП, ВВ, ВЫВ, ЗСТ, ИСТ. Для неиспользуемой зоны адресного пространства любой управляющий сигнал будет некорректным.

Для обнаружения синтаксически некорректных ситуаций в контролируемой системе необходимо значения выходного кода шифратора 4 сопоставить с устройством, к которому осушествля- ется обращение по адресной шине 7 в текущий мгмент времени. Это осутпе- ствляется мультиплексором 6. При нормальной работе микропроцессорной системы исполняемые команды синтаксически корректны, поэтому на соответствующем выходе шифратора 4 и на выходе мультиплексора 6 будет постоянный уровень логического нуля. Это связано с тем, что на управляющих входах мультиплексора 6 блок 1 постоянной памяти устанавливает код устройства, к которому идет обращение, и выбирается соответствующий информационный вход мультиплексора 6. Последний подключен к соответствующему выходу шифратора 4 (табл.2), где единицами закодированы только некорректные обращения (табл.3). Поскольку на выход мультиплексора 6 сигнал не поступает, триггер II, фиксирующий однократную ошибку в контролируемой системе, остается в обнуленном состоянии, которое было установлено при сбросе микропроцессорной системы через вход 10 сброса устройства.

При исполнении процессором микропроцессорной системы программы в результате сбоя или отказа его элементов возможно возникновение некорректной синтаксической ситуации при обращении к какому-либо устройству системы. К таким ситуациям относятся попытка извлечения команды из зоны oneративной памяти в результате сбоя программного счетчика процессора, попытка записи числа в зону ПЗУ в результате сбоя косвенного адреса или отказа одной из линий адресной шины и т.п. Некорректным является также любое обращение к используемой зоне адресного пространства. При возникновении подобной некорректной синтак- сической ситуации работа устройства описывается следующей последовательностью событий. Блок постоянной памяти 1 устанавливает на управляющих входах мультиплексора 6 код устройст- ва микропроцессорной системы, к которому должно производиться обращение. Благодаря этому, среди информационных входов мультиплексора 6 выбирается тот, который связан с соответствую- щим выходом шифратора 4. При некорректной ситуации код адресной зоны выбираемого устройства не соответствует комбинации управляющих сигналов на шине управления 5. Поэтому на выбранном информационном входе мультиплексора 6 всегда будет присутствовать логическая единица (табл.3), а на его выходе появится сигнал, свидетельствующий об ошибке. Этот сигнал поступает на установочный вход триггера 11, переводя его в единичное состояние.

В результате этого в триггере 1 I фиксируется факт наступления в копт- ролируемой системе однократной ошибки некоторого типа.

Для обеспечения высокой гибкости и достоверности контроля в предлагаемом устройстве осуществляется раз- личная обработка ошибок различного типа. При этом все обнаруживаемые ошибки разделены на пять типов в соответствии с типами устройств контролируемой микропроцессорной системы, при обращении к которым они возникают. В соответствии с этим в отдельные типы выделены ошибки при обращении к ПЗУ, ОЗУ, стеку, УВВ и неиспользуемой зоне памяти. Возможность раз- личной обработки этих ошибок обусловлена тем, что они вызывают различные последствия в контролируемой системе. Например, ошибки при обращении к программному ПЗУ и стеку, в которых чаще всего хранится управляющая информация, могут вызвать непредсказуемые последствия и, следовательно, в этом случае сразу же, при однократной ошибке, должны быть приняты соответствующие меры. С другой стороны, в большом классе микропроцессорных систем, реализующих функции контроллеров, ошибки при обращении к ОЗУ и УВВ, хранящим регенерируемые данные, а также к неиспользуемой зоне памяти за данными не вызывают столь критичных последствий. Это обусловлено тем, что в контроллерах реализуется непрерывный процесс управления и программа решения задачи представляет собой бесконечный цикл. При этом, как правило, объект управления обладает большой инерционностью и не может изменить своего состояния при генерации ложных управляющих воздействий в течение коротких интервалов времени. Вследствие цикличности процесса управления ошибки, возникшие в результате сбоя в текущем цикле, исправляются уже в следующем цикле и не вызывают нарушения процесса управления, так как длительность программного цикла в контроллерах очень мала. При этом ошибки, связанные с обращением к неиспользуемой зоне памяти за командами, также не вызывают критических последствий. Это обусловлено тем, что в неиспользуемую зону всегда вводятся программные ловушки, обеспечивающие автоматический перезапуск программы сначала при попадании в нее. В этом случае возникновение ошибок такого типа влечет за собой пропуск некоторой части программы лишь в текущем цикле, что не вызывает нарушения процесса управления в целом. Для повышения устойчивости процесса управления в условиях сильных помех, вызывающих сбои в контролируемой микропроцессорной системе, фиксация ошибок, не вызывающих критичных последствий, с принятием соответствующих мер должна осуществляться не при их однократном проявлении, а после превышения некоторого порога в их потоке. При этом могут быть установлены различные типы порогов для фиксации общей ошибки.

В предлагаемом устройстве обработка ошибок осуществляется по двум типам наиболее важнмх порогов: порога плотности распределения потока ошибок и интегрального или суммарного порога потока ошибок, Плотность распределения потока ошибок характеризует частоту их появления во времени.

Этот порог превышается, если подряд в течение некоторого заранее заданного количества последовательных циклов контроля фиксируется факт появле ния ошибки одного типа. Если же эта ошибка носит перемежающиеся характер с количеством ошибок в пачке, не превышающем установленного порога плотности, то общая ошибка в этом случае не фиксируется,.

Интегральный показатель потока ошибок характеризует общее количество появления однократных ошибок од чого типа, в течение некоторого заранее установленного интервала времени наблюдения, в качестве которого может использоваться общее время работы устройства. Интегральный порог превышается, если в течение времени наблюдения количество однократных ошибок одного типа становится равным некоторому заранее выбранному числу.

Анализ однократных ошибок, возникающих в контролируемой системе, с учетом их типов и установленных порогов осуществляется следующим образом. В микропроцессорных системах (например, на базе микропроцессора КР580ВК80А) каждая команда програм- мм выполняется в течение нескольких машинных циклов, каждый из которых состоит из нескольких машинных такто Каждый машинный цикл связан с обращением к внешним по отношению к процессору системы устройствам (ПЗУ, ОЗУ, стеку, УВВ)f и, следовательно, в каждом машинном цикле возможно появление однократной ошибки некоторого типа, В связи с этим анализ сос- .тояния триггера I 1, фиксирующего однократную ошибку, осуществляется в каждом машинном цикле.

В начале каждого машинного цикла процессор системы генерирует сигнал Синхронизация11, поступающий на тактовый вход 27 устройства. По спаду этого сигнала триггер 11 в начале каждого мапшнного цикла устанавливается в исходное нулевое состояние (фиг.2). Это обеспечивает сброс результата контроля однократной ошибки в предыдущем машинном цикле и подготавливает устройство к ее фиксации в текущем машинном цикле. При этом одновременно в регистре 2 фиксируется код устройства (табл.2), к которому осуществляется обращение в текущем машинном цикле. Этот код по

0

5

0

5

0

5

0

5

ступает на вход дешифратору 3, рабо- та которого в данный момент запрещена нулевым уровнем на входе стро- бирования. Поэтому все выходы дешифратора 3 при этом остаются в пассивном состоянии. Вслед за сигналом Синхронизация процессор контролируемой системы генерирует управляющие сигналы, осуществляющие фактическое обращение к выбранному по шине адреса устройству системы. При несоответствии адреса на входе 7 управляющему сигналу на входе 5 в триггере 1I фиксируется однократная ошибка в контролируемой системе, что было подробно рассмотрено выше.

Выходной сигнал с триггера I1 поступает на информационные входы триггеров 12 и 13, регистров 15-17 сдвига и вход(1 элементов И 21-23, управляющих прохождением сигналов на счетные входы счетчиков 18-20. Это подготавливает предлагаемое устройство к анализу типа зафиксированной однократной ошибки. Триггеры 12 и 13 предназначены для фиксации однократных ошибок при обращении к программному ПЗУ и стеку соответственно, регистры 5-1 7 сдвига - для фиксации плотности распределения потоков ошибок при обращении к ОЗУ, УВВ и неиспользуемой зоне адресного пространства соответственно, а счетчики 18-20 - для фиксации интегральных показателей потоков ошибок при обрашении к тем же устройствам. Разрядность элементов 12 и 13, 15-20 определяется максимальным допустимым значением соответствующих порогов для фиксации общей ошибки.

Факт достижения порога плотности распределения и интегрального потока ошибок при обращении к ОЗУ, УВВ и неиспользуемой зоне памяти устанавливается с помощью элементов И-ИЛИ 24- 26 соответственно. Их настройка на некоторый порог осуществляется путем соответствующего подключения их входов к прямым выходам регистров 15-17 сдвига или к прямым и инверсным выходам счетчиков 18-20 в зависимости от выделяемого кода. Например, если порог плотности распределения потока ошибок при обращении к ОЗУ установлен на уровне 8, то разрядность регистра 15 сдвига должна быть равна 8, и восемь входов первой группы элемента И-ИЛИ 24 должны быть подключены к

прямым выходам всех триггеров регистра 1 5 сдвига. Если интегральный порог по-4 тока ошибок при обращении к ОЗУ установлен на уровне 100 11000100,, то разряд- нЬсть счетчика 18 должна быть равна 7, а семь входов второй группы элемента И-ИЛИ 24 должны быть подключены к прямым выходам 7,6 и 3 и инверсным выходам 5,4, 2 и 1 триггеров ачетчика 18. Аналогичным образом определяется разрядность остальных регистров сдвига, счетчиков и вариант подключения к ним соответствующих элементов И-ИЛИ.

Анализ типа однократной ошибки, зафиксированный в триггере 11, осуществляется по фронту очередного сигнала Синхронизация (фиг.2). При этом по

10

15

Рассмотренный процесс функциони вания предлагаемого устройства обе печивает избирательную фильтрацию тока однократных ошибок с их разде ным накоплением по различным типам ошибок и их оценку по различным по гам. При достижении в некотором ка ле какого-либо установленного поро ошибок активируется выход соответствующего элемента И-ИЛИ 24-26 или выход триггеров 12 и 13, подключен к информационным входам мультиплек сора 14. Этот мультиплексор предна начен для оценки необходимости фик саций общей ошибки. Для этого код регистра 2 поступает на управляющий вход мультиплексора 14 и выбирает его информационный вход, соответст

входу стробирования разрешается рабо- 2Q вующий типу ошибки, контролируемой

та дешифратора 3, и активный уровень появляется на его выходе, соответствующем коду, запомненному в регистре 2, т.е. типу устройства контролируемой системы, к которому было обраще- 25 ние в предьрущем машинном цикле. По фронту выходного сигнала дешифратора 3 осуществляется фиксация однократной ошибки с выхода триггера 11 в соответствующем канале контроля. Например, 30 если активируется нулевой или второй выходы дешифратора 3, то однократная ошибка фиксируется в триггерах 12 или 13 соответственно. При активировании первого, третьего или четверто- 35 го выходов дешифратора 3 ошибка фиксируется путем сдвига соответствующего регистра сдвига и инкрементирова- ния соответствующего счетчика, так как все элементы И в этот момент вре- 40 мени открыты сигналом с выхода триггера 1 1 .

Если при обращении к некоторому - устройству контролируемой системы однократная ошибка в очередном машин- 45 ном цикле не обнаруживается, то работа предлагаемого устройства описывается совершенно аналогичной последовательностью событий. Однако в этом случае триггер 11 находится в 50 нулевом состоянии. Поэтому при активировании выхода дешифратора 3 состояние всех счетчиков не изменяется, а в.соответствующий регистр сдвига записывается логический О. Это обес- печивает отсчет плотности распределения потока ошибок при обращении к соответствующему устройству контролируемой системы сначала.

в текущий момент времени. Если в р зультате фиксации очередной однокр ной ошибки в выбранном канале дост гается какой-либо порог, то на выб ранном информационном входе мульт плексора 14, а следовательно, и на выходе появляется активный уровень устанавливающий триггер 8, фиксирую щий общую ошибку, в единичное состояние. В результате этого на выход 9 устройства появляется активный уровень, свидетельствующий о возник новении в контролируемой системе ошибки, по которой должны быть при няты соответствующие меры.

Выход 9 ошибки устройства соеди няется с в.ходом запроса прерывания микропроцессорной системы или, може использоваться каким-либо другим о разом. В первом случае при возникновении ошибки выполнение текущей программы прерывается и система переходит к выполнению программы обработки прерывания по ошибке. Эта программа может предусматривать вос становление процесса, нарушенного общей ошибкой, может иметь диагнос ческий характер (выявление причин ошибки) или обеспечивать останов нарушенного про-цесса.

« Формула изобретени

Устройство для контроля микропро цессорной системы, содержащее блок постоянной памяти, шифратор, первый мультиплексор, первый триггер, регистр и дешифратор, причем информационный вход устройства для подключения к управляющей шине объекта ко

5

Рассмотренный процесс функционирования предлагаемого устройства обеспечивает избирательную фильтрацию потока однократных ошибок с их раздельным накоплением по различным типам ошибок и их оценку по различным порогам. При достижении в некотором канале какого-либо установленного порога ошибок активируется выход соответствующего элемента И-ИЛИ 24-26 или выход триггеров 12 и 13, подключенных к информационным входам мультиплексора 14. Этот мультиплексор предназначен для оценки необходимости фиксаций общей ошибки. Для этого код с регистра 2 поступает на управляющий вход мультиплексора 14 и выбирает его информационный вход, соответствующий типу ошибки, контролируемой

в текущий момент времени. Если в результате фиксации очередной однократной ошибки в выбранном канале достигается какой-либо порог, то на выбранном информационном входе мультиплексора 14, а следовательно, и на выходе появляется активный уровень, устанавливающий триггер 8, фиксирующий общую ошибку, в единичное состояние. В результате этого на выходе 9 устройства появляется активный уровень, свидетельствующий о возникновении в контролируемой системе ошибки, по которой должны быть приняты соответствующие меры.

Выход 9 ошибки устройства соединяется с в.ходом запроса прерывания микропроцессорной системы или, может использоваться каким-либо другим образом. В первом случае при возникновении ошибки выполнение текущей программы прерывается и система переходит к выполнению программы обработки прерывания по ошибке. Эта программа может предусматривать восстановление процесса, нарушенного общей ошибкой, может иметь диагностический характер (выявление причин ошибки) или обеспечивать останов нарушенного про-цесса.

« Формула изобретения

Устройство для контроля микропро- цессорной системы, содержащее блок постоянной памяти, шифратор, первый мультиплексор, первый триггер, регистр и дешифратор, причем информационный вход устройства для подключения к управляющей шине объекта кон13

роля соединен с входом шифратора, выход которого соединен с входами данных первого мультиплексора, адресный вход устройства для подключения к адресной шине объекта контроля соединен с адресным входом блока постоянной памяти, выход которого соединен с управляющими входами первого мультиплексора, с информационными входами регистра, выходы которого соединены с информационными входами дешифратора, вход сброса устройства соединен с входом начальной установки первого ре гистра, с нулевым входом первого триггера, прямой выход которого является выходом ошибки устройства, отличающееся тем, что, с целью повышения дидгност тческих возможностей устройства за счет разделения возникающих ошибок на ошибки, требующие и не требующие перезапуска, в устройство введены второй, третий и четвертый триггеры, второй мультиплексор, три регистра сдвига, три счетчика, три элемента И и три элемента 2 И-ИЛИ, причем вход сброса устройства соединен с нулевыми входами второго, третьего и четвертого триггеров, с входами начальной уста- нопки первого, второго и третьего счетчиков, первого, второго и третьего регистров сдвига, тактовый вход устройства соединен с тактовыми входами дешифратора, регистра и второго триггера, выход первого мультиплексора соединен с единичным входом второго триггера, прямой выход которого соединен с информационными входами третьего и четвертого триггеров, с ин формационными входами первого, второго и третьего регистров сдвига, информационный вход второго триггера соединен с шиной логического нуля устройства, первый, второй, третий, чет- вертый и пятый выходы дешифратора соединены с тактовыми.входами соответственно третьего триггера, первого регистра сдвига, четвертого триггера, второго и третьего регистров сдвига,,

5

0

5

Q5 40 4550

второй, четвертый и пятый в.ьгходы де-, шифратора соединены с первыми входам соответственно первого, второго и третьего элементов И, прямой выход второго триггера соединен с вторыми входами первого, второго и третьего элементов И, выходы которых соединены со счетными входами соответственно первого, второго и третьего счетчиков, выходы первого, второго и третьего регистров сдвига соединены с первыми входами соответственно первого, второго и третьего элементов 2И-ИЛИ, выходы первого, второго и третьего счетчиков соединены с вторыми входами соответственно первого, второго и третьего элементов 2И-ИЛИ, выходы третьего триггера, первого элемента 2И-ИЛИ, четвертого триггера, второго и третьегА элементов 2И-ИЛИ соединены соответственно с первым, вторым и третьим, четвертым и пятым информационными входами второго мультиплексора, выход которого соединен с единичным входом первого триггера, выход регистра соединен с управляющим входом ВТОРОГО мультиплексора.

Таблица 1 ..

30

Адресный массив

Устройства микропроцессорной системы

A«A14Af3A f2AM

О

о

14

0о

11

о

т

о J

ПЗУ

А.Ц. А14 А 3А МА i1

ОЗУ

Стек

Не использовано

111

УВВ

15

154522116

Таблица 2

000

i i i

000

ПЗУ

ОЗУ

0101

о i i о

iiii

Стек

УВВ

0

1

О

О

1

2 4

Таблица 3

Фиг. 2

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-23—Публикация

1988-05-03—Подача