Изобретение относится к вычислительной и может быть использовано для сопряжения ЭВМ, имекмцих единый канал обмена информации (интерфейс типа канал), например ЭВМ Электроника-60 с внешними устройствами пользователя.

Целью изобретения является упрощение устройства и повышение его быстродействия.

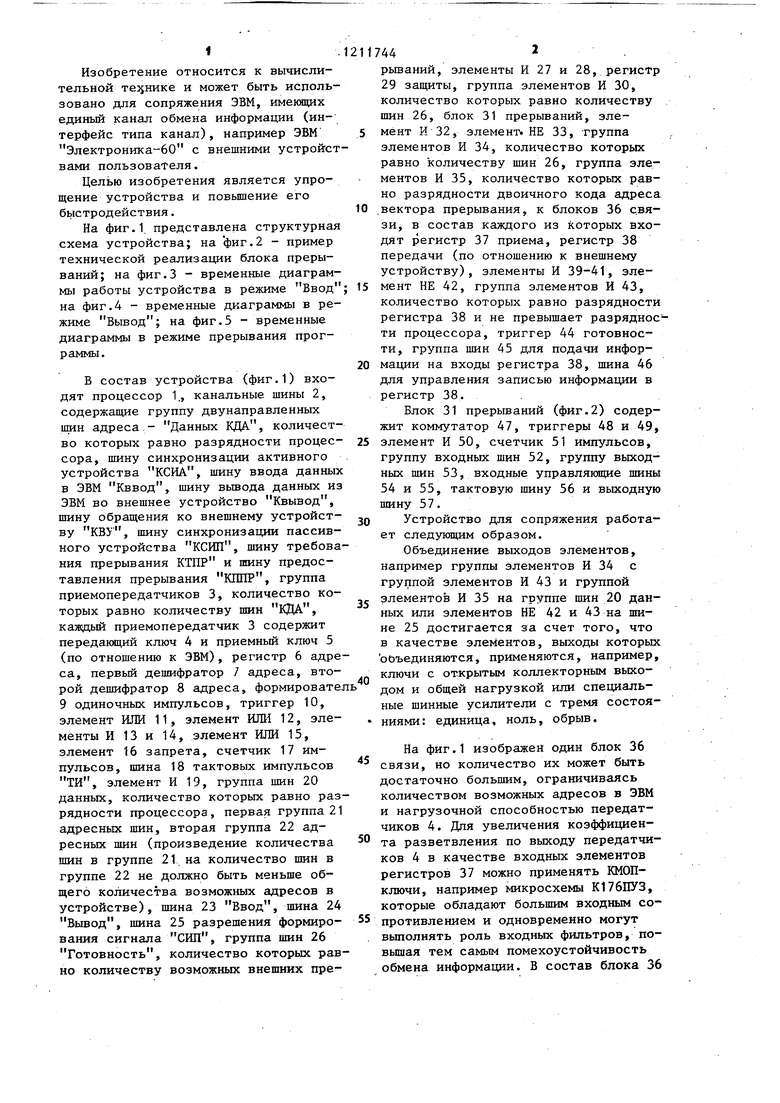

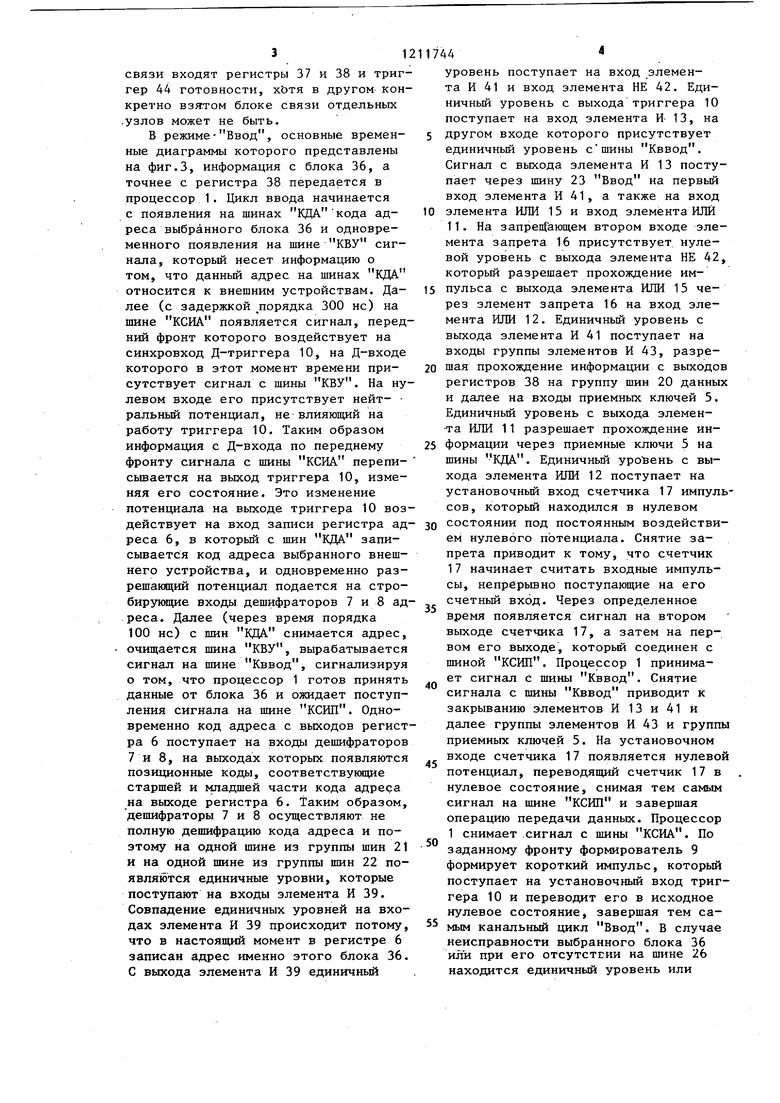

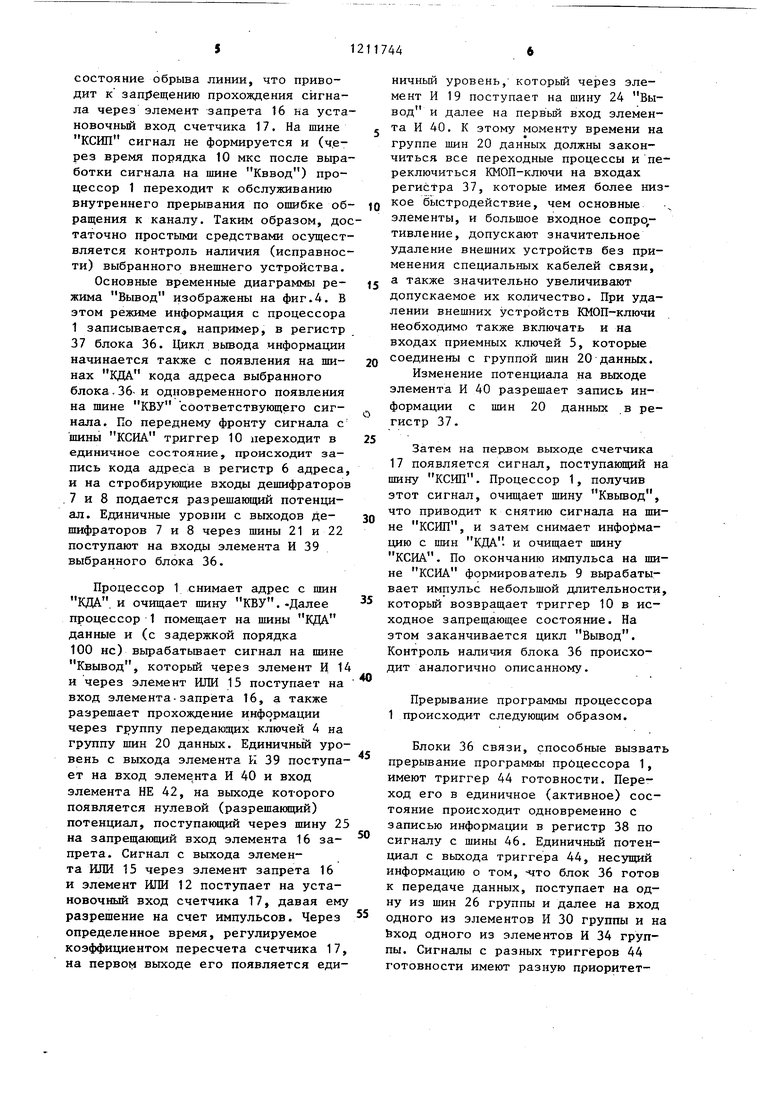

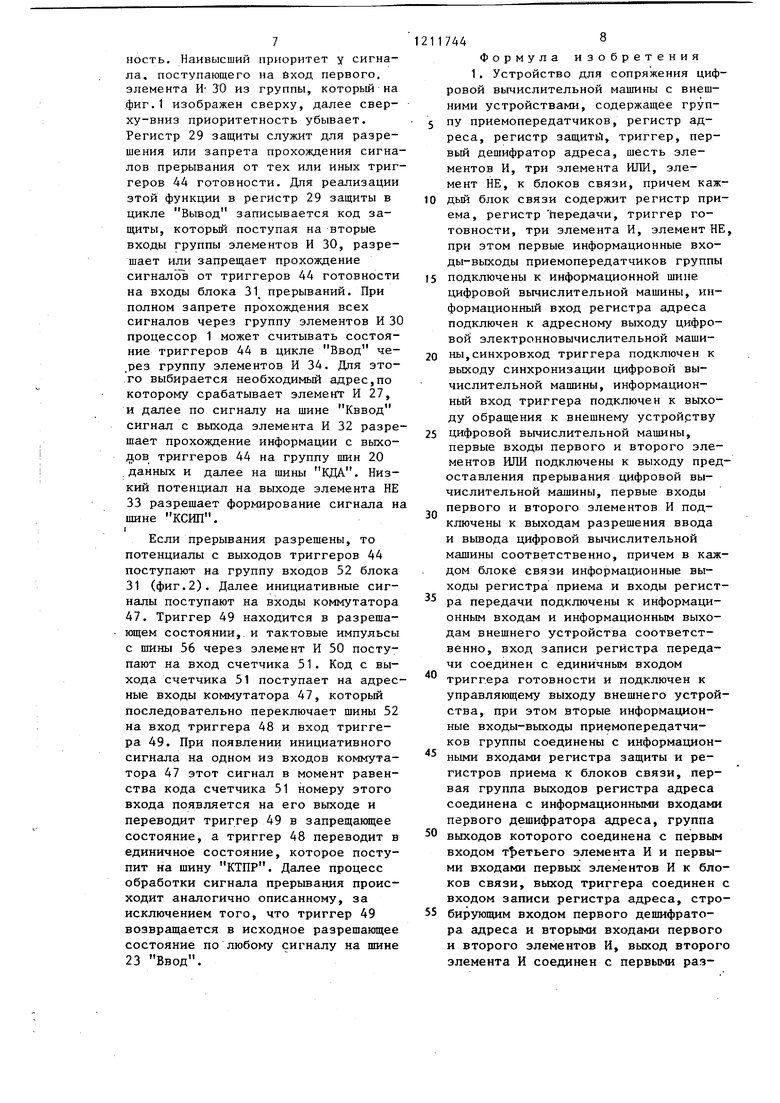

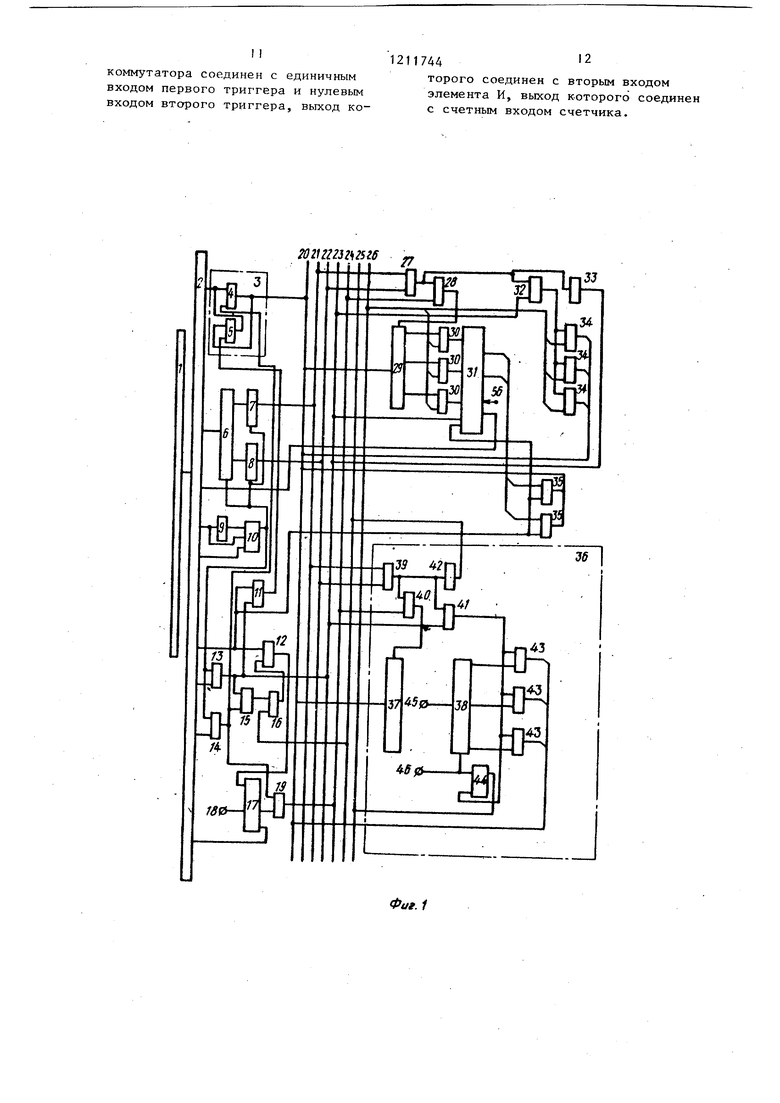

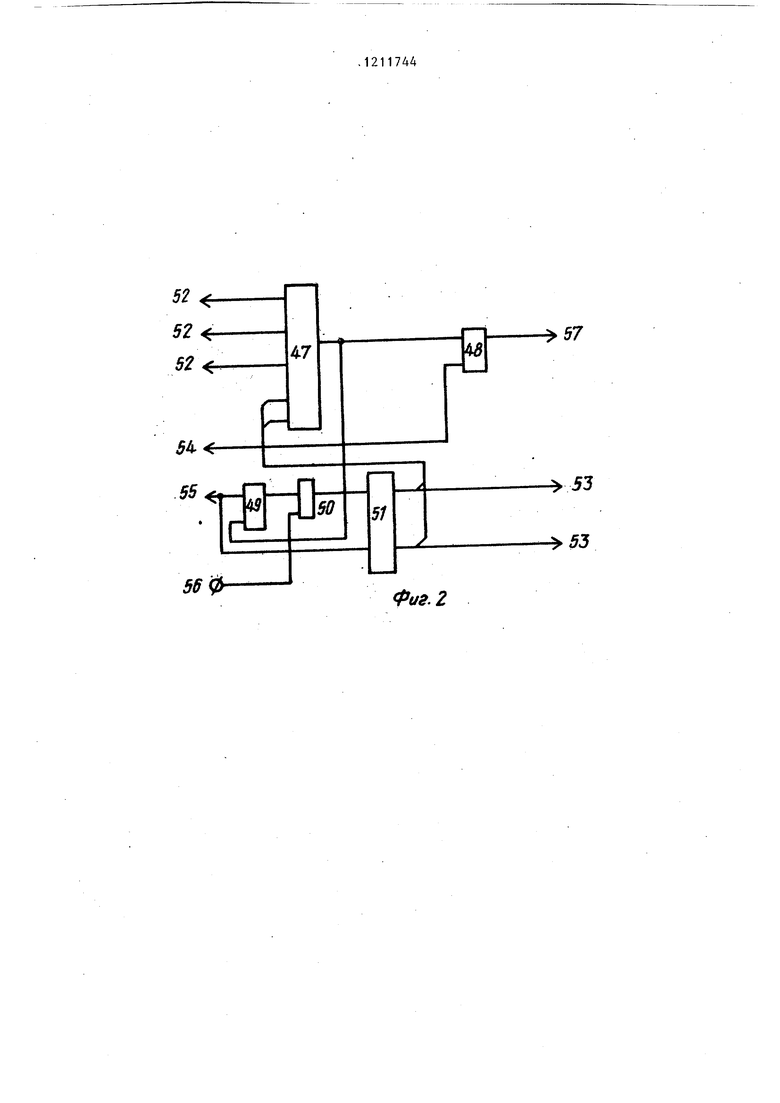

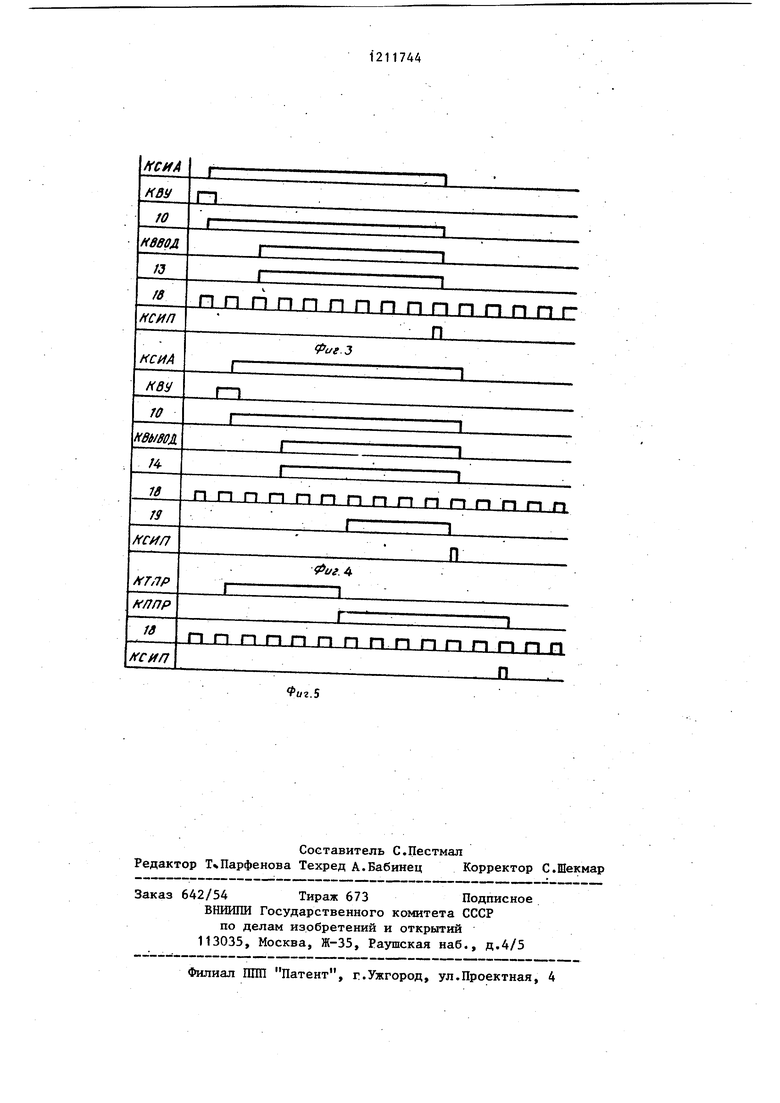

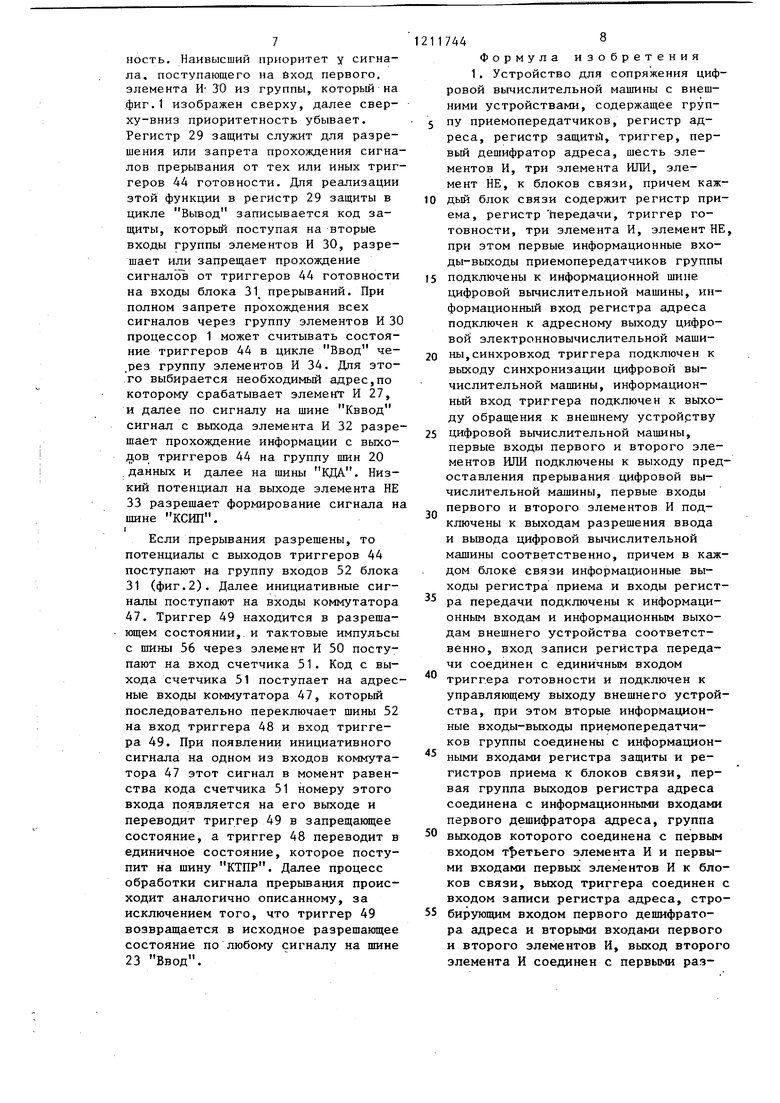

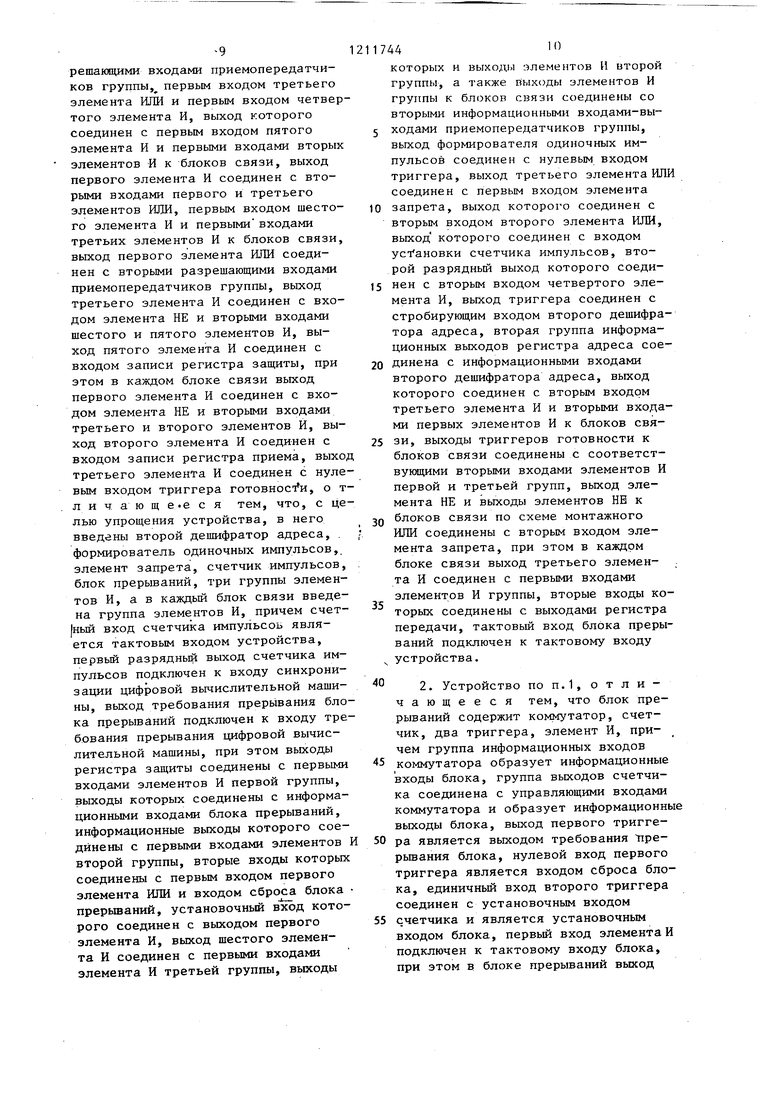

На фиг.1. представлена структурная схема устройства; на фиг.2 - пример технической реализации блока прерываний; на фиг.З - временные диаграммы работы устройства в режиме Ввод на фиг.4 - временные диаграммы в режиме Вывод ; на фиг.З - временные диаграммы в режиме прерывания программы.

В состав устройства (фиг.1) входят процессор 1., канальные шины 2, содержащие группу двунаправленных ишн адреса,- Данных КДА, количество которых равно разрядности процессора, шину синхронизации активного устройства КСИА, шину ввода данных в ЭВМ Кввод, шину вьшода данных из ЭВМ во внешнее устройство Квывод, шину обращения ко внешнему устройству КВУ, шину синхронизации пассивного устройства КСИП, шину требования прерывания КТПР и шину предоставления прерывания КППР, группа приемопередатчиков 3, количество которых равно количеству шин КДА, каявдый приемопередатчик 3 содержит передающий ключ 4 и приемный ключ 5 (по отношению к ЭВМ), регистр 6 адреса, первый дешифратор 7 адреса, второй дешифратор 8 адреса, формировател 9 одиночных импульсов, триггер 10, элемент ИЛИ 11, элемент ИЛИ 12, элементы И 13 и 14, элемент ИЛИ 15, элемент 16 запрета, счетчик 17 импульсов, шина 18 тактовых импульсов ТИ, элемент И 19, группа шин 20 данных, количество которых равно разрядности процессора, первая группа 21 адресных шин, вторая группа 22 адресных шин (произведение количества шин в группе 21 на количество шин в группе 22 не должно быть меньше общего количества возможных адресов в устройстве), шина 23 Ввод, шина 24 Вывод, шина 25 разрешения формирования сигнала СИП, группа шин 26 Готовность, количество которых равно количеству возможных внешних пре

5

5

0

0

5

0

5

0

5

0

5

7442

рьшаний, элементы И 27 и 28, регистр 29 защиты, группа элементов И 30, количество которых равно количеству шин 26, блок 31 прерываний, элемент И 32, элемент. НЕ 33, труппа элементов И 34, количество которых равно количеству шин 26, группа элементов И 35, количество которых равно разрядности двоичного кода адреса .вектора прерывания, к блоков 36 связи, в состав каждого из которых входят регистр 37 приема, регистр 38 передачи (по отношению к внешнему устройству), элементы И 39-41, элемент НЕ 42, группа элементов И 43, количество которых равно разрядности регистра 38 и не превышает разрядности процессора, триггер 44 готовности, группа шин 45 для подачи информации на входы регистра 38, шина 46 для управления записью информации в регистр 38.

Влок 31 прерываний (фиг.2) содержит коммутатор 47, триггеры 48 и 49, элемент И 50, счетчик 51 импульсов, группу входных шин 52, группу выходных шин 53, входные управляющие шины 54 и 55, тактовую шину 56 и выходную шину 57.

Устройство для сопряжения работает следующим образом.

Объединение выходов элементов, например группы элементов И 34 с группой элементов И 43 и группой элементов И 35 на группе шин 20 данных или элементов НЕ 42 и 43 на шине 25 достигается за счет того, что в качестве элементов, выходы которых объединяются, применяются, например, ключи с открытым коллекторным выходом и общей нагрузкой или специальные шинные усилители с тремя состояниями: единица, ноль, обрыв.

На фиг.1 изображен один блок 36 связи, но количество их может быть достаточно большим, ограничиваясь количеством возможных адресов в ЭВМ и нагрузочной способностью передатчиков 4. Для увеличения коэффициента разветвления по выходу передатчиков 4 в качестве входных элементов регистров 37 можно применять КМОП- ключи, например микросхемы К17611УЗ, которые обладают большим входным сопротивлением и одновременно могут вьшолнять роль входных фильтров, по- вьш1ая тем самым помехоустойчивость обмена информации. В состав блока 36

31

связи входят регистры 37 и 38 и триггер 44 готовности, хЬтя в другом конкретно взятом блоке связи отдельных .узлов может не быть.

В режиме- Ввод, основные временные диаграммы которого представлены на фиг.З, информация с блока 36, а точнее с регистра 38 передается в процессор 1. Цикл ввода начинается с появления на шинах КДА кода адреса выбранного блока 36 и одновременного появления на шине КВУ сигнала, который несет информацию о том, что данный адрес на шинах КДА относится к внешним устройствам. Далее (с задержкой порядка 300 не) на шине КСИА появляется сигнал, перед НИИ фронт которого воздействует на синхровход Д-триггера 10, на Д-входе которого в этот момент времени присутствует сигнал с шины КВУ. На ну левом входе его присутствует нейт- ральный потенциал, не влияющий на работу триггера 10. Таким образом информация с Д-входа по переднему фронту сигнала с шины КСИА перепи- сьшается на выход триггера 10, изменяя его состояние. Это изменение потенциала на выходе триггера 10 воз действует на вход записи регистра ад раса 6, в который с шин КДА записывается код адреса выбранного внешнего устройства, и одновременно разрешающий потенциал подается на стро- бирутощие входы дешифраторов 7 и 8 адреса. Далее (через время порядка 100 не) с шин КДА снимается адрес, очищается шина КВУ, вырабатывается сигнал на шине Кввод, сигнализируя о том, что процессор 1 готов принять данные от блока 36 и ожидает поступления сигнала на шине КСИП. Одновременно код адреса с выходов регистра 6 поступает на входы дешифраторов 7 и 8, на выходах которых появляются позиционные коды, соответствующие старшей и младшей части кода адреса на выходе регистра 6. Таким образом, дешифраторы 7 и 8 осуществляют не полную дешифрацию кода адреса и поэтому на одной шине из группы шин 21 и на одной шине из группы шин 22 появляются единичные уровни, которые поступают на входы элемента И 39. Совпадение единичных уровней на входах элемента И 39 происходит потому, что в настоящий момент в регистре 6 записан адрес именно этого блока 36. С выхода элемента И 39 единичный

11744

уровень поступает на вход элемента И 41 и вход элемента НЕ 42. Единичный уровень с выхода триггера 10 поступает на вход элемента И 13, на

5 другом входе которого присутствует единичный уровень с шины Кввод. Сигнал с выхода элемента И 13 поступает через шину 23 Ввод на первый вход элемента И 41, а также на вход

10 элемента ИЛИ 15 и вход элемента ИЛИ 11. На запрегЦающем втором входе элемента запрета 16 присутствует, нулевой уровень с выхода элемента НЕ 42, который разрешает прохождение им15 пульса с выхода элемента ИЛИ 15 через элемент запрета 16 на вход элемента ИЛИ 12. Единичный уровень с выхода элемента И 41 поступает на входы группы элементов И 43, разре20 шая прохождение информации с выходов регистров 38 на группу шин 20 данных и далее на входы приемных ключей 5. Единичный уровень с выхода элемента ИЛИ 11 разрешает прохождение ин25 формации через приемные ключи 5 на шины КДА. Единичный уровень с выхода элемента ИЛИ 12 поступает на установочный вход счетчика 17 импульсов, который находился в нулевом

30 состоянии под постоянным воздействием нулевого потенциала. Снятие запрета приводит к тому, что счетчик 17 начинает считать входные импульсы, непрерьшно поступающие на его счетный вход. Через определенное время появляется сигнал на втором выходе счетчика 17, а затем на первом его выходе, который соединен с шиной КСИП. Процессор 1 принимает сигнал с шины Кввод. Снятие сигнала с шины Кввод приводит к закрыванию элементов И 13 и 41 и далее группы элементов И 43 и группы приемных ключей 5. На установочном входе счетчика 17 появляется нулевой потенциал, переводящий счетчик 17 в нулевое состояние, снимая тем самым сигнал на шине КСИП и завершая операцию передачи данных. Процессор 1 снимает сигнал с шины КСИА. По заданному фронту формирователь 9 формирует короткий импульс, который поступает на установочный вход триггера 10 и переводит его в исходное нулевое состояние, завершая тем са- мым канальный цикл Ввод. В случае неисправности выбранного блока 36 или при его отсутствии на шине 26 находится единичный уровень или

35

40

45

состояние обрыва линии, что приводит к зап 5ещению прохождения сигнала через элемент запрета 16 на уста- новочньй вход счетчика 17. На шине КСИП сигнал не формируется и (ч.е- рез время порядка 10 мкс после выработки сигнала на шине Кввод) процессор 1 переходит к обслуживанию внутреннего прерывания по ошибке об- ращения к каналу. Таким образом, достаточно простыми средствами осуществляется контроль наличия (исправности) выбранного внешнего устройства.

Основные временные диаграммы ре- жима Вывод изображены на фиг.4. В этом режиме информация с процессора 1 записывается, например, в регистр 37 блока 36. Цикл вывода информации начинается также с появления на ши- нах КДА кода адреса выбранного блока,36-и одновременного появления на шине КВУ соответствующего сиг- нала. По переднему фронту сигнала с шины КСИА триггер 10 переходит в единичное состояние, происходит запись кода адреса в регистр 6 адреса, и на стробирующие входы дешифраторов .7 и 8 подается разрешающий потенциал. Единичные уровни с выходов да- шифраторов 7 и 8 через шины 21 и 22 поступают на входы элемента И 39 выбранного блока 36.

Процессор 1 снимает адрес с шин КДА. и очищает шину КВУ.-Далее процессор 1 помещает на шины КДА данные и (с задержкой порядка 100 не) вырабатывает сигнал на шине Квывод, которьш через элемент И 14 и через элемент ИЛИ 15 поступает на вход элемента-запрета 16, а также разрешает прохождение информации через группу передающих ключей 4 на группу шин 20 данных. Единичньй уровень с выхода элемента К 39 поступает на вход элеме нта И 40 и вход элемента НЕ 42, на выходе которого появляется нулевой (разрешаннций) потенциал, поступающий через шину 25 на запрещающий вход элемента 16 за- прета. Сигнал с выхода элемента ИЛИ 15 через элемент запрета 16 и элемент ИЛИ 12 поступает на установочный вход счетчика 17, давая ему разрешение на счет импульсов. Через определенное время, регулируемое коэффициентом пересчета счетчика 17, на первом выходе его появляется еди

, ю

is 0 5 о

5

0

ничныи уровень, который через элемент И 19 поступает на шину 24 Вывод и далее на перв ый вход элемента И 40. К этому моменту времени на

группе шин 20 данных должны закончиться все переходные процессы и переключиться КМОП-ключи на входах регистра 37, которые имея более низкое быстродействие, чем основные элементы, и большое входное сопро,- тивление, допускают значительное удаление внешних устройств без применения специальных кабелей связи, а также значительно увеличивают допускаемое их количество. При удалении внешних устройств КМОП-ключи необходимо также включать и на входах приемных ключей 5, которые соединены с группой шин 20 данньйс. Изменение потенциала на выходе элемента И 40 разрешает запись информации с шин 20 данных в регистр 37.

Затем на первом выходе счетчика 17 появляется сигнал, поступающий на шину КСИП. Процессор 1, получив этот сигнал, очищает шину Квьшод, что приводит к снятию сигнала на шине КСИП, и затем снимает информацию с шин КДА. и очищает шину КСИА. По окончанию импульса на шине КСИА формирователь 9 вырабатывает импульс небольшой длительности, который возвращает триггер 10 в исходное запрещающее состояние. На этом заканчивается цикл Вывод. Контроль наличия блока 36 происходит аналогично описанному.

Прерывание программы процессора 1 происходит следующим образом.

Блоки 36 связи, способные вызвать прерывание программы процессора 1, имеют триггер 44 готовности. Переход его в единичное (активное) состояние происходит одновременно с записью информации в регистр 38 по сигналу с шины 46. Единичный потенциал с выхода триггера 44, несущий информацию о том, -что блок 36 готов к передаче данных, поступает на одну из шин 26 группы и далее на вход одного из элементов И 30 группы и на Ьход одного из элементов И 34 группы. Сигналы с разных триггеров 44 готовности имеют разную приоритет

7

ность. Наивысший приоритет у сигнала, поступающего на Вход первого, элемента И 30 из группы, который на .фиг.1 изображен сверху, далее сверху-вниз приоритетность убывает. Регистр 29 защиты служит для разрешения или запрета прохождения сигналов прерывания от тех или иных триггеров 44 готовности. Для реализации этой функции в регистр 29 защиты в цикле Вывод записывается код защиты, который поступая на вторые входы группы элементов И 30, разрешает или запрещает прохождение сигналов от триггеров 44 готовности на входы блока 31 прерываний. При полном запрете прохождения всех сигналов через группу элементов И 30 процессор 1 может считывать состояние триггеров 44 в цикле Ввод че- ,рез группу элементов И 34. Для этого выбирается необходимый адрес,по которому срабатывает элемейт И 27, и далее по сигналу на шине Кввод сигнал с выхода элемента И 32 разрешает прохождение информации с выходов триггеров 44 на группу шин 20 данных и далее на шины КДА. Низкий потенциал на выходе элемента НЕ 33 разрешает формирование сигнала н

шине КСИП.

I

Если прерывания разрешены, то

потенциалы с выходов триггеров 44 поступают на группу входов 52 блока 31 (фиг.2). Далее инициативные сигналы поступают на входы коммутатора 47. Триггер 49 находится в разрешающем состоянии,, и тактовые импульсы с шины 56 через элемент И 50 поступают на вход счетчика 51. Код с выхода счетчика 51 поступает на адресные входы коммутатора 47, который последовательно переключает шины 52 на вход триггера 48 и вход триггера 49. При появлении инициативного сигнала на одном из входов коммутатора 47 этот сигнал в момент равенства кода счетчика 51 номеру этого входа появляется на его выходе и переводит триггер 49 в запрещающее состояние, а триггер 48 переводит в единичное состояние, которое поступит на шину КТПР. Далее процесс обработки сигнала прерьшания происходит аналогично описанному, за исключением того, что триггер 49 возвращается в исходное разрешающее состояние по любому сигналу на шине 23 Ввод.

0

5

11

с 5

0

5

5

0

5

0

7448

Формула изобретения 1. Устройство для сопряжения цифровой вычислительной машины с внешними устройствами, содержащее группу приемопередатчиков, регистр адреса, регистр защити, триггер, пер- вьш дешифратор адреса, шесть элементов И, три элемента ИЛИ, элемент НЕ, к блоков связи, причем каждый блок связи содержит регистр приема, регистр передачи, триггер готовности, три элемента И, элемент НЕ, при этом первые информационные входы-выходы приемопередатчиков группы подключены к информационной шине цифровой вычислительной машины, информационный вход регистра адреса подключен к адресному выходу цифровой электронновычислительной машины, синхровход триггера подключен к выходу синхронизации цифровой вычислительной машины, информационный вход триггера подключен к выходу обращения к внешнему устройртву цифровой вычислительной машины, первые входы первого и второго элементов ИЛИ подключены к выходу предоставления прерывания цифровой вычислительной машины, первые входы первого и второго элементов И подключены к выходам разрешения ввода и вьшода цифровой вычислительной машины соответственно, причем в каждом блоке связи информационные выходы регистра приема и входы регистра передачи подключены к информационным входам и информационным выходам внешнего устройства соответственно, вход записи регистра передачи соединен с единичным входом триггера готовности и подключен к управляющему выходу внешнего устройства, при этом вторые информационные входы-выходы приемопередатчиков группы соединены с информационными входами регистра защиты и регистров приема к блоков связи, первая группа выходов регистра адреса соединена с информационными входами первого дешифратора адреса, группа выходов которого соединена с первым входом т| етьего элемента И и первыми входами первых элементов И к блоков связи, выход триггера соединен с входом записи регистра адреса, стро- бирующим входом первого дешифратора адреса и вторыми входами первого и второго элементов И, выход второго элемента И соединен с первыми

решающими входами приемопередатчиков группы, первым входом третьего элемента ШШ и первым входом четвертого элемента И, выход которого соединен с первым входом пятого элемента И и первыми входами вторых элементов И к блоков связи, выход первого элемента И соединен с вторыми входами первого и третьего элементов ИЛИ, первым входом шестого элемента И и первыми входами третьих элементов И к блоков связи, выход первого элемента ИЛИ соединен с вторыми разрешающими входами приемопередатчиков группы, выход третьего элемента И соединен с входом элемента НЕ и вторыми входами шестого и пятого элементов И, выход пятого элемента И соединен с входом записи регистра защиты, при этом в каждом блоке связи выход первого элемента И соединен с входом элемента НЕ и вторыми входами третьего и второго элементов И, выход второго элемента И соединен с входом записи регистра приема, выхо третьего элемента И соединен с нулевым входом триггера готовност и, о т л и ч а ю щ е.е с я тем, что, с целью упрощения устройства, в него введены второй дешифратор адреса, . формирователь одиночных импульсов, элемент запрета, счетчик импульсов, блок прерываний, три группы элементов И, а в каждый блок связи введена группа элементов И, причем счет- |ный вход счетчика импульсов является тактовым входом устройства, первый разрядный выход счетчика импульсов подключен к входу синхронизации цифровой вычислительной машины, выход требования прерывания блока прерываний подключен к входу требования прерывания цифровой вычислительной машины, при этом выходы регистра защиты соединены с первыми входами элементов И первой группы, выходы которых соединены с информационными входами блока прерываний, информационные выходы которого соединены с первыми входами элементов второй группы, вторые входы которых соединены с первым входом первого элемента ШШ и входом сброса блока прерьшаний, установочный вход которого соединен с выходом первого элемента И, выход шестого элемента И соединен с первыми входами элемента И третьей группы, выходы

117441

которых и выходы элементов И второй группы, а также выходы элементов И группы к блоков связи соединены со вторыми информационными входами-вы- 5 ходами приемопередатчиков группы, выход формирователя одиночных импульсов соединен с нулевым входом триггера, выход третьего элемента ИЛИ соединен с первым входом элемента

10 запрета, выход которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с входом уст ановки счетчика импульсов, второй разрядный выход которого соеди15 нен с вторьгм входом четвертого элемента И, выход триггера соединен с стробирующим входом второго дешифратора адреса, вторая группа информационных выходов регистра адреса сое20 динена с информационными входами второго дешифратора адреса, выход которого соединен с вторым входом третьего элемента И и вторыми входами первых элементов И к блоков свя25 зи, выходы триггеров готовности к блоков связи соединены с соответствующими вторыми входами элементов И первой и третьей групп, выход элемента НЕ и выходы элементов НЕ к

блоков связи по схеме монтажного

ИЛИ соединены с вторым входом элемента запрета, при этом в каждом блоке связи выход третьего элемента И соединен с первыми входами элементов И группы, вторые входы которых соединены с выходами регистра передачи, тактовый вход блока прерываний подключен к тактовому входу устройства.

2. Устройство по п.1, отличающееся тем, что блок прерываний содержит коммутатор, счетчик, два триггера, элемент И, причем группа информационных входов

коммутатора образует информационные входы блока, группа выходов счетчика соединена с управляющими входами коммутатора и образует информационные выходы блока, выход первого триггера является выходом требования пре- рьшания блока, нулевой вход первого триггера является входом сброса блока, единичный вход второго триггера соединен с установочным входом

счетчика и является установочным входом блока, первый вход элемента И подключен к тактовому входу блока, при этом в блоке прерываний выход

коммутатора соединен с единичным входом первого триггера и нулевым входом второго триггера, выход ко 1211744

торого соединен с вторым входом элемента И, выход которого соединен с счетным входом счетчика.

52 52 52

47

.liHt

гУ

550W

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с внешними устройствами | 1988 |

|

SU1524062A2 |

| Устройство для сопряжения двух электронно-вычислительных машин с внешними абонентами | 1985 |

|

SU1264192A1 |

| Устройство для сопряжения двух микро эвм с общей памятью | 1985 |

|

SU1280643A1 |

| Устройство для сопряжения двух микроЭВМ с общей памятью | 1988 |

|

SU1674141A1 |

| Устройство для обмена информацией | 1985 |

|

SU1334151A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1605239A1 |

| Устройство для ввода информации от аналоговых датчиков | 1985 |

|

SU1310796A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения ЭВМ, имеющих единый канал обмена информации, например ЭВМ Электроника-60 с внешни- ми устройствами пользователя. Основной задачей изобретения является упрощение устройства и повышение его быстродействия. Устройство содержит группу приемопередатчиков, регистры адреса, дешифраторы адреса, формирователь одиночных импульсов, триггеры, элементы ИЛИ, элементы запрета, счетчик импульсов, регистр защиты, группы элементов И, блок прерываний,, элементы НЕ, группу блоков связи. 1 з.п. ф-лы, 5 ил. I (Л

| Устройство для сопряжения | 1978 |

|

SU746491A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения цифровойВычиСлиТЕльНОй МАшиНы C ВНЕшНиМиуСТРОйСТВАМи | 1979 |

|

SU849190A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| с | |||

| Способ образования азокрасителей на волокнах | 1918 |

|

SU152A1 |

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

Авторы

Даты

1986-02-15—Публикация

1984-08-27—Подача