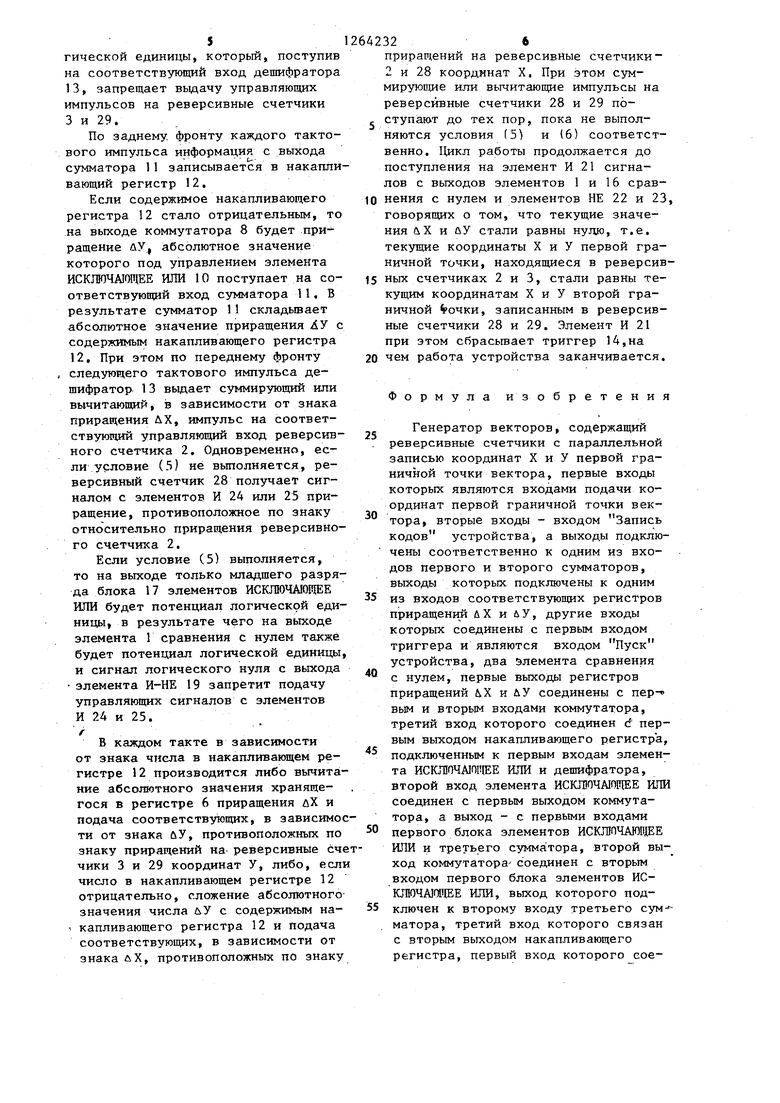

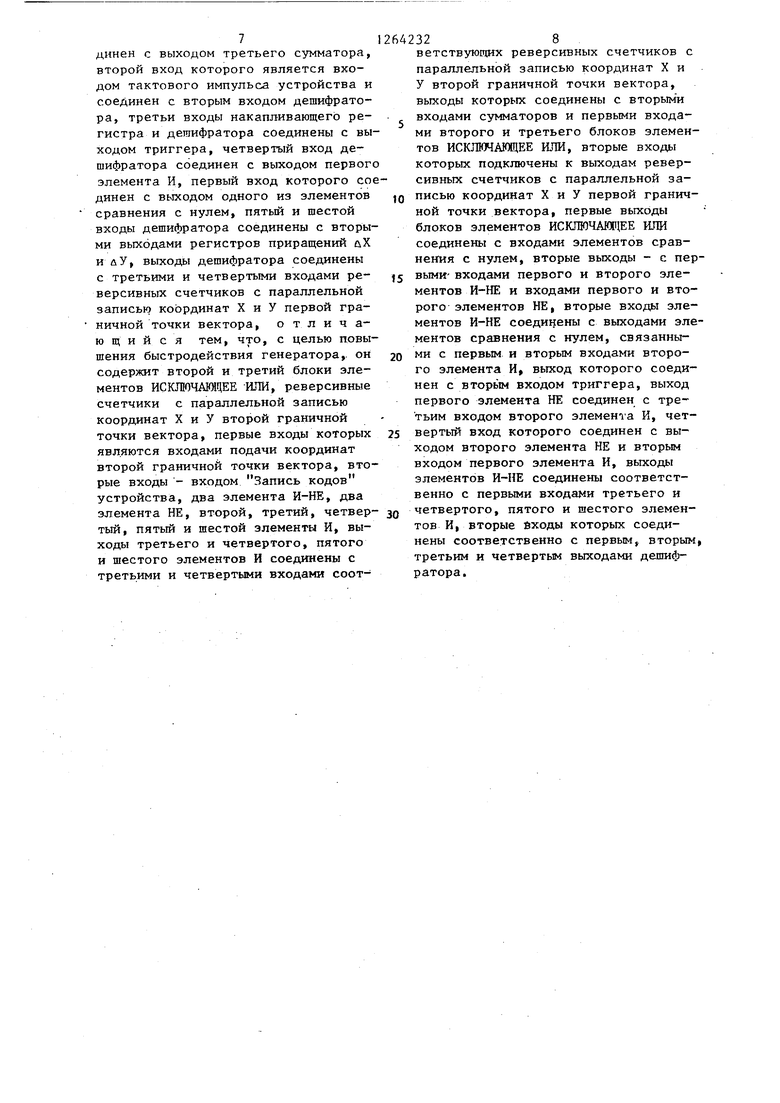

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построе нии генераторов векторов устройств для отображения графической информации . Цель изобретения - повьппение быстродействия генератора. На фиг. 1 представдЕна структурная схема генератора; на Фиг. 2 структурная схема дешифратора. Генератор векторов содержит первый элемент 1 сравнения с нулем, реверсивные счетчики 2 и 3 с параллельной записью координат X и У пер вой- граничной точки вектора, первый и второй сумматоры 4 и 5, регистры 6 и 7 приращений йХ и дУ, коммутатор 8, первый блок 9 элементов ИСКЛЮЧАЮЩЕ ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, третий сумматор 11, накапли вающий регистр 12, дешифратор 13, триггер 14, первый элемент И 15, второй элемент 16 сравнения с нулем, второй и третий блоки 17 и 18 элементов ИСКЛЮЧАЮ1ЧЕЕ ИЛИ, первый и второй элементы И-НЕ 19 и ,0, вто рой элемент И 21, первый и второй элементы НЕ 22 и 23, третий, четвер тый, пятый и шестой элементы И 2427, реверсивные счетчики 28 и 29 с параллельной записью координат X и У второй граничной точки вектора, вход 30 Запись кодов. Дешифратор 13 содержит (фиг. 2} четыре элемента НЕ 31-34 и четыре элемента И 35-38. Дешифратор имеет входы 39-44 и выходы 45-48. Сигналы с выходов 45 и 46 вызыва ют соответственно уменьшение и увеличение на еданицу содержимого реверсивного счетчика 3 и после прохо дения через элементы 26 и 27 И соответственно увеличение и уменьшение на единицу содержимого реверсивного счетчика 29, Аналогично сигналы с выходов 47 и 48 дешифрат ра 13 вызывают соответственно умен шение и увеличение на единицу соде жимого реверсивного счетчика 2 и после прохождения через элементы И 24 и 25 - соответственно увеличе ние И уменьшение на единицу содержимого реверсивного счетчика 28. Появление сигналов на выходах 4 48 дешифратора 13 описывается следующими выражениями: 2 вых. 45(вх. 39) Я1вх. % (вх. 42) Я (вх. 43)8 вх. 41Г) (1) вых. 46(вх. 39) (вх. 41)& (вх. 42) 8 (вх. 43)8((вх. 44); (2) вых. 47(вх. 39)3 (вх. 40) (вх. 42) а (вх. 43)8 ; (3) вых. 48(их. 39) S (вх. 40)8(вх. 42) а (вх. 43) . (it) Реверсивные счетчики 2 и 3, 28 и 29 с параллельной записью предназначены для приема и модификации в процессе генерации координат X. и Уд, Xg и Уц граничных точек вектора. Эти координаты во время работы устройства меняются, постоянно приближа ясь друг к другу. Сумматоры 4 и 5 Необходимы для вычисления приращений ЛХ и лУ, которые подаются на регистры 6 и 7 приращений. Блоки 17 и 18 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы 1 и 16 сравнения с нулем, элементы И-НЕ 19 и 20 соответственно предназначены для определения условий: luXl ii (5) МУ| 1. (6) Элемент И 15 позволяет определить момент равенства нулю приращения л У и подать управляющий сигнал на шестой вход дешифратора 13. Элементы НЕ 22 и 23 и элемент И 21 необходимы для определения момента равенства нулю приращений лХ и ДУ и подачи сбрасывающего сигнала на триггер 14. Коммутатор 8 приращений произво- дит подключение кодов приращений лХ и ДУ в зависимости от знака числа в накапливакицем регистре 12. Если содержимое накапливающего регистра 12 положительно или равно нулю то на входаг сзгмматора 11 через блок 9 элементов ИСКЛЮЧА1ОДЕЕ ИЛИ поступит абсолютное значение приращения ДХ со знаком минус, а если содержимое накапливающего регистра 12 отрицательнЬ, то абсолютное значение прираще- ния UУ со знаком плюс. Установку знака абсолютного значения лХ и дУ производит управляемый в зависимости от знака исходного приращения дХ и ДУ и знака числа

в накапливающем регистре 12 элемент ИСКЛЮЧАЮШЕЕ ИЛИ 10.

Дешифратор 13 предназначен для подачи импульсов суммирования или вычитания на реверсные счетчики 5 2 и 3 координат X и У первой граничной точки. Распределение импульсов по выходам дешифратора осуществляется в зависимости от знаков приращений, поступающих с регистров 6 и Ю 7, и от текущего знака с инверсного выхода накапливающего регистра 12,

Элементы И 24-27 необходимы для подачи импульсов вычитания или суммирования на реверсивные счетчи- 15 ки 28 и 29 координат X и У второй граничной точки. Подача этих импульсов осуществляется при невыполнении условий (З) и (б).

Триггер 14 служит для формирова- 20 ния цикла работы устройства от момента прихода импульса на внешний вход Пуск до прихода сбрасьшающего сигнала с выхода элемента И 21. Триггер 14 обнуляет накапливающий регистр 25 12 и запрешает появление на выходах дешифратора 13 импульсов после окончания работы устройства.

Устройство работает следующим образом.30

С входов Хд, Уд, Xg, У по сигналу Запись кодов в реверсивные счетчики 2, 3, 28 и 29 вводятся значения кодов X и У граничных точек вектора. Сумматоры 4 и 5 производят , вычисление л и & -Уд , после чего по сигналу Пуск значения йХ и дУ записываются соответственно в регистры 6 и 7 приращений и триггер 14 устанавливается в состояние Q логической единицы, что указывает на начало работы устройства.

При этом с управляющего входа накапливающего регистра 12 и одного из входов дешифратора 13 исчезает сиг- нал установки в нуль. Потенциал логической единицы с инверсного выхода знакового разряда накапливающего регистра 12 поступает на управляющий вход коммутатора 8 и на 50 соответствующий вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10, в результате чего на выходе коммутатора 8 будет приращение ЛХ. При этом если приращение лХ отрицательно, то с выхода элемента 55 ИСКЛЮЧАЮЩЕЕ ИЛИ Ш на вход переноса сумматора 11 и на соответствующие йходы блока 9 элементов ИСКЛЮЧАИНЕЕ

ИЛИ поступает потенп.иал логической единицы, в результате чего на соответствующем входе сумматора 1I появляется проинвертированное значени приращения йХ. Если же приращение дХ положительно или равно нулю, то под управлением элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 на вход переноса сумматора 11 поступает потенциал логичекого нуля, а на соответствующий информационный вход - прнр.ящение лХ без преобразования.

Таким образом, если содержимое накапливающего регистра 12 положительно или равно нулю, то суммато 11 вьгчитает абсолютное значение приращения Л X из содержимого накапливающего регистра 12.

По переднему фронту внешнего тактового импульса, если содержимое накапливающего регистра 12 не отрицательно и приращение дУ не равно нулю, дешифратор 13 подает на управляющие входы реверсивного счетчика 3 суммирующий или вычитающий импульс в зависимости от знака приращения ДУ. При этом если условие (6) не выполняется, то на управляющие входы реверсивного счетчика 29 с выхода элементов И 26 или 27 поступает вычитающий или суммирующий импульс. В результате реверсивный счетчик 29 получает приращение, противоположное по знаку относительно приращения реверсивного счетчика 3.

Если условие (6) вьтолняется, то на выходе только младшего разряда блока 18 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ будет логическая единица, поступаюпдая на соответствующий вход элемента И-НЕ 20, на другой вход которого поступает потенциал логической единицы с выхода элемента 16 сравнения с нулем. В результате этого на выходе элемента И-НЕ 20 будет потенциал логического нуля, который запрещает подачу управляюпщх импульсов с элементов И 26 и 27.

Если содержимое накапливающего регистра 12 не отрицательно и приращение д У равно нулю, то на выходе всех разрядов блока 18 элементов ИСКЛЮЧА101иЕЕ ИЛИ будет потенциал логического нуля, а на выходах элемента НЕ 22 и элемента 16 сравнения с нулем- - потенциал логической едини1 } 1, в результате чего на выходе элемента И 15 появляется потенциал логической единицы, который, поступив на соответствующий вход дешифратора 13, запрещает выдачу управляющих импульсов на реверсивные счетчики 3 и 29.

По заднему фронту каждого тактового импульса информация с выхода сумматора 11 записывается в накапливающий регистр 12,

Если содержимое накапливающего регистра 12 стало отрицательным, то на выходе коммутатора 8 будет приращение ДУ, абсолютное значение которого под управлением элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 поступает на соответствующий вход сумматора 11, В результате сумматор 11 складьшает абсолютное значение приращения ЛУ с содержимым накапливающего регистра 2, При этом по переднему фронту следующего тактового импульса дешифратор 13 выдает суммирующий или вычитаюш 1й, в зависимости от знака приращения ДХ, импульс на соответствующий управляющий вход реверсивного счетчика 2, Одновременно, если условие (5) не выполняется, реверсивный счетчик 28 получает сигналом с элементов И 24 или 25 приращение, противоположное по знаку относительно приращения реверсивного счетчика 2,

Если условие (5) выполняется, то на выходе только младшего разряда блока 17 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ будет потенциал логической единицы, в результате чего на выходе элемента 1 сравнения с нулем также будет потенциал логической единицы, и сигнал логического нуля с выхода элемента И-НЕ 19 запретит подачу управляющих сигналов с элементов И 24 и 25, V ,

В каждом такте в зависимости

от знака числа в накапливающем регистре 12 производится либо вычитание абсолютного значения хранящегося в регистре 6 приращения лХ и подача соответствующих, в зависимости от знака йУ, противоположных по знаку приращений на реверсивные счечики 3 и 29 координат У, либо, если число в накапливающем регистре 12 отрицатехп но, сложение абсолютногозначения числа лУ с содержимым на капливающего регистра 12 и подача соответствующих, в зависимости от знака дХ, противоположных по знаку

приращений на реверсивные счетчики 2 и 28 координат X, При этом суммируюпще или вычитающие импульсы на реверсивные счетчики 28 и 29 поступают до тех пор, пока не выполняются условия (5) и (6) соответственно. Цикл работы продолжается до поступления на элемент И 21 сигналов с выходов элементов 1 и 16 сравнения с нулем и элементов НЕ 22 и 23, говорящих о том, что текущие значения йХ и йУ стали равны нудю, т,е, текущие координаты X и У первой граничной точки, находящиеся в реверсивных счетчиках 2 и 3, стали равны текущим координатам X и У второй граничной %очки, записанным в реверсивные счетчики 28 и 29, Элемент И 21 при этом сбрасьшает триггер 14,на

чем работа устройства заканчивается.

Формула изобретения

Генератор векторов, содержащий реверсивные счетчики с параллельной записью координат X и У первой граничной точки вектора, первые входы которых являются входами подачи координат первой граничной точки вектора вторые входы - входом Запись кодов устройства, а выходы подключены соответственно к одним из входов первого и второго сумматоров, выходы которых подключены к одним из входов соответствующих регистров приращений йХ и &У, другие входы которых соединены с первым входом триггера и являются входом Пуск устройства, два элемента сравнения с нулем, первые выходы регистров приращений &Х и йУ соединены с пер- вым и вторым входами коммутатора, третий вход которого соединен rf первым выходом накапливающего регистра, подключенным к первым входам элемента ИСКЛЮЧА1ПЩЕ ИЛИ и дешифратора, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым выходом коммутатора, а выход - с первыми входами первого блока элементов ИСКШЛЧАЮП ЕЕ ИЛИ и третьего сумматора, второй выход коммутатора соединен с вторым входом первого блока элементов ИСКЛЮЧА ЩЕ ИЛИ, выход которого подключен к второму входу третьего сумматора, третий вход которого связан с вторым выходом накапливающего регистра, первый вход которого сое7

дннен с выходом третьего сумматора, второй вход которого является входом тактового импульса устройства и соединен с вторым входом дешифратора, третьи входы накапливающего регистра и дешифратора соединены с выходом триггера, четвертый вход дешифратора соединен с выходом первог элемента И, первый вход которого содинен с выходом одного из элементов сравнения с нулем, пятый и тестой входы дешифратора соединены с вторыми выходами регистров приращений лХ и дУ, выходы дешифратора соединены с третьими и четвертыми входами реверсивных счетчиков с параллельной записью координат X и У первой граничной точки вектора, о т л и ч аю щ и и с я тем, что, с целью повышения быстродействия генератора,, он содержит второй и третий блоки элементов ИСКЛЮЧАМЦЕЕ ИЛИ, реверсивные счетчики с параллельной записью координат X и У второй граничной точки вектора, первые входы которых являются входами подачи координат второй граничной точки вектора, вторые входы - входом Запись кодов устройства, два элемента И-НЕ, два элемента НЕ, второй, третий, четвертый, пятый и шестой элементы И, выходы третьего и четвертого, пятого и шестого элементов И соединены с третьими и четвертыми входами соот642328

ветствующих реверсивных счетчиков с параллельной записью координат X и У второй граничной точки вектора, выходы которых соединены с вторыми

входами сумматоров и первыми входами второго и третьего блоков элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых подключены к выходам реверсивных счетчиков с параллельной заJO писью координат X и У первой граничной точки вектора, первые выходы блоков элементов ИСКЛЮЧАЮРЩЕ ИЛИ соединены с входами элементов сравнения с нулем, вторые выходы - с перJ5 выми входами первого и второго элементов И-НЕ и входами первого и второго элементов НЕ, вторые входы элементов И-НЕ соединены с выходами элементов сравнения с нулем, связанны0 ми с первым и вторым входами второго элемента И, выход которого соединен с BTopbiM входом триггера, выход первого элемента НЕ соединен с третьим входом второго элеменча И, чет5 вертый вход которого соединен с выходом второго элемента НЕ и вторым входом первого элемента И, выходы элементов И-НЕ соединены соответственно с первыми входами третьего и

четвертого, пятого и шестого элементов И, вторые йходы которых соединены соответственно с первым, вторым, третьим и четвертым выходами дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор векторов | 1985 |

|

SU1278926A1 |

| Генератор векторов | 1986 |

|

SU1361613A1 |

| Генератор векторов | 1985 |

|

SU1300541A1 |

| Генератор векторов | 1988 |

|

SU1596375A2 |

| Генератор векторов | 1981 |

|

SU1010646A1 |

| Генератор векторов | 1987 |

|

SU1462403A1 |

| Устройство интерполяции для отображения графической информации | 1984 |

|

SU1164732A1 |

| Генератор векторов | 1989 |

|

SU1654863A1 |

| Устройство для определения координат траектории скважины | 1980 |

|

SU909145A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении генераторов векторов устройств для отображения графичес. кой информации. Цель изобретения повышение быстродействия генератора, которая достигается введением последовательно соединенных второй группы элементов ИСКЛЮЧАЮРдаР ИЛИ, первого элемента НЕ и второго элемента И, последовательно соединенных первого элемента И-НЕ,третьего элемента И и третьего реверсивного счетчика,, последовательно соединенных третьей группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, второго элемента И-НЕ, четвертого элемента И и четвертого с S реверсивного счетчика, второго элемента НЕ, пятого и шестого элемен(Л та И и соответствуклцих функциональных связей. 2 ил.

| Генератор векторов для системы отображения графической информации | 1974 |

|

SU525980A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор векторов | 1981 |

|

SU1010646A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1986-10-15—Публикация

1985-05-20—Подача