-UД

«I m

О

ел

Јь

00

оэ со

Яияяай,

027

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении систем отображения графической информации.

Цель изобретения - повышение точности генератора.

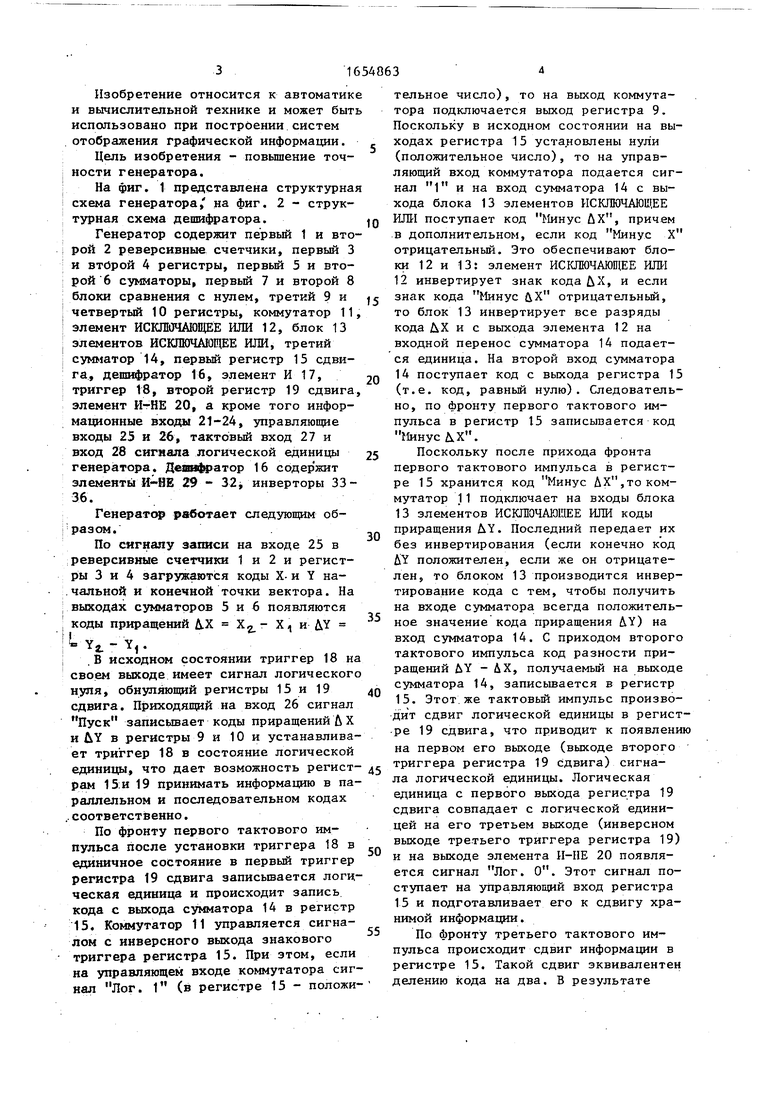

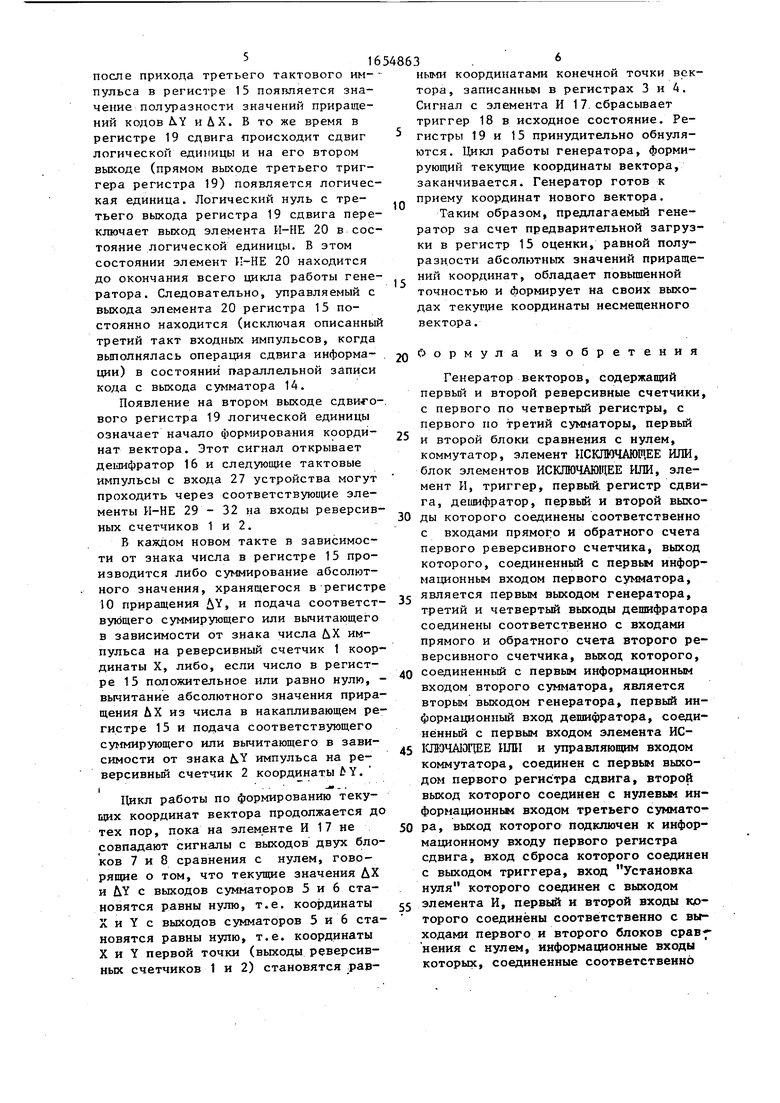

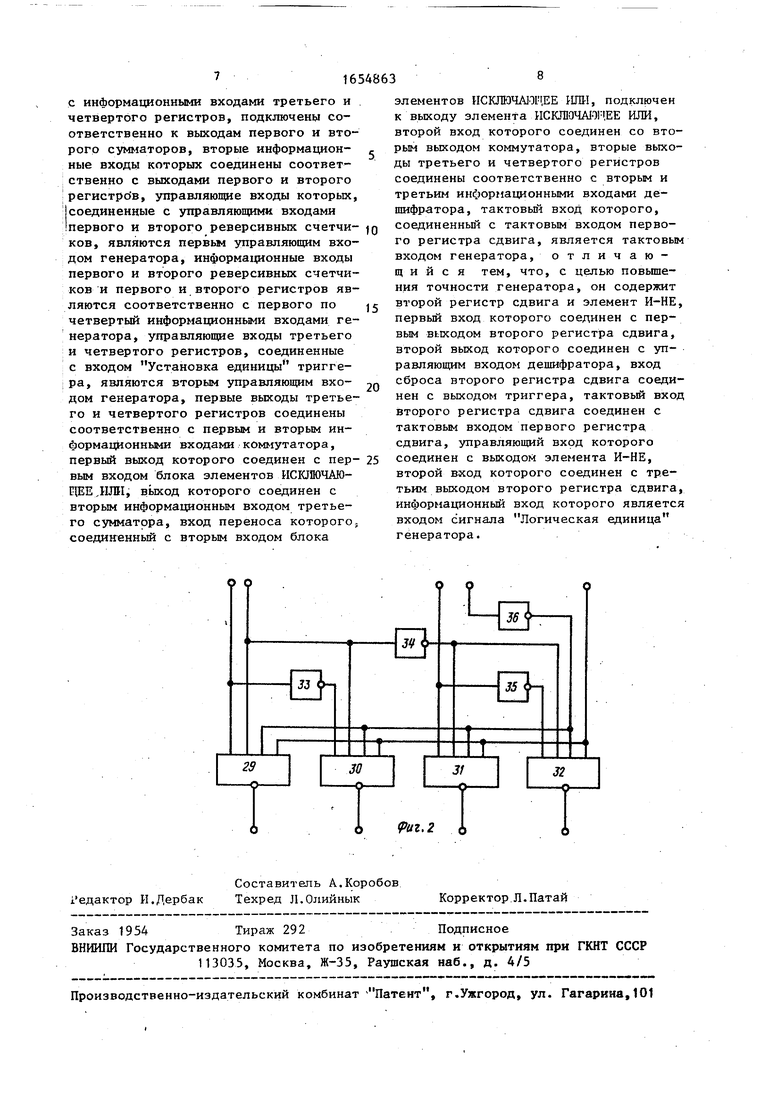

На фиг. 1 представлена структурная схема генератора, на фиг. 2 - структурная схема дешифратора.

Генератор содержит первый 1 и второй 2 реверсивные счетчики, первый 3 и второй 4 регистры, первый 5 и второй 6 сумматоры, первый 7 и второй 8 блоки сравнения с нулем, третий 9 и четвертый 10 регистры, коммутатор 11, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12, блок 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, третий сумматор 14, первый регистр 15 сдвига, дешифратор 16, элемент И 17, триггер 18, второй регистр 19 сдвига, элемент И-НЕ 20, а кроме того информационные входы 21-24, управляющие входы 25 и 26, тактовый вход 27 и вход 28 сигнала логической единицы генератора. Депюфратор 16 содержит элементы И-НЕ 29 - 32, инверторы 33- 36.

Генератор работает следующим образом.

По сигналу записи на входе 25 в реверсивные счетчики 1 и 2 и регистры 3 и 4 загружаются коды Х- и Y начальной и конечной точки вектора. На выходах сумматоров 5 и 6 появляются коды приращений U.X Xt-X,,H&Y

5 Yj.- Y,.

.В исходном состоянии триггер 18 на своем выходе имеет сигнал логического нуля, обнуляющий регистры 15 и 19 сдвига. Приходящий на вход 26 сигнал Пуск записывает коды приращений ft X и &Y в регистры 9 и 10 и устанавливает триггер 18 в состояние логической единицы, что дает возможность регистрам 15 и 19 принимать информацию в параллельном и последовательном кодах .соответственно.

По фронту первого тактового импульса после установки триггера 18 в единичное состояние в первый триггер регистра 19 сдвига записывается логическая единица и происходит запись кода с выхода сумматора 14 в регистр 15. Коммутатор 11 управляется сигналом с инверсного выхода знакового триггера регистра 15. При этом, если на управляющем входе коммутатора сигнал Лог. 1 (в регистре 15 - положи0

5

0

5

0

5

0

5

0

5

тельное число), то на выход коммутатора подключается выход регистра 9. Поскольку в исходном состоянии на выходах регистра 15 установлены нули (положительное число), то на управляющий вход коммутатора подается сигнал 1 и на вход сумматора 14 с выхода блока 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ поступает код Минус ДХ, причем в дополнительном, если код Минус X отрицательный. Это обеспечивают блоки 12 и 13: элемент ИСКЛЮЧАЮЩЕЕ ИЛИ

12инвертирует знак кода ДХ, и если знак кода Минус йХ отрицательный, то блок 13 инвертирует все разряды кода ДХ и с выхода элемента 12 на входной перенос сумматора 14 подается единица. На второй вход сумматора

14поступает код с выхода регистра 15 (т.е. код, равный нулю). Следовательно, по фронту первого тактового импульса в регистр 15 записывается код Минус ДХ.

Поскольку после прихода фронта первого тактового импульса в регистре 15 хранится код Минус ДХ,то коммутатор 11 подключает на входы блока

13элементов ИСКЛЮЧАЮЩЕЕ ИЛИ коды приращения ДҐ. Последний передает их без инвертирования (если конечно код № положителен, если же он отрицателен, то блоком 13 производится инвертирование кода с тем, чтобы получить на входе сумматора всегда положительное значение кода приращения AY) на вход сумматора 14. С приходом второго тактового импульса код разности приращений &Y - АХ, получаемый на выходе сумматора 14, записывается в регистр 15. Этот же тактовый импульс производит сдвиг логической единицы в регистре 19 сдвига, что приводит к появлению на первом его выходе (выходе второго триггера регистра 19 сдвига) сигнала логической единицы. Логическая единица с первого выхода регистра 19 сдвига совпадает с логической единицей на его третьем выходе (инверсном выходе третьего триггера регистра 19)

и на выходе элемента И-НЕ 20 появляется сигнал Лог. О. Этот сигнал поступает на управляющий вход регистра

15и подготавливает его к сдвигу хранимой информации.

По фронту третьего тактового импульса происходит сдвиг информации в регистре 15. Такой сдвиг эквивалентен делению кода на два. В результате

после прихода третьего тактового им-- пульса в регистре 15 появляется значение полуразности значений приращений кодов A.Y иДХ. В то же время в регистре 19 сдвига происходит сдвиг логической единицы и на его втором выходе (прямом выходе третьего триггера регистра 19) появляется логическая единица. Логический нуль с третьего выхода регистра 19 сдвига переключает выход элемента И-НЕ 20 в состояние логической единицы. В этом состоянии элемент Н-НЕ 20 находится до окончания всего цикла работы генератора. Следовательно, управляемый с выхода элемента 20 регистра 15 постоянно находится (исключая описанный третий такт входных импульсов, когда выполнялась операция сдвига информации) в состояний параллельной записи кода с выхода сумматора 14.

Появление на втором выходе сдвигового регистра 19 логической единицы означает начало формирования координат вектора. Этот сигнал открывает дешифратор 16 и следующие тактовые импульсы с входа 27 устройства могут проходить через соответствующие элементы И-НЕ 29-32 на входы реверсивных счетчиков 1 и 2.

В каждом новом такте в зависимости от знака числа в регистре 15 производится либо суммирование абсолютного значения, хранящегося в регистре 10 приращения &Y, и подача соответствующего суммирующего или вычитающего в зависимости от знака числа &Х импульса на реверсивный счетчик 1 координаты X, либо, если число в регистре 15 положительное или равно нулю, - вычитание абсолютного значения приращения ЛХ из числа в накапливающем регистре 15 и подача соответствующего суммирующего или вычитающего в зависимости от знака &Y импульса на реверсивный счетчик 2 координаты ЈY.

i--

Цикл работы по формированию текущих координат вектора продолжается до тех пор, пока на элементе И 17 не совпадают сигналы с выходов двух блоков 7 и 8 сравнения с нулем, говорящие о том, что текущие значения ДХ и &Y с выходов сумматоров 5 и 6 становятся равны нулю, т.е. координаты X и Y с выходов сумматоров 5 и 6 становятся равны нулю, т.е. координаты X и Y первой точки (выходы реверсивных счетчиков 1 и 2) становятся рав

ными координатами конечной точки вектора, записанным в регистрах 3 и 4. Сигнал с элемента И 17 сбрасывает триггер 18 в исходное состояние. Регистры 19 и 15 принудительно обнуляются. Цикл работы генератора, формирующий текущие координаты вектора, заканчивается. Генератор готов к приему координат нового вектора.

Таким образом, предлагаемый генератор за счет предварительной загрузки в регистр 15 оценки, равной полуразности абсолютных значений приращений координат, обладает повышенной точностью и Формирует на своих выходах текугще координаты несмещенного вектора.

Формула изобретения

Генератор векторов, содержащий первый и второй реверсивные счетчики, с первого по четвертый регистры, с первого по третий сумматоры, первый и второй блоки сравнения с нулем, коммутатор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И, триггер, первый, регистр сдвига, дешифратор, первый и второй выходы которого соединены соответственно с входами прямого и обратного счета первого реверсивного счетчика, выход которого, соединенный с первым информационным входом первого сумматора,

является первым выходом генератора, третий и четвертый выходы дешифратора соединены соответственно с входами прямого и обратного счета второго реверсивного счетчика, выход которого,

соединенный с первым информационным входом второго сумматора, является вторым выходом генератора, первый информационный вход дешифратора, соединенный с первым входом элемента ИСКЛЭЧАЮГЩЕ ИЛИ и управляющим входом коммутатора, соединен с первым выходом первого регистра сдвига, второй выход которого соединен с нулевым информационным входом третьего сумматора, выход которого подключен к информационному входу первого регистра сдвига, вход сброса которого соединен с выходом триггера, вход Установка нуля которого соединен с выходом

элемента И, первый и второй входы которого соединены соответственно с выходами первого и второго блоков нения с нулем, информационные входы которых, соединенные соответственно

с информационными входами третьего и четвертого регистров, подключены соответственно к выходам первого и второго сумматоров, вторые информацион- ные входы которых соединены соответственно с выходами первого и второго регистров, управляющие входы которых, соединенные с управляющими входами первого и второго реверсивных счетчи- ков, являются первым управляющим входом генератора, информационные входы первого и второго реверсивных счетчиков и первого и второго регистров являются соответственно с первого по четвертый информационными входами генератора, управляющие входы третьего и четвертого регистров, соединенные с входом Установка единицы триггера, являются вторым управляющим вхо- дом генератора, первые выходы третьего и четвертого регистров соединены соответственно с первым и вторым информационными входами коммутатора, первый выход которого соединен с пер- вым входом блока элементов ИСКЛЮЧАЮЩЕЕ,ИЛИ, выход которого соединен с вторым информационным входом третьего сумматора, вход переноса которого соединенный с вторым входом блока

элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен со вторым выходом коммутатора, вторые выходы третьего и четвертого регистров соединены соответственно с вторым и третьим информационными входами дешифратора, тактовый вход которого, соединенный с тактовым входом первого регистра сдвига, является тактовым входом генератора, отличающийся тем, что, с целью повышения точности генератора, он содержит второй регистр сдвига и элемент И-НЕ, первый вход которого соединен с первым выходом второго регистра сдвига, второй выход которого соединен с управляющим входом дешифратора, вход сброса второго регистра сдвига соединен с выходом триггера, тактовый вход второго регистра сдвига соединен с тактовым входом первого регистра сдвига, управляющий вход которого соединен с выходом элемента И-НЕ, второй вход которого соединен с третьим выходом второго регистра сдвига, информационный вход которого является входом сигнала Логическая единица генератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор векторов | 1985 |

|

SU1278926A1 |

| Генератор векторов | 1986 |

|

SU1361613A1 |

| Генератор векторов | 1985 |

|

SU1300541A1 |

| Генератор векторов | 1985 |

|

SU1264232A1 |

| Генератор векторов | 1981 |

|

SU1010646A1 |

| Генератор векторов | 1987 |

|

SU1462403A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

| Устройство интерполяции для отображения графической информации | 1984 |

|

SU1164732A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство для отображения кривых на экране электронно-лучевой трубки | 1988 |

|

SU1547022A1 |

Авторы

Даты

1991-06-07—Публикация

1989-02-07—Подача