Изобретение относится к нычисли- тельной технике и может быть использовано при построении устройств дпя отображения графической шгформации.

Цель изобретения - повышение точности генератора векторов„

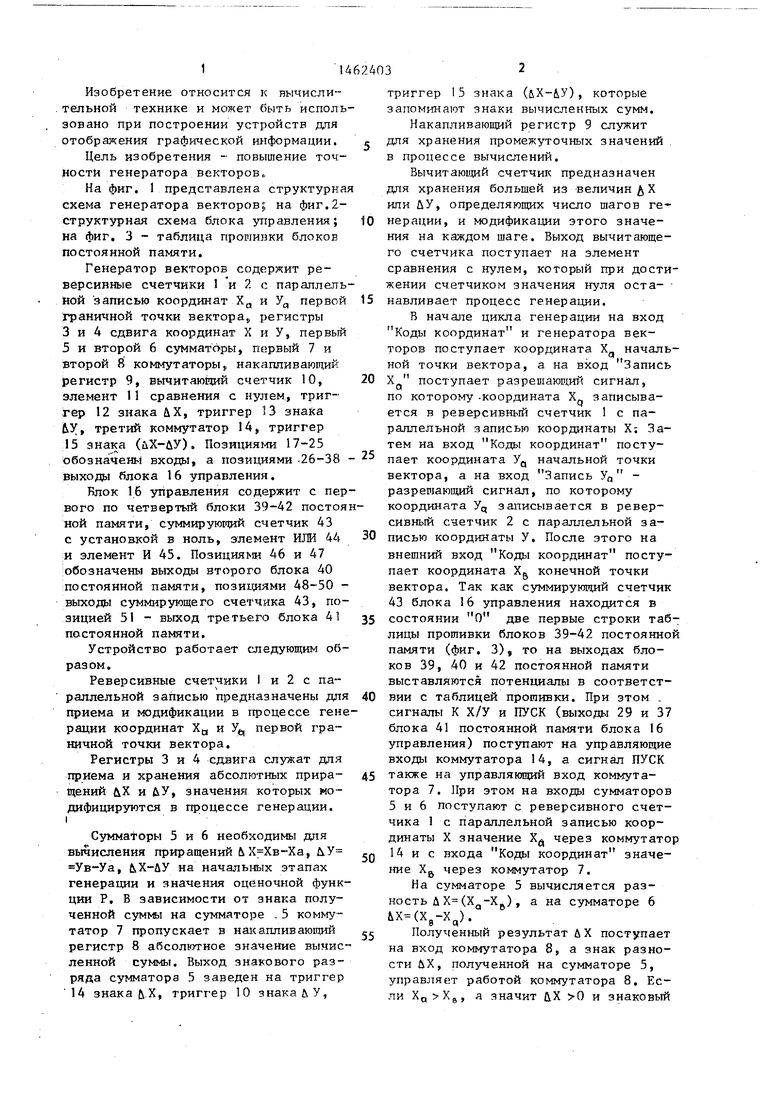

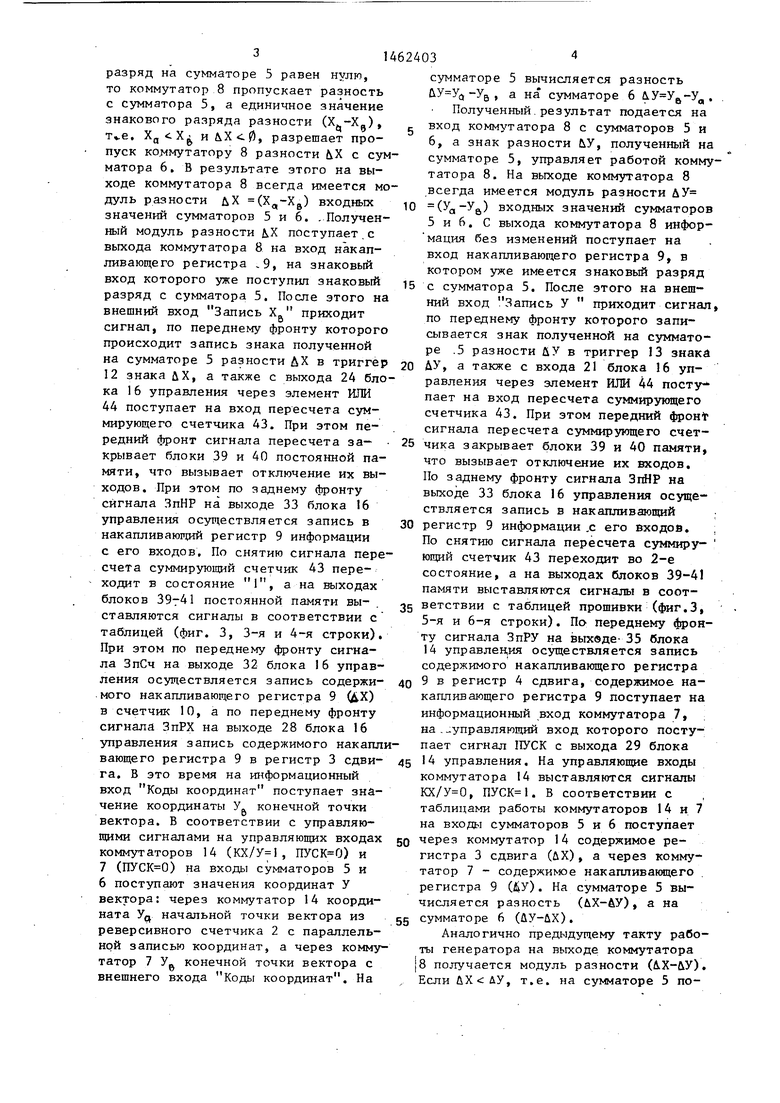

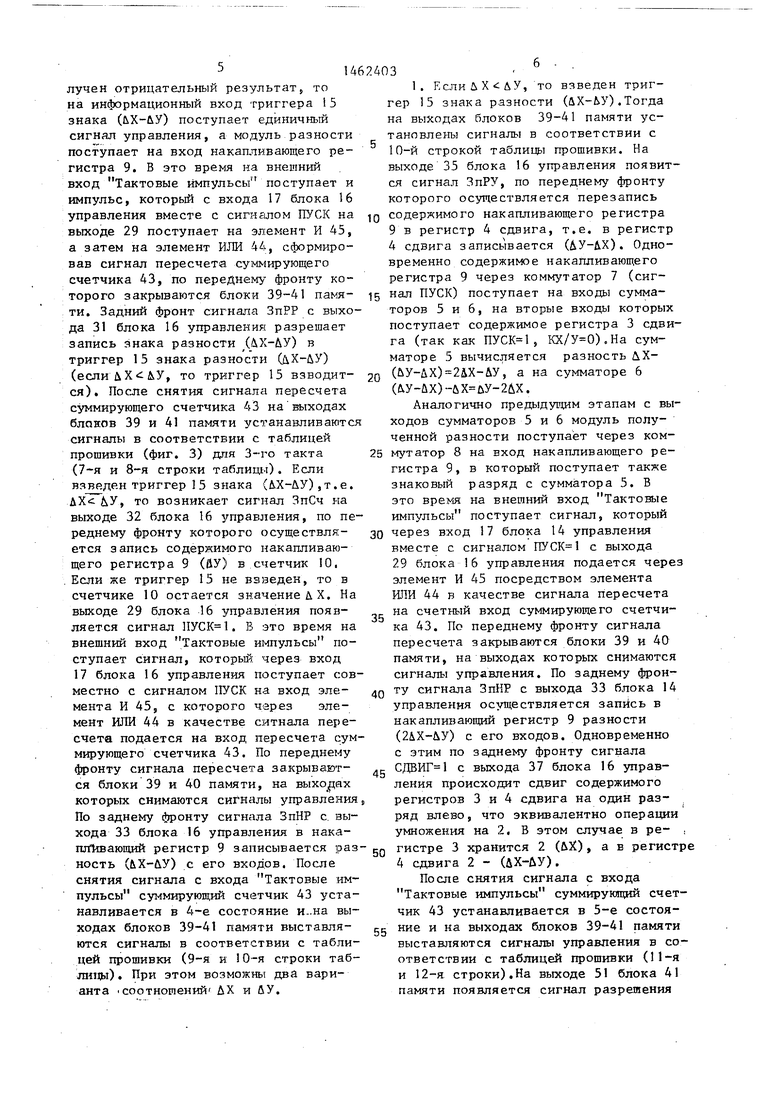

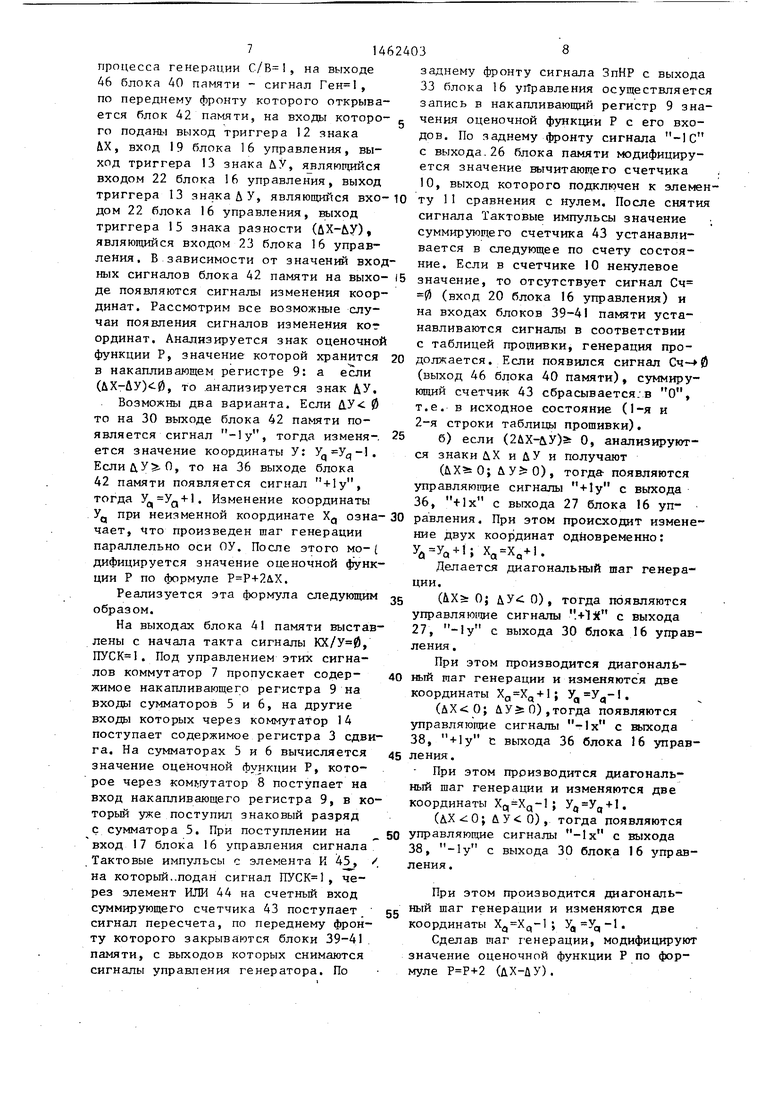

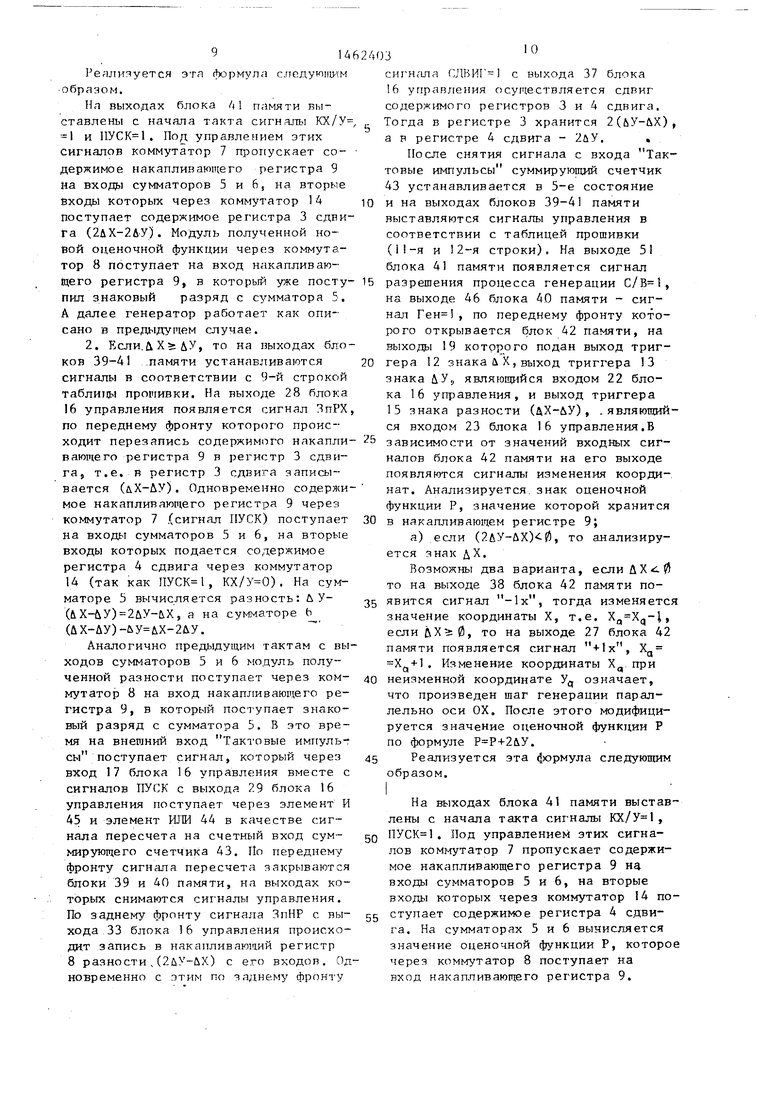

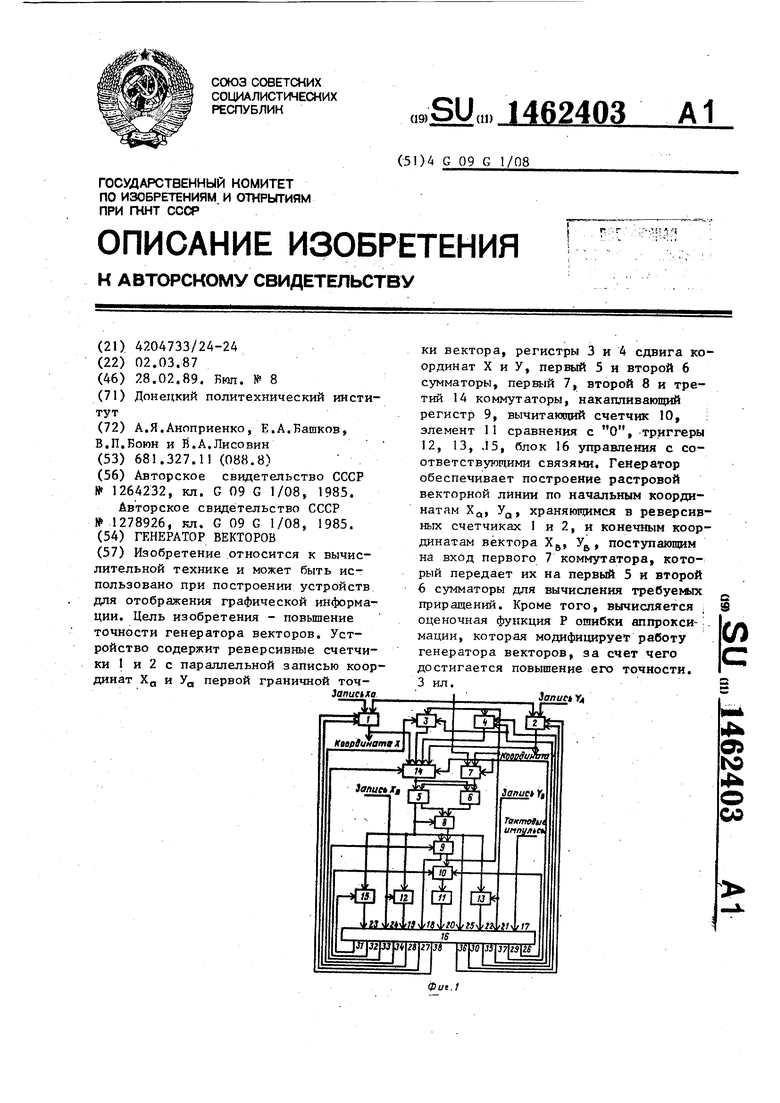

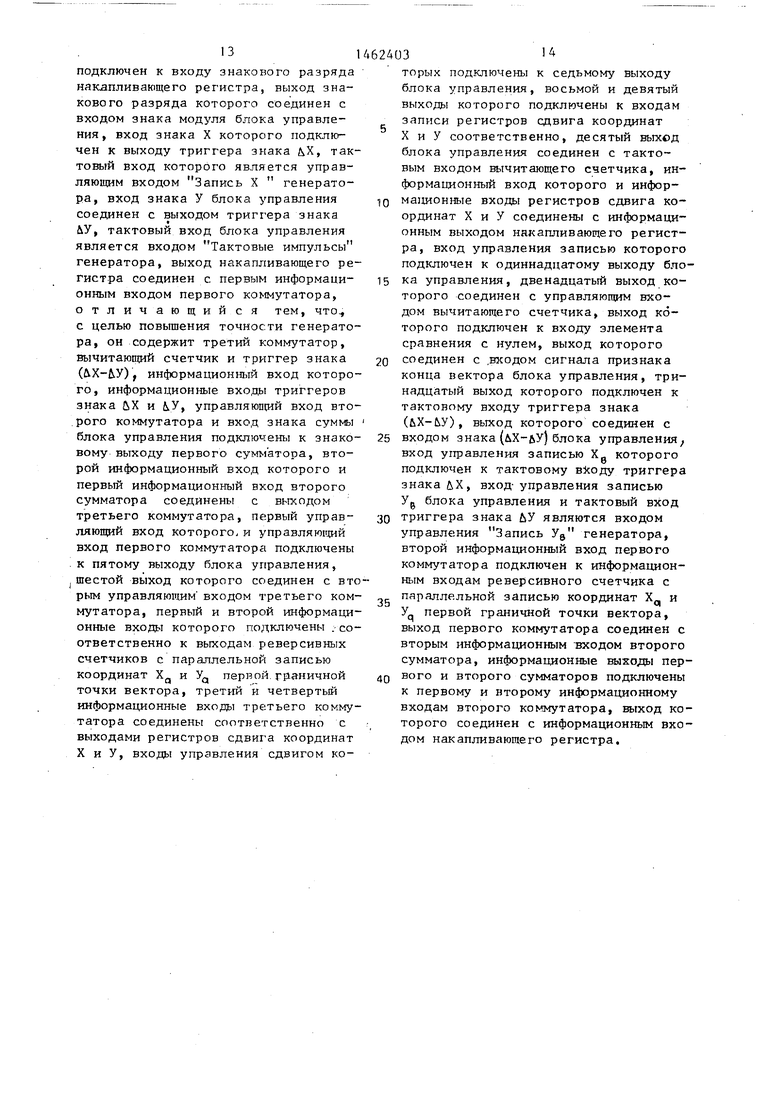

На фиг, 1 представлена структурная схема генератора векторов;; на фиг.2- структурная схема блока управления; на фиг. 3 - таблица прошиззки блоков постоянной памяти.

Генератор векторов содержит реверсивные счетчики 1 и . с параплелъ

триггер 15 знака (), которые запоминают знаки вычисленных сумм.

Накапливающий регистр 9 служит дпя хранения промежуточных значений в процессе вычислений.

Вычитающий счетчик предназначен для хранения большей из -величин X или ЛУ, определяющих число шагов генерации, и модификации этого значения на каждом шаге. Выход вычитающего счетчика поступает на элемент сравнения с нулем, который при достижении счетчиком значения нуля оста-

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор векторов | 1986 |

|

SU1361613A1 |

| Генератор векторов | 1985 |

|

SU1264232A1 |

| Генератор векторов | 1985 |

|

SU1300541A1 |

| Генератор векторов | 1985 |

|

SU1278926A1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| Цифровой интерполятор | 1986 |

|

SU1310778A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Генератор векторов | 1988 |

|

SU1596375A2 |

| Многокоординатный цифровой интерполятор | 1984 |

|

SU1200246A1 |

| Многокоординатный цифровой линейный интерполятор | 1987 |

|

SU1522154A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств для отображения графической информации. Цель изобретения - повышение точности генератора векторов. Устройство содержит реверсивные счетчики 1 и 2 с параллельной записью координат XQ и УО первой граничной точЗапиаха ки вектора, регистры 3 и 4 сдвига координат X и У, первый 5 и второй 6 сумматоры, первый 7, второй 8 и третий 14 коммутаторы, накапливающий регистр 9, вычитающий счетчик 10, элемент 11 сравнения с О, триггеры 12, 13, .15, блок 16 управления с соответствующими связями. Генератор обеспечивает построение растровой векторной линии по начальным координатам XQ, Уд, храняющимся в реверсивных счетчиках 1 и 2, и конечным координатам вектора Х, У, поступающим на вход первого 7 коммутатора, который передает их на первый 5 и второй 6 сумматоры для вычисления требуемьпс приращений. Кроме того, вычисляется ; оценочная функция Р ошибки аппрокси-|. мации, которая модифицирует работу генератора векторов, за счет чего достигается повышение его точности. 3 ил. (Л с Запись YJ 4i О N) 4 О СО

йой записью координат Xа и Уд первой 15 навливает процесс генерации. Граничной точки вектора, регистры В начале цикла генерации на вход 3 и 4 сдвига координат X и У, первый Коды координат и генератора век- 5 и второй 6 сумматоры, первый 7 и второй И коммутаторы, накапливающий регистр 9, вычитающий счетчик 10, 20 элемент 11 сравнения с нулем, триггер 12 знака йХ, триггер 13 знака 6,У, третий коммутатор 14, триггер

торов поступает координата Х началь Запись

по которому -координата Х записыванои точки вектора, а на вход

поступает разрев1аю1 ;ий сигнал,

15 знака (йХ-ДУ). Позициями 17-25

ется в реверсивный счетчик 1 с параллельной записью координаты X; За ..,тем на вход Коды координат постуобозначень входы, а позициями .26-38 - пает координата Уд начальной точки выходы блока 16 управления.вектора, а на вход Запись Уд Блок 16 управления содержит с разреиаюпщй сигнал, по которому вого по четвертый блоки 39-42 постоянной памяти, суммирующий счетчик 43

с установкой в ноль, элемент ИЛИ 44 и элемент И 45. Позициями 46 и 47 :обозначены выходы второго блока 40 постоянной памяти, позициями 48-50 - выходы суммирующего счетчика 43, позицией 51 - выход третьего блока 41 постоянной памяти.

Устройство работает следующим образом.

Реверсивные счетчики I и 2 с параллельной записью предназначены дпя приема и модификации в процессе генерации координат XQ и , первой граничной точки вектора.

Регистры 3 и 4 сдвига служат для приема и хранения абсолютных приращений йХ и йУ, значения которых модифицируются в гсроцессе генерации.

Сумматоры 5 и 6 необходимы для вычисления приращений &Х Хв-Ха, уУ Ув-Уа, 6,Х-йУ на начальных этапах генерации и значения оценочной функции Р. В зависимости от знака полученной суммы на сумматоре .5 коммутатор 7 пропускает в накапливающий регистр 8 абсолютное значение вычисленной суммы. Выход знакового разряда сумматора 5 заведен на триггер 14 знака ЬХ, триггер 10 знака и У,

30

координата У, записывается в реверсивный снетчик 2 с параллельной за40

писью координаты У. После этого на внещний вход Коды координат поступает координата Х конечной точки вектора. Так как суммирующий счетчик 43 блока 16 управления находится в 35 состоянии О две первые строки таблицы прошивки блоков 39-42 постоянной памяти (фиг. 3), то на выходах блоков 39, 40 и 42 постоянной памяти выставляются потенциалы в соответствии с таблицей прошивки. При этом сигналы К Х/У и ПУСК (выходы 29 и 37 блока 41 постоянной памяти блока 16 управления) поступают на управляющие входы коммутатора 14, а сигнал ПУСК также на управляющий вход коммутатора 7. При этом на входы сумматоров 5 и 6 поступают с реверсивного счетчика 1 с параллельной записью координаты X значение К через коммутатор 14 и с входа Коды координат значение Хц через коммутатор 7.

На сумматоре 5 вычисляется разность U Х () , а на сумматоре 6

&х(х,-х,).

55Полученный результатах поступает

на вход коммутатора 8, а знак разности ЛХ, полученной на сумматоре 5, управлябгг работой коммутатора 8. Если Х(,Х, а значит йХ 0 и знаковый

45

50

навливает процесс генерации. В начале цикла генерации на вход Коды координат и генератора век-

торов поступает координата Х началь Запись

по которому -координата Х записыванои точки вектора, а на вход

поступает разрев1аю1 ;ий сигнал,

ется в реверсивный счетчик 1 с параллельной записью координаты X; Заразреиаюпщй сигнал, по которому 0

координата У, записывается в реверсивный снетчик 2 с параллельной за0

писью координаты У. После этого на внещний вход Коды координат поступает координата Х конечной точки вектора. Так как суммирующий счетчик 43 блока 16 управления находится в 5 состоянии О две первые строки таблицы прошивки блоков 39-42 постоянной памяти (фиг. 3), то на выходах блоков 39, 40 и 42 постоянной памяти выставляются потенциалы в соответствии с таблицей прошивки. При этом сигналы К Х/У и ПУСК (выходы 29 и 37 блока 41 постоянной памяти блока 16 управления) поступают на управляющие входы коммутатора 14, а сигнал ПУСК также на управляющий вход коммутатора 7. При этом на входы сумматоров 5 и 6 поступают с реверсивного счетчика 1 с параллельной записью координаты X значение К через коммутатор 14 и с входа Коды координат значение Хц через коммутатор 7.

На сумматоре 5 вычисляется разность U Х () , а на сумматоре 6

&х(х,-х,).

5Полученный результатах поступает

на вход коммутатора 8, а знак разности ЛХ, полученной на сумматоре 5, управлябгг работой коммутатора 8. Если Х(,Х, а значит йХ 0 и знаковый

5

0

разряд на сумматоре 5 равен нулю, то коммутатор 8 пропускает разность с сумматора 5, а единичное значение знакового разряда разности (Х,-Хд), Tve. ХдСХ , разрешает пропуск ко.ммутатору 8 разности Х с сумматора 6. В результате этого на выходе коммутатора 8 всегда имеется модуль разности йХ (Х,-Хц) входных значений сумматоров 5 и 6. .Полученный модуль разности Х поступает,с выхода коммутатора 8 на вход накапливающего регистра .9, на знаковый вход которого уже поступил знаковый разряд с сумматора 5. После этого на внешний вход Запись X приходит сигнал, по переднему фронту которого происходит запись знака полученной на сумматоре 5 разности ДХ в триггер 12 знака йХ, а также с выхода 24 блока 16 управления через элемент ИЛИ 44 поступает на вход пересчета суммирующего счетчика 43. При этом передний фронт сигнала пересчета за- крывает блоки 39 и 40 постоянной памяти, что вызывает отключение их выходов. При этом по заднему фронту сигнала ЗпНР на выходе 33 блока 16 управления осутцествляется запись в накапливаюрщй регистр 9 информации с его входов. По снятию сигнала пересчета суммирующий счетчик 43 переходит в состояние 1, а на выходах блоков 39741 постоянной памяти выставляются сигналь в соответствии с таблицей (фиг. 3, 3-я и 4-я строки). При этом по переднему фронту сигнала ЗпСч на выходе 32 блока 16 управления осуществляется запись содержимого накапливающего регистра 9 OiX) в счетчик 10, а по переднему фронту сигнала ЗпРХ на выходе 28 блока 16 управления запись содержимого накаплвающего регистра 9 в регистр 3 сдвига. В это время на информационный вход Коды координат поступает значение координаты У конечной точки вектора. В соответствии с управляющими сигналами на управляющих входах коммутаторов 14 (, ) и 7 () на входы сумматоров 5 и 6 поступают значения координат У вектора: через коммутатор 14 координата У начальной точки вектора из реверсивного счетчика 2 с параллельной записью координат, а через коммутатор 7 У конечной точки вектора с внешнего входа Коды координат. На

сумматоре 5 вычисляется разность йУ Уо-Ув, а на сумматоре 6 У Ув-Уа . Полученный.результат подается на

g вход коммутатора 8 с сумматоров 5 и 6, а знак разности ЬУ, полученный на сумматоре 5, управляет работой коммутатора 8. На выходе коммутатора 8 всегда имеется модуль разности ДУ

10 ( входных значений сумматоров 5 и 6. С выхода коммутатора 8 инфор- мация без изменений поступает на вход накапливающего регистра 9, в котором уже имеется знаковьй разряд

15 с сумматора 5. После этого на внешний вход Запись У приходит сигнал,

по переднему фронту которого записывается знак полученной на сумматоре .5 разности йУ в триггер 13 знака

20 ДУ, а также с входа 21 блока 16 управления через элемент ИЛИ 44 поступает на вход пересчета суммирзтощего счетчика 43. При этом передний фрон сигнала пересчета суммирующего счет- 25 чика закрывает блоки 39 и 40 памяти, что вызывает отключение их входов. По заднему фронту сигнала ЗгйР на выходе 33 блока 16 управления осуществляется запись в накапливающий

30 регистр 9 информации .с его входов. ; По снятию сигнала пересчета суммиру- ющий счетчик 43 переходит во 2-е состояние, а на выходах блоков 39-41 памяти выставляются сигналы в соот35 ветствии с таблицей прошивки (фиг.3, 5-я и 6-я строки). Па переднему фронту сигнала ЗпРУ на выходе- 35 блока 14 управлеция осуществляется запись содержимого накапливающего регистра 9 в регистр 4 сдвига, содержимое накапливающего регистра 9 поступает на информационный вход коммутатора 7, на .„управляющий вход которого поступает сигнал ПУСК с выхода 29 блока

45 14 управления. На управляющие входы коммутатора 14 выставляются сигналы , . В соответствии с таблицами работы коммутаторов 14 и 7 на входы сумматоров 5 и 6 поступает

0 через коммутатор 14 содержимое регистра 3 сдвига (йХ), а через коммутатор 7 - содержимое накапливающего регистра 9 (У). На сумматоре 5 вычисляется разность (ЛХ-&У), а на

5 сумматоре 6 (йУ-ЛХ).

Аналогично предыдущему такту работы генератора на выходе коммутатора {в получается модуль разности (й.Х-йУ). Если , т.е. на сумматоре 5 по40

лучен отрицательный результатj то на информационный вход триггера 15 знака (ЬХ-йУ) поступает единичный сигнал управления, а модуль разности пост упает на вход накапливающего регистра 9. В это время на внегчний вход Тактовые 11мпульсы поступает и импульс, которьй с входа 17 блока 16 управления вместе с ПУСК на выходе 29 поступает на элемент И 45, а затем на элемент ИЛИ 44, сформировав сигнал пересчета суммирующего счетчика 43, по переднему фронту которого закрываются блоки 39-41 памяти. Задний фронт сигнала ЗпРР с выхо да 31 блока 16 управления разрешает запись знака разности (4Х-&У) в триггер 15 знака разности (ДХ-ДУ) (еслийХ &У, то триггер 15 взводится). После снятия сигнала пересчета суммирующего счетчика 43 на выходах блпнов 39 и 41 памяти устанавливаются сигналы в соответствии с таблицей прошивки (фиг. 3) для 3-го такта (7-я и 8-я строки таблищ.). Если взведен триггер 1 5 знака (&Х-АУ),т.е. , то возникает сигнал ЗпСч на выходе 32 блока 16 отравления, по переднему фронту которого осуществляется запись содержимого накапливающего регистра 9 (ЙУ) в счетчик 10, Если же триггер 15 не взведен, то в счетчике 10 остается значение ДХ, На выходе 29 блока 16 управления появляется сигнал . В это время на внешний вход Тактовые импульсы поступает сигнал, который: через вход 17 блока 16 управления поступает совместно с сигналом ПУСК на вход эпе- мента И 45, с которого через элемент ИЛИ 44 в качестве ситнала пересчета подается на вход пересчета суммирующего счетчика 43. По переднему фронту сигнала пересчета закрываются блоки 39 и 40 памяти, на которых снимаются сигналы управления s По заднему фронту сигнала ЗпНР с. выхода 33 блока 16 управления в накапливающий регистр 9 записывается разность (ЬХ-ЛУ) с его входов. После снятия сигнала с входа Тактовые импульсы су1 1мирующий счетчик 43 устанавливается в 4-е состояние и-.на выходах блоков 39-41 памяти выставляются сигналы в соответствии с таблицей прошивки (9-я и 10-я строки таб- лнньО При этом возможны два варианта Соотношений ДХ и йУ.

10

20

1462403,

Аналогично предь дуп1им этапам с выходов сумматоров 5 и 6 модуль полученной разности поступает через ком- 25 мутатор 8 на вход накапливающего регистра 9, в который поступает также знаковый разряд с сумматора 5. В это время на внешний вход Тактовые импульсы поступает сигнал, который через вход 17 блока 14 управления вместе с сигналом с выхода 29 блока 16 управления подается через элемент И 45 посредством элемента ИЛИ 44 в качестве сигнала Цересчета на счетный вход суммирующего счетчика 43. По переднему фронту сигнала пересчета закрываются блоки 39 и 40 памяти, на выходах которых снимаются сигналы управления. По заднему фронту сигнала ЗпНР с выхода 33 блока 14 управления осуществляется запись в накапливающий регистр 9 разности (2iX-&y) с его входов. Одновременно с этим по заднему фронту сигнала СДВИГ 1 с выхода 37 блока 16 управления происходит сдвиг содержимого регистров 3 и 4 сдвига на один раз- . ряд влево, что эквивалентно операции умножения на 2. В этом случае в ре- , гистре 3 хранится 2 (йХ), а в регистре 4 сдвига 2 - (йХ-йУ).

После снятия сигнала с входа Тактовые импульсы суммирующий счетчик 43 устанавливается в 5-е состоя- сц ние и на выходах блоков 39-41 памяти выставляются сигналы управления в соответствии с таблицей прощивки (11-я и 12-я строки).На выходе 51 блока 41 памяти появляется сигнал разрешения

30

35

40

45

50

714624038

процесса генерации С./В I , на выходезаднему фронту сигнала ЗпНР с выхода 46 блока 40 памяти - сигнал ,33 блока 16 угТравления осуществляется по переднему фронту которого открыва-запись в накапливающий регистр 9 знается блок 42 памяти, на входы которо- чения оценочной функции Р с его вхо- го поданы выход триггера 12 знакадов. По заднему фронту сигнала -1C &Х, вход 19 блока 16 управления, выход триггера 13 знака йУ, я вляющийся входом 22 блока 16 управления, выход

, г-ч- у „ - .,и, j.v л. v--j- w J. Ч- Jiv j jirj- dl л L3JAtlMt;n

триггера 13 знака Д У, являющиТгся вхо-ю ту 11 сравнения с нулем. После снятия дом 22 блока 16 управления, выходсигнала Тактовые импульсы значение

триггера 15 знака разности (йХ-ЛУ), являющийся входом 23 блока 16 управления. В зависимости от значений вход- ние. Если в счетчике 10 ненулевое ных сигналов блока 42 цамяти на выхо- (5 значение, то отсутствует сигнал Сч де появляются сигналы изменения коор-

динат. Рассмотрим все возможные случаи появления сигналов изменения кот- ординат. Анализируется знак оценочной

.,- J1I ,1д у J. ни и

функции Р, значение которой хранится 20 должается. Если появился сигнал Сч-40 в накапливающем регистре 9: а если(вьшод 46 блока 40 памяти), суммирус выхода.26 блока памяти модифицируется значение вычитающего счетчика 10, выход которого подключен к элекюн

суммирующего счетчика 43 устанавливается в следующее по счету состоя-0 (вход 20 блока 16 управления) и на входах блоков 39-41 памяти устанавливаются сигналы в соответствии с таблицей прощивки, генерация про(ЛХ-ЛУ)г10, то анализируется знак ДУ. Возможны два варианта. Если Л.У 0 то на 30 выходе блока 42 памяти появляется сигнал -1у, тогда изменя-. 25 ется значение координаты У: . Если U.У5 О, то на 36 выходе блока 42 памяти появляется сигнал +1у, тогда Изменение координаты

Го

ющий счетчик 43 сбрасывается:в О, т.е. в исходное состояние (1-я и 2-я строки таблицы прошивки),

б) если ()2j О, анализируются знаки Д.Х и ДУ и получают

(uX5sO; ), тогда- появляются управляюгще сигналы + 1у с выхода 36, tlx с выхода 27 блока 16 уп« ъл- т. --- ..--jt t. VfV 11

y при неизменной координате Хд озиа-30 равления. При этом происходит изменечает, что произведен шаг генерацииние двух координат одновременно:

параллельно оси ОУ. После этого мо-(УЛ У -f-l X Х +1.

дифицируется значение оценочной функ-Делаете диагональный шаг генерации Р по формуле ,Х.цки,

Реализуется эта формула следующим 35 (AXi 0; ), тогда появляются

образом.управляюгчие сигналы .+lj{ с выхода

На выходах блока 41 памяти выстав-27, -1у с выхода 30 блока 16 управлены с начала такта сигналы ,ления.

При этом производится диагональ- 40 ный таг генерации и изменяются две координаты Хд Хд+1; .

( ДУЭ:0),тогда появляются управляюпхие сигналы -1х с выхода 38, +1у с выхода 36 блока 16 управПУСК 1. Под управлением этих сигналов коммутатор 7 пропускает содержимое накапливающего регистра 9 на входы сумматоров 5 и 6, на другие входы которых через коммутатор 14 поступает содержимое регистра 3 сдвига. На сумматорах 5 и 6 вычисляется45 ления значение оценочной функции Р, кото-- При этом производится диагональ- рое через ком татор 8 поступает на„ый шаг генерации и изменяются две вход накапливающего регистра 9, в ко- координаты ; У.,У +1. торый уже поступил знаковый разряд( ), тогда появляются с сумматора 5. При поступлении надО управляющие сигналы -1х с выхода вход 17 блока 16 управления сигнала38, -1у с выхода 30 блока 16 управ- Тактовые импульсы с элемента К 45, /ления. на который..подан сигнал , через элемент ИЛИ 44 на счетный входПри этом производится диагональ- суммирующего счетчика 43 поступаетев ™ генерации и изменяются две сигнал пересчета, по переднему фрон-координаты ,-l ; i Ур-1. ту которого закрываются блоки 39-41.Сделав шаг генерации, модифицируют памяти, с выходов которых снимаютсязначение оценочной функции Р по фор- сигналы управления генератора. По муле (ДХ-ДУ).

заднему фронту сигнала ЗпНР с выхода 33 блока 16 угТравления осуществляется запись в накапливающий регистр 9 значения оценочной функции Р с его вхо- дов. По заднему фронту сигнала -1C

- у „ - .,и, j.v л. v--j- w J. Ч- Jiv j jirj- dl л L3JAtlMt;n

ту 11 сравнения с нулем. После снятия сигнала Тактовые импульсы значение

с выхода.26 блока памяти модифицируется значение вычитающего счетчика 10, выход которого подключен к элекюн ту 11 сравнения с нулем. После сняти сигнала Тактовые импульсы значение

ние. Если в счетчике 10 ненулевое значение, то отсутствует сигнал Сч

суммирующего счетчика 43 устанавливается в следующее по счету состоя ние. Если в счетчике 10 ненулевое значение, то отсутствует сигнал Сч

-.,- J1I ,1д у J. ни и

должается. Если появился сигнал Сч-4 (вьшод 46 блока 40 памяти), суммиру-0 (вход 20 блока 16 управления) и на входах блоков 39-41 памяти устанавливаются сигналы в соответствии с таблицей прощивки, генерация продолжается. Если появился сигнал Сч-4 (вьшод 46 блока 40 памяти), суммирующий счетчик 43 сбрасывается:в О, т.е. в исходное состояние (1-я и 2-я строки таблицы прошивки),

б) если ()2j О, анализируются знаки Д.Х и ДУ и получают

(uX5sO; ), тогда- появляются управляюгще сигналы + 1у с выхода 36, tlx с выхода 27 блока 16 уп т. --- ..--jt t. VfV 11

равления. При этом происходит изменеРеализуется эта формула слсдуюнц-ш образом.

На выходах блока 41 памяти выставлены с начала такта сигналы КХ/У, и 11УСК 1. Под управлением этих сигналов коммутатор 7 пропускает со- держимое накапливающего регистра 9 На входы сумматоров 5 и 6, на вторые Входы которых через коммутатор 14 поступает содержимое регистра 3 сдвига (2ДХ-2Л-У). Модуль полученной новой оценочной функции через коммутатор 8 поступает на вход накапливаю10

сиг Нс ша СЛВИГ 1 с выхода 37 блока 16 управления осу1ч.ествляется сдвиг содержимого регистров 3 и 4 сдвига, ц Тогда в регистре 3 хранится 2(&У-&Х), а в регистре 4 сдвига - 2йУ..

После снятия сигнала с входа Тактовые импульсы суммирующий счетчик 43 устанавливается в 5-е состояние и на выходах блоков 39-41 памяти выставляются сигналы управления в соответствии с таблицей прошивки (1i-я и 12-я строки). На выходе 51 блока 41 памяти появляется сигнал щего регистра 9, в который уже посту- 15 разрешения процесса генерации , пил знаковый разряд с сумматора 5.на выходе 46 блока 4.0 памяти - сигА далее генератор работает как описано в предыдущем случае.

(ЛХ-йУ)-; У ЛХ-2ДУ.еслийХ г0, то на выходе 27 блока 42

Аналогично пред,1дущим тактам с вы- памяти появляется сигнал -t-lx, Xg

„ при

нал Ген, по переднему фронту которого открывается блок 42 памяти, на выходы 19 которого подан выход триггера 12 знакаUХ,выход триггера 13 знака ДУ,, являющийся входом 22 блока 16 управления, и выход триггера 15 знака разности (йХ-ДУ), .являющийся входом 23 блока 16 управления.Б

25 зависимости от значений входных сигналов блока 42 памяти на его выходе появляются сигналь изменения координат. Анализируется, знак оценочной функции Р, значение которой хранится

30 в накапливающем регистре 9;

а) если (2йУ-ДХ)-(5, то анализируется знак ДХ.

Возможны два варианта, еслийХ 10 то на выходе 38 блока 42 памяти по35 явится сигнал -1х, тогда изменяется значение координаты X, т.е. X Хд-1,

ходов сумматоров 5 и 6 модуль полу Хд+1. Изменение координаты Х

ченной разности поступает через ком- 40 неизменной координате У означает.

мутатор 8 на вход накапливающего регистра 9, в который поступает знаковый разряд с сумматора 5. В это время на внешний вход Тактовые импульсы поступает сигнал, который через вход 17 блока 16 управления вместе с сигналов ПУСК с выхода 29 блока 16 управления поступает через элемент И 45 и элемент ИЛИ 44 в качестве сигнала пересчета на счетный вход суммирующего счетчика 43. По переднему фронту сигнала пересчета закрываются блоки 39 и 40 памяти, на выходах ко- тор.ых снимаются сигналы управления. По заднему фронту сигнала ЗпНР с выхода.33 блока 16 управления происхо- ди.т запись в накапливающий регистр 8 разности. (2йУ-ДХ) с е.го входов. Одновременно с этим по заднему фронту

45

что произведен шаг генерации параллельно оси ОХ. После этого модифицируется значение оценочной функции Р по формуле Р Р+2&У.

Реализуется эта 4 ормула следующим образом.

50

На выходах блока 41 памяти выставлены с начала такта сигналы , . Под управлением этих сигналов коммутатор 7 пропускает содержимое накапливающего регистра 9 на входы сумматоров 5 и 6, на вторые входы которых через коммутатор 14 по- gg ступает содержимое регистра 4 сдвига. На сумматорах 5 и 6 вычисляется значение оценочной функции Р, которое через коммутатор 8 поступает на вход накапливающего регистра 9.

еслийХ г0, то на выходе 27 блока 42

нал Ген, по переднему фронту которого открывается блок 42 памяти, на выходы 19 которого подан выход триггера 12 знакаUХ,выход триггера 13 знака ДУ,, являющийся входом 22 блока 16 управления, и выход триггера 15 знака разности (йХ-ДУ), .являющийся входом 23 блока 16 управления.Б

зависимости от значений входных сигналов блока 42 памяти на его выходе появляются сигналь изменения координат. Анализируется, знак оценочной функции Р, значение которой хранится

в накапливающем регистре 9;

а) если (2йУ-ДХ)-(5, то анализируется знак ДХ.

Возможны два варианта, еслийХ 10 то на выходе 38 блока 42 памяти появится сигнал -1х, тогда изменяется значение координаты X, т.е. X Хд-1,

памяти появляется сигнал -t-lx

„

Хд+1. Изменение координаты Х

неизменной координате У означ

что произведен шаг генерации параллельно оси ОХ. После этого модифицируется значение оценочной функции Р по формуле Р Р+2&У.

Реализуется эта 4 ормула следующим образом.

На выходах блока 41 памяти выставлены с начала такта сигналы , . Под управлением этих сигналов коммутатор 7 пропускает содержимое накапливающего регистра 9 на входы сумматоров 5 и 6, на вторые входы которых через коммутатор 14 по- ступает содержимое регистра 4 сдвига. На сумматорах 5 и 6 вычисляется значение оценочной функции Р, которое через коммутатор 8 поступает на вход накапливающего регистра 9.

Далее, как и в предыдущих случаях модифшщруется значение счетчика 10, анализируется его содержимое и осуществляется модификация оценочной функции.

б) Если (.&У-ЛХ)&0, то анализируется знак йХ и ДУ, результаты аналогичны случаю, когда и (2&Х- ЬУ)- О, появляются сигналь: изменения координат X и У„. Производится ди

агональный шаг генерации.

Сделав шаг генерации, модифицируется значение оценочной функции Р по формуле (CkX-йУ).

Реализуется эта формула следующим образом.

На выходах блока 41 памяти выставляются с начала такта сигналы КХ/У 0, . Под управлением этих сигналов коммутатор 7 пропускает содержимое накапливающего регистра 9 на входы сумматоров 5 и 6, на вторые входы которых через коммутатор 14 поступает содержимое регистра 4 сдви га (2АХ-2&У). Модуль полученной новой оценочной функции через коммутатор 8 поступает на вход накапливаю- щего регистра 9,в которьш уже поступил знаковый разряд с сумматора 5. Да- лее генератор работает,как описано- в предадущем случае.

Таким образом, в течение тактов 0-3 производится ввод координат граничных точек вектора, вычисляется приращение по координатам X иДУ, причем большее из вычисленных значений запоминается в счетчике 10, значение которого определяет число шагов генерации, а также значение разности (ДХ-ДУ), по знаку которой определяется октант, в котором производится генерация. В регистрах 3 и 4 сдвига хранятся значения: еслиДХ Л то в регистре 3 сдвига (ДХ-ДУ), в регистре 4 сдвига (ДУ) ; еслийХ сду, то в регистре 3 сдвига (ДХ), в регистре 4 сдвига (йУ-ДХ). При этом начальное значение оценочной функции Р, вычисленное на сумматорах 5 и 6, равно (2ДХ-йУ), еслиДХ йУ, иди (2ДУ-ДХ), еслийХ ДУ. В конце 4-го такта увеличивается вдвое содержимое регистров 3 и 4 сдвига. После этог начиная с 5-го такта в зависимости от знака оценочной функции Р и знаков LX ийУ производится шаг генерации. При этом если оценочная функция Р меньше 0, то делается шаг вдоль

2403

20

25 30

соответствующей оси, если же оценочная функция Р больше или равна 0, то делается диагональный шаг с одновременным изменением обеих координат. После этого модифицируется значение оценочной фyнкJ ии:

если&Х ДУ , то Р Р+2йХ,

еслийХЭ йУ, то ,+2ДУ 10 (при шаге вдоль оси координат);

если ДХ. tsy, то (ДХ-ЛУ) ;

еслиДХ5:ДУ, то (ДУ-ЛХ) (при диагональном шаге генерации).

После шага генерации уменьшается 15 на единищг значение счетчика 10. Процесс генерации прекращается по достижении счетчиком 10 значения 0.

Таким образом, изобретение повышает точность генератора векторов, поскольку выбираются точки, ближайшие к идеальной прямой, причем движение разрешено не только вдоль одной из осей координат, но и по диагонали .

Формула изобретения

Генератор векторов, содержащий реверсивные счетчики с параллельной записью координат Хд и Уд первой гра- ничной точки вектора, информационные входы которых являются входом координат первой граничной точки вектора генератора, регистры сдвига координат X и У, первый и второй сумматоры, первый и второй коммутаторы, накапливающий регистр, элемент сравнения с нулем, триггер ;.знака ДХ, триггер знака йУ и блок управления, входы записи реверсивных счетчиков с параллельной записью координат X и У первой граничной точки вектора являются входами управления записью Хд и 3{j генератора, выходами Координата X и Координата У которогб являются соответственно выходы реверсивных счетчиков с параллельной записью координат Xjj и Уц первой граничной точки вектора, тактовые входы которых подключены соответственно к первому и второму выходам блока управления, третий и четвертый выходы которого соединены с вычитающими входами реверсивных счетчиков с параллельной записью координат Хд и У, первой граничной точки вектора, выход первого коммутатора соединен с первым информационным входом первого сумматора, выход знакового разряда которого

1314

подключен к входу знакового разряда накапливающего регистра, выход знакового разряда которого соединен с входом знака модуля блока управления, вход знака X которого подклкг- ен к выходу триггера знака Х, тактовый вход которого является управяющим входом Запись X генератоа, вход знака У блока управления соединен с выходом триггера знака &У, тактовый вход блока управления вляется входом Тактовые импульсы генератора, выход накапливающего регистра соединен с первым информационным входом первого коммутатора, тличающийся тем, что с целью повышения точности генератора, он содержит третий коммутатор, вычитающий счетчик и триггер знака ()J информационный вход которого, информационные вхо,цы триггеров знака йХ и &.У, управляюпсий вход втоого коммутатора и вход знака суммы блока управления подключены к знаковому выходу первого сумматора, второй информационный вход которого и первый информационный вход второго сумматора соединены с выходом третьего коммутатора, первый управяющий вход которого, и управляю1ций вход первого коммутатора подключены к пятому выходу блока управления,

шестой выход которого соединен с вторым управляющим входом третьего коммутатора, первый и второй информационные входы которого подключены .соответственно к выходам реверсивных счетчиков с параллельной записью координат Хд и У первой, граничной точки вектора, третий и четвертый информационные входы третьего коммутатора соединены соответственно с выходами регистров сдвига координат X и У, входы управления сдвигом ко3l

торых подключены к седьмому выходу блока управления, восьмой и девятый выходы которого подключены к входам

записи регистров сдвига координат X и У соответственно, десятый выход блока управления соединен с тактовым входом вычитающего счетчика, информационный вход которого и информационные входы регистров сдвига координат X и У соединены с информационным выходом накапливающего регистра, вход управления записью которого подключен к одиннадцатому выходу блока управления, двенадцатый выход которого соединен с управляющим входом вычитающего счетчика, выход которого подключен к входу элемента сравнения с нулем, выход которого

соединен с .шсодом сигнала признака конца вектора блока управления, тринадцатый выход которого подключен к тактовому входу триггера знака (&Х-ЬУ), выход которого соединен с

входом знака (лХ-ьУ)блока управления; вход управления записью Х которого подключен к тактовому триггера знака йХ, вход-управления записью Ур блока управления и тактовый вход

триггера знака йУ являются входом управления Запись Уд генератора, второй информационный вход первого коммутатора подключен к информационным входам реверсивного счетчика с

параллельной записью координат X и У первой граничной точки вектора, выход первого коммутатора соединен с вторым информационным входом второго сумматора, информационные выходы первого и второго сумматоров подключены к первому и второму информационному входам второго коммутатора, атход которого соединен с информационным входом накапливающего регистра.

2 11

21

г

5

V5

f f

tfl

1 г 5 1

J9

ф

J7

V ф ф

У У

J« 37 25 32 16

фиг. 2

1462403

/8

20

5f

25 23 /5 22

Ш1

i

ff2

7 If8

« iWiHVBH B

ф ф ф ф

27 31 J JO

| Генератор векторов | 1985 |

|

SU1264232A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Генератор векторов | 1985 |

|

SU1278926A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1989-02-28—Публикация

1987-03-02—Подача