И:1обретение относится к импульсной технике и может быть использовано в вычислительных устройствах и в устройствах автоматического управления. Целью изобретения является расширение функциональных возможностей путем обеспечения возможности фильтрации помех и записи сбойной ситуации, т.е. возможности фиксации состояния входов устройства при сбое для последующего анализа. На фиг.1 приведена функциональная схема устройства для контроля последовательности импульсов и фильтрации помех; на фиг.2 - блок памяти. Устройство для контроля последова тёльности импульсов- и фильтрации помех (фиг.1) содержит блок 1 ввода, N первых элементов И 2, выходы которых являются первыми выходами 3 устройства, N вторых элементов И 4, выход каждого Из которых соединен с ин формационным входом соответствующего основного триггера 5, входы обнуления которых соединены, первый 6 и второй 7 элементы ИЛИ, блок 8 памяти блок 9 индикации, первый 10 и второй 11 формирователи, третий элемент И 12, дополнительный триггер 13, первый 14 и второй 15 элементы ИСКЛЮЧАЮ ЩЕЕ ИЛИ, первый вход первого из кото рых соединен с инверсным выходом дополнительного триггера 13, вход обну ления которого соединен с входами об нуления основных триггеров 5 и подключен к входу 16 обнуления устройст ва, тактовый вход подключен к тактовым входам основных триггеров 5, соединен с выходом первого элемента ИЛИ бис входами первого 10 и второ го 11 формирователей, прямой выход дополнительного триггера 13 соединен с первым входом третьего элемента И 12, второй вход которого соединен с выходом первого формирователя 10, а третий вход подключен к выходу второго элемента ИСКЛЮЧАНЦЕЕ ИЛИ 15 и к управляющему входу блока 8 памяти, информационные входы которого со- 50

единены с соответствующими входами блока 1 ввода и с первыми входами соответствующих первых элементов И 2, вторые входы которых соединены с прямыми выходами соответствующих основных триггеров 5, инверсный выход каждого из которых подключен к первому входу соответствующего второго элесостояния по щине сброса, устанавливающим в исходное состояние основные 5 и дополнительный 13 триггеры.

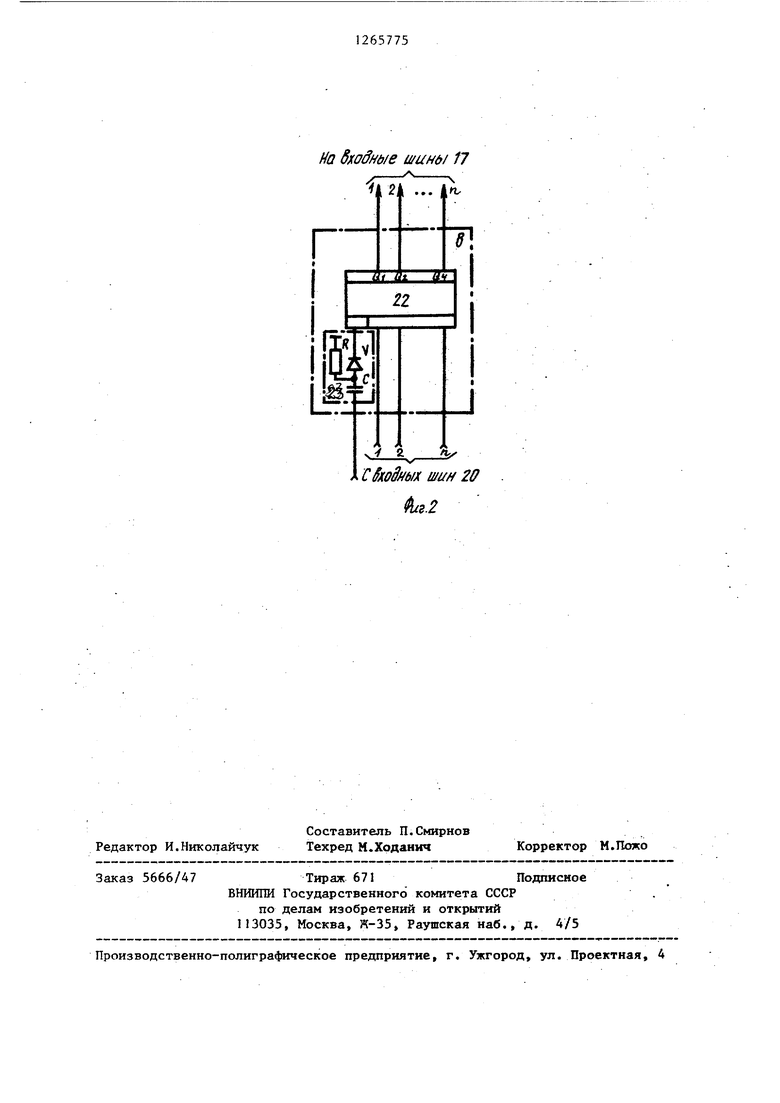

Прямые выходы основных триггеров 5 блоюяруют прохождение входных сигналов через все вторые элементы И 4, кроме первого, что обеспечивается наличием в цепи обратной связи от и-го мента И 4, второй вход каждого из которых соединен с соответствующим выходом блока ввода и с соответствующим входом второго элемента ИЛИ 7, выход которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15, второй вход которого подключен к выходу второго формирователя 11, третий вход первого из вторых элементов И соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14, третий вход каждого последующего из вторых элементов И соединен, с прямым выходом предыдущего основного триггера и с соответствующим входом блока 9 индикации, выход первого элемента ИСКЛЮЧАТ ЦЕЕ ИЛИ 14 соединен с дополнительным входом блока 9 индикации, выходы вторых элементов И соединены с соответствующими входами первого элемента ИЛИ 6, причем выходы блока 8 памяти являются вторыми выходами 17 устройства, выход третьего элемента И 1 2 является третьим выходом 18 устройства, выход второго элемента ИСКЛЮЧАЩЕЕ ИЛИ 15 является четвертым выходом 19 устройства, а информационными входами устройства являются соответствующие входы 20 блока 1 ввода, который содержит N формирователей 21, входы и выходы каждого из которых соединены соответственно с соответствующими входами и выходами блока 1 ввода. В состав устройства входит блок 8 памяти (фиг.2), который содержит регистр 22 с параллельным вводом информации и дифференцирующую цепь 23, вход которой соединен с управляющим входом блока 8 памяти, информационные входы регистра 22 соединены с информационными входами блока 8 памяти, выходы регистра 22 подключены к выходам блока 8 памяти, а выход дифференцирующей цепи 23 соединен с тактовым входом регистра 22. Устройство работает следующим образом. Исходное состояние устройства задается импульсом установки исходного 312 основного триггера 5 к первому из вторых элементу И 4.1 первого элемента ИСКЛОЧАПГДЕЕ ИЛИ 14, управляемого дополнительным триггером 13. В исходном состоянии этот элемент инвентирует потенциал прямого выхода h-го триггера. Первые элементы И 2 заблокированы потенциалами прямых выходов основных триггеров 5, поэтому на первых 3 сигналы отсутствуют. До прихода импульса на первый вход блока 1 ввода импульсы, приходящие на остальные входы блока 1 ввода не изменяют состояние основных и вспомогательных триггеров. В то же .время они проходят через второй элемент ИЛИ 7, вызывают изменение потенциала на выходе второго элемента ИСКЛЮЧАЮЩЕЕ ШШ 15 и соответственно на четвертом выходе 19 устройства, тем самым информируя о наличии сбоя по входным шинам. Это, однако, не вызывает появление сигнала Прерывание н-а третьем выходе 18 устройства, так как третий элемент И 12 закрыт потенциалом с прямого выхода дополнительного триггера 13. В блоке 8 памяти происходит запись состояния входных шин по сигналу Сбой. При приходе сигнала на первый вход блока 1 ввода входной сигнал поступает на вход первого из вторых элемента И 4.1, с выхода которого он поступает на информационный вход первого из основных триггеров 5. Тот же сигнал,прошедший через первый элемент ИЛИ 6, поступает на тактовые входы основных триггеров. Таким образом, происходит установка первого из основных триггера 5.1 в состояние 1. , Сигнал с прямого выхода этого триггера разрешает прохождение входного сигнала через первый элемент И 2.1 на выход устройства и подготавливает к работе второй из вторых элемент И 4.2. Потенциал с инверсного выхода первого из основных триггера 5.1, перейдя из состояния 1 к О, блокирует дальнейшее прохождение сигнала через первый из вторых элемент И 4.1. В момент прохождения полезного сигнала на четвертом выходе .19 устройства не вырабатывается сигнал Сбой, так как на выходах второго элемента ИЛИ 7 и второго формирова теля 11 образуется одинаковый потенциал. 5 Одновременно с переключением первого из основных триггеров переключается и дополнительный триггер 13. Его прямой выход разблокирует третий элемент И 12, а инверсный выход переводит первый элемент ИСКЛЮЧАЩЕЕ ИЛИ 14 в режим работы повторителя. При поочередном приходе входных им пульсов на входы блока 1 ввода происходит последовательное переключе.ние основных триггеров 5, она логичное описанному, что позволяет получить на выходах устройства последовательность импульсов, совпадающую с входной. Состояние основных триггеров 5 фиксируется блоком 9 индикации. При несвоевременном приходе сигнала по какому-либо из входов он не может поступить на вход первого элемента ИЛИ 6 и соответствующую выходную шину, так как вторые элементы И 4 оказываются заблокированными соответствующими основными триггерами. Этот ложный сигнап, пройдя через второй элемент ИЛИ 7, вызывает появление на выходе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 единичного сигнала, информирующего о сбое в канале. Состояние входов фиксируется в блоке 8 памяти. Однако сигнал Прерьгоание не вьфабатывается до тех пор, пока не окончится блокирующее действие выходного сигнала первого формирователя 10, запущенного предыдущим, своевременно пришедшим импульсом. Длительность сигнала первого формирователя 10 выбирается пользователем из условия, что она больше максимально ожидаемого интервала между вход- ными импульсами соседних каналов. Если за указанное время очередной ожидаемый импульс появляется, он снимает сигнал Сбой. и подтверждает запуск первого формирователя 10 на оче-i редкой период. В противном случае по окончании выходного сигнала формирователя на третьем выходе 18 Прерьгеание появляется сигнал, информирующий об устойчивом нарушении в контролируемой последовательности. В случае устойчивого отсутствия импульсов по одному из каналов устройство восприиимает следукнцие за ним импульсы как помеху, и происходит процесс, аналогичный описанному. Если в какой-либо момент времени в очередной канал приходит импульс. устройство снимает сигналы Сбой и Прерывание и продолжает процесс контроля. .Анализ сбоя можно провести, сравнивая информацию из блока 8 памяти . с состоянием блока 9 индикации. Формула изобретения 1, Устройство для контроля последовательности импульсов и фильтрации помех, содержащее блок ввода, N первых элементов И, выходы которых являются первыми выходами устройства N вторых элементов И, выход каждого из которых соединен с информационным входом -соответствующего основного триггера, входы обнуления которых со единены, первый и второй элементы ИЛИ, блок памяти, блок индикации, первый и второй формирователи, третий элемент И и дополнительный триггер, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения возможности фильтрации помех и фикса ции сбойной ситуации, в него введены первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход первого из которых соединен с инверсным выходом дополни тельного триггера, вход обнуления ко торого соединен с входами обнуления ОСНОВН.ЫХ триггеров и подключен к вхо ду обнуления устройства, тактовый вход подключен к тактовым входам основных триггеров, соединен с выходом первого элемента ИЛИ и с входами пер вого и второго формирователей, прямой выход дополнительного триггера соединен с первым входом третьего элемента И, второй вход которого соединен с выходом первого формировате ля, а третий вход подключен к выходу второго элемента ИСКЛЮЧАКЯЦЕЕ ИЛИ и к управляющему входу блока памяти, информационные входы которого соединены с соответствующими входами блока ввода и с первыми входами соответствзпощих первых элементов И, вторые входы которых соединены с прямыми выходами соответствующих основных триггеров, инверсный выход каждого из которых подключен к первом входу соответствующего второго элемента И, второй вход каждого из которых соединен,с соответствующим входом блока ввода и с соответствующим входом второго элемента ИЛИ, выход которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу второго формирователя, третий вход первого из вторых элементов И соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий вход каждого последун его из вторых элементов И, кроме первого, соединен с прямыми выходами предыдущего основного триггера и с соответсующим входом блока индикации, выход первого элемента ИСКЛЮЧАМЦЕЕ ИЛИ соединен с дополнительным входом блока индикации, выходы вторых элементов И соединены с соответствующими входами первого элемента ИЛИ, причем выходы блока памяти являются вторыми выходами устройства, выход третьего элемента И является третьим выходом устройства, выход второго элемента ИСКЛЮЧАЮЩЕЕ ШШ является четвертым выходом устройства, а информационными входами устройства являются соответствующие входы блока ввода. 2. Устройство по П.1, of.r л и чающееся тем, что блок Ьвода содержит N формирователей, входы и выходы каждого из которых соединены соответственно с соответствующими входами и выходами блока ввода.

На бхоЗнд/е шины /7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| УСТРОЙСТВО АКТИВНОЙ ЗАЩИТЫ И ОБЕСПЕЧЕНИЯ ТЕХНИЧЕСКОЙ ГОТОВНОСТИ ЭЛЕМЕНТОВ РАСПРЕДЕЛЕННОЙ ЛОКАЛЬНОЙ ВЫЧИСЛИТЕЛЬНОЙ СЕТИ В УСЛОВИЯХ ВНЕШНИХ ДЕСТРУКТИВНЫХ ВОЗДЕЙСТВИЙ | 2006 |

|

RU2316810C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Устройство для контроля программно-логических матриц | 1987 |

|

SU1469504A1 |

| УСТРОЙСТВО ДЛЯ АНАЛИЗА РОДОВОЙ ДЕЯТЕЛЬНОСТИ | 1998 |

|

RU2130645C1 |

| Устройство для выдачи команд об изменении движения транспорта | 1986 |

|

SU1446640A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство записи и воспроизведения двоичной информации на магнитной ленте | 1983 |

|

SU1117689A2 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Устройство для идентификации частиц | 1986 |

|

SU1382210A1 |

Изобретение может быть использовано в вычислительных устройствахи в устройствах автоматического управления. Цель изобретения - расширение функциональных возможностей устройства. Устройство контроля содержит блок 1 ввода, N элементов И 2 к 4, .триггеры 13 и 5, элементы ИЛИ 6 и 7, блок 8 памяти, блок 9 индикации, формирователи 10 и 11, элемент И 12. Введение в устройствб элементов ИСКЛОЧАВДЕЕ ИЛИ 14 и 15 и N формироа вателей 21 в блок 1 ввода, а также (Л образование новых функциональных связей между элементами устройства обеспечивает возможность записи сбойной ситуации т.е. «{яоссацию состояния входов устройства при сбое для последующего анализа. 1 з.п. ф-лы, 2 ил. ю Од сд vj ел HLOa уо

С хоЗных шкн 20 г.2

| Устройство для контроля последовательности импульсов | 1980 |

|

SU930630A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля выполнения последовательности действий оператора | 1983 |

|

SU1128258A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

Авторы

Даты

1986-10-23—Публикация

1984-08-10—Подача