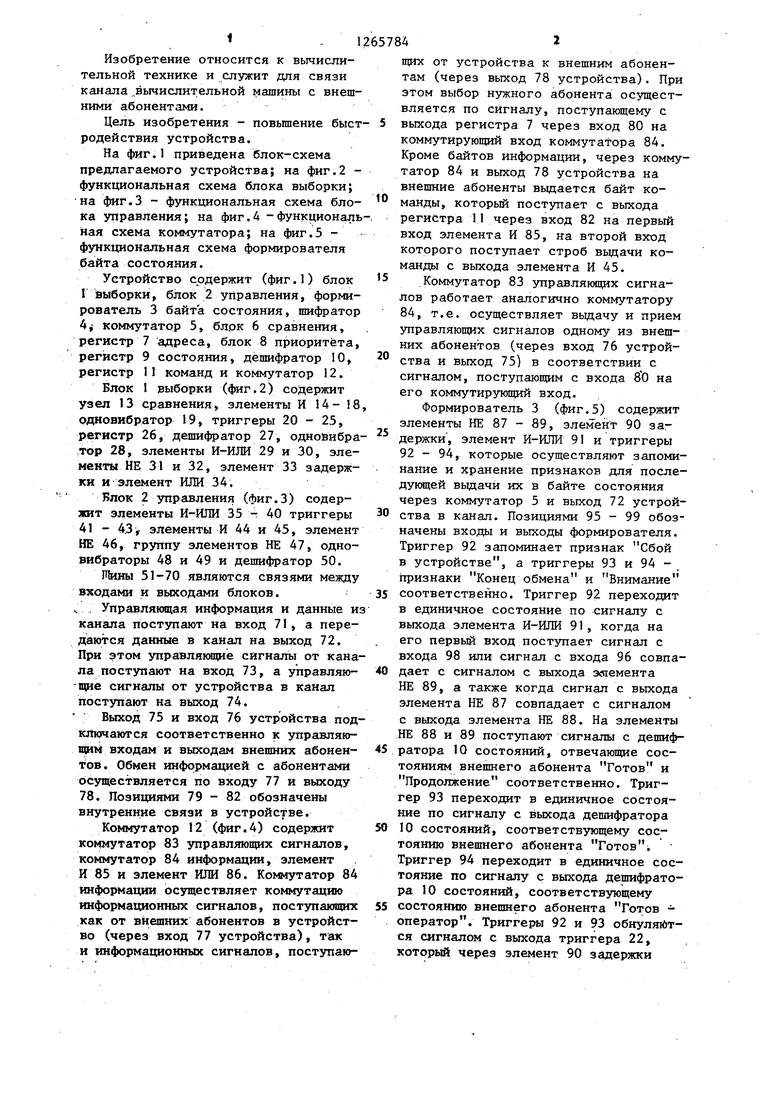

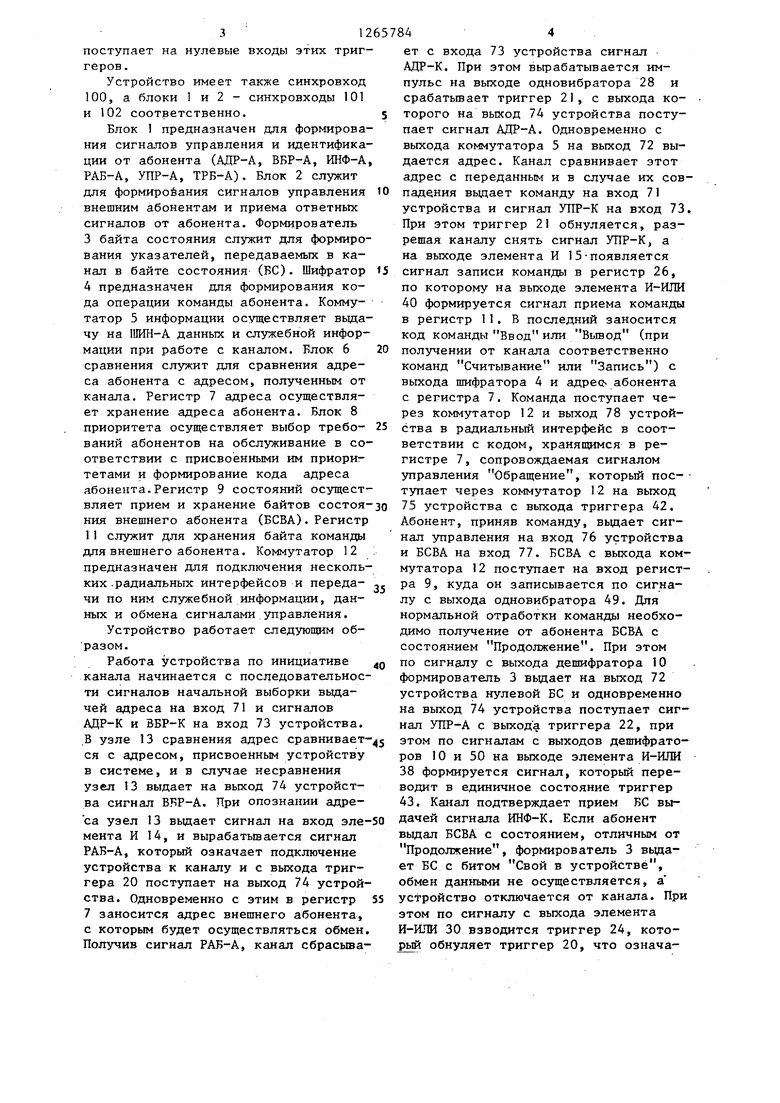

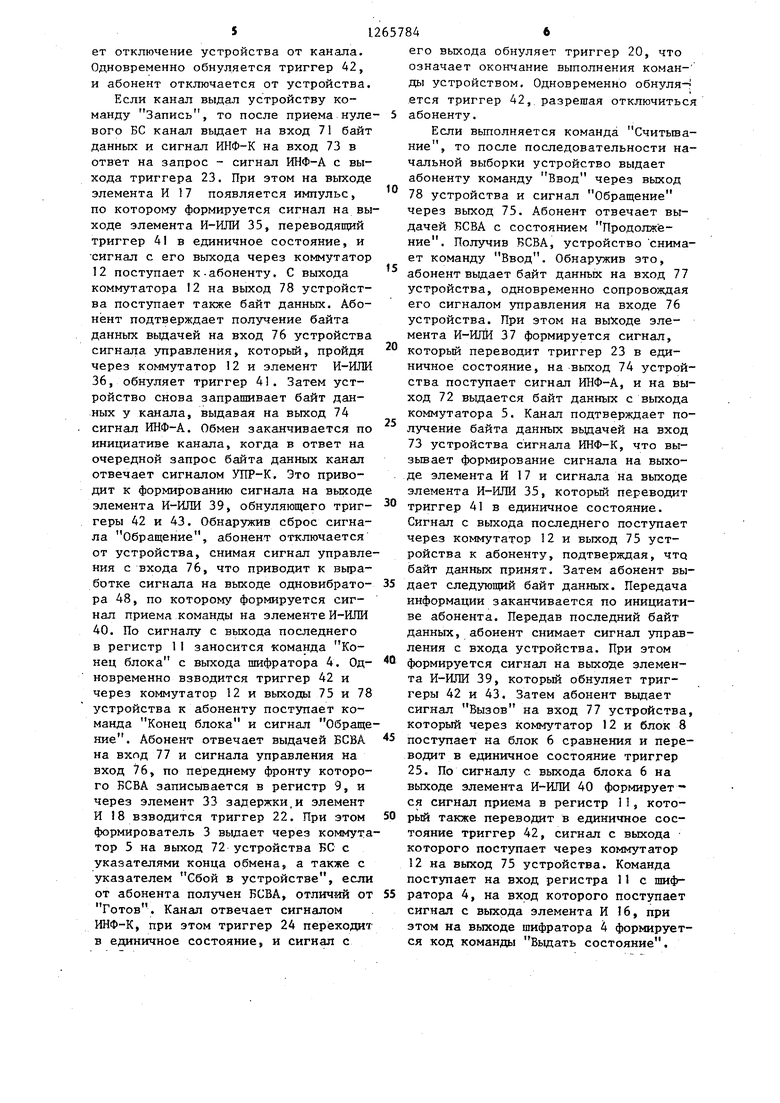

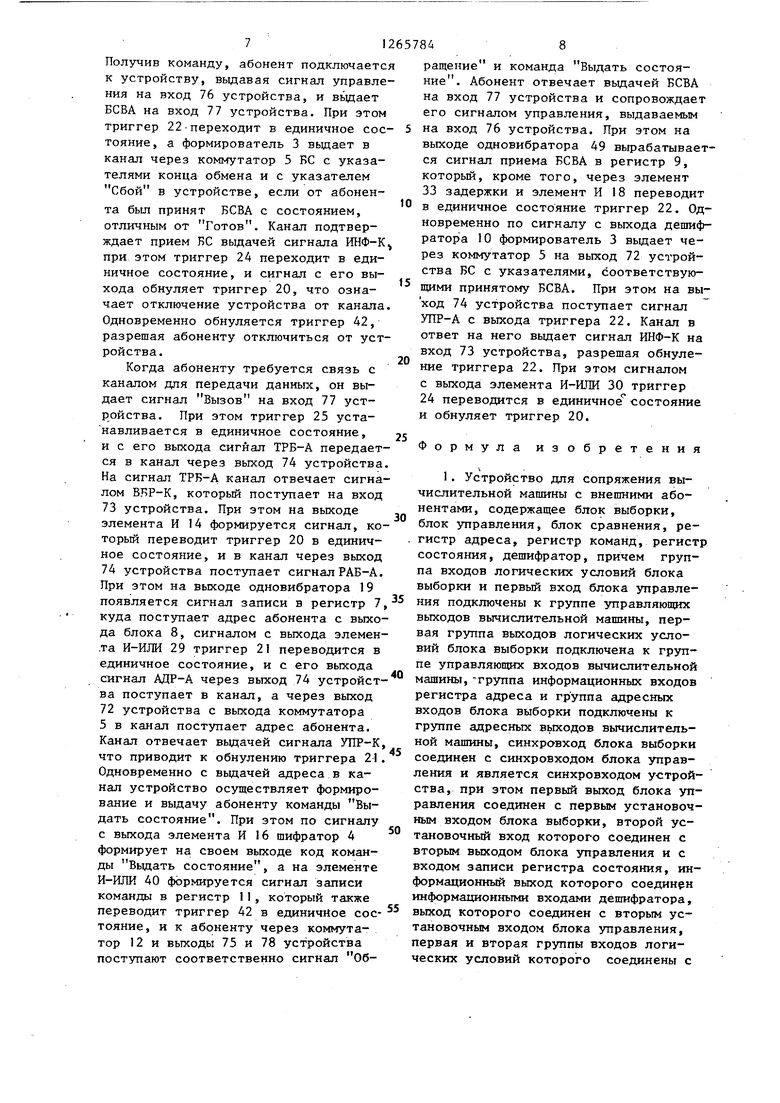

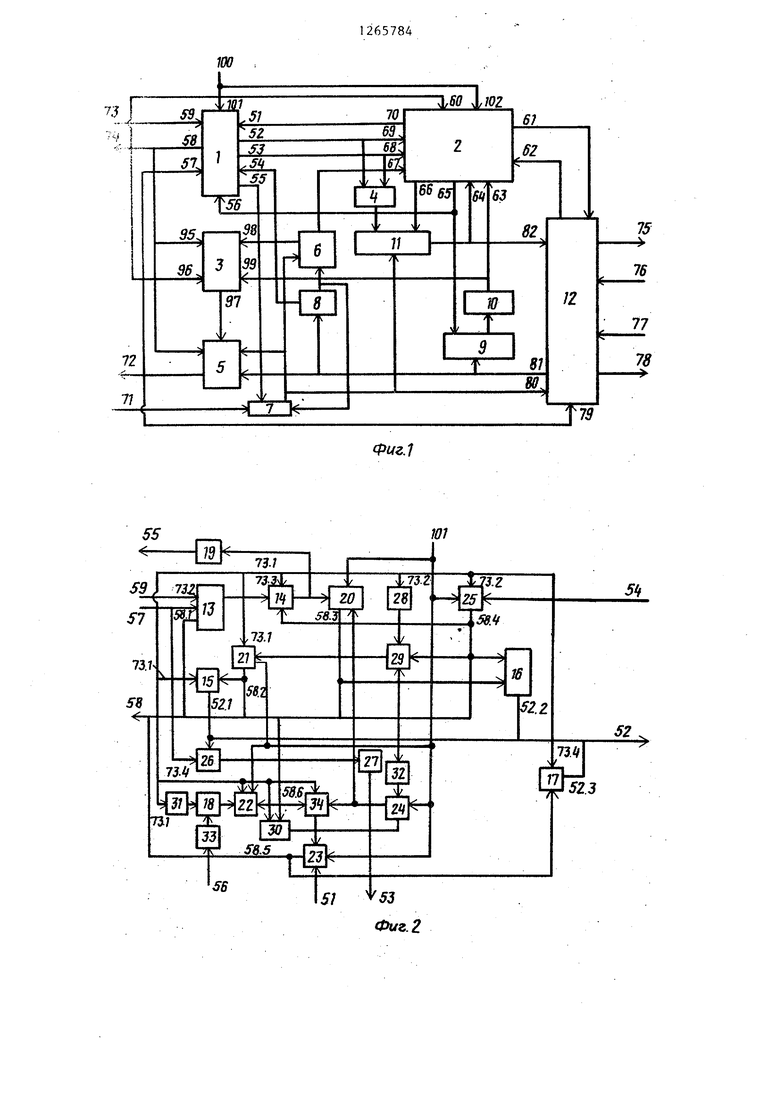

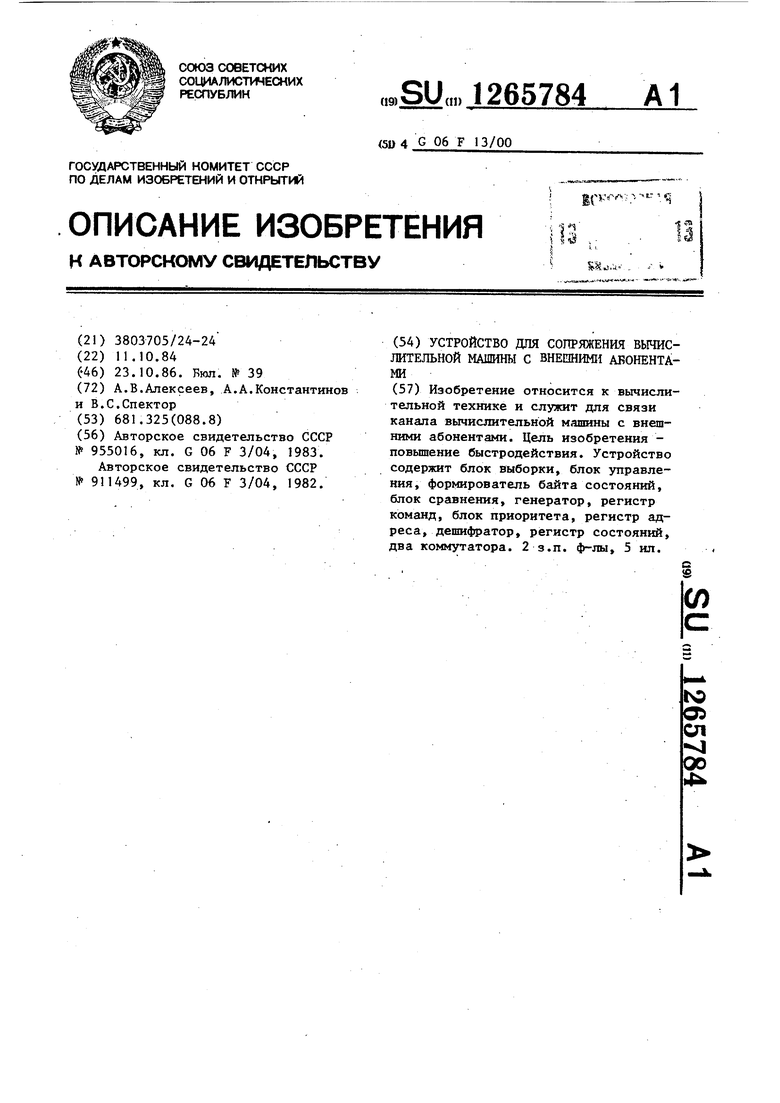

Изобретение относится к вычислительной технике и служит для связи канала .вычислительной машины с внешними абонентами. Цель изобретения - повьш1ение быст родействия устройства. На фиг.1 приведена блок-схема предлагаемого устройства; на фиг.2 функциональная схема блока выборки; на фиг.З - функциональная схема блока управления; на фиг.4 -функциональ ная схема коммутатора; на фиг.З функциональная схема формирователя байта состояния. Устройство содержит (фиг.1) блок I выборки, блок 2 управления, формирователь 3 байта состояния, шифратор 4,- коммутатор 5, блок 6 сравнения, регистр 7 адреса, блок 8 приоритета, регистр 9 состояния, дешифратор 10, регистр 11 команд и коммутатор 12. Блок 1 выборки (фиг.2) содержит узел 13 сравнения, элементы И 14- 18 одновибратор 19, триггеры 20 - 25, регистр 26, дешифратор 27, однойибра тор 28, элементы И-ИЛИ 29 и 30, элементы НЕ 31 и 32, элемент 33 задержки и элемент ИЛИ 34. Блок 2 управления (фиг.3) содержит элементы И-ИЛИ 35 -т 40 триггеры 41 - 4.3,- элементы И 44 и 45, элемент НЕ 46, группу элементов НЕ 47, одновибраторы 48 и 49 и дешифратор 50. ГЫны 51-70 являются связями между входами и выходами блоков. . , Управляющая информация и данные и канала поступают на вход 71, а передаются данные в канал на выход 72. При этом управляющие сигналь от кана ла поступают на вход 73, а управляю-щие сигналы от устройства в канал поступают на выход 74. Выход 75 и вход 76 устройства под ключаются соответственно к управляющим входам и выходам внешних абонентов. Обмен информацией с абонентами осуществляется по входу 77 и выходу 78. Позициями 79 - 82 обозначены внутренние связи в устройстве. Коммутатор 12 (фиг.4) содержит коммутатор 83 управляющих сигналов, коммутатор 84 информации, элемент И 85 и элемент ИЛИ 86. Коммутатор 84 информации осуществляет коммутацию информационных сигналов, поступающих как от внешних абонентов в устройство (через вход 77 устройства), так и информационных сигналов, поступающих от устройства к внешним абонентам (через выход 78 устройства). При этом выбор нужного абонента осзтцествляется по сигналу, поступающему с выхода регистра 7 через вход 80 на коммутирующий вход коммутатора 84. Кроме байтов информации, через коммутатор 84 и выход 78 устройства на внешние абоненты выдается байт команды, который поступает с вьпсода регистра 11 через вход 82 на первый вход элемента И 85, на второй вход которого поступает строб выдачи команды с выхода элемента И 45. Коммутатор 83 управляющих сигналов работает аналогично коммутатору 84, т.е. осуществляет вьщачу и прием управляюш 1х сигналов одному из внешних абонентов (через вход 76 устройства и выход 75) в соответствии с сигналом, поступающим с входа 80 на его коммутирзгющий вход. Формирователь 3 (фиг.5) содержит элементы НЕ 87 - 89, элемент 90 задержки, элемент И-ИЛИ 91 и триггеры 92 - 94, которые осуществляют запоминание и хранение признаков для последующей вьщачй их в байте состояния через коммутатор 5 и выход 72 устройства в канал. Позициями 95 - 99 обозначены входы и выходы формирователя. Триггер 92 запоминает признак Сбой в устройстве, а триггеры 93 и 94 признаки Конец обмена и Внимание соответственно. Триггер 92 переходит в единичное состояние по сигналу с выхода элемента И-ИЛИ 91, когда на его первьй вход поступает сигнал с входа 98 или сигнал с входа 96 совпадает с сигналом с выхода элемента НЕ 89, а также когда сигнал с выхода элемента НЕ 87 совпадает с сигналом с выхода элемента НЕ 88. На элементы НЕ 88 и 89 поступают сигналы с дешифратора 10 состояний, отвечающие состояниям внешнего абонента Готов и Продолжение соответственно. Триггер 93 переходит в единичное состояние по сигналу с выхода дешифратора 10 состояний, соответствующему состоянию внепгаего абонента Готов. Триггер 94 переходит в единичное состояние по сигналу с выхода дешифратора 10 состояний, соответствующему состоянию внешнего абонента Готов оператор. Триггеры 92 и 93 обнуляются сигналом с выхода триггера 22, который через элемент 90 задержки

поступает на нулевые входы этих триггеров.

Устройство имеет также синхровход 100, а блоки 1 и 2 - синхровходы 101 и 102 соответственно.

Блок 1 предназначен для формирования сигналов управления и идентификации от абонента (АДР-А, ВБР-А, ИНФ-А РАБ-А, УПР-А, ТРБ-А). Блок 2 служит для формиройания сигналов управления внешним абонентам и приема ответных сигналов от абонента. Формирователь

3байта состояния служит для формирования указателей, передаваемых в канал в байте состояния (БС). Шифратор

4предназначен для формирования кода операции команды абонента. Коммутатор 5 информации осуществляет вьщачу на ШИН-А данных и служебной информации при работе с каналом. Блок 6 сравнения служит для сравнения адреса абонента с адресом, полученным от канала. Регистр 7 адреса осуществляет хранение адреса абонента. Блок 8 приоритета осуществляет выбор требований абонентов на обслуживание в соответствии с присвоенными им приоритетами и формирование кода адреса абонента.Регистр 9 состояний осуществляет прием и хранение байтов состоякия внешнего абонента (БСВА). Регистр

11 служит для хранения байта команды для внешнего абонента. Коммутатор 12 предназначен для подключения нескольких .радиальных интерфейсов и передачи по ним служебной информации, данных и обмена сигналами управления.

Устройство работает следующим образом.

Работа устройства по инициативе канала начинается с последовательности сигналов начальной выборки вьщачей адреса на вход 71 и сигналов АДР-К и ВБР-К на вход 73 устройства, В узле 13 сравнения адрес сравнивается с адресом, присвоенным устройству в системе, и в случае несравнения узел 13 выдает на выход 74 устройства сигнал ВБР-А. При опознании адреса узел 13 выдает сигнал на вход элемента И 14, и вырабатьшается сигнал РАВ-А, который означает подключение устройства к каналу и с выхода триггера 20 поступает на выход 74 устройства. Одновременно с этим в регистр 7 заносится адрес внещнего абонента, с которым будет осуществляться обмен. Получив сигнал РАБ-А, канал сбрасывает с входа 73 устройства сигнал АДР-К. При этом вырабатывается импульс на выходе одновибратора 28 и срабатьгоает триггер 21, с выхода которого на выход 74 устройства поступает сигнал АДР-А. Одновременно с выхода коммутатора 5 на выход 72 выдается адрес. Канал сравнивает этот адрес с переданным и в случае их совпадения выдает команду на вход 71 устройства и сигнал УПР-К на вход 73 При этом триггер 21 обнуляется, разрешая каналу снять сигнал УПР-К, а на выходе элемента И I5-появляется сигнал записи команды в регистр 26, по которому на выходе элемента И-ИЛИ 40 формируется сигнал приема команды в регистр 11. В последний заносится код команды Ввод или Вьшод (при получении от канала соответственно команд Считывание или Запись) с выхода шифратора 4 и адрес- абонента с регистра 7. Команда поступает через коммутатор 12 и выход 78 устройства в радиальный интерфейс в соответствии с кодом, хранящимся в регистре 7, сопровождаемая сигналом управления Обращение, который поступает через коммутатор 12 на выход 75 устройства с выхода триггера 42. Абонент, приняв команду, вьщает сигнал управления на вход 76 устройства и БСВА на вход 77. БСВА с выхода коммутатора 12 поступает на вход регистра 9, куда он записывается по сигналу с выхода одновибратора 49. Для нормальной отработки команды необходимо получение от абонента БСВА с состоянием Продолжение. При этом по сигналу с вьпсода дешифратора IО формирователь 3 вьщает на выход 72 устройства нулевой БС и одновременно на выход 74 устройства поступает сигнал УПР-А с выхода триггера 22, при этом по сигналам с выходов дешифраторов 10 и 50 на выходе элемента И-ИЛИ 38 формируется сигнал, который переводит в единичное состояние триггер 43, Канал подтверждает прием БС выдачей сигнала ИНФ-К. Если абонент вьщал БСВА с состоянием, отличным от Продолжение, формирователь 3 вьщает БС с битом Свой в устройстве, обмен данными не осуществляется, а устройство отключается от канала. При этом по сигналу с выхода элемента И-ИЛИ 30 взводится триггер 24, который обнуляет триггер 20, что означает отключение устройства от канала. Одновременно обнуляется триггер 42, и абонент отключается от устройства.

Если канал выдал устройству команду Запись, то после приема нулевого БС канал выдает на вход 71 байт данньпс и сигнал ИНФ-К на вход 73 в ответ на запрос - сигнал ИНФ-А с выхода триггера 23. При этом на выходе элемента И 17 появляется импульс, по которому формируется сигнал на выходе элемента И-ИЛИ 35, переводящий триггер 41 в единичное состояние, и сигнал с его выхода через коммутатор 12 поступает к-абоненту. С выхода коммутатора 12 на выход 78 устройства поступает также байт данных. Абонент подтверждает получение байта данньпс вьщачей на вход 76 устройства сигнала управления, который, пройдя через коммутатор 12 и элемент И-ИЛИ 36, обнуляет триггер 41. Затем устройство снова запрашивает байт данных у канала, выдавая на выход 74 сигнал ИНФ-А. Обмен заканчивается по инициативе канала, когда в ответ на очередной запрос байта данных канал отвечает сигналом УПР-К. Это приводит к формированию сигнала на выходе элемента И-ИЛИ 39, обнуляющего триггеры 42 и 43. Обнаружив сброс сигнала Обращение, абонент отключается от устройства, снимая сигнал управления с входа 76, что приводит к выработке сигнала на выходе одновибратора 48, по которому формируется сигнал приема команды на элементе И-ШШ 40. По сигналу с выхода последнего в регистр 11 заносится команда Конец блока с выхода шифратора 4. Одновременно взводится триггер 42 и через коммутатор 12 и выходы 75 и 78 устройства к абоненту поступает команда Конец блока и сигнал Обращение. Абонент отвечает выдачей БСВА на вход 77 и сигнала управления на вход 76, по переднему фронту которого БСВА записьшается в регистр 9, и через элемент 33 задержки,и элемент И 18 взводится триггер 22. При этом формирователь 3 выдает через коммутатор 5 на выход 72 устройства БС с указателями конца обмена, а также с указателем Сбой в устройстве, если от абонента получен БСВА, отличий от Готов. Канал отвечает сигналом ИНФ-К, при этом триггер 24 переходит в единичное состояние, и сигнал с

его выхода обнуляет триггер 20, что означает окончание выполнения команды устройством. Одновременно обнуля- ется триггер 42, разрешая отключиться 5 абоненту.

Если выполняется команда Считьшание, то после последовательности начальной выборки устройство выдает абоненту команду Ввод через выход 78 устройства и сигнал Обращение через выход 75. Абонент отвечает выдачей БСВА с состоянием Продолжение. Получив БСВА, устройство снимает команду Ввод. Обнаружив это, абонент вьщает байт данных на вход 77 устройства, одновременно сопровождая его сигналом управления на входе 76 устройства. При этом на выходе элемента И-ИЛИ 37 формируется сигнал,

который переводит триггер 23 в единичное состояние, на выход 74 устройства поступает сигнал ИНФ-А, и на выход 72 вьщается байт данных с выхода коммутатора 5. Канал подтверждает получение байта данных вьщачей на вход 73 устройства сигнала ИНФ-К, что вызывает формирование сигнала на выходе элемента И 17 и сигнала на выходе элемента И-ИЛИ 35, который переводит

триггер 41 в единичное состояние. Сигнал с выхода последнего поступает через коммутатор 12 и выход 75 устройства к абоненту, подтверждая, что байт данных принят. Затем абонент выдает следующий байт данных. Передача информации заканчивается по инициативе абонента. Передав последний байт данных, абонент снимает сигнал управления с входа устройства. При этом

0 формируется сигнал на выходе элемента И-ИЛИ 39, который обнуляет триггеры 42 и 43. Затем абонент вьщает сигнал Вызов на вход 77 устройства, который через коммутатор 12 и блок 8

5 поступает на блок 6 сравнения и переводит в единичное состояние триггер 25. По сигналу с выхода блока 6 на выходе элемента И-ИЛИ 40 формируется сигнал приема в регистр I1, кото0 рый также переводит в единичное состояние триггер 42, сигнал с выхода которого поступает через коммутатор 12 на выход 75 устройства. Команда поступает на вход регистра 11 с шиф5 ратора 4, на вход которого поступает сигнал с выхода элемента И 16, при этом на выходе шифратора 4 формируется код команды Выдать состояние.

Получив команду, абонент подключается к устройству, вьщавая сигнал управления на вход 76 устройства, и вьщает БСВА на вход 77 устройства. При этом триггер 22-переходит в единичное сое- 5 на тояние, а формирователь 3 выдает в канал через коммутатор 5 БС с указателями конца обмена и с указателем Сбой в устройстве, если от абонента был принят БСВА с состоянием, отличным от Готов. Канал подтверждает прием БС выдачей сигнала ИНФ-К при этом триггер 24 переходит в единичное состояние, и сигнал с его выхода обнуляет триггер 20, что означает отключение устройства от канала Одновременно обнуляется триггер 42, разрешая абоненту отключиться от устройства. Когда абоненту требуется связь с каналом для передачи данных, он выдает сигнал Вызов на вход 77 устройства. При этом триггер 25 устанавливается в единичное состояние, и с его выхода сигнал ТРБ-А передается в канал через выход 74 устройства На сигнал ТРБ-А канал отвечает сигналом ВБР-К, который поступает на вход 73устройства. При этом на выходе элемента И 14 формируется сигнал, который переводит триггер 20 в единичное состояние, и в канал через выход 74устройства поступает сигнал РАБ-А. При этом на выходе одновибратора 19 появляется сигнал записи в регистр 7 куда поступает адрес абонента с выхода блока 8, сигналом с выхода элемен.та И-ИЛИ 29 триггер 21 переводится в единичное состояние, и с его выхода сигнал АДР-А через выход 7 устройства поступает в канал, а через выход 72 устройства с выхода коммутатора 5 в канал поступает адрес абонента. Канал отвечает вьщачей сигнала УПР-К что приводит к обнулению триггера 2-1 Одновременно с вьщачей адреса в канал устройство осуществляет формирование и выдачу абоненту команды Выдать состояние. При этом по сигналу с выхода элемента И 16 шифратор 4 формирует на своем выходе код команды Выдать состояние, а на элементе И-ИЛИ 40 формируется сигнал записи команды в регистр 11, который также переводит триггер 42 в единичное соетояние, и к абоненту через коммутатор 12 и выходы 75 и 78 устройства поступают соответственно сигнал Об12657848

ращение и команда Выдать состояние. Абонент отвечает выдачей БСВА на вход 77 устройства и сопровождает его сигналом управления, выдаваемым вход 76 устройства. При этом на выходе одновибратора 49 вырабатывается сигнал приема БСВА в регистр 9, который, кроме того, через элемент 33 задержки и элемент И 18 переводит в единичное состояние триггер 22. Одновременно по сигналу с выхода дешифратора 10 формирователь 3 выдает через коммутатор 3 на выход 72 устройства БС с указателями, соответствующими принятому БСВА. При этом на выход 74 устройства поступает сигнал УПР-А с выхода триггера 22. Канал в ответ на него выдает сигнал ИНФ-К на вход 73 устройства, разрешая обнуление триггера 22. При этом сигналом с выхода элемента И-ИЛИ 30 триггер 24 переводится в единичное состояние и обнуляет триггер 20. Формула изобретения 1. Устройство для сопряжения вычислительной машины с внешними абонентами, содержащее блок выборки, блок управления, блок сравнения, регистр адреса, регистр команд, регистр состояния, дешифратор, причем группа входов логических условий блока выборки и первый вход блока управления подключены к группе управляющих выходов вьиислительной машины, первая группа выходов логических условий блока выборки подключена к группе управляющих входов вычислительной машины,труппа информационных входов регистра адреса и группа адресных входов блока выборки подключены к группе адресных вьгходов вычислительной машины, синхровход блока выборки соединен с синхровходом блока управления и является синхровходом устройства, при этом первый выход блока управления соединен с первым установочным входом блока выборки, второй установочный вход которого соединен с вторым выходом блока управления и с входом записи регистра состояния, информационный выход которого соединен информационными входами депшфратора. выход которого соединен с вторым установочным входом блока управления, первая и вторая группы входов логических условий которого соединены с второй и третьей группами выходов логических условий блока выборки соответстйенно, выход записи которого соединен с входом записи регистра адреса, группа информационных выходов которого соединена с группой информационных входов регистра команд группа информационных выходов которо го соединена с третьей группой входов логических условий блока управле ния, третий выход которого соединен с входом записи регистра команд, отличающееся тем, что, .с целью повышения быстродействия, в него введены шифратор, формирователь байта состояния, регистр приоритета два коммутатора, причем информационный выход первого коммутатора подклю чен к информационному входу вычислительной машины, первая и вторая груп пы информационных, входов-выходов второго коммутатора подключены к группам управляющих и информационных входов-выходов внешних абонентов соответственно , группа управляющих вхо дов второго коммутатора подключена к группе адресных выходов вычислительной машины, первый установочный вход формирователя байта подключен к соответствующему управляющему выходу вычислительной машины, при этом второй установочный вход формироват ля байта состояния и управляющий вход первого коммутатора соединены с соответствующими выходами первой группы выходов логических условий блока выборки, вторая и третья груп пы выходов логических условий которого соединены с первой и второй группами информационных входов шифр тора соответственно, группа информационных выходов которого соединена с группой информационных входов регистра команд, группа информационных выходов которого соединена с первой группой информационных входов второго коммутатора, вторая группа информационных входов которого соединена с первой группой входов сравнения, с первой группой информационных

входов второго коммутатора и с группой информационных выходов регистра адреса, вход чтения которого соединен с выходом регистра приоритета, группа выходов которого соединена с второй группой входов блока сравнения, выход равенства которого соединен с третьим установочным входом

.ветственно, синхровход первого триггера соединен с синхровходами второго и третьего триггеров и является синхровходом блока управления, вьпсо55 ды четвертого элемента И-ИЖ и второго одновибратора являются первым и вторым выходами блока управления соответственно, выход второго эле410формирователя байта состояния, группа установочных входов которого соединена с группой выходов дешифратора, третий установочньй вход блока выборки соединен с выходом регистра приоритета, группа информационных входов которого соединена с группой информационных входов регистра состояний, с второй группой информационных входов первого коммутатора и с первой группой информационных выходов второго коммутатора, вторая группа информационных выходов и группа тактовых входов, которые соединены с четвертой группой входов логических условий и группой выходов блока управления соответственно, третий установочный вход которого соединен с выходом неравенства блока сравнения, группа информационных выходов формирователя байта состояний соединена с третьей группой информационных входов первого коммутатора. 2. Устройство по П.1, отличающееся тем, что блок управления содержит дешифратор, два одновибратора, три триггера, шесть элементов И-ИЛИ, два элемента И, элемент НЕ, группу элементов НЕ, причем первые входы первого и второго элементов И-ИЛИ и первого элемента И образуют первую группу входов логических условий блока управления, вторые входы первого и второго элементов И-ИЛИ и первые входы третьего и четвертого элементов И-ИЛИ образуют вторую группу входов логических условий блока управления, группа информационных входов дешифратора образует третью , группу входов логических условий блока управления, второй вход третьего элемента И-ИЛИ, входы элементов НЕ группы и входы первого и второго одновибраторов образуют четвертую группу входов логических условий блока управления, первые входы пятого и шестого элементов И-ИЛИ и третий вход второго элемента И-ИЛИ являются первым, вторьт и третьим установочными входами блока управления соотмента И-ШТИ соединен с единичньгм входом второго триггера и является третьим выходом блока управления,-выходы первого и второго триггеров первого и второго элементов И образ.уют группу выходов блока управления, при этом выход первого элемента И-ИЛИ с входом элемента НЕ, выход которого соединен с вторым входом четвертого элемента И-ЙЛИ, третий вход которого соединен с выходом третьего триггера, нулевой вход которого соединен с выходом пятого элемента И-ИЛИ и с нулевым входом второго триггера, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с первым выходом элемента НЕ группы, второй выход которого соединен с третьим входом третьего элемента И-ИЛИ, выход которого соединен с нулевым входом первого триггера, второй вход первого элемента И соединен с первым выходом дешифратора, с вторым входом шестого элемента И-ИЛИ и вторым входом пятого элемента И-ИЛИ, третий вход которого соединен с вторым выходом . дешифратора и с третьим входом шестого элемента И-ИЛИ, выход которого соединен с единичным входом третьего триггера, выход первого одновибратора соединен с четвертыми входами второго и шестого элементов И-ИЛИ. 3. Устройство по п.1, о т л и ча-ющееся тем, что блок выборки содержит узел сравнения, регистр, дешифратор, шесть триггеров, два одновибратора, пять элементов И, два элемента И-ИЛИ, один элемент ИЛИ, два элемента НЕ, один элемент задержки, причем группа входов узла сравнения соединена с группой информационных входов регистра и образует группу адресных входов блока выборки, вход узла сравнения, первьй и второй входы первого элемента И, первьй вход второго элемента И образуют группу входов логических условий блока выборки, выходы первого, второго, третьего, четвертого и пятого триггеров, первый выход узла сравнения образуют первую группу выходов логических условий блока выборки, выходы второго, третьего и четвертого элементов И образуют вторую группу выходов логических условий блока выборки, синхровход первого триггера соединен с синхровходами второго, третьего.

.четвертого, пятого, шестого триггеров и является синхровходом блока выборки, выход первого одновибратора является выходом записи блока выборки, группа выходов дешифратора образует третью группу выходов логических условий блока выборки, единичный вход пятого триггера, вход элемента задержки и единичный вход первого триггера являются первым, вторым и третьим установочными входами блока выборки соответственно, при этом в блоке выборки первый вход первого элемента И объединен с нулевым входом третьего триггера, с первым входом третьего элемента И и входом первого элемента НЕ, выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с выходом элемента задержки, нулевой вход первого триггера объединен с входом второго одновибратора и входом узла сравнения, второй выход которого соединен с третьим входом первого элемента И, выход которого соединен с единичными входами второго триггера и входом первого одновибратора, первый вход второго элемента И объединен с первым входом элемента ИЛИ, с первым входом первого элемента И-ИЛИ, с нулевым входом четвертого триггера, единичный вход которого соединен с выходом пятого элемента И, первый вход четвертого элемента И соединен с первым входом второго элемента И-ИЛИ, с четвертым входом первого элемента И и с выходом первого триггера, выход второго одновибратора соединён с вторым входом второго элемента И-ИЛИ, третий вход которого соединен с выходом второго тригI гера, с вторым входом четвертого эле,мента И и с входом элемента НЕ, выход которого соеданен с выходом первого элемента И-ИЛИ, второй вход которого соединен с выходом четвертого триггера и с вторым входом элемента ИЛИ, третий вход которого соединен с выходом шестого триггера и нулевым входом второго триггера, вход дешифратора соединен с выходом регистра, выход элемента ИЛИ соединен с нулевым входом пятого триггера,выход второго элемента И-ИЛИ соединен с единичными входом третьего триггера,вькод которог го соединен с вторым входом третьего элемента И,выход пятого триггера соединен с вторьм входом второго элемента И.

ФигЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сопряжения абонентов с каналами ввода-вывода ЭВМ | 1984 |

|

SU1275456A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения источников информации с вычислительной машиной | 1984 |

|

SU1179358A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1439609A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1265789A1 |

Изобретение относится к вычислительной технике и служит для связи канала вычислительной машины с внешними абонентами. Цель изобретения повьш1ение быстродействия. Устройство содержит блок выборки, блок управления, формирователь байта состояний, блок сравнения, генератор, регистр команд, блок приоритета, регистр адреса, дешифратор, регистр состояний, два коммутатора. 2 з.п. ф-лы, 5 ил. (Л С

Фиг. 2

68

1265784

юг 70

61

62

65

| Устройство для сопряжения канала ввода-вывода с периферийными устройствами | 1980 |

|

SU955016A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена | 1978 |

|

SU911499A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-23—Публикация

1984-10-11—Подача