.... , I1

j/TjTlr- |7Г

элемент НЕ 16, два одновибратора 14 и 15, два элемента ИЛИ 18, 21 и дешифратор 17. Запоминающий блок последовательности команд 2 содержит шесть регистров и пять коммутаторов. Устройство обнаруживает

появление на шине адреса данных контролируемой микропроцессорной системы таких кодов операций, которые задают несуществующие команды. 1 з.п.ф-лы, бил., 1 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для контроля микропроцессорной системы | 1985 |

|

SU1287161A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для контроля микропроцессора | 1988 |

|

SU1599862A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для контроля хода программы | 1988 |

|

SU1663612A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1817096A1 |

| Устройство для сопряжения с микропроцессором | 1983 |

|

SU1109730A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в микропроцессорных системах, которые построены на основе микропроцессора, работающего в максимальном режиме. Цель изобретения - повышение достоверности и оперативности контроля мик- ропроцессорной системы в процессе функционирования. Устройство для контроля микропроцессорной системы содержит блок управления 1 и запоминающий блок последовательности команд 2. Для достижения поставленной цели в устройство введен блок контроля 3, содержащий узел контроля кодов 22 и триггер 23, а в состав блока управления 1 введены коммутатор 4, счетчик команд 5, элемент ИЛИ 6, триггер 7, сумматор по модулю два 8 и узел управления 9, содержащий элемент ИЛ И-НЕ 10, три элемента И 11, 19, 20, элемент И-ИЛИ 12, (Л С

Изобретение относится к автоматике и вычислительной технике и может быть использовано в микропроцессорных системах, которые построены на основе микропроцессора К1810ВМ86, работающе- го в максимальном режиме.

Известно устройство для контроля ЭВМ, содержащее блок счетчиков, дешифратор, пять триггеров, два элемента ИЛИ, элемент ИЛИ-НЕ, два формирователя им- пульсов, три элемента И, элемент И-НЕ, два элемента задержки, два регистра и схему сравнения.

Известно также устройство для контроля микропроцессорной системы, содержа- щее три регистра операндов, два буферных регистра адреса, три блока сравнения, счетчик команд, два сумматора, формирователь сигналов опроса, коммутатор, два триггера управления, триггер отказа, формирователь константы, элементы И, дешифратор кода операции, элементы ИЛИ.

Недостатком данных устройств является низкая достоверность контроля, обусловленная низкой полнотой контроля по числу команд, выполняемых в системе.

Наиболее близким к предлагаемому является устройство для контроля микропроцессорной системы, содержащее первый и второй элементы НЕ, мультиплексор дан- ных, дешифратор адреса, интерфейсный блок, первый и второй регистры управления, коммутатор, схему сравнения адреса, запоминающий блок последовательности микрокоманд, блок управления режимом. Причем выход блока управления режимом является первым выходом задания режима устройства для подключения к шине управления контролируемой микропроцессорной системы. Первый информационный вход схемы сравнения адреса подключен к входу - выходу устройства для подключения к шине адреса контролируемой микропроцессорной системы. Выход первого регистра управления соединен с управляющими вхо- дами мультиплексора данных и коммутатора и является вторым выходом задания режима устройства для подключения к шине управления контролируемой микропроцессорной системы. Выход второго управления соединен с разрешающим входом блока управления режимом, с входом записи запоминающего блока последовательности микрокоманд и с управляющим входом схемы сравнения. Вход разрешения запоминающего блока последовательности микрокоманд, вход синхронизации интерфейсного блока и входы синхронизации первого и второго регистров управления соединены с выходом дешифратора адреса. Вход записи чтения устройства подключен к входам разрешения дешифратора адреса интерфейсного блока. Информационный вход-выход устройства подключен к первому информационному входу-выходу интерфейсного блока, информационным входам первого и второго регистров управления и к выходу признака переполнения адреса запоминающего блока последовательности микрокоманд. Второй информационный вход-выход интерфейсного блока соединен с первым информационным входом-выходом коммутатора, вторым информационным входом схемы сравнения и инфорационным выходом запоминающего блока последовательности микрокоманд. Вход-выход устройства для подключения к шине адреса контролируемой микропроцессорной системы подключен к второму информационному входу-выходу коммутатора и к входу адреса микрокоманд запоминающего блока последовательности микрокоманд. Вход устройства для подключения к выходу данных контролируемой микропроцессорной системы подключен к второму информационному входу мультиплексора данных, выход которого соединен с информационным входом интерфейсного блока. Выход схемы сравнения соединен с информационным входом интерфейсного блока. Выход схемы сравнения соединен с третьим информационным входом мультиплексора данных и через первый элемент НЕ - с входом признака сравнения адреса запоминающего блока последовательности микрокоманд. Адресный вход интерфейсного блока подключен к выходу адреса управляющей микропроцессорной системы. Вход начальной установки устройства подключен к входам начальной установки первого и второго регистров управления и через вто- элемент НЕ - к входу начальной установки интерфейсного блока, первый и второй входы синхронизации устройства подключены соответственно к первому и второму входам синхронизации запоминающего блока последовательности микрокоманд. Выход схемы сравнения адреса блока управления режимом, информационный вход дешифратора адреса подключены к адресному входу устройства. Первый информационный вход мультиплексора данных подключен к выходу микрокоманд контролируемой микропроцессорной системы.

Недостатком данного устройства является низкая оперативность контроля и достоверность функционирования, связанные с невозможностью контроля в реальном масштабе времени. Низкая оперативность контроля обусловлена тем, что результат контроля формируется периодически - после выполнения специальной программы контроля. Это не позволяет локализовать момент появления ошибки во времени с точностью до выполняемой команды и предотвратить тем самым распространение ошибки в микропроцессорной системе. Вследствие этого оказывается низкой и достоверность контроля.

Цель изобретения - повышение достоверности и оперативности контроля.

Поставленная цель достигается тем, что в известную совокупность элементов, содержащую блок управления и запоминающий блок последовательности команд, информационный вход которого подключен к информационному входу устройства для подключения к шине адреса данных контролируемой микропроцессорной системы, синхровход устройства подключен к синх- ровходу блока управления, дополнительно введен блок контроля, а блок управления содержит счетчик команд, элемент ИЛИ, коммутатор, сумматор по модулю два, триггер и узел управления, содержащий дешифратор, триггер, элемент И-ИЛИ, три элемента И, элемент ИЛИ-НЕ, элемент НЕ, два элемента ИЛИ и два одновибратора, причем с первого по шестой управляющие входы блока управления являются соответственно с первого по шестой управляющими входами устройства для подключения соответственно к первому, второму и третьему выходам статуса магистрального цикла, выходу чтения и первому и второму выходам статуса очереди команд шины управления контролируемой микропроцессорной системы, вход сброса блока управления подключен к входу сброса устройства, с первого по девятый выходы блока управления соединены соответственно с первого по седьмойуправляющимивходами

запоминающего блока последовательности команд и первым и вторым управляющими входами блока контроля, третий управляющий вход которого и восьмой управляющий

вход запоминающего блока последовательности команд соединены с десятым выходом блока управления, первая и вторая группа выходов запоминающего блока последовательности команд соединены соот0 ветственно с первой и второй группами информационных входов блока контроля, выход которого является выходом сигналь ошибки устройства, причем в блоке управления первый вход первого элемента И и

5 первый и второй входы элемента ИЛИ-НЕ узла управления подключены соответственно к первому, второму и третьему управляющим входам блока управления, выход

0 элемента ИЛИ-НЕ соединен с вторым входом первого элемента И, выход которого соединен с информационным входом триггера узла управления, выход которого соединен с первым входом второго элемента И

5 и первым входом элемента И-ИЛИ, второй вход которого соединен с синхровходом триггера узла управления, с входами элемента НЕ и первого одновибратора и подключен к синхровходу блока управления,

0 вход сброса которого подключен к первому входу элемента ИЛИ блока управления и к третьему входу элемента И-ИЛИ, выход которого соединен с входом сброса триггера узла управления, вход разрешения записи

5 которого подключен к четвертому управляющему входу блока управления, выход первого одновибратора соединен с вторым входом второго элемента И, выход которого соединен с первым входом первого элемен0 та ИЛИ узла управления, с первым входом управления режимом счетчика команд, входом установки в единицу триггера блока управления и с первым управляющим входом коммутатора, второй управляющий

5 вход которого является восьмым выходом блока управления и соединен с входом установки в нуль триггера блока управления, с вторым входом первого элемента ИЛИ узла управления, с вторым входом управле0 ния режимом счетчика команд и с выходом третьего элемента И, первый и второй входы которого соединены с выходами соответственно второго одновибратора и второго элемента ИЛИ, первый вход которого сое5 динен с первым выходом дешифратора и подключен к девятому выходу блока управления, пятый и шестой управляющие входы которого подключены соответственно к первому и второму входам дешифратора, второй и третий выходы которого соедине- ны соответственно с вторым входом элемента ИЛИ блока управления и вторым входом второго элемента ИЛИ узла управления, выход первого элемента ИЛИ узла управления является первым выходом блока управления и подключен к синхровходу счетчика команд, вход сброса которого соединен с выходом элемента ИЛИ блока управления и является десятым выходом блока управления, с первого по четвертый выходы счетчика команд соединены соответственно с первого по четвертый информационными входами коммутатора и с первого по четвертый входами сумматора по модулю два блока управления, выход которого является третьим выходом блока управления, с четвертого по седьмой выходы которого подключены соответственно к выходам коммутатора с первого по четвертый, выход триггера узла управления является вторым выходом блока управления, причем блок контроля содержит узел контроля кодов и триггер, выход которого является выходом блока контроля, первая и вторая группы информационных входов которого подключены соответственно к первой и второй группам входов узла контроля кодов, синхровход, вход разрешения записи, вход сброса и информационный входы триггера блока контроля подключены соответственно к первому, второму и третьему управляющим входам блока контроля и выходу узла контроля кодов.

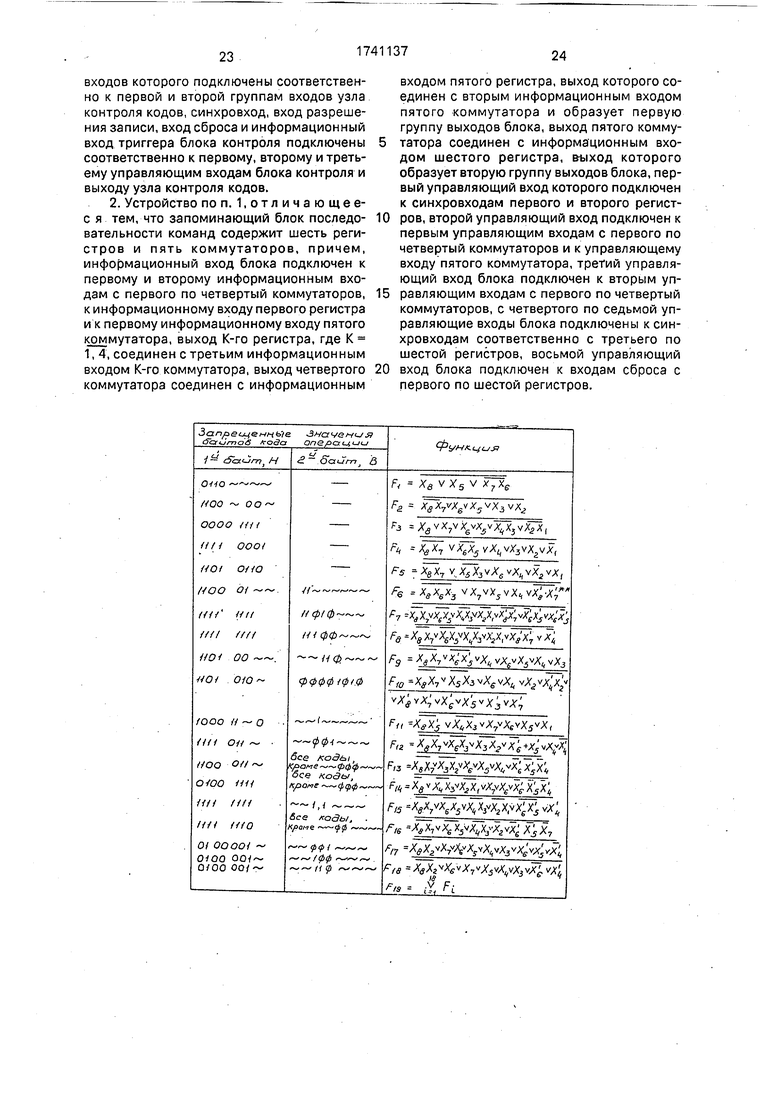

Сущность изобретения состоит в обнаружении появления в момент выборки кода команды таких ее первых и вторых байтов, которые задают несуществующие коды операции, Такие коды являются запрещенными, их наличие обусловлено избыточностью формата команды по отношению к множеству фактически существующих команд,

Предлагаемое устройство осуществляет контроль непрерывно - в моменты выборки каждой очередной команды из очереди байтов команд микропроцессора, не требуя остановки системы. Следовательно, оно обеспечивает более оперативное обнаружение ошибок в работе системы и более точную их локализацию во времени. Благодаря этому упрощается и ускоряется процесс восстановления нормального функционирования системы. Ввиду обеспечения непрерывности контроля выход предлагаемого устройства в каждый момент времени более достоверно отражает состояние системы. Следовательно, за счет этого обеспечивается более высокая достоверность контроля. Это приводит к сокращению простоев микропроцессорной системы, вызванных ошибками в ее работе, а также к уменьшению потерь, вызванных несвоевременным обнаружением этих ошибок.

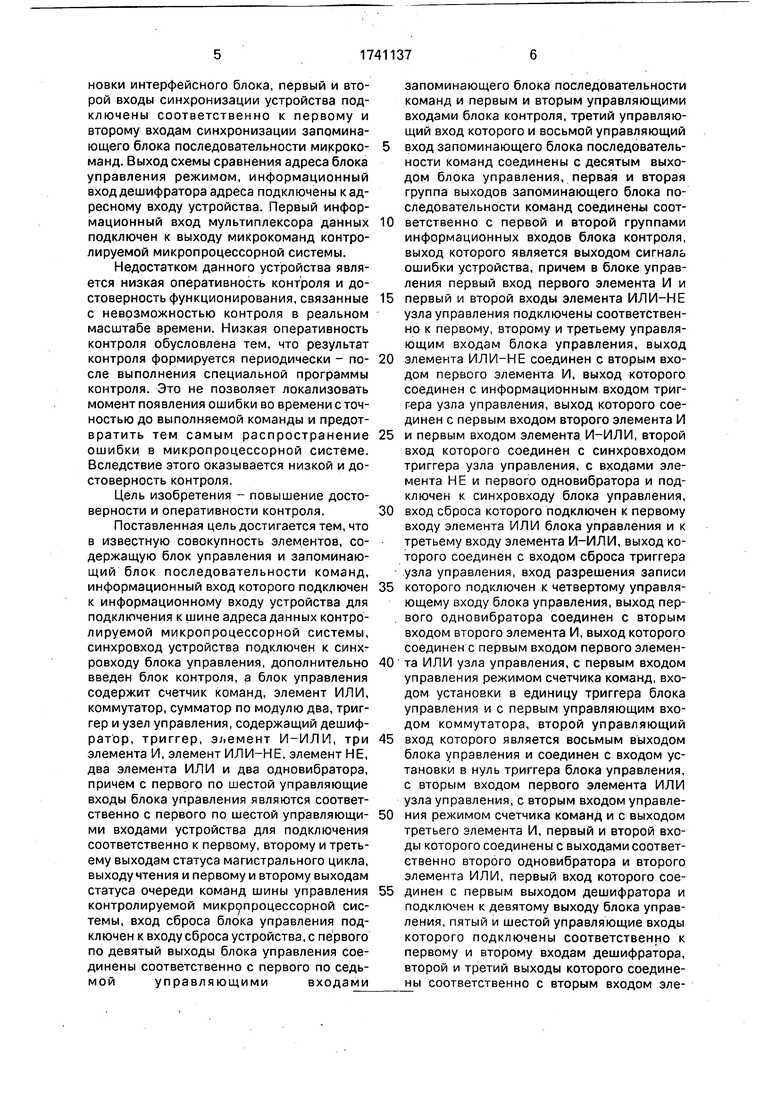

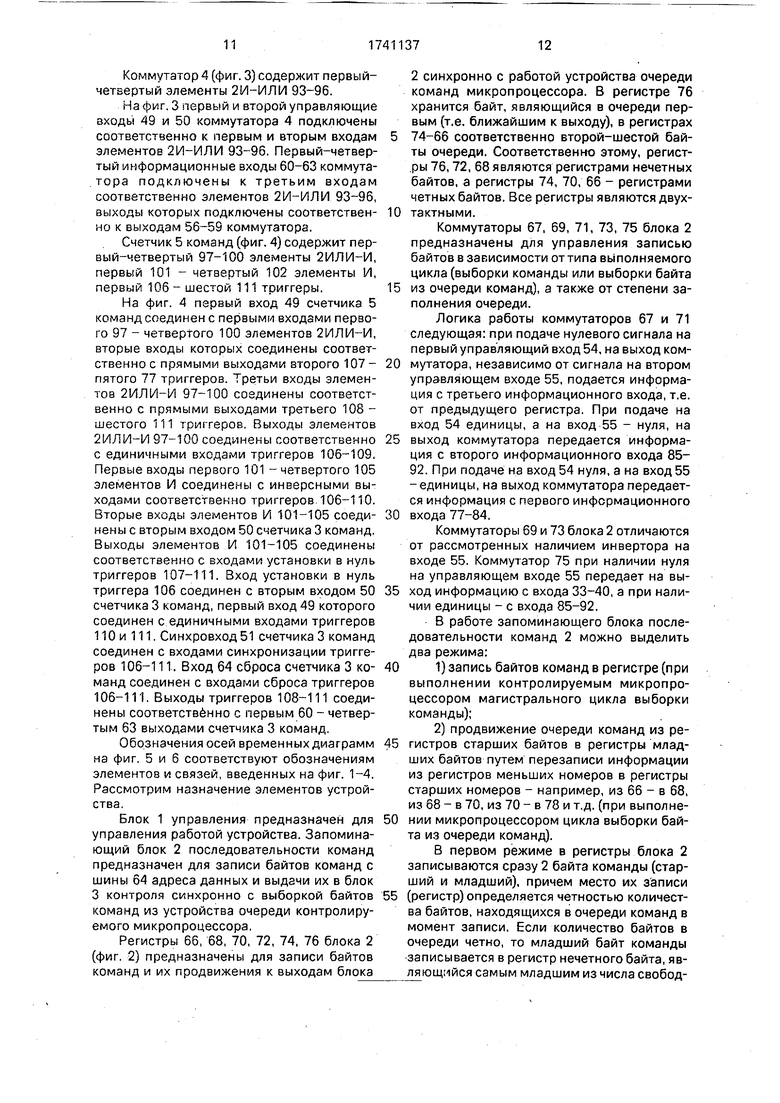

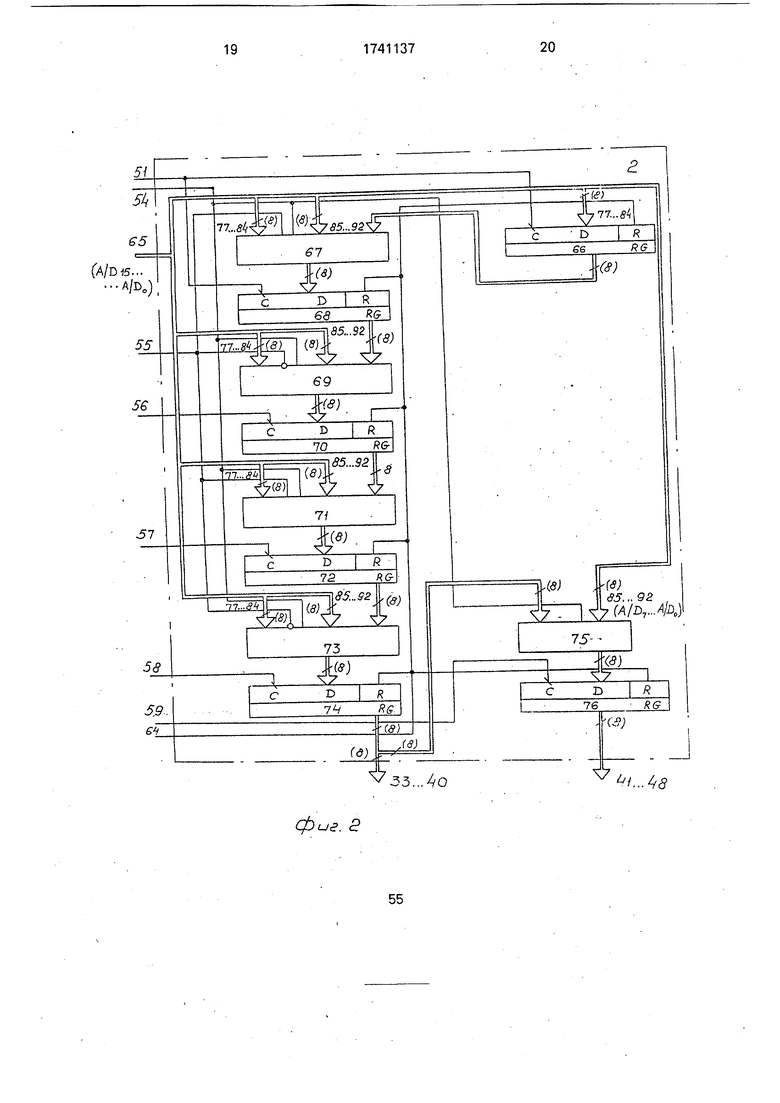

На фиг. 1 приведена структурная схема устройства; на фиг. 2-4 - функциональные

схемы соответственно запоминающего блока последовательности команд, коммутатора и счетчика команд; на фиг. 5 и 6 - временные диаграммы работы устройства. Устройство для контроля микропроцес0 сорной системы (фиг. 1) содержит блок 1 управления, запоминающий блок 2 после- дсвательности команд, блок 3 контроля, коммутатор 4, счетчик 5 команд, элемент ИЛИ 6, триггер 7, сумматор 8 по модулю два

5 и узел 9 управления, содержащий элемент ИЛИ-НЕ 10, первый элемент И 11, элемент И-ИЛИ 12, триггер 13, первый 14 и второй 15 одновибраторы, элемент НЕ 16, дешифратор 17, второй элемент ИЛИ 18, третий

0 элемент И 19, второй элемент И 20 и второй элемент ИЛИ 21, а также узел 22 контроля кодов и триггер 23, входящие в блок 3 контроля, первый-четвертый управляющие входы устройства 24-27, синхровход 28

5 устройств, пятый 29 и шестой 30 управляющие входы устройства, вход 31 сброса устройства, выход 32 сигнала ошибки устройства, первую 33...40 - вторую 41...48 группы выходов запоминающего блока по0 следовательности команд, первый управляющий вход 49 коммутатора и счетчика команд, восьмой 50 и первый 51 входы блока управления, второй 52 выход дешифратора, девятый 53, второй 54, третий 55 - седьмой

5 59 выходы блока управления, первый 60 - четвертый 63 выходы счетчика команд, 64 - десятый выход блока управления, 65 - информационный вход устройства.

На фиг. 1 информационный вход 65 уст0 ройства подключен к информационному входу запоминающего блока последовательности команд 2, синхровход устройства 28 подключен к синхровходу блока управления 1, с первого по шестой управляющие

5 входы блока управления подключены соответственно к первому-шестому 24-27, 29, 30 входам устройства, вход сброса блока 1 управления подключен к входу 31 сброса устройства, с первого по девятый выходы

0 51, 54 - 59, 50, 53 блока 1 управления соединены соответственно с первым-седьмым управляющими входами запоминающего блока 2 последовательности команд, с первым и вторым управляющими входами бло5 ка 3 контроля, третий управляющий вход которого и восьмой управляющий вход запоминающего блока 2 последовательности команд соединены с десятым выходом 64 блока управления. Первая 33...40 и вторая 41 ...48 группы выходов запоминающего

блока последовательности команд 2 соединены соответственно с первой и второй группами информационных входов узла 22 контроля, выход которого подключен к информационному входу триггера 23, прямой выход которого соединен с выходом 32 сигнала ошибки устройства. Синхронизирующий вход, вход разрешения записи и вход сброса триггера 23 соединены с выходами соответственно 50, 53 и 64 блока управления и с восьмым управляющим входом запоминающего блока 2 памяти команд.

В блоке 1 управления первый вход первого элемента И 11, первый и второй входы элемента ИЛИ-НЕ 10 узла управления подключены соответственно к первому, второму и третьему управляющим входам 24-26 блока управления. Выход элемента ИЛИ- НЕ 10 соединен с вторым входом первого элемента И 11, выход которого соединен с информационным входом триггера 13, прямой выход которого соединен с первым входом второго элемента И 20 и с первым входом элемента И-ИЛИ 12, второй вход которого соединен с синхровходом триггера 13, с входом элемента НЕ 16 и первого од- новибратора 14 и подключен к синхровходу 28 блока управления, вход 31 сброса которого подключен к первому входу элемента ИЛИ 16 блока управления и к третьему входу элемента И-ИЛИ 12, вход которого соединен с входом сброса триггера 13 узла управления, вход разрешения записи которого подключен к четвертому управляющему входу 27 блока управления. Выход первого одновибратора 14 соединен с вторым входом второго элемента И 20, выход которого соединен с первым входом первого элемента ИЛ И 21 узла управления, с первым входом управления режимом счетчика 5 команд, входом установки в единицу триггера 7 блока управления и с первым управляющим входом коммутатора 4, второй управляющий вход которого является восьмым выходом 50 блока управления и соединен с входом установки в нуль триггера 7, с вторым входом элемента ИЛИ 21, с вторым входом управления режимом счетчика 5 команд и с выходом третьего элемента И 19, первый и второй выходы которого соединены с выходами соответственно второго одновибратора 15 и второго элемента ИЛИ 18 узла управления, первый вход которого соединен с первым выходом дешифратора 17 и с девятым выходом 53 блока управления, пятый 29 и шестой 30 управляющие входы которого подключены соответственно к первому и второму входам дешифратора 17, второй и третий выходы которого соединены соответственно с вторым входом элемента ИЛИ 6 и вторым входом элемента ИЛИ 18. Выход элемента ИЛИ 21 является первым выходом 51 блока управления и подключен к синхровходу счетчика 5 команд,

вход сброса которого соединен с выходом элемента ИЛИ 6 и является десятым выходом блока управления, с первого по четвертый выходы 60-63 счетчика 5 команд соединены соответственно с первым-четвертым информационными входами коммутатора 4 и с первым-четвертым входами сумматора 8 по модулю два, выход которого является-третьим выходом 55 блока управления, с четвертого по седьмой выходы 5659 которого подключены соответственно к первому-четвертому выходам коммутатора 4. Выход триггера 7 является вторым выходом 54 блока управления.

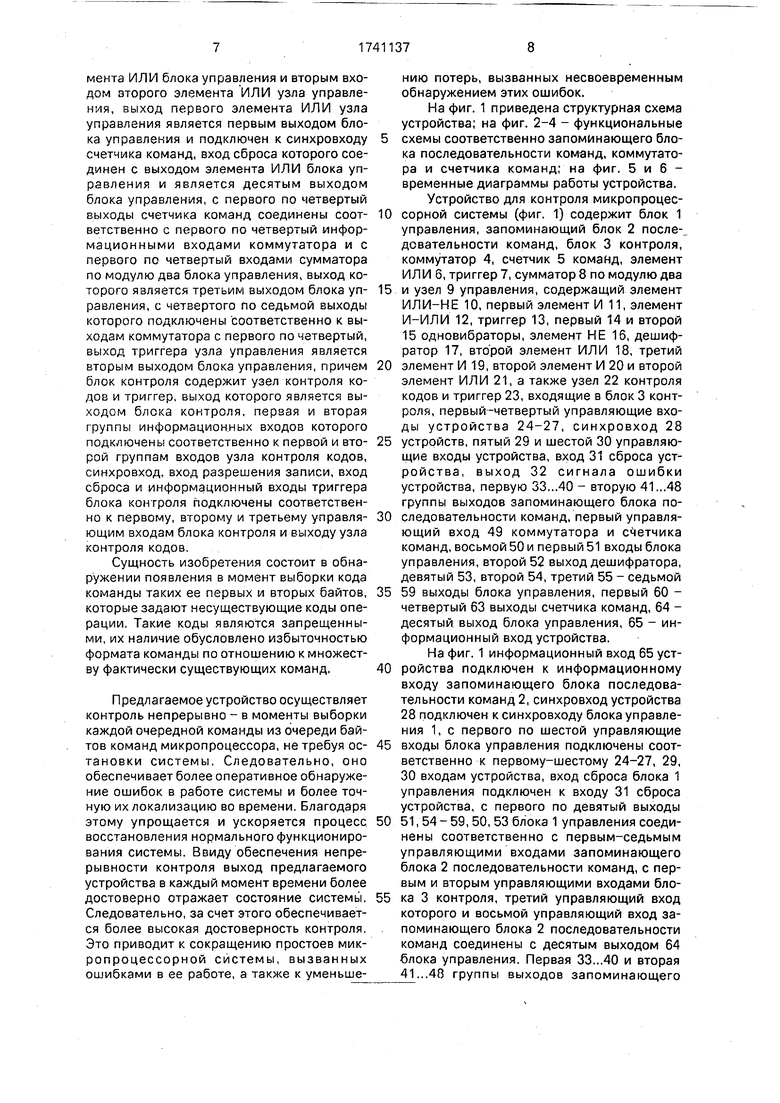

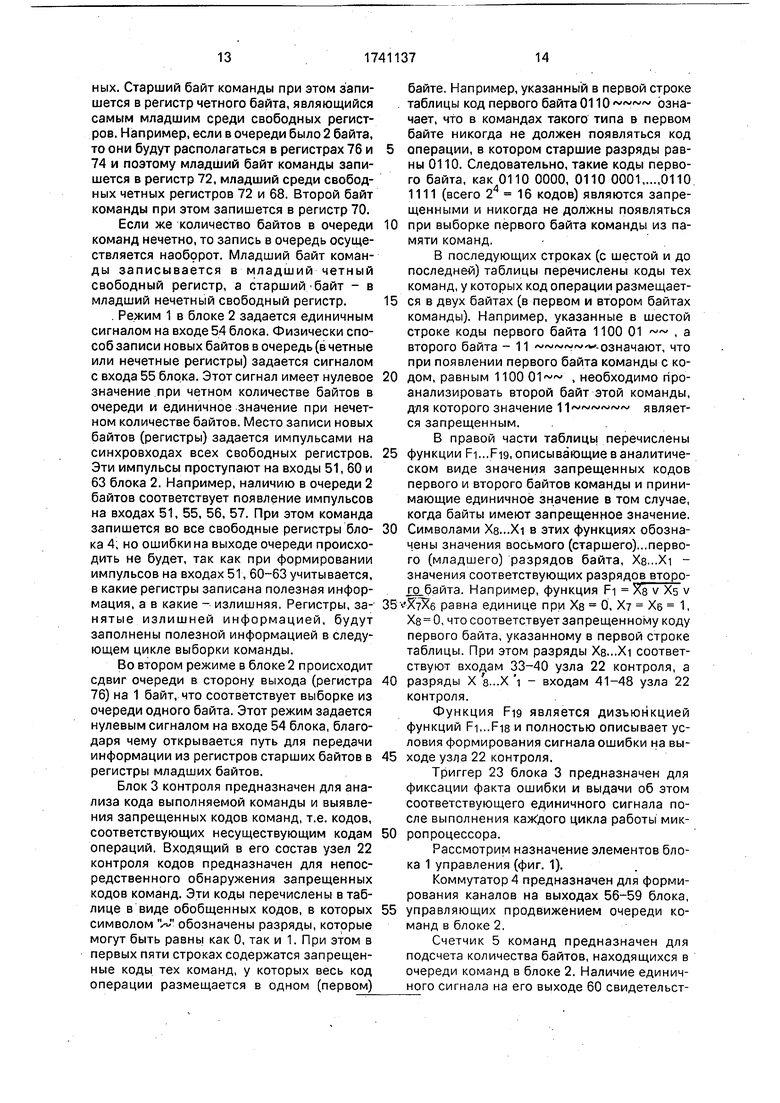

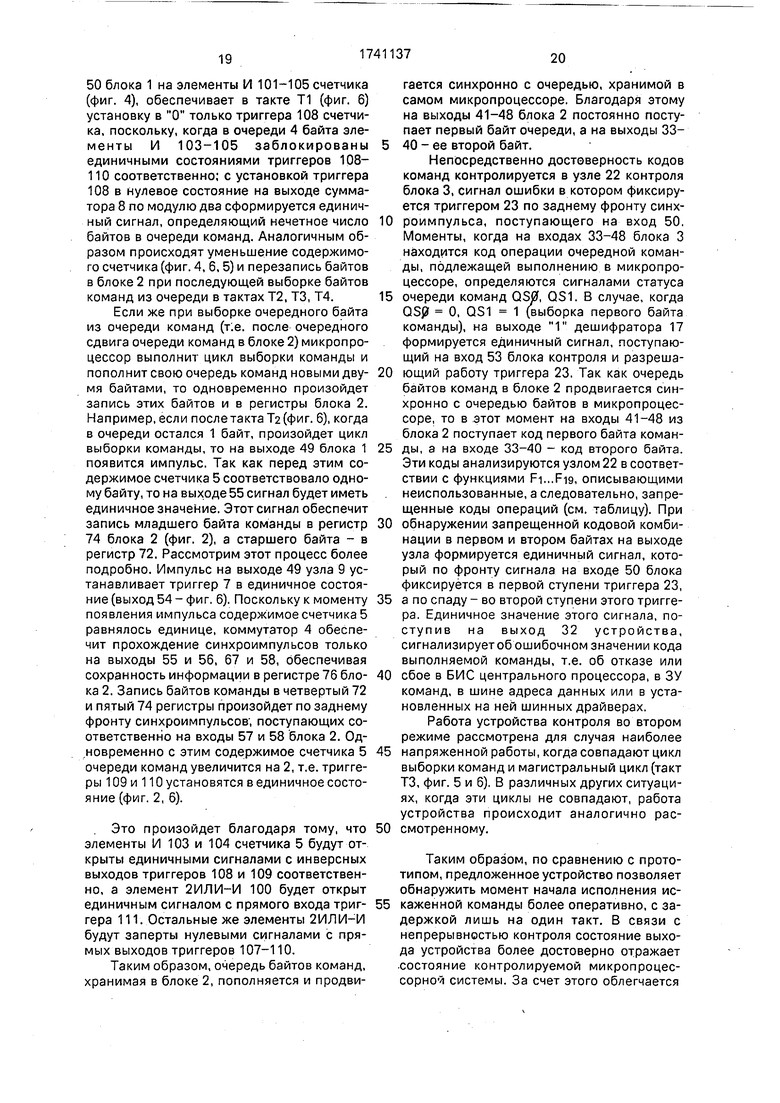

Запоминающий блок 2 последовательности команд (фиг. 2) содержит первый-ше- стой регистры 66, 68, 70, 72, 74, 76, первый-пятый коммутаторы 67, 69, 71. 73, 75, пятнадцатый 77 - восьмой 84 и седьмой

85 - нулевой 92 разряды информационного входа 65, соответствующие пятнадцатому- нулевому разрядам мультиплексной шины адреса данных, к которой подключен вход 65.

На фиг. 2 разряды 77-84 входа 65 блока 2 подключены к первому информационному входу коммутаторов 67, 69, 71, 73 и к информационному входу регистра 66 блока, разряды 85-92 входа 65 блока подключены к

второму информационному входу коммутаторов 67, 69, 71, 73 и 75. Выход регистра 66(68, 70, 72) соединен с третьим информационным входом коммутатора 67(69, 71, 73). Выход коммутатора 73 соединен с информационным входом регистра 74, выход которого соединен с вторым информационным входом коммутатора 75 и образует первую группу выходов 33-40 блока. Выход коммутатора 75 соединен с информационным входом регистра 76, выход которого образует вторую группу выходов 41-48 блока, первый управляющий вход 51 которого подключен к синхровходам регистров 66 и 68. Второй управляющий вход 54 блока подключен к

первым управляющим входам коммутаторов 67, 69, 71, 73 и к управляющему входу коммутатора 75. Третий управляющий вход 55 блока подключен к вторым управляющим входам коммутаторов 67, 69, 71, 73. С четвертого по седьмой управляющие входы 56- 59 блока подключены к синхровходам регистров соответственно 70, 72, 74 и 76. Восьмой управляющий вход 64 блока подключен к входам сброса регистров 66,68,70, 72, 74, 76.

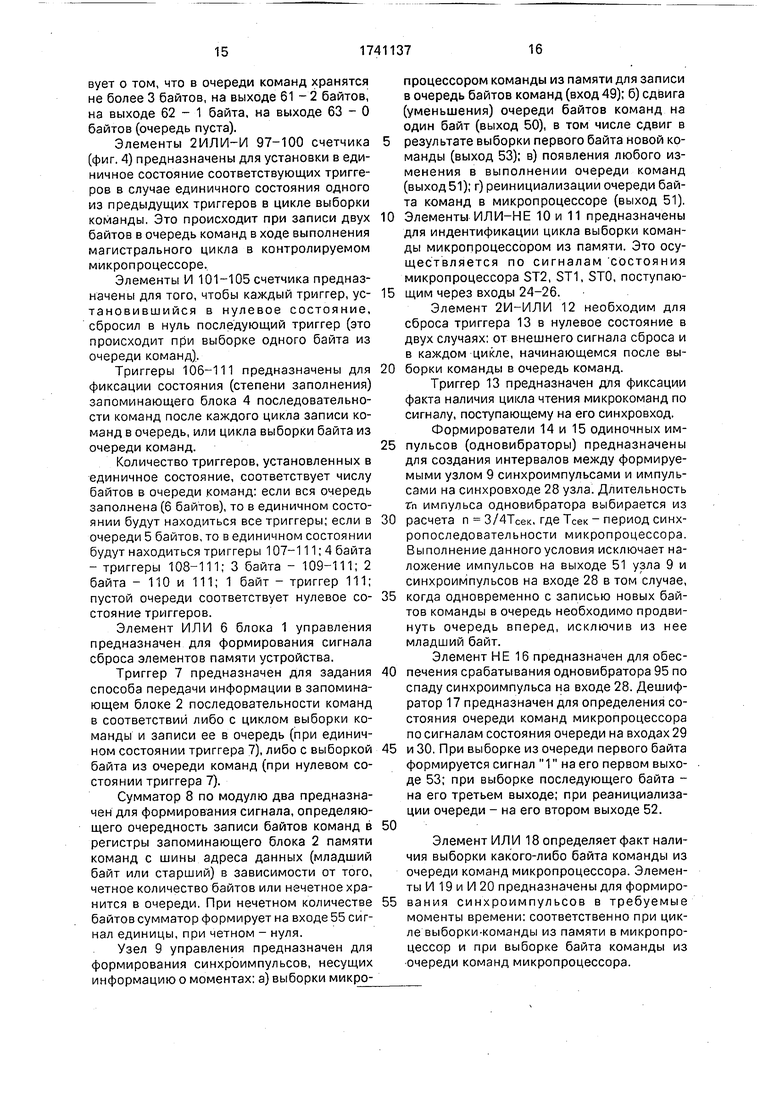

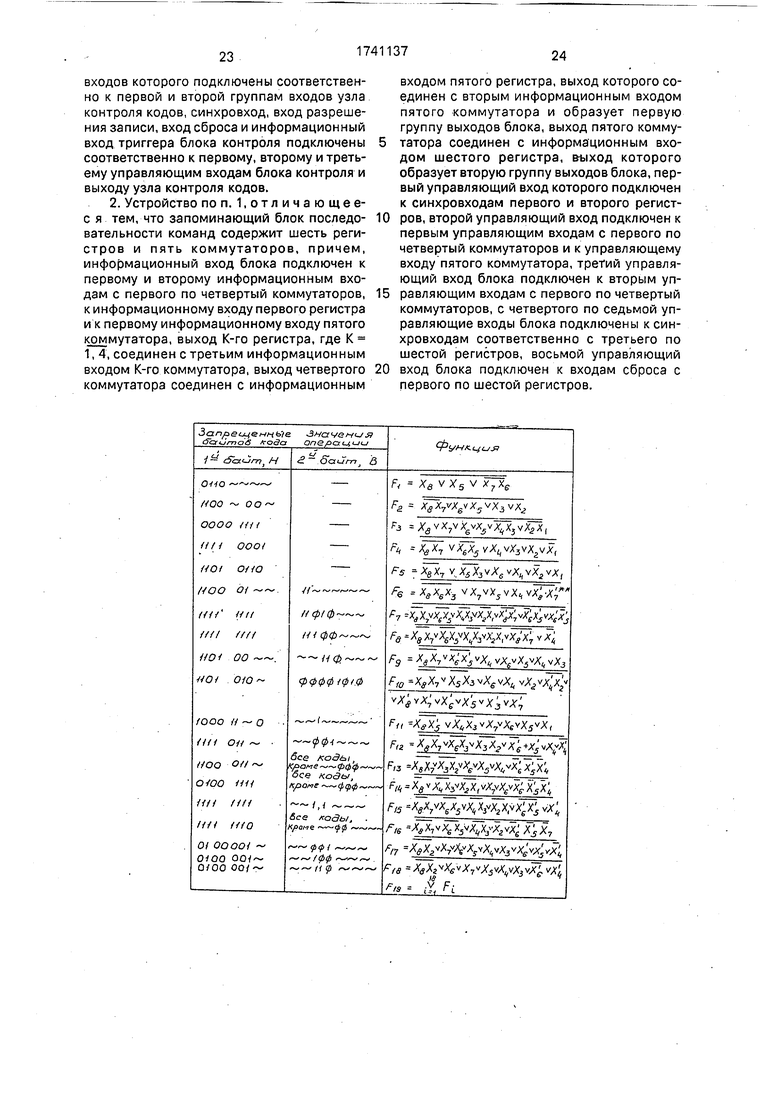

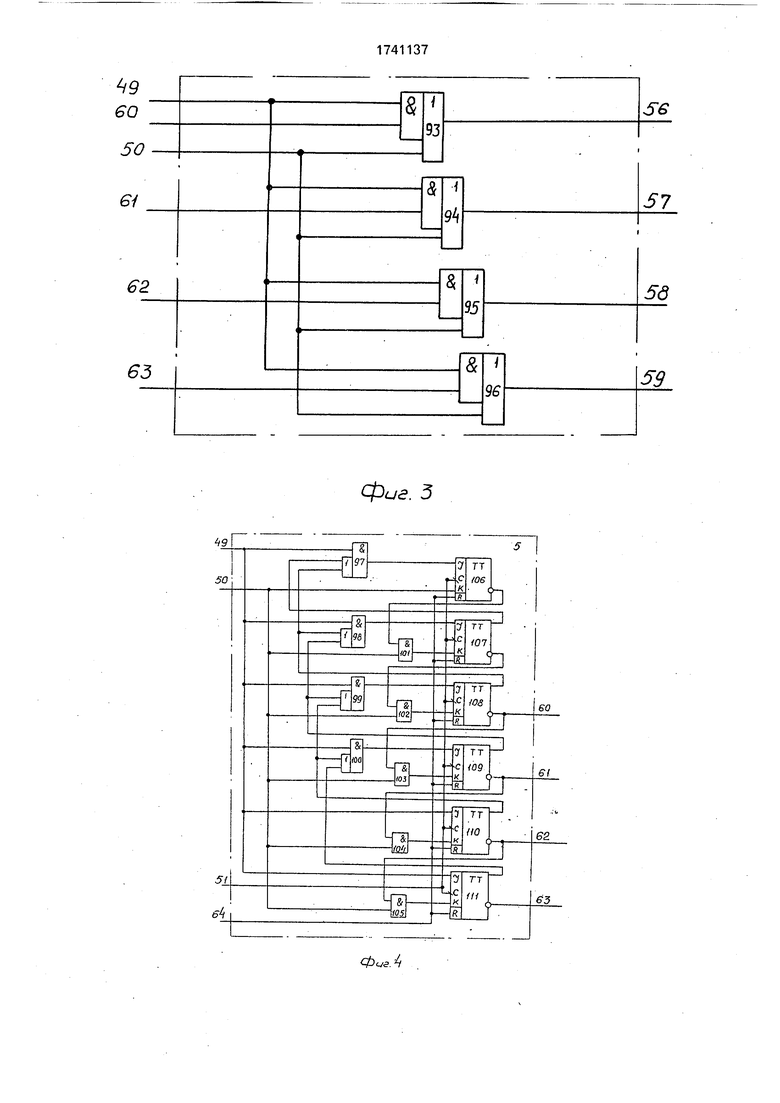

Коммутатор 4 (фиг. 3) содержит первый- четвертый элементы 2И-ИЛИ 93-96.

На фиг. 3 первый и второй управляющие входы 49 и 50 коммутатора 4 подключены соответственно к первым и вторым входам элементов 2И-ИЛИ 93-96. Первый-четвер- тый информационные входы 60-63 коммутатора подключены к третьим входам соответственно элементов 2И-ИЛИ 93-96, выходы которых подключены соответственно к выходам 56-59 коммутатора.

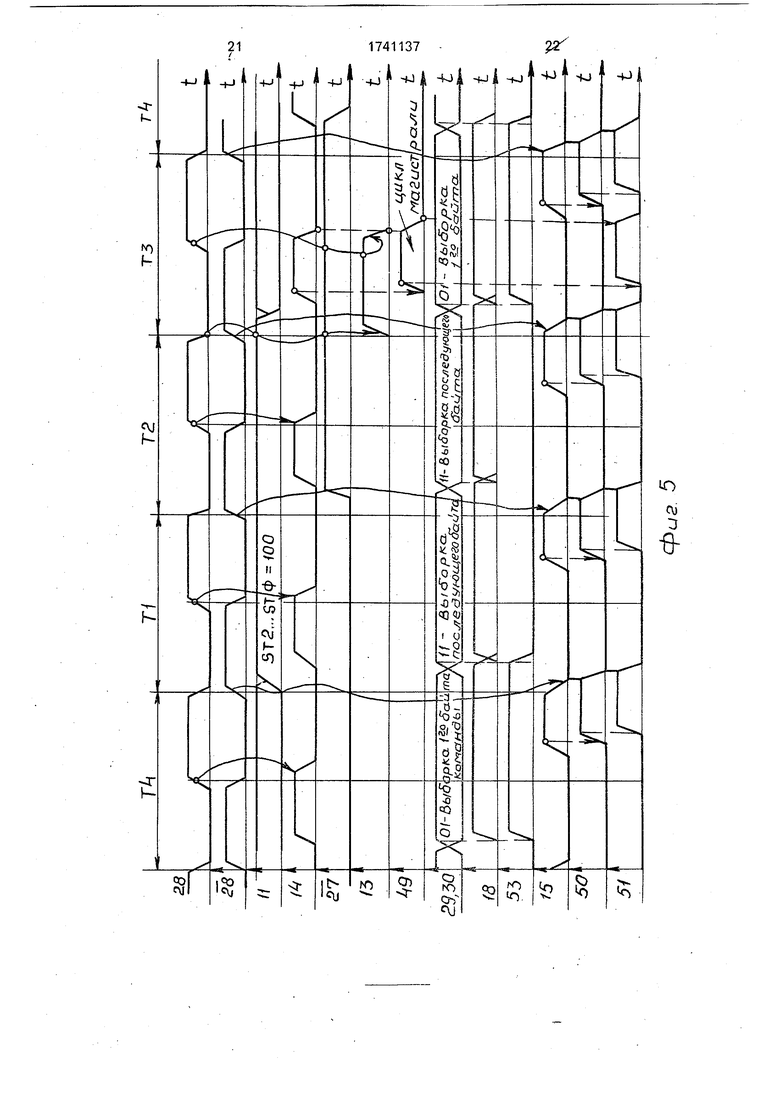

Счетчик 5 команд (фиг. 4) содержит пер- вый-четвертый 97-100 элементы 2ИЛИ-И, первый 101 - четвертый 102 элементы И, первый 106 - шестой 111 триггеры.

На фиг. 4 первый вход 49 счетчика 5 команд соединен с первыми входами первого 97 - четвертого 100 элементов 2ИЛИ-И, вторые входы которых соединены соответственно с прямыми выходами второго 107 - пятого 77 триггеров. Третьи входы элементов 2ИЛИ-И 97-100 соединены соответственно с прямыми выходами третьего 108 - шестого 111 триггеров. Выходы элементов 2ИЛИ-И 97-100 соединены соответственно с единичными входами триггеров 106-109. Первые входы первого 101 - четвертого 105 элементов И соединены с инверсными выходами соответственно триггеров 106-110. Вторые входы элементов И 101-105 соединены с вторым входом 50 счетчика 3 команд. Выходы элементов И 101-105 соединены соответственно с входами установки в нуль триггеров 107-111. Вход установки в нуль триггера 106 соединен с вторым входом 50 счетчика 3 команд, первый вход 49 которого соединен с единичными входами триггеров 110 и 111. Синхровход 51 счетчика 3 команд соединен с входами синхронизации триггеров 106-111. Вход 64 сброса счетчика 3 команд соединен с входами сброса триггеров 106-111. Выходы триггеров 108-111 соединены соответственно с первым 60 - четвертым 63 выходами счетчика 3 команд.

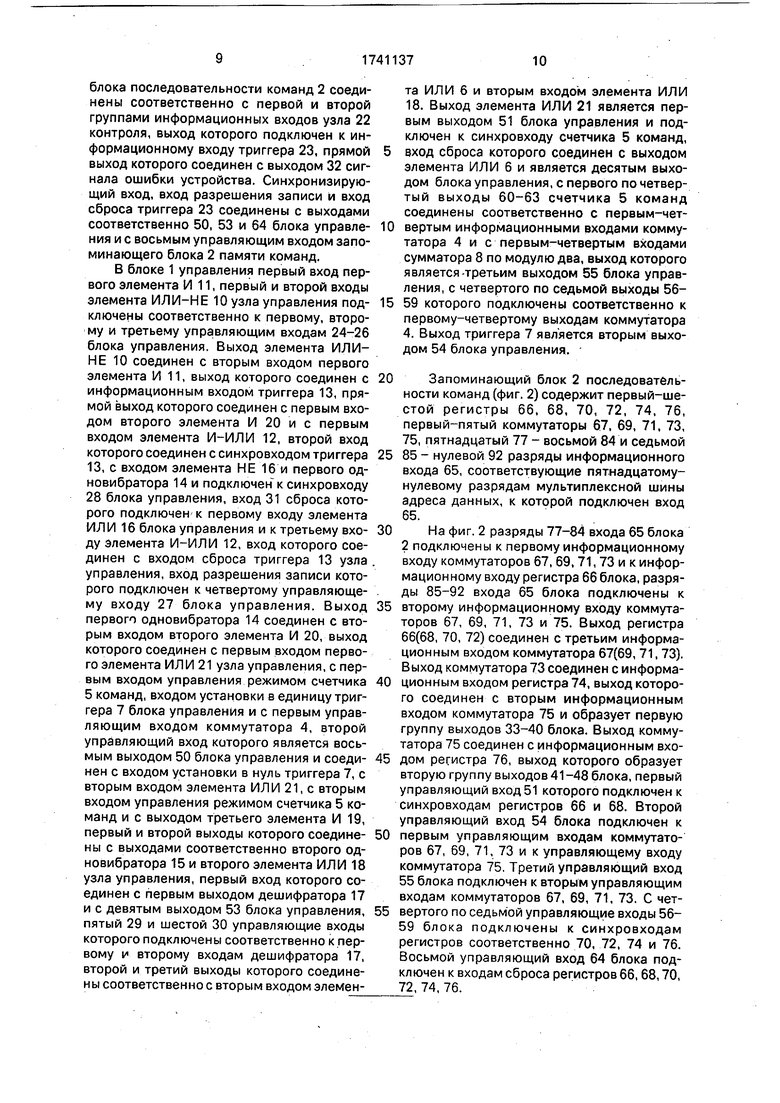

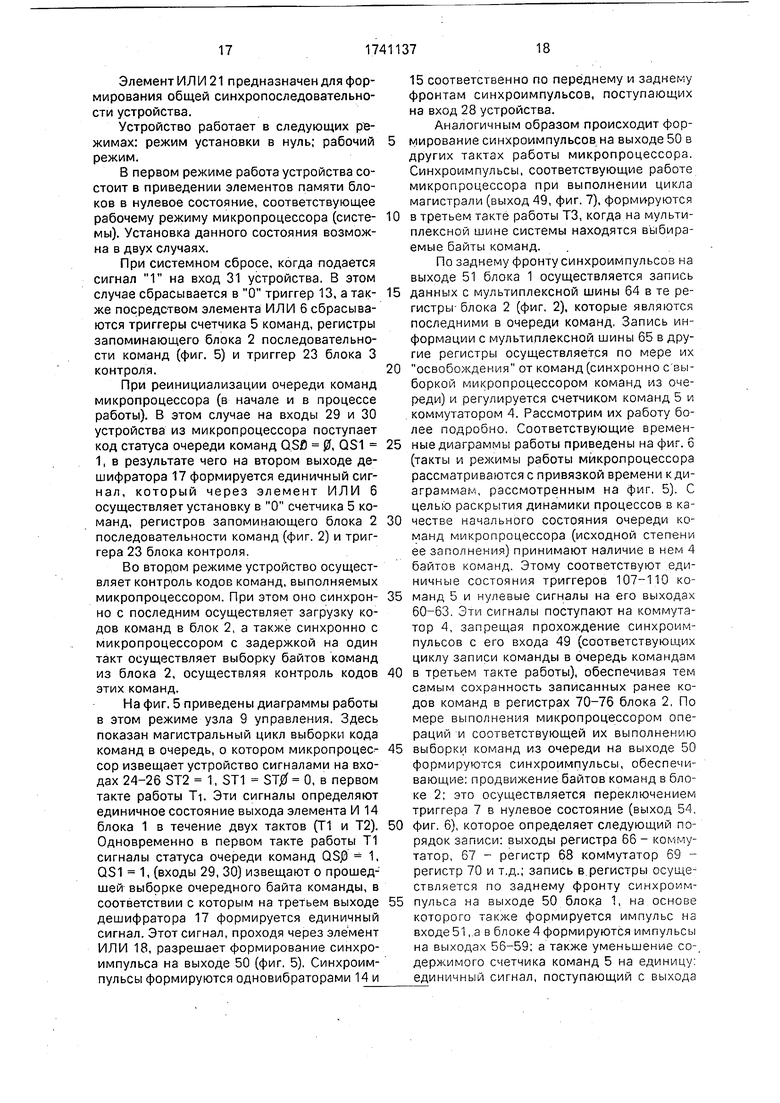

Обозначения осей временных диаграмм на фиг. 5 и 6 соответствуют обозначениям элементов и связей, введенных на фиг. 1-4. Рассмотрим назначение элементов устройства.

Блок 1 управления предназначен для управления работой устройства. Запоминающий блок 2 последовательности команд предназначен для записи байтов команд с шины 64 адреса данных и выдачи их в блок 3 контроля синхронно с выборкой байтов команд из устройства очереди контролируемого микропроцессора.

Регистры 66, 68, 70, 72, 74, 76 блока 2 (фиг. 2) предназначены для записи байтов команд и их продвижения к выходам блока

2 синхронно с работой устройства очереди команд микропроцессора. В регистре 76 хранится байт, являющийся в очереди первым (т.е. ближайшим к выходу), в регистрах

5 74-66 соответственно второй-шестой байты очереди. Соответственно этому, регистры 76, 72, 68 являются регистрами нечетных байтов, а регистры 74, 70, 66 - регистрами четных байтов. Все регистры являются двух0 тактными.

Коммутаторы 67, 69, 71, 73, 75 блока 2 предназначены для управления записью байтов в зависимости от типа выполняемого цикла (выборки команды или выборки байта

5 из очереди команд), а также от степени заполнения очереди.

Логика работы коммутаторов 67 и 71 следующая: при подаче нулевого сигнала на первый управляющий вход 54, на выход ком0 мутатора, независимо от сигнала на втором управляющем входе 55, подается информация с третьего информационного входа, т.е. от предыдущего регистра. При подаче на вход 54 единицы, а на вход 55 - нуля, на

5 выход коммутатора передается информация с второго информационного входа 85- 92. При подаче на вход 54 нуля, а на вход 55 -единицы, на выход коммутатора передается информация с первого информационного

0 входа 77-84.

Коммутаторы 69 и 73 блока 2 отличаются от рассмотренных наличием инвертора на входе 55. Коммутатор 75 при наличии нуля на управляющем входе 55 передает на вы5 ход информацию с входа 33-40, а при наличии единицы - с входа 85-92.

В работе запоминающего блока последовательности команд 2 можно выделить два режима:

0 1) запись байтов команд в регистре (при выполнении контролируемым микропроцессором магистрального цикла выборки команды);

2) продвижение очереди команд из ре5 гистров старших байтов в регистры младших байтов путем перезаписи информации из регистров меньших номеров в регистры старших номеров - например, из 66 - в 68, из 68 - в 70, из 70 - в 78 и т.д. (при выполне0 нии микропроцессором цикла выборки байта из очереди команд).

В первом режиме в регистры блока 2 записываются сразу 2 байта команды (старший и младший), причем место их записи

5 (регистр) определяется четностью количества байтов, находящихся в очереди команд в момент записи, Если количество байтов в очереди четно, то младший байт команды записывается в регистр нечетного байта, яв гтющийся самым младшим из числа свободных. Старший байт команды при этом запишется в регистр четного байта, являющийся самым младшим среди свободных регистров. Например, если в очереди было 2 байта, то они будут располагаться в регистрах 76 и 74 и поэтому младший байт команды запишется в регистр 72, младший среди свободных четных регистров 72 и 68. Второй байт команды при этом запишется в регистр 70.

Если же количество байтов в очереди команд нечетно, то запись в очередь осуществляется наоборот. Младший байт команды записывается в младший четный свободный регистр, а старший байт - в младший нечетный свободный регистр.

Режим 1 в блоке 2 задается единичным сигналом на входе 54 блока. Физически способ записи новых байтов в очередь (в четные или нечетные регистры) задается сигналом с входа 55 блока. Этот сигнал имеет нулевое значение при четном количестве байтов в очереди и единичное значение при нечетном количестве байтов. Место записи новых байтов (регистры) задается импульсами на синхровходах всех свободных регистров. Эти импульсы проступают на входы 51, 60 и 63 блока 2. Например, наличию в очереди 2 байтов соответствует появление импульсов на входах 51, 55, 56, 57. При этом команда запишется во все свободные регистры блока 4, но ошибки на выходе очереди происходить не будет, так как при формировании импульсов на входах 51, 60-63 учитывается, в какие регистры записана полезная информация, а в какие - излишняя. Регистры, занятые излишней информацией, будут заполнены полезной информацией в следующем цикле выборки команды.

Во втором режиме в блоке 2 происходит сдвиг очереди в сторону выхода (регистра 76) на 1 байт, что соответствует выборке из очереди одного байта. Этот режим задается нулевым сигналом на входе 54 блока, благодаря чему открывается путь для передачи информации из регистров старших байтов в регистры младших байтов.

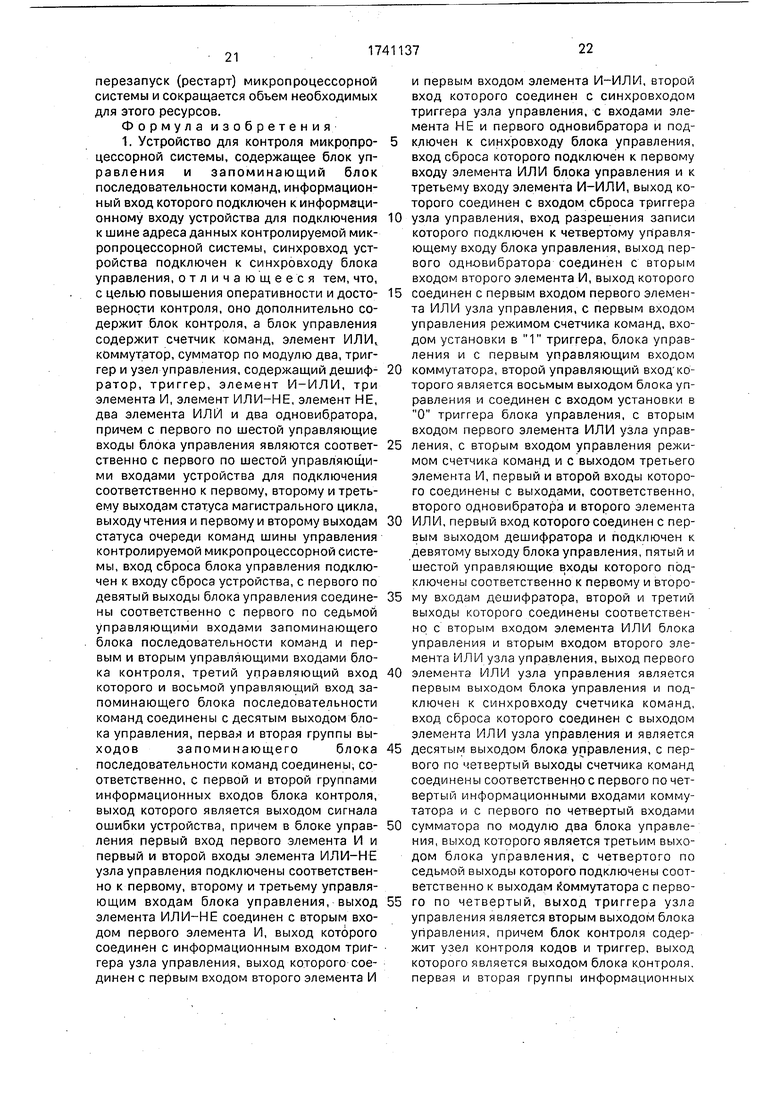

Блок 3 контроля предназначен для анализа кода выполняемой команды и выявления запрещенных кодов команд, т.е. кодов, соответствующих несуществующим кодам операций. Входящий в его состав узел 22 контроля кодов предназначен для непосредственного обнаружения запрещенных кодов команд. Эти коды перечислены в таблице в виде обобщенных кодов, в которых символом V обозначены разряды, которые могут быть равны как 0, так и 1. При этом в первых пяти строках содержатся запрещенные коды тех команд, у которых весь код операции размещается в одном (первом)

байте. Например, указанный в первой строке таблицы код первого байта 0110 означает, что в командах такого типа в первом байте никогда не должен появляться код

операции, в котором старшие разряды равны 0110. Следовательно, такие коды первого байта, как 0110 0000, 0110 00010110

1111 (всего 24 16 кодов) являются запрещенными и никогда не должны появляться

0 при выборке первого байта команды из памяти команд,

В последующих строках (с шестой и до последней) таблицы перечислены коды тех команд, у которых код операции размещает5 ся в двух байтах (в первом и втором байтах команды). Например, указанные в шестой строке коды первого байта 1100 01 , а второго байта - 11 -означают, что при появлении первого байта команды с ко0 дом, равным 1100 01 , необходимо проанализировать второй байт этой команды, для которого значение 11 является запрещенным.

В правой части таблицы перечислены

5 функции Fi...Fi9, описывающие в аналитическом виде значения запрещенных кодов первого и второго байтов команды и принимающие единичное значение в том случае, когда байты имеют запрещенное значение.

0 Символами Xs...Xi в этих функциях обозначены значения восьмого (старшего)...первого (младшего) разрядов байта, Xs...Xi - значения соответствующих разрядов второго байта. Например, функция Fi X°s v ХБ v

равна единице при Xs О, X Хб 1, Х8 0, что соответствует запрещенному коду первого байта, указанному в первой строке таблицы. При этом разряды Xs...Xi соответствуют входам 33-40 узла 22 контроля, а

0 разряды X 8...Х т - входам 41-48 узла 22 контроля.

Функция Fig является дизъюнкцией функций Fi,..Fis и полностью описывает условия формирования сигнала ошибки на вы5 ходе узла 22 контроля.

Триггер 23 блока 3 предназначен для фиксации факта ошибки и выдачи об этом соответствующего единичного сигнала после выполнения каждого цикла работы мик0 ропроцессора.

Рассмотрим назначение элементов блока 1 управления (фиг. 1).

Коммутатор 4 предназначен для формирования каналов на выходах 56-59 блока,

5 управляющих продвижением очереди команд в блоке 2.

Счетчик 5 команд предназначен для подсчета количества байтов, находящихся в очереди команд в блоке 2. Наличие единичного сигнала на его выходе 60 свидетельствует о том, что в очереди команд хранятся не более 3 байтов, на выходе 61-2 байтов, на выходе 62-1 байта, на выходе 63-0 байтов (очередь пуста).

Элементы 2ИЛИ-И 97-100 счетчика (фиг. 4) предназначены для установки в единичное состояние соответствующих триггеров в случае единичного состояния одного из предыдущих триггеров в цикле выборки команды. Это происходит при записи двух байтов в очередь команд в ходе выполнения магистрального цикла в контролируемом микропроцессоре.

Элементы И 101-105 счетчика предназначены для того, чтобы каждый триггер, установившийся в нулевое состояние, сбросил в нуль последующий триггер (это происходит при выборке одного байта из очереди команд).

Триггеры 106-111 предназначены для фиксации состояния (степени заполнения) запоминающего блока 4 последовательности команд после каждого цикла записи команд в очередь, или цикла выборки байта из очереди команд.

Количество триггеров, установленных в единичное состояние, соответствует числу байтов в очереди команд: если вся очередь заполнена (6 байтов), то в единичном состоянии будут находиться все триггеры; если в очереди 5 байтов, то в единичном состоянии будут находиться триггеры 107-111; 4 байта - триггеры 108-111; 3 байта - 109-111; 2 байта - 110 и 111; 1 байт - триггер 111; пустой очереди соответствует нулевое состояние триггеров.

Элемент ИЛИ 6 блока 1 управления предназначен для формирования сигнала сброса элементов памяти устройства.

Триггер 7 предназначен для задания способа передачи информации в запоминающем блоке 2 последовательности команд в соответствии либо с циклом выборки команды и записи ее в очередь (при единичном состоянии триггера 7), либо с выборкой байта из очереди команд (при нулевом состоянии триггера 7).

Сумматор 8 по модулю два предназначен для формирования сигнала, определяющего очередность записи байтов команд в регистры запоминающего блока 2 памяти команд с шины адреса данных (младший байт или старший) в зависимости от того, четное количество байтов или нечетное хранится в очереди. При нечетном количестве байтов сумматор формирует на входе 55 сигнал единицы, при четном - нуля.

Узел 9 управления предназначен для формирования синхроимпульсов, несущих информацию о моментах; а) выборки микропроцессором команды из памяти для записи в очередь байтов команд (вход 49); б) сдвига (уменьшения) очереди байтов команд на один байт (выход 50), в том числе сдвиг в результате выборки первого байта новой команды (выход 53); в) появления любого изменения в выполнении очереди команд (выход 51); г) реинициализации очереди байта команд в микропроцессоре (выход 51).

Элементы ИЛИ-НЕ 10 и 11 предназначены для индентификации цикла выборки команды микропроцессором из памяти. Это осуществляется по сигналам состояния микропроцессора ST2, ST1, STO, поступающим через входы 24-26.

Элемент 2И-ИЛИ 12 необходим для сброса триггера 13 в нулевое состояние в двух случаях: от внешнего сигнала сброса и в каждом цикле, начинающемся после выборки команды в очередь команд.

Триггер 13 предназначен для фиксации факта наличия цикла чтения микрокоманд по сигналу, поступающему на его синхровход. Формирователи 14 и 15 одиночных импульсов (одновибраторы) предназначены для создания интервалов между формируемыми узлом 9 синхроимпульсами и импульсами на синхровходе 28 узла. Длительность Гп импульса одновибратора выбирается из

расчета п 3/4ТСек, где ТСек - период синх- ропоследовательности микропроцессора. Выполнение данного условия исключает наложение импульсов на выходе 51 узла 9 и синхроимпульсов на входе 28 в том случае,

когда одновременно с записью новых байтов команды в очередь необходимо продвинуть очередь вперед, исключив из нее младший байт.

Элемент НЕ 16 предназначен для обеспечения срабатывания одновибратора 95 по спаду синхроимпульса на входе 28. Дешифратор 17 предназначен для определения состояния очереди команд микропроцессора по сигналам состояния очереди на входах 29

и 30. При выборке из очереди первого байта формируется сигнал 1 на его первом выходе 53; при выборке последующего байта - на его третьем выходе; при реанициализа- ции очереди - на его втором выходе 52.

Элемент ИЛ И 18 определяет факт наличия выборки какого-либо байта команды из очереди команд микропроцессора. Элементы И 19 и И 20 предназначены для формирования синхроимпульсов в требуемые моменты времени: соответственно при цикле выборки-команды из памяти в микропроцессор и при выборке байта команды из очереди команд микропроцессора.

Элемент ИЛИ21 предназначен для формирования общей синхропоследовательно- сти устройства.

Устройство работает в следующих режимах: режим установки в нуль; рабочий режим.

В первом режиме работа устройства состоит в приведении элементов памяти блоков в нулевое состояние, соответствующее рабочему режиму микропроцессора (системы). Установка данного состояния возможна в двух случаях.

При системном сбросе, когда подается сигнал 1 на вход 31 устройства. В этом случае сбрасывается в О триггер 13, а также посредством элемента ИЛИ 6 сбрасываются триггеры счетчика 5 команд, регистры запоминающего блока 2 последовательности команд (фиг. 5) и триггер 23 блока 3 контроля.

При реинициализации очереди команд микропроцессора (в начале и в процессе работы). В этом случае на входы 29 и 30 устройства из микропроцессора поступает код статуса очереди команд QSS 0, QS1 1, в результате чего на втором выходе дешифратора 17 формируется единичный сигнал, который через элемент ИЛИ 6 осуществляет установку в О счетчика 5 команд, регистров запоминающего блока 2 последовательности команд (фиг. 2) и триггера 23 блока контроля.

Во втором режиме устройство осуществляет контроль кодов команд, выполняемых микропроцессором. При этом оно синхронно с последним осуществляет загрузку кодов команд в блок 2, а также синхронно с микропроцессором с задержкой на один такт осуществляет выборку байтов команд из блока 2, осуществляя контроль кодов этих команд.

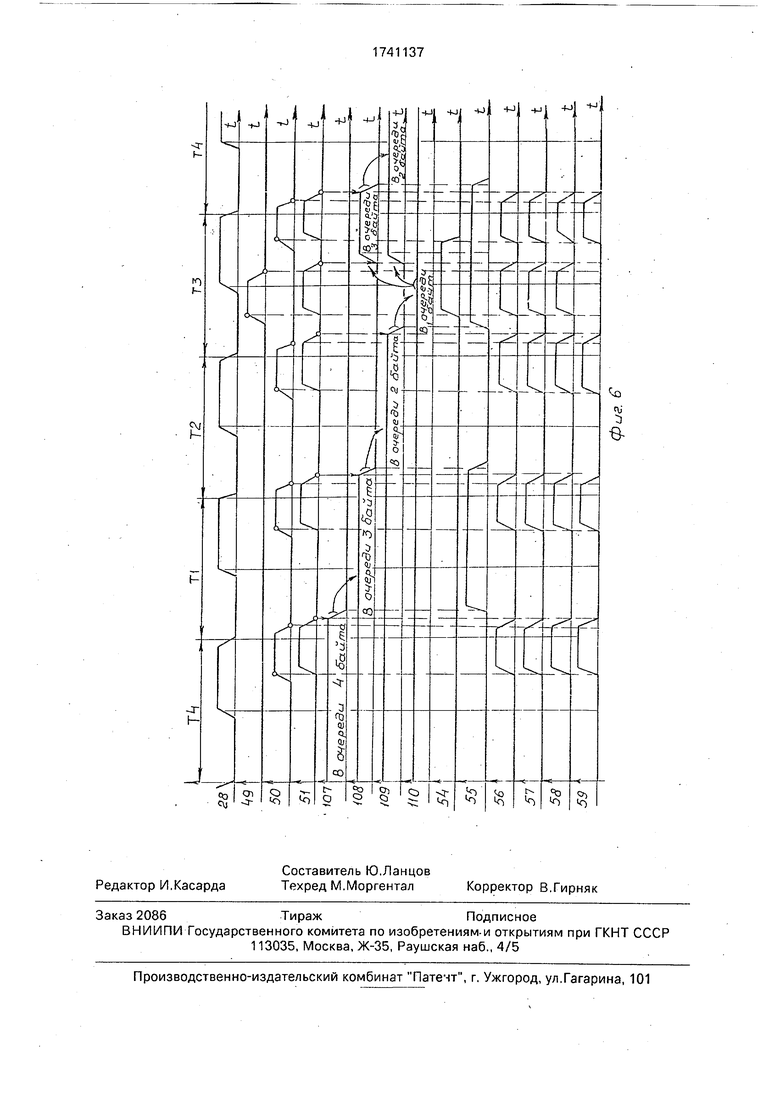

На фиг, 5 приведены диаграммы работы в этом режиме узла 9 управления. Здесь показан магистральный цикл выборки кода команд в очередь, о котором микропроцессор извещает устройство сигналами на входах 24-26 ST2 1, ST1 ST0 0, в первом такте работы TL Эти сигналы определяют единичное состояние выхода элемента И 14 блока 1 в течение двух тактов (Т1 и Т2). Одновременно в первом такте работы Т1 сигналы статуса очереди команд QSJ3 1, QS1 1, (входы 29, 30) извещают о прошедшей выборке очередного байта команды, в соответствии с которым на третьем выходе дешифратора 17 формируется единичный сигнал. Этот сигнал, проходя через элемент ИЛИ 18, разрешает формирование синхроимпульса на выходе 50 (фиг, 5). Синхроимпульсы формируются одновибраторами 14 и

15 соответственно по переднему и заднему фронтам синхроимпульсов, поступающих на вход 28 устройства.

Аналогичным образом происходит формирование синхроимпульсов на выходе 50 в других тактах работы микропроцессора. Синхроимпульсы, соответствующие работе микропроцессора при выполнении цикла магистрали (выход 49, фиг. 7), формируются

0 в третьем такте работы ТЗ, когда на мультиплексной шине системы находятся выбираемые байты команд.

По заднему фронту синхроимпульсов на выходе 51 блока 1 осуществляется запись

5 данных с мультиплексной шины 64 в те регистры блока 2 (фиг. 2), которые являются последними в очереди команд, Запись информации с мультиплексной шины 65 в другие регистры осуществляется по мере их

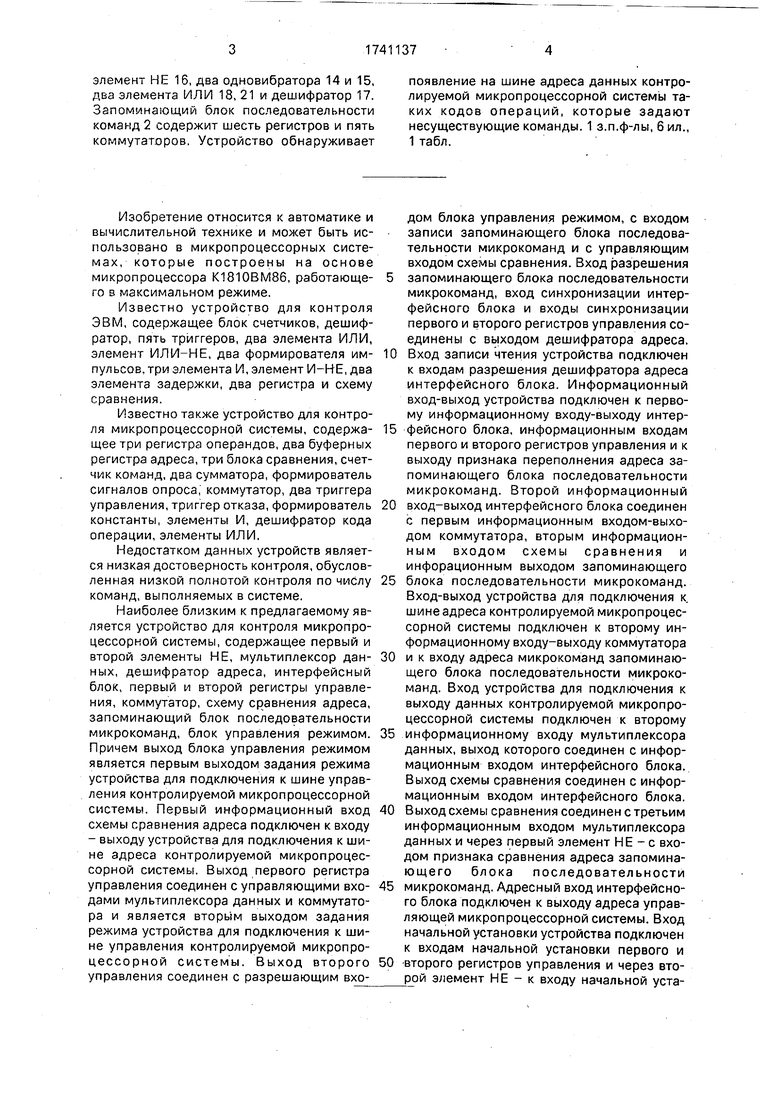

0 освобождения от команд (синхронно с выборкой микропроцессором команд из очереди) и регулируется счетчиком команд 5 и коммутатором 4. Рассмотрим их работу более подробно. Соответствующие времен5 ные диаграммы работы приведены на фиг. 6 (такты и режимы работы микропроцессора рассматриваются с привязкой времени к диаграммам, рассмотренным на фиг. 5). С целью раскрытия динамики процессов в ка0 честве начального состояния очереди команд микропроцессора (исходной степени ее заполнения) принимают наличие в нем 4 байтов команд. Этому соответствуют единичные состояния триггеров 107-110 ко5 манд 5 и нулевые сигналы на его выходах 60-63 Эти сигналы поступают на коммутатор 4, запрещая прохождение синхроимпульсов с его входа 49 (соответствующих циклу записи команды в очередь командам

0 в третьем такте работы), обеспечивая тем самым сохранность записанных ранее кодов команд в регистрах 70-76 блока 2, По мере выполнения микропроцессором операций и соответствующей их выполнению

5 выборки команд из очереди на выходе 50 формируются синхроимпульсы, обеспечивающие: продвижение байтов команд в блоке 2; это осуществляется переключением триггера 7 в нулевое состояние (выход 54

0 фиг. 6), которое определяет следующий порядок записи: выходы регистра 66 - коммутатор, 67 - регистр 68 коммутатор 69 - регистр 70 и т.д.; запись в регистры осуществляется по заднему фронту синхроим5 пульса на выходе 50 блока 1, на основе которого также формируется импульс на входе 51, а в блоке 4 формируются импульсы на выходах 56-59; а также уменьшение содержимого счетчика команд 5 на единицу единичный сигнал, поступающий с выхода

50 блока 1 на элементы И 101-105 счетчика (фиг. 4), обеспечивает в такте Т1 (фиг. 6) установку в О только триггера 108 счетчика, поскольку, когда в очереди 4 байта элементы И 103-105 заблокированы единичными состояниями триггеров 108- 110 соответственно; с установкой триггера 108 в нулевое состояние на выходе сумматора 8 по модулю два сформируется единичный сигнал, определяющий нечетное число байтов в очереди команд. Аналогичным образом происходят уменьшение содержимого счетчика (фиг. 4, 6,5) и перезапись байтов в блоке 2 при последующей выборке байтов команд из очереди в тактах Т2, ТЗ, Т4.

Если же при выборке очередного байта из очереди команд (т.е. после очередного сдвига очереди команд в блоке 2) микропроцессор выполнит цикл выборки команды и пополнит свою очередь команд новыми двумя байтами, то одновременно произойдет запись этих байтов и в регистры блока 2. Например, если после такта Т2 (фиг. 6), когда в очереди остался 1 байт, произойдет цикл выборки команды, то на выходе 49 блока 1 появится импульс. Так как перед этим содержимое счетчика 5 соответствовало одному байту, то на выходе 55 сигнал будет иметь единичное значение. Этот сигнал обеспечит запись младшего байта команды в регистр 74 блока 2 (фиг. 2), а старшего байта - в регистр 72. Рассмотрим этот процесс более подробно. Импульс на выходе 49 узла 9 устанавливает триггер 7 в единичное состояние (выход 54 - фиг. 6). Поскольку к моменту появления импульса содержимое счетчика 5 равнялось единице, коммутатор 4 обеспечит прохождение синхроимпульсов только на выходы 55 и 56, 67 и 58, обеспечивая сохранность информации в регистре 76 блока 2. Запись байтов команды в четвертый 72 и пятый 74 регистры произойдет по заднему фронту синхроимпульсов, поступающих соответственно на входы 57 и 58 блока 2. Одновременно с этим содержимое счетчика 5 очереди команд увеличится на 2, т.е. триггеры 109 и 110 установятся в единичное состояние (фиг. 2, 6).

Это произойдет благодаря тому, что элементы И 103 и 104 счетчика 5 будут открыты единичными сигналами с инверсных выходов триггеров 108 и 109 соответственно, а элемент 2ИЛИ-И 100 будет открыт единичным сигналом с прямого входа триггера 111. Остальные же элементы 2ИЛИ-И будут заперты нулевыми сигналами с прямых выходов триггеров 107-110.

Таким образом, очередь байтов команд, хранимая в блоке 2, пополняется и продвигается синхронно с очередью, хранимой в самом микропроцессоре. Благодаря этому на выходы 41-48 блока 2 постоянно поступает первый байт очереди, а на выходы 3340 - ее второй байт.

Непосредственно достоверность кодов команд контролируется в узле 22 контроля блока 3, сигнал ошибки в котором фиксируется триггером 23 по заднему фронту синхроимпульса, поступающего на вход 50. Моменты, когда на входах 33-48 блока 3 находится код операции очередной команды, подлежащей выполнению в микропроцессоре, определяются сигналами статуса

очереди команд QS0, QS1. В случае, когда QSJ О, QS1 1 (выборка первого байта команды), на выходе 1 дешифратора 17 формируется единичный сигнал, поступающий на вход 53 блока контроля и разрешающий работу триггера 23. Так как очередь байтов команд в блоке 2 продвигается синхронно с очередью байтов в микропроцессоре, то в этот момент на входы 41-48 из блока 2 поступает код первого байта команды, а на входе 33-40 - код второго байта. Эти коды анализируются узлом 22 в соответствии с функциями Fi...Fig, описывающими неиспользованные, а следовательно, запрещенные коды операций (см. таблицу). При

обнаружении запрещенной кодовой комбинации в первом и втором байтах на выходе узла формируется единичный сигнал, который по фронту сигнала на входе 50 блока фиксируется в первой ступени триггера 23,

а по спаду - во второй ступени этого триггера. Единичное значение этого сигнала, поступив на выход 32 устройства, сигнализирует об ошибочном значении кода выполняемой команды, т.е. об отказе или

сбое в БИС центрального процессора, в ЗУ команд, в шине адреса данных или в установленных на ней шинных драйверах.

Работа устройства контроля во втором режиме рассмотрена для случая наиболее

напряженной работы, когда совпадают цикл выборки команд и магистральный цикл (такт ТЗ, фиг. 5 и 6). В различных других ситуациях, когда эти циклы не совпадают, работа устройства происходит аналогично рассмотренному.

Таким образом, по сравнению с прототипом, предложенное устройство позволяет обнаружить момент начала исполнения ис- каженной команды более оперативно, с задержкой лишь на один такт. В связи с непрерывностью контроля состояние выхода устройства более достоверно отражает состояние контролируемой микропроцессорной системы. За счет этого облегчается

перезапуск (рестарт) микропроцессорной системы и сокращается объем необходимых для этого ресурсов.

Формула изобретения 1. Устройство для контроля микропро- цессорной системы, содержащее блок управления и запоминающий блок последовательности команд, информационный вход которого подключен к информационному входу устройства для подключения к шине адреса данных контролируемой микропроцессорной системы, синхровход устройства подключен к синхровходу блока управления, отличающееся тем, что, с целью повышения оперативности и досто- верности контроля, оно дополнительно содержит блок контроля, а блок управления содержит счетчик команд, элемент коммутатор, сумматор по модулю два, триггер и узел управления, содержащий дешиф- ратор, триггер, элемент И-ИЛИ, три элемента И, элемент ИЛИ-НЕ, элемент НЕ, два элемента ИЛИ и два одновибратора, причем с первого по шестой управляющие входы блока управления являются соответ- ственно с первого по шестой управляющими входами устройства для подключения соответственно к первому, второму и третьему выходам статуса магистрального цикла, выходу чтения и первому и второму выходам статуса очереди команд шины управления контролируемой микропроцессорной системы, вход сброса блока управления подключен к входу сброса устройства, с первого по девятый выходы блока управления соедине- ны соответственно с первого по седьмой управляющими входами запоминающего блока последовательности команд и первым и вторым управляющими входами блока контроля, третий управляющий вход которого и восьмой управляющий вход запоминающего блока последовательности команд соединены с десятым выходом блока управления, первая и вторая группы выходовзапоминающегоблокапоследовательности команд соединены, соответственно, с первой и второй группами информационных входов блока контроля, выход которого является выходом сигнала ошибки устройства, причем в блоке управ- ления первый вход первого элемента И и первый и второй входы элемента ИЛИ-НЕ узла управления подключены соответственно к первому, второму и третьему управляющим входам блока управления, выход элемента ИЛИ-НЕ соединен с вторым входом первого элемента И, выход которого соединен с информационным входом триггера узла управления, выход которого соединен с первым входом второго элемента И

и первым входом элемента И-ИЛИ, второй вход которого соединен с синхровходом триггера узла управления, с входами элемента НЕ и первого одновибратора и подключен к синхровходу блока управления, вход сброса которого подключен к первому входу элемента ИЛИ блока управления и к третьему входу элемента И-ИЛИ, выход которого соединен с входом сброса триггера узла управления, вход разрешения записи которого подключен к четвертому управляющему входу блока управления, выход первого одновибратора соединен с вторым входом второго элемента И, выход которого соединен с первым входом первого элемента ИЛИ узла управления, с первым входом управления режимом счетчика команд, входом установки в 1 триггера, блока управления и с первым управляющим входом коммутатора, второй управляющий вход которого является восьмым выходом блока управления и соединен с входом установки в О триггера блока управления, с вторым входом первого элемента ИЛИ узла управления, с вторым входом управления режимом счетчика команд и с выходом третьего элемента И, первый и второй входы которого соединены с выходами, соответственно, второго одновибратора и второго элемента ИЛИ, первый вход которого соединен с первым выходом дешифратора и подключен к девятому выходу блока управления, пятый и шестой управляющие входы которого подключены соответственно к первому и второму входам дешифратора, второй и третий выходы которого соединены соответственно с вторым входом элемента ИЛИ блока управления и вторым входом второго элемента ИЛИ узла управления, выход первого элемента ИЛИ узла управления является первым выходом блока управления и подключен к синхровходу счетчика команд, вход сброса которого соединен с выходом элемента ИЛИ узла управления и является десятым выходом блока управления, с первого по четвертый выходы счетчика команд соединены соответственно с первого по четвертый информационными входами коммутатора и с первого по четвертый входами сумматора по модулю два блока управления, выход которого является третьим выходом блока управления, с четвертого по седьмой выходы которого подключены соответственно к выходам коммутатора с первого по четвертый, выход триггера узла управления является вторым выходом блока управления, причем блок контроля содержит узел контроля кодов и триггер, выход которого является выходом блока контроля, первая и вторая группы информационных

входов которого подключены соответственно к первой и второй группам входов узла контроля кодов, синхровход, вход разрешения записи, вход сброса и информационный вход триггера блока контроля подключены соответственно к первому, второму и третьему управляющим входам блока контроля и выходу узла контроля кодов.

входом пятого регистра, выход которого соединен с вторым информационным входом пятого коммутатора и образует первую группу выходов блока, выход пятого коммутатора соединен с информационным входом шестого регистра, выход которого образует вторую группу выходов блока, первый управляющий вход которого подключен к синхровходам первого и второго регистров, второй управляющий вход подключен к первым управляющим входам с первого по четвертый коммутаторов и к управляющему входу пятого коммутатора, третий управляющий вход блока подключен к вторым управляющим входам с первого по четвертый коммутаторов, с четвертого по седьмой управляющие входы блока подключены к синхровходам соответственно с третьего по шестой регистров, восьмой управляющий

вход блока подключен к входам сброса с первого по шестой регистров.

(A/BIS...

фиг. 3

V33...40

V

...

49 Г

фиг. 5

Фиг 4

10

си

3

ЯS5

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля микропроцессорной системы | 1985 |

|

SU1287161A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля микропроцессорной системы | 1985 |

|

SU1392562A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-06-15—Публикация

1990-05-18—Подача