tc

о ел

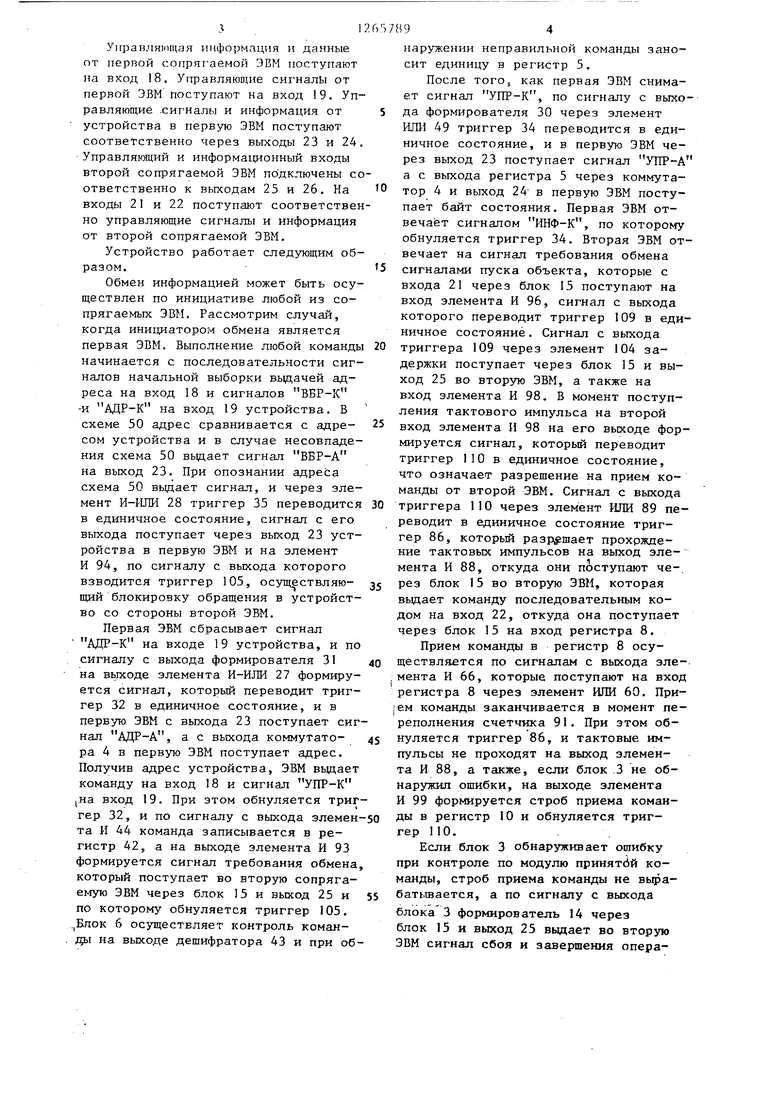

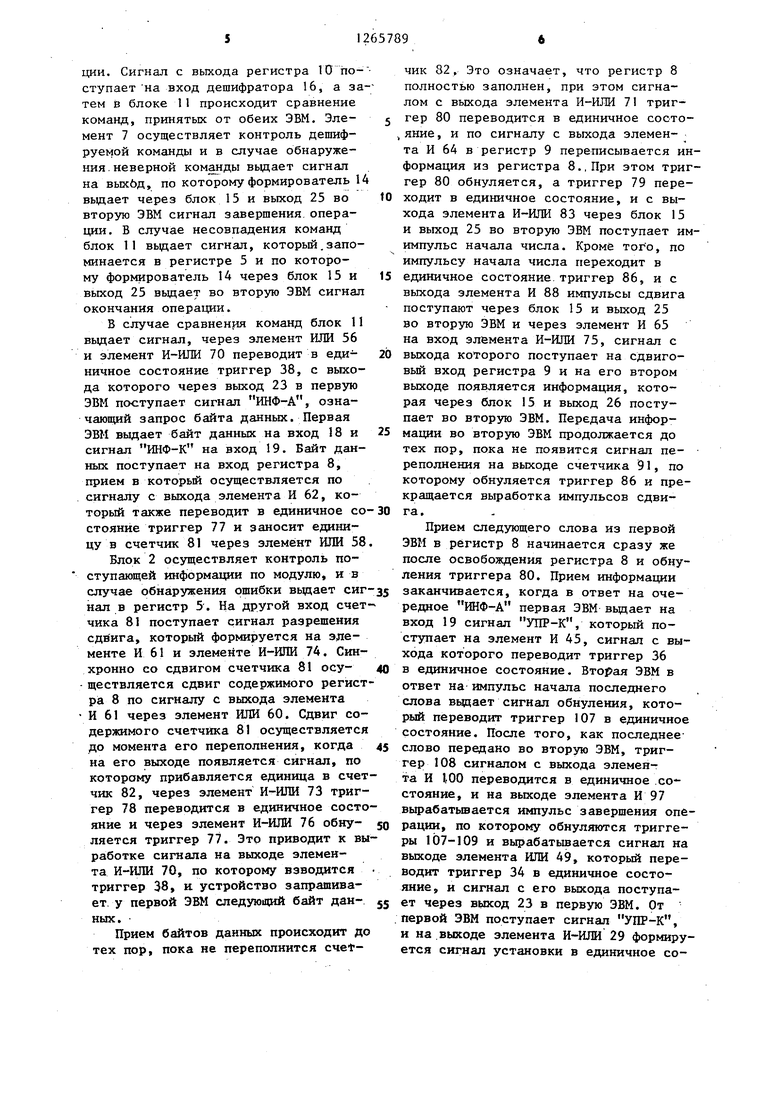

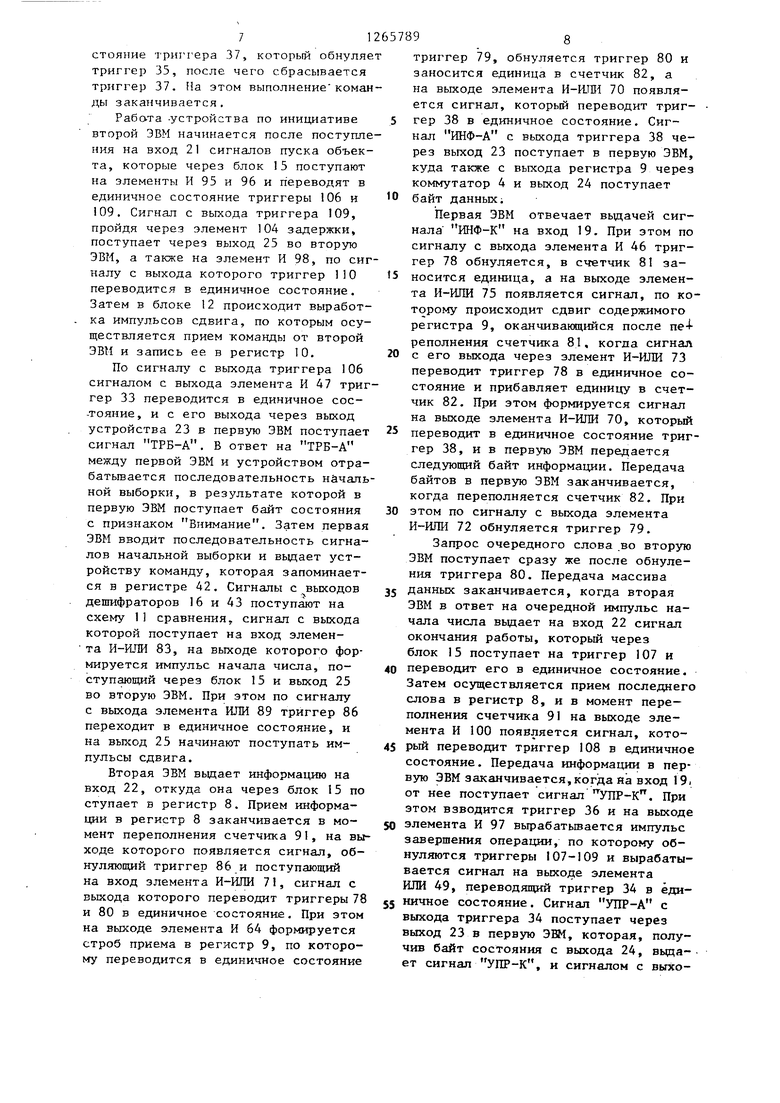

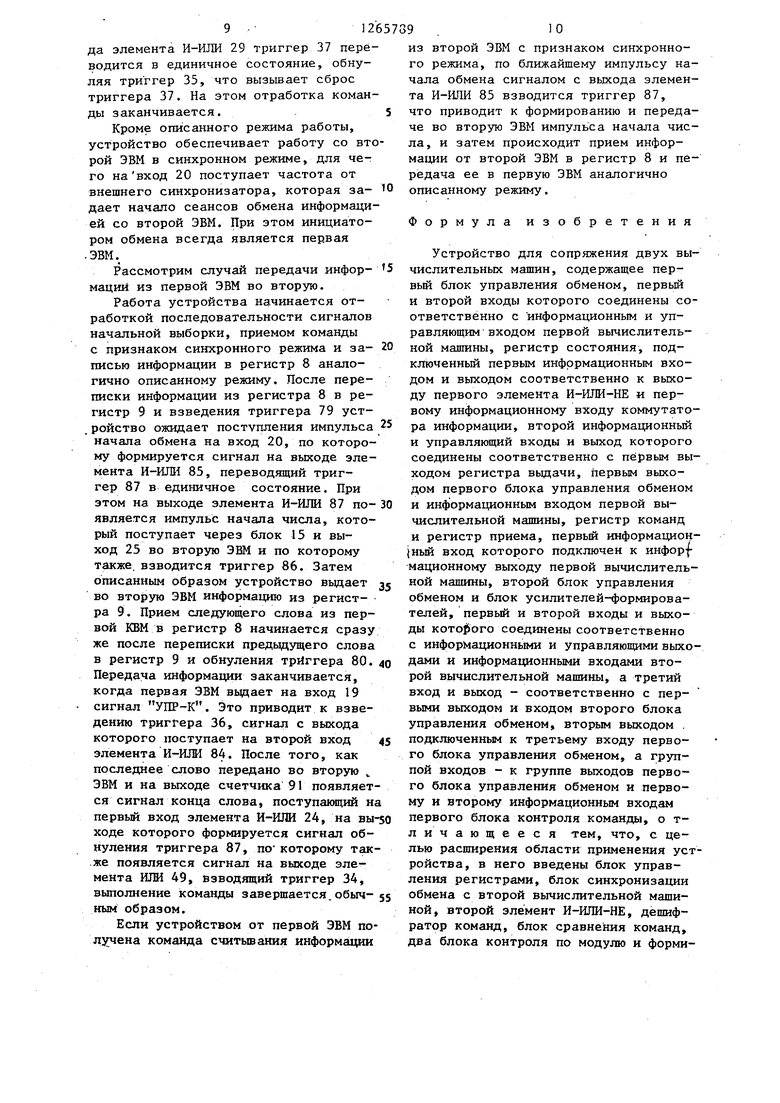

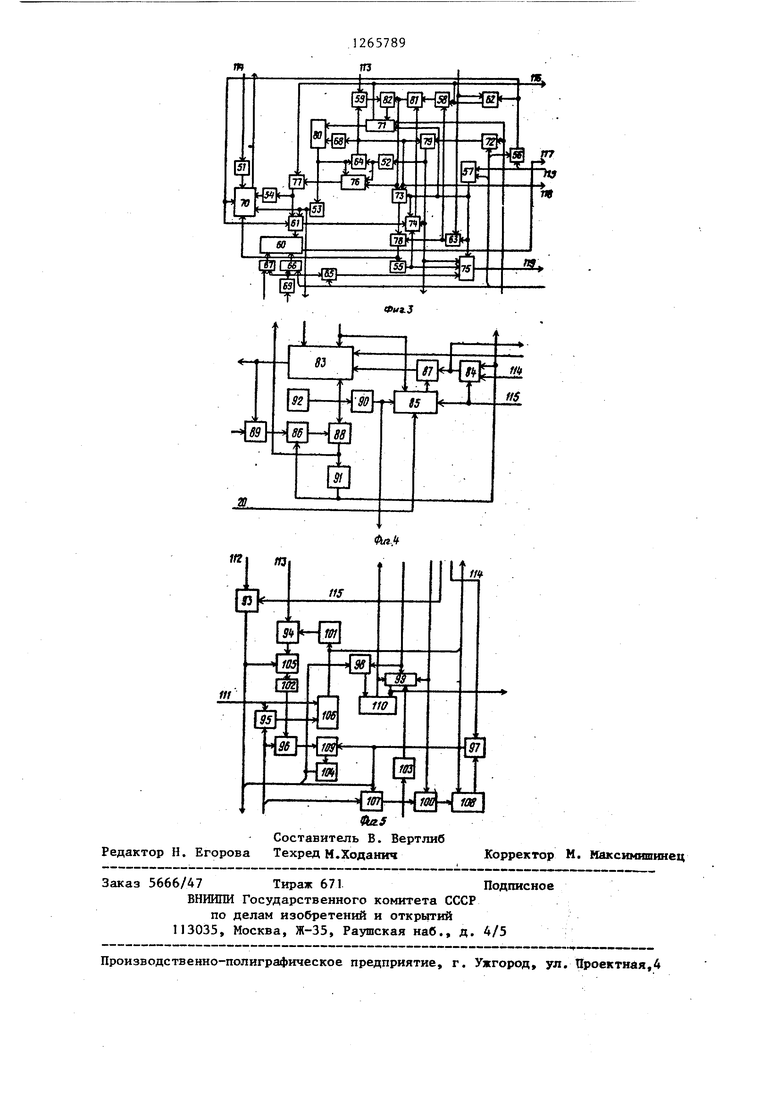

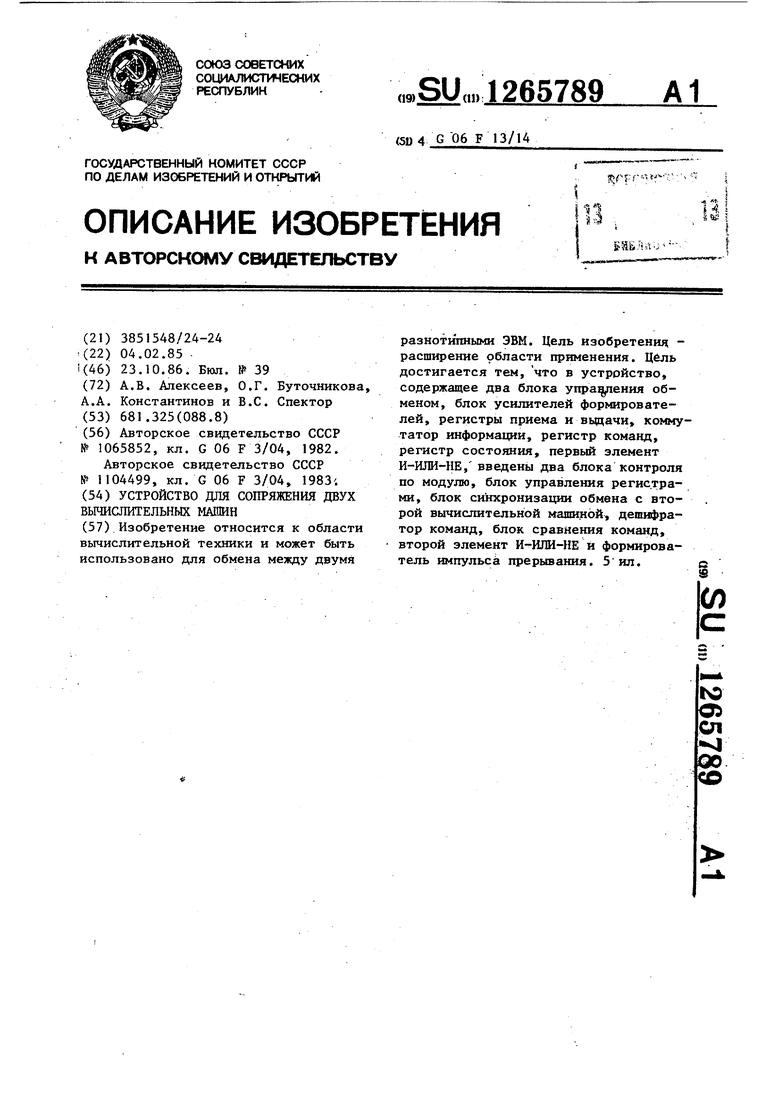

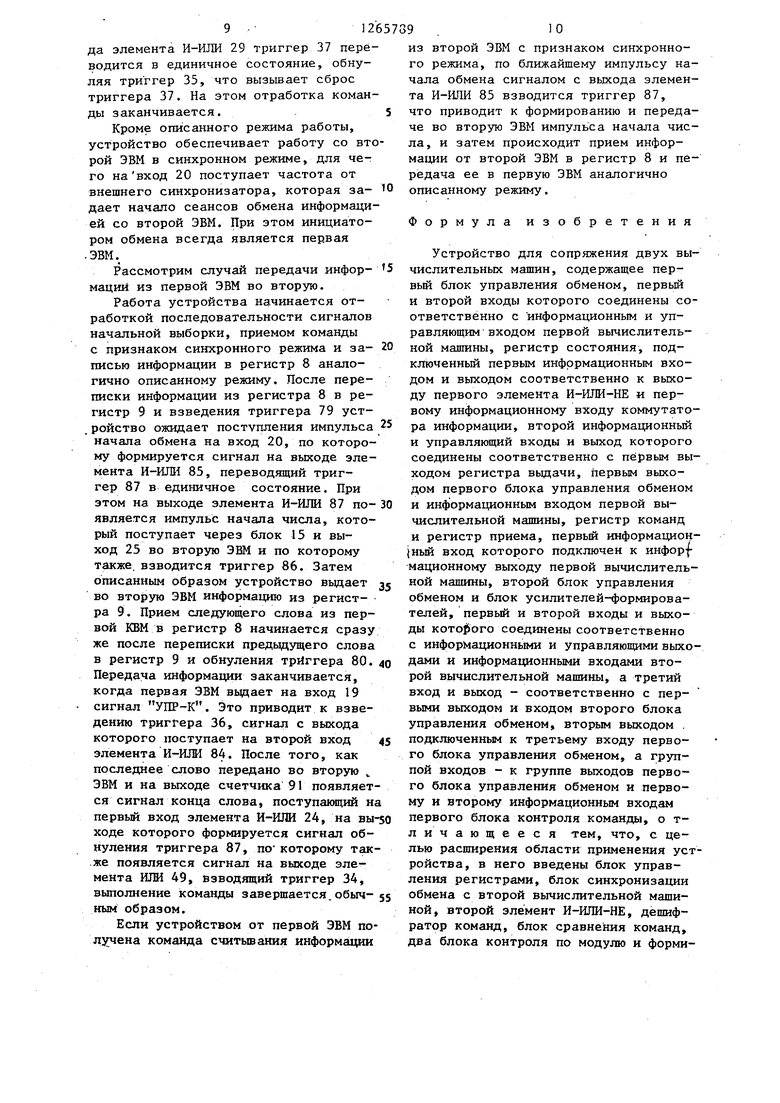

оо со Изобретение относится к области вычислительной техники и может быть использовано для обмена информацией между двумя разнотипными ЭВМ. Целью изобретения является расширение области применения устройства. На фиг. I представлена блок-схема устройства; на фиг. 2-5 - функциональные схемы блока управления обменом, блока управления регистрами, блока синхронизации и блока сопряжения соответственно. Устройство содержит (фиг. 1) первый блок 1 управления обме1яом, вый блок 2 контроля по модулю, второй блок 3 контроля по модулю, коммутатор 4 информации, регистр 5 состояния, первый элемент И-ИЛИ-НЕ 6, второй элемент И-ИЛИ-НЕ 7, регистр 8 приема, регистр 9 выдачи, регистр 10 команд, блок 11 сравнения команд, блок 12 синхронизации, второй блок 13 управления обменом, формирователь 14 импульса прерывания, блок 15 усипителей-формирователей, дешифратор 16 команд, блок 17 управления регистрами, входы 18-22 устройства, выходы 23 26 устройства. Первый блок 1 управления обменом (фиг. 2) содержит элементы И-ИЛИ 2729, формирователи 30 и 3 импульса заднего фронта, триггеры 32-38, фор.мирователь 39 импульса переднего фронта, элемент 40 задержки, элемент НЕ 41, регистр 42 команд, дешифратор 43 команд, элементы И 44-47 элементы ИЛИ 48 и 49, схему 50 сравнения с константой адреса. Блок 17 управления регистрами (фиг. 3) содержит элементы НЕ 51-55, элементы ИЖ 56-60, элементы И 61-67 элементы 68 и 69 задержки, элемен ты И-ИЛИ 70-76, триггеры 77-80,счетчик 81 битов, счетчик 82 байтов. Блок 12 синхронизации обмена со второй вычислительной машиной («фиг. 4) содержит элементы И-ИЛИ 83-85, триггеры 86 и 87, элемент ИЛИ 89, элемент 90 задержки, счетчик 91 импульсов, генератор 92 тактовых импульсйв Второй блок 13 управления обменом (фиг. 5) содержит элементы И 93-100, элементы НЕ 101-103, элемент 104 задержки, триггеры 105-110. В состав устройства входят линии 111-115 группы выходов блока 1 и линии 116, 17 и 118, 119 первого и второго выходов блока 17. Блок 1 предназначен для интерпретации и формирования управляющих сигналов взаимодействия с первой ЭВМ. Блоки 2 и 3 контроля по модулю служат для контроля поступаощих данных от обеих сопрягаемых ЭВМ. Коммутатор 4 информации предназначен для выдачи байтов информации, а также байтов состояния в канал первой сопрягаемой ЭВМ. Регистр 5 состояния служит для хранения байта состояния. Элементы 6 и 7 служат для контроля команд, поступающих от обеих сопрягаемых ЭВМ, и вырабатывают сигналы контроля, если полученная команда не принадлежит системе команд устройства . Регистр 8 приема служит для приема данных и вьщачи их в регистр выдачи. Регистр 9 вьщачи служит для приема данных из регистра приема и их выдачи в одну из сопрягаемь1х ЭВМ. Регистр 10 команд предназначен для хранения и приема команды, поступающей от второй ЭВМ. Блок 11 сравнения команд предназначен для сравнения направлений обмена, запрашиваемых сопрягаемыми ЭВМ. Блок 12 служит для выработки тактовых импульсов для второй ЭВМ и для организации синхронной работы с ней; Блок 13 предназначен для организации взаимодействия со второй сопрягаемой ЭВМ. Формирователь 14 прерывания содержит элемент ИЛИ, соедйненньш выходом со входом выходного -формирователя импульса, и служит для вьщачи во вторую ЭВМ сигналов управления при отклонедаях от нормального выполнения операций обмена. Блок 15 усилителей-формирователей предназначен для электрического согласования информационных и управляющих сигналов, передаваемых на вторую ЭВМ и поступающих от нее в устройство . Дешифратор 16 команд осуществляетдешифрацию команды, поступающей от второй ЭВМ, и сигнал с его выхода определяет режим работы устройства. Блок 17 управления регистрами предназначен для организащи приема данньпс в регистр, приема от передающей ЭВМ и выдачи их с регистра вьщачи в принимающую ЭВМ в соответствии с интерфейсом сопрягаемых ЭВИ.1

У1гракля 01дая информация н данные от первой сопрягаемой ЭВМ поступают на вход 8, Управляюп;не сигналы от первой ЭВМ поступают на вход 19. Управляющие .сигналы и информация от 5 устройства в первую ЭВМ поступают соответственпо через выходы 23 и 24. Управляющий и информационный входы второй сопрягаемой ЭВМ подключены соответственно к выходам 25 и 26. На О входы 2I и 22 поступают соответственно управляющие сигналы и информация от второй сопрягаемой ЭВМ.

Устройство работает следующим образом.5

Обмен информацией может быть осуществлен по инициативе любой из сопрягаемых ЭВМ. Рассмотрим случай, когда инициатором обмена является первая ЭВМ. Выполнение любой команды 20 начинается с последовательности сигналов начальной выборки вьдачей адреса на вход 18 и сигналов ВБР-К и АДР-К на вход 19 устройства. В схеме 50 адрес сравнивается с ядре- 25 сом устройства и в случае несовпадения схема 50 выдает сигнал ВБР-А на вьгход 23. При опознании адреса схема 50 вьщает сигнал, и через элемент И-Р-ШИ 28 триггер 35 переводится 30 в единичное состояние, сигнал с его выхода поступает через выход 23 устройства в первую ЭВМ и на элемент И 94, по сигналу с выхода которого взводится триггер 105, осуществляю- 35 щий блокировку обращения в устройство со стороны второй ЭВМ.

Первая ЭВМ сбрасывает сигнал АДР-К на входе 19 устройства, и по сигналу с выхода формирователя 31 40 на вьтходе элемента И-ИЛИ 27 формируется сигнал, который переводит триггер 32 в единичное состояние, и в первую ЭВМ с выхода 23 поступает сигнал АДР-А, а с выхода коммутато- 45 ра 4 в первую ЭВМ поступает адрес. Получив адрес устройства, ЭВМ вьвдает команду на вход 18 и сигнал УПР-К Ha вход 19. При этом обнуляется триггер 32, и по сигналу с выхода элемен-зо та И 44 команда записывается в регистр 42 5 а на вьпсоде элемента И 93 ормируется сигнал требования обмена, который поступает во вторую сопрягаемую ЭВМ через блок 15 и выход 25 и 55 о которому обнуляется триггер 105. Епок 6 осуществляет контроль команы на выходе дешифратора 43 и при обнаружении неправильной команды заносит единицу в регистр 5.

После того5 как первая ЭВМ снимает сигнал УПР-К, по сигналу с выхода формирователя 30 через элемент ИШ 49 триггер 34 переводится в единичное состояние, и в первую ЭВМ через выход 23 поступает сигнал УПР-А а с выхода регистра 5 через коммутатор 4 и выход 24 в первую ЭВМ поступает байт состояния. Первая ЭВМ отвечает сигналом ИНФ-К, по которому обнуляется триггер 34. Вторая ЭВМ отвечает на сигнал требования обмена сигналами пуска объекта, которые с входа 21 через блок 15 поступают на вход элемента И 96, сигнал с выхода которого переводит триггер 109 в единичное состояние. Сигнал с выхода триггера 109 через элемент 104 задержки поступает через блок 15 и выход 25 во вторую ЭВМ, а также на вход элемента И 98. В момент поступления тактового импульса на второй вход элемента Н 98 на его выходе формируется сигнал, который переводит триггер 110 в единичное состояние, что означает разрешение на прием команды от второй ЭВМ. Сигнал с выхода триггера 110 через элемент ИЛИ 89 переводит в единичное состояние триггер 86, который разрешает прохождение тактовых импульсов на выход элемента И 88, откуда они поступают через блок 15 во вторую ЭВМ, которая вьщает команду последовательным кодом на вход 22, откуда она поступает через блок 15 на вход регистра 8.

Прием команды в регистр 8 осуществляется по сигналам с выхода элемента И 66, которые поступают на вход регистра 8 через элемент ШШ 60. При1ем команды заканчивается в момент переполнения счетчика 91. При этом обнуляется триггер 86, и тактовые импульсы не проходят на выход элемента И 88, а также, если блок 3 не обнаружил ошибки, на выходе элемента И 99 формируется строб приема команды в регистр 10 и обнуляется триггер ПО.

Если блок 3 обнаруживает ошибку при контроле по модулю принятий команды, строб приема команды не вырабат1,шается, а по сигналу с выхода

блока 3 формирователь 14 через блок 13 и выход 25 выдает во вторую ЭВМ сигнал сбоя и завершения операции. Сигнал с выхода регистра 10 по-ступает на вход дешифратора 16, а затем в блоке 11 происходит сравнение команд, принятых от обеих ЭВМ. Элемент 7 осуществляет контроль дешифруемой команды и в случае обнаружения, неверной команды вьщает сигнал на выхбд, по которому формирователь 14 вьщает через блок 15 и выход 25 во вторую ЭВМ сигнал завершения, операции. В случае несовпадения команд блок 11 вьщает сигнал, который.запоминается в регистре 5 и по которому формирователь 14 через блок 15 и выход 25 вьщает во вторую ЭВМ сигнал окончания операции.

В случае сравнения команд блок 11 вьщает сигнал, через элемент ИЛИ 56 и элемент И-ИЛИ 70 переводит в единичное состояние триггер 38, с выхода которого через выход 23 в первую ЭВМ поступает сигнал ИНФ-А, означающий запрос байта данных. Первая ЭВМ выдает байт данных на вход 18 и сигнал ИНФ-К на вход 19. Байт данных поступает на вход регистра 8, прием в которьй осуществляется по сигналу с выхода элемента И 62, который также переводит в единичное состояние триггер 77 и заносит единицу в счетчик 81 через элемент ИЛИ 58.

Блок 2 осуществляет контроль поступающей информации по модулю, и в случае обнаружения ощибки вьщает сигнал в регистр 5. На другой вход счетчика 81 поступает сигнал разрещения сдвига, который формируется на элементе И 61 и элементе И-ИЛИ 74. Синхронно со сдвигом счетчика 81 осу-ществляется сдвиг содержимого регистра 8 по сигналу с выхода элемента

И 61 через элемент ИЛИ 60. Сдвиг содержимого счетчика 81 осуществляется до момента его переполнения, когда на его выходе появляется сигнал, по которому прибавляется единица в счетчик 82, через элемент И-ИЛИ 73 триггер 78 переводится в единичное состояние и через элемент И-ИЛИ 76 обнуляется триггер 77. Это приводит к выработке сигнала на выходе элемента И-ШШ 70, по которому взводится Т1 1ггер 38, и устройство запрашивает, у первой ЭВМ следующий байт данных.

Прием байтов данных происходит до тех пор, пока не переполнится 82, Это означает, что регистр 8 полностью заполнен, при этом сигналом с выхода элемента И-ИЛИ 71 триггер 80 переводится в единичное состояние, и по сигналу с выхода элемен- та И 64 в регистр 9 переписывается информация из регистра 8., При этом триггер 80 обнуляется, а триггер 79 переходит в единичное состояние, и с выхода элемента И-ИЛИ 83 через блок 15 и выход 25 во вторую ЭВМ поступает имимпульс начала числа. Кроме того, по импульсу начала числа переходит в

единичное состояние триггер 86, и с

вьпсода элемента И 88 импульсы сдвига поступают через блок 15 и выход 25 во вторую ЭВМ и через элемент И 65 на вход элемента И-ИЛИ 75, сигнал с

выхода которого поступает на сдвиговый вход регистра 9 и на его втором выходе появляется информация, которая через блок 15 и выход 26 поступает во вторую ЭВМ. Передача информации во вторую ЭВМ продолжается до тех пор, пока не появится сигнал пе- реполнения на вькоде счетчика 91, по которому обнуляется триггер 86 и прекращается выработка импульсов сдвига. Прием следующего слова из первой ЭВМ в регистр 8 начинается сразу же после освобождения регистра 8 и обнуления триггера 80. Прием информации

заканчивается, когда в ответ на очередное ИНФ-А первая ЭВМ вьщает на вход 19 сигнал УПР-К, который поступает на элемент И 45, сигнал с выхода которого переводит триггер 36

в единичное состояние. Вторая ЭВМ в ответ на импульс начала последнего слова ввдает сигнал обнуления, который переводит триггер 107 в единичное состояние. После того, как последнее

слово передано во вторую ЭВМ, триггер 108 сигналом с выхода элемента И 100 переводится в единичное состояние, и на выходе элемента И 97 вырабатывается импульс завершения операции, по которому обнуляются триггеры 107-109 и вырабатывается сигнал на выходе элемента ИЛИ 49, который переводит триггер 34 в единичное состояние, и сигнал с его выхода поступает через выход 23 в первую ЭВМ. От первой ЭВМ поступает сигнал УПР-К, и на выходе элемента И-ИЛИ 29 формируется сигнал установки в единичное состояние триггера 37, который обнуляет триггер 35, после чего сбрасывается триггер 37. На этом выполнениекоманды заканчивается ,

Рабата -устройства по инициативе второй ЭВМ начинается после поступления на вход 21 сигналов пуска объекта, которые через блок 15 поступают на элементы И 95 и 96 и переводят в единичное состояние триггеры 106 и 109. Сигнал с выхода триггера 109, пройдя через элемент 104 задержки, поступает через выход 25 во вторую ЭВМ, а также на элемент И 98, по сигналу с выхода которого триггер 110 переводится в единичное состояние. Затем в блоке 12 происходит выработка импульсов сдвига, по которым осуществляется прием тсоманды от второй ЭВМ и запись ее в регистр 10.

По сигналу с выхода триггера 106 сигналом с выхода элемента И 47 триггер 33 переводится в единичное состояние, и с его выхода через выход устройства 23 в первую ЭВМ поступает сигнал ТРВ-А. В ответ на ТРБ-А между первой ЭВМ и устройством отрабатьгоается последовательность начальной выборки, в результате которой в первую ЭВМ поступает байт состояния с признаком Внимание. Затем первая ЭВМ вводит последовательность сигнаов начальной выборки и вьщает устройству команду, которая запоминается в регистре 42. Сигналы с выходов епгафраторов 16 и 43 поступают на схему 11 сравнения, сигнал с выхода которой поступает на вход элемента И-ИЛИ 83, на выходе которого формируется импульс начала числа, поступающий через блок 15 и выход 25 во вторую ЭВМ. При этом по сигналу с выхода элемента ИЛИ 89 триггер 86 переходит в единичное состояние, и на выход 25 начинают поступать импульсы сдвига.

Вторая ЭВМ вьщает информацию на вход 22, откуда она через блок 15 по ступает в регистр 8. Прием информации в регистр 8 заканчивается в момент переполнения счетчика 91, на выходе которого появляется сигнал, обнуляюпщй триггер 86 и поступающий на вход элемента И-ИЛИ 71, сигнал с выхода которого переводит триггеры 78 80 в единичное состояние. При этом на выходе элемента И 64 формируется строб приема в регистр 9, по которому переводится в единичное состояние

триггер 79, обнуляется триггер 80 и заносится единица в счетчик 82, а на выходе элемента H-RHJi 70 появляется сигнал, который переводит триггер 38 в единичное состояние. Сигнал ИНФ-А с выхода триггера 38 через выход 23 поступает в первую ЭВМ, куда также с выхода регистра 9 через коммутатор 4 и выход 24 поступает байт данных;

Первая ЭВМ отвечает вьщачей сигнала ИНФ-К на вход 19. При этом по сигналу с выхода элемента И 46 триггер 78 обнуляется, в счетчик 81 заносится единица, а на выходе элемента И-ИЛИ 75 появляется сигнал, по которому происходит сдвиг содержимого регистра 9, оканчивающийся после пе4реполнения счетчика 81, когда сигнал с его выхода через элемент И-ИЛИ 73 переводит триггер 78 в единичное состояние и прибавляет единицу в счетчик 82. При этом формируется сигнал на выходе элемента И-ИЛИ 70, которьй переводит в единичное состояние триггер 38, и в первую ЭВМ передается следующий байт информации. Передача байтов в первую ЭВМ заканчивается, когда переполняется счетчик 82. При этом по сигналу с выхода элемента И-ИЛИ 72 обнуляется триггер 79.

Запрос очередного слова .во вторую ЭВМ поступает сразу же после обнуления триггера 80. Передача массива

ЭВМ в ответ на очередной импульс начала числа вьщает на вход 22 сигнал окончания работы, который через блок 15 поступает на триггер 107 и

переводит его в единичное состояние. Затем осуществляется прием последнего слова в регистр 8, и в момент переполнения счетчика 91 на выходе элемента И 100 появляется сигнал, котоРый переводит триггер 108 в единичное состояние. Передача информации в первую ЭВМ заканчивается,когда йа вход 19от нее поступает сигнал УПР-К. При этом взводится триггер 36 и на выходе

элемента И 97 вьфабатьшается импульс завершения операции, по которому обнуляются триггеры 107-109 и вырабатывается сигнал на выходе элемента ЛИ 49, переводящий триггер 34 в ёдиничное состояние. Сигнал УПР-А с выхода триггера 34 поступает через выход 23 в первую ЭВМ, которая, получив байт состояния с выхода 24, вьща- ет сигнал УПР-К, и сигналом с выхода элемента И-ШШ 29 триггер 37 переводится в единичное состояние, обнуляя триггер 35, что вызывает сброс триггера 37. На этом отработка команды заканчивается.

Кроме описанного режима работы, устройство обеспечивает работу со второй ЭВМ в синхронном режиме, для чего навход 20 поступает частота от внешнего синхронизатора, которая задает начало сеансов обмена информацией со второй ЭВМ. При этом инициатором обмена всегда является первая .ЭВМ.

Рассмотрим случай передачи информации из первой ЭВМ во вторую.

Работа устройства начинается отработкой последовательности сигналов начальной выборки, приемом команды с признаком синхронного режима и записью информации в регистр 8 аналогично описанному режиму. После переписки информации из регистра 8 в регистр 9 и взведения триггера 79 устройство ожидает поступления импульса начала обмена на вход 20, по которому формируется сигнал на выходе элемента И-ИЛИ 85, переводящий триггер 87 в единичное состояние. При этом на выходе элемента И-ИЛИ 87 появляется импульс начала числа, который поступает череэ блок 15 и выход 25 во вторую ЭВМ и по которому также, взводится триггер 86. Затем описанным образом устройство вьщает во вторую ЭВМ информацию из регистра 9. Прием следующего слова из первой КВН в регистр 8 начинается сразу же после переписки предьздущего слова в регистр 9 и обнуления триггера 80. Передача информации заканчивается, когда первая ЭВМ ввдает на вход 19 сигнал УПР-К. Это приводит к взведению триггера 36, сигнал с выхода которого поступает на второй вход элемента И-ИЛИ 84. После того, как последнее слово передано во вторую ЭВМ и на выходе счетчика 91 появляется сигнал конца слова, поступающий н первьй вход элемента И-ШЖ 24, на вы ходе которого формируется сигнал обнуления триггера 87, по которому так.же появляется сигнал на выходе элемента ШШ 49, вэводящий триггер 34, выполнение команды завершается, обьгчным образом.

Если устройством от первой ЭВМ подучена команда считывания информации

из второй ЭВМ с признаком синхронного режима, по ближайшему импульсу начала обмена сигналом с вьрсода элемента И-Ш1И 85 взводится триггер 87, что приводит к формированию и передаче во вторую ЭВМ импульса начала числа, и затем происходит прием информации от второй ЭВМ в регистр 8 и передача ее в первую ЭВМ аналогично описанному режиму.

Формула изобретения

Устройство для сопряжения двух вычислительных машин, содержащее первый блок управления обменом, первьй и второй входы которого соединены соответственно с информационным и управляющим входом первой вычислительной машины, регистр состояния, подключенный первым информационным входом и выходом соответственно к выходу первого элемента И-ИЛИ-НЕ и первому информационному входу коммутатора информации, второй информационный и управляющий входы и выход которого соединены соответственно с первым выходом регистра вьщачи, первьм выходом первого блока управления обменом и информационным входом первой вычислительной машины, регистр команд и регистр приема, первый информацион|ный вход которого подключен к инфор| мационному выходу первой вычислительной машины, второй блок управления обменом и блок усилителей-формирователей, первый и второй входы и выходы которого соединены соответственно с информационными и управляющими выходами и информационными входами второй вычислительной машины, а третий вход и выход - соответственно с первыми выходом и входом второго блока управления обменом, вторым выходом . подключенным к третьему входу первого блока упра:вления обменом, а группой входов - к группе выходов первого блока управления обменом и первому и второму информационным входам первого блока контроля команды, о тличающееся тем, что, с целью расширения области применения устройства, в него введены блок управления регистрами, блок синхронизации обмена с второй вычислительной машиной, второй элемент И-ИЛИ-НЕ, дешифратор команд, блок сравнения команд, два блока контроля по модулю и формирователь импульса прерьшания, причем информационный вход второго разряда и управляющий вход регистра состояния подключены соответственно через первьй блок контроля по модулю - к информационному выходу и к управляющему выходу первой вычислительной машины, а инфррмационньй вход третьего разряда регистра - к выходу несравнения блока сравнения команд и выходу второго блока контроля по модулю, управляющие входы регистра приема и регистра выдачи соединены соответственно с первым и вторым выходами блока управления регистрами, первьй, второй и третий выход которого подключены соответственно к группе выходов, второму выходу и четвертому входу первого блока управления обменом, пятым входом соединенного с первыми информационными входами второго элемента И-ИЛИ-НЕ, блока сравнения команд и через дешифратор команд - с выходом регистра команд, первьй и второй информационные входы которого подключены соответственно к третьему выходу второго блока управления обменом и первому выходу регистра приемаi вторым выходом соединенного с информаци онным входом регистра вьдачи, а вторым информационным входом - с входом второго блока контроля по модутпо и четвертым выходом блока усилителейформирователей, четвертый и пятый входы которого подключены соответственно к второму выходу регистра вьща чи и выходу формирователя импульса прерывания и второму входу второго блока управления обменом, третий и четвертый входы которого подключены соответственно к первому и второму вькодам блока синхронизации обмена с второй вычислительной машиной, первы вход которого подключен к выходу сра нения блока сравнения команд и треть ему входу блока управления регистрами, а второй и третьи входы и выходы соединены соответственно с четвертыми и пятыми выходами и входами блока управления регистрами, шестым входом подключенного к четвертому выходу второго блока управления обменом и четвертому входу блока синхронизации обмена с второй вычислительной машиной, второй и четвертый выходы которого соединены с шестым входом блока усилителей-формирователей, а группа входов, пятый выход и пятый вход соответственно с группой выходов и третьим входом первого блока управления обменом и тактовым выходом второй вычислительной мапшны, второй информационный вход блока сравнения команд подключен к группе выходов первого блока управления обменом, выход несравнения которого и выходы второго блока контроля по модулю и второго элемента И-ИЛИ-НЕ подключены соответственно к первому , второму и третьему входам запуска формирователя импульса прерьшания, причем первый блок управления обменом содержит схему сравнения с константой адреса. три элемента И-ИЖ, два формирователя импульса заднего фронта, семь триггеров, формирователь импульса переднего фронта, элемент НЕ, четыре элемента И, элемент задержки, регистр команд, дешифратор команд, два элемента ИЛИ, причем первый вход блока соединен с информационными входами схемы сравнения с константой адреса jj регистра команд, вход записи которого соединен через элемент задержки с группой выходов блока и выходом первого элемента И,- первый вход которого соединен с первым выходом блока и выходом первого триггера, установочный вход которого соединен с выходом первого элемента И-ИЛИ, первый вход которого соединен с выходом второго триггера, первьм входом второго элемента И-ИЛИ, первым выходом и группой выходов блока, второй вход которого соединен с входами сброса второго и третьего триггеров, первыми входами второго и третьего элементов И, третьего элемента И-ИЛИ, первого элемента ИЛИ, через первьй и второй формирователи импульса заднего фронта с первым входом второго элемента ИЛИ и рторым входом первого элемента И-ШШ, с управляющим входом схемы сравнения с константой адоеса. вторьм входом втооого элемента И-ИЛИ, входом сброса первого триггера и вторым входом первого элемента И, выходы несравнения и сравнения схемы сравнения с константой адреса соединены соответственно с первым выходом блока и третьим входом второго элемента И-ШШ, выход которого соединен с входом установки четвертого триггера, выход которого сое/Ц1нен с третьим входом элемента И-ШШ, с первым выходом блока, через формироват ;ль импульса переднего фронта с гру пой выходов блока, через элемент НЕ с входлМи сброса пятого и шестого TpHiiepoB и группой выходов блока, выход и установочный вход пятого триг гера соединены соответственно с группой выходов блока и выходом второго элемента И, второй вход которого соедине с первым выходом блока, выходом седьмого триггера и вторым входом третьего элемента И, выход которого соединен с вторым выходом блока четвертый вход которого соединен с .установочным входом седьмого триггера, вход сброса которого соединен с выходом первого элемента ИЛИ, второй вход которого соединен с первым выходом блока, выходом .третьего триггера и вторым входом третьего элемента И-ЙЛИ, выход которого соединен с установочным входом шестого триггера, выход которого соединен с входом сбро са четвертого триггера и третьим входом первого элемента ИЛИ, установочньй вход третьего триггера соединен с выходом второго элемента ИЛИ, выход регистра команд череэ дешифратор команд соединен с группой выходов блока, третий вход которого соединен с вторым входом второго элемента ИЛИ и первым входом четвертого элемента И второй вход и выход которого соединены соответственно с пятым входом блока и установочным входом второго триггера, причем блок управления регистрами содержит пять элементов НЕ, пять элементов ИЛИ, семь элементов И два элемента задержки, семь элементов И-ИЛИ, четыре триггера, счетчик битов, счетчик байтов, причем выход первого элемента И-ИЛИ соединен с тре тьим выходом блока, первый вход ко торого соединен с первыми входами первого и второго элементов ИЛИ и через первый элемент НЕ с первым входом 45 та

первого элемента И-Ш1И, второй вход которого соединен с первыми входами первого и второго элементов И и выходом первого элемента ИЛИ, выход второго элемента И соединен с установочным входом первого триггера, первыми входами второго элемента И-ИЛИ и третьего элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, входом сброса второго триггера и первым входом третьего элемента И-ИЛИ, второй вход которого соединен с четвертым входом блока и

нен с выходом второго триггера и через пятый элемент НЕ с третьими входами пятого и шестого элементов ИИЛИ, четвертый вход которого соединен

с выходом пятого элемента И, первьй вход которого соединен с первыми входами шестого и седьмого элементов И и через второй элемент задержки с пятым входом блока, шестой вход которого соединен с вторым входом седьмого элемента И, выход которого соединен с первым входом пятого элемента И, второй вход которого соединён вторым входом второго элемента И-ИГГИ, третий вход которого соединен с первыми входами четвертого, пятого и шестого элементов И-ИЖ, выходом второго элемента ИЛИ и первым входом третьего элемента И, второй вход которого соединен с вторым входом второго элемента вторым входом блока, первый и второй входы четвертого элемента ИЛИ соединены соответственно с первым входом блока и входом четвертого элемента И-ИЛИ, выходом четвертого элемента И и через первый элемент задержки с входом сброса четвертого триггера, установочный вход которого соединен с выходом второго элемента И-ИЛИ, четвертый вход которого соединен с выходом счетчика байтов, вход сброса которого соединен с выходом четвертого элемента ИЛИ, счетный вход счетчика байтов соединен с третьим входом четвертого элемента И-ИЛИ, первым входом седьмого элемента И-ИЛИ и выходом счетчика битов, счетный и разрешающий входы которого соединены соответственно с выходом третьего элемента И и йыходом пятого элемента И-ИЛИ, второй вход которого соединен с пятым выходом блока, с вторым входом шестого элемента И-ИЛИ, с выходом третьего триггера и через второй элемент НЕ. с вторым входом седьмого элемента И-ИЛИ и первым входом четвертого элемента И, второй вход которого подключен к третьему входу седьмого элемента И-ИЛИ, к выходу четвертого триггера и через третий элемент НЕ к третьему входу первого элемента И-ИЛИ, к четвертому выходу блока и второму входу первого элемента И,третий вход которого соединен с выходом первого триггера и через четвертый элемент НЕ с четвертым входом первого элеменИ-ИЛИ, пятый вход которого соедис выходом шестого элемента И, выходы второго элемента И и пятого элемента ИЛИ образуют первый выход блока, третий вход блока соединен с вторыми входами первого и второго элементов ИЛИ пятого и шестого элементов И и третьим входом третьего элемента И-ИЛИ, выход которого соединен с установйчным входом третьего триггера, выход четвертого элемента И-ИЛИ соединен с установочным входом второго триггера, выход первого элемента И соединен с третьим входом пятого эле мента ИЛИ и четвертым входом пятого элемента И-ИЛИ, выходы четвертого элемента И и шестого элемента И-ИПИ образуют второй выход блока, причем блок синхронизации обмена с второй вычислительной машиной содержит гене ратор тактовых импульсов, три элемен та И-ШШ, два триггера, элемент задержки, элемент И, элемент ШШ, счет чик импульсов, причем выход первого элемента И-ИЛИ соединен с четвертым выходом блока и первым входом элемента ШШ, второй вход и выход которого соединены соответственно с четвертым входом устройства и установоч ным входом первого триггера, выход которого соединен с первым входом элемента И, выход которого соединен с третьим вЬкодом блока и входом сче чика импульсов, выход которого соеди нен с входом сброса первого триггера с вторым выходом блока и пе{1вым входом второго элемента И-ИЛИ, второй и третий входы которого соединены с группой входов блока и первым входом третьего элемента И-ИШ, выход второ го элемента И-ШШ соединен с пятым вьгходом блока и входом сброса второго триггера, установочный вход которого соединен с выходом третьего элемента И-ШШ, второй вход и выход которого соединены соответственно с выходом элемента задержки, первьы выходом блока и пятым входом блока, четвертый вход третьего элемента И-ИПИ соединен с третьим входом блока и пер вым входом первого элемента И-ШШ, второй, третий и четвертый входы которого соединены соответственно с вто рым и первьм входами блока и выходом второго триггера, выход генератора

тактовых импульсов подключен к пято- 55 им выходом блока. му входу первого элемента И-ИЛИ, второму входу элемента И и входу элемента задержки, причем второй блок управления обменом содержит восемь элементов И, три элемента НЕ, шесть триггеров, элемент задержки, причем выход первого элемента И соединен с первым вьгходом блока и входом сброса первого триггера, установочный вход которого соединен с выходом второго элемента И, первый вход которого подключен через первый элемент НЕ к второму выходу блока и выходу второго триггера, установочный вход которого соединен с выходом третьего элемента И, первый вход которого соединен с входом сброса второго триггера, а второй вход -. с первым входом блока, первым входом четвертого элемента И и установочным входом третьего триггера, вход сброса которого соединен с вторым и первым выходами блока, выходом пятого элемента И, входами сброса четвертого и пятого триггеров, установочный вход которого соединен с выходом четвертого элемента И, второй вход которого через второй элемент НЕ соединен с выходом первого триггера, выход пятого триг-. гера через элемент задержки соеди нен с первьм выходом блока и первым входом шестого элемента И, выход которого соединен с установочным входом шестого триггера, выход которого соединен с четвертым выходом блока и первьм входом седьмого элемента И, второй вход которого соединен с вторым входом шестого элемента И и третьим входом блока, третий вход седьмого элемента И соединен четвертьм входом блока и перйым входом восьмого элемента И, второй вход и выход которого соединены соответственно с выходом третьего -триггера и установочным входом четвертого триггера, выход которого соедииен с первьм входом йятого элемента И, первые входы первого и третьего элементов И и вторые входы первого и пятого злементон И образуют группу входов блока, четвертый вход седьмого элемента И соединен через третий элемент НЕ с вторым входом блока, а выход - с входом сброса шестого триггера и третьда 19

UTT 525 г гг

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источников информации с вычислительной машиной | 1984 |

|

SU1179358A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1439609A1 |

| Устройство для сопряжения двух вычислительных машин | 1979 |

|

SU885988A1 |

| Устройство для измерения параметров многополюсников | 1986 |

|

SU1478147A1 |

| Устройство для обмена информацией | 1979 |

|

SU826328A1 |

| Устройство для сопряжения двух вычислительных машин | 1983 |

|

SU1179312A1 |

| Устройство для обмена информацией | 1983 |

|

SU1142824A1 |

| Устройство для сопряжения вычислительной машины с внешними абонентами | 1984 |

|

SU1265784A1 |

| Устройство для сопряжения двух цифровых вычислительных машин | 1979 |

|

SU868741A1 |

| Устройство для сопряжения вычислительных машин | 1987 |

|

SU1425697A1 |

Изобретение относится к области вычислительной техники и может быть использовано для обмена между двумя разнотипными ЭВМ. Цель изобретения расширение рбласти применения. Цель достигается тем, что в устройство, содержащее два блока обменом, блок усилителей формирователей, регистры приема и вьщачи, коммутатор информации, регистр команд, регистр состояния, первый элемент И-ИЛИ-НЕ, введены два блока контроля по модулю, блок управления регистрами, блок синхронизации обмена с второй вычислительной машиной, дешифратор команд, блок сравнения команд, второй элемент И-ШШ-НЕ и формирователь импульса прерывания. 5ил.

| Устройство для сопряжения вычислительных машин | 1982 |

|

SU1065852A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство сопряжения для вычислительных комплексов | 1983 |

|

SU1104499A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-23—Публикация

1985-02-04—Подача