(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

ДВУХ ЦИФРОВЫХ ВЫЧИС.т1ТЕЛЬНЫХ МАШИН

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| Устройство для сопряжения интерфейсов ЭВМ и внешней памяти | 1984 |

|

SU1262509A1 |

| Устройство для обмена информацией | 1985 |

|

SU1339572A1 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Устройство для обмена информацией | 1985 |

|

SU1310828A1 |

| Устройство сопряжения для вычислительных комплексов | 1983 |

|

SU1104499A1 |

| Устройство для сопряжения вычислительных машин | 1982 |

|

SU1065852A1 |

| Устройство для обмена информацией | 1982 |

|

SU1068925A1 |

| Устройство для сопряжения ЭВМ с синхронными каналами передачи данных | 1986 |

|

SU1347083A1 |

| Устройство для сопряжения вычислительных машин | 1987 |

|

SU1425697A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в системах реального времени для организации обмена информации между двумя цифровыми вычислительными машинами (ЦВМ).

Известны устройства ,Й(1Я сопряжения, двух ЦВМ, содержаише блоки электрического согласования первой и второй ЦВМ, блоки входных и выхода1ых элементов И, блок синхронизации, блок управления, блок регистров, блок формирования команд и блок хранения команд 1 .

Недостаток этих устройств состоит в ограниченной области их применения.

Наиболее близким к предлагаемому по технической сущности является устройство для остряжения двух вычислительных машин, содержащее узлы согласования выходных и входта. сягналсш информации и упраале1шя, соединенных с каналом первой ЦВМ, узел сравнения адресов, соеданенный входом с выходом регистра адреса, буферный регистр, подключенный входом, через входной коммутатор к выходу второй ЦВМ, а выходом - ко входу выходного коммутатора, узел контроля по чет

кости, регистр управления, соединенный выходами и входами с соответствующими выходами и входами второй ЦВМ и канала первой 1ЩМ и входами и выходами узлов согласования входных и выходных сигналов управления (2.

Недостаток известного устройства состоит в ограниченной области его применения.

Цель изобретения - расширешге области применения.

10

Поставленная цель достигается тем, что в устройство, содержащее регистр управляющего слова, выходом соединенный с первым входом первой цифровой вычислительной мапганы, первый выход которой подключен к первому

5 входу блока сравнения адресов, соединенного вторым входом с выходом регистра адреса, и к первому входу блока контроля по модулю, первый выход которого соединен с пертым входом триггера контроля, выхидом соединенного

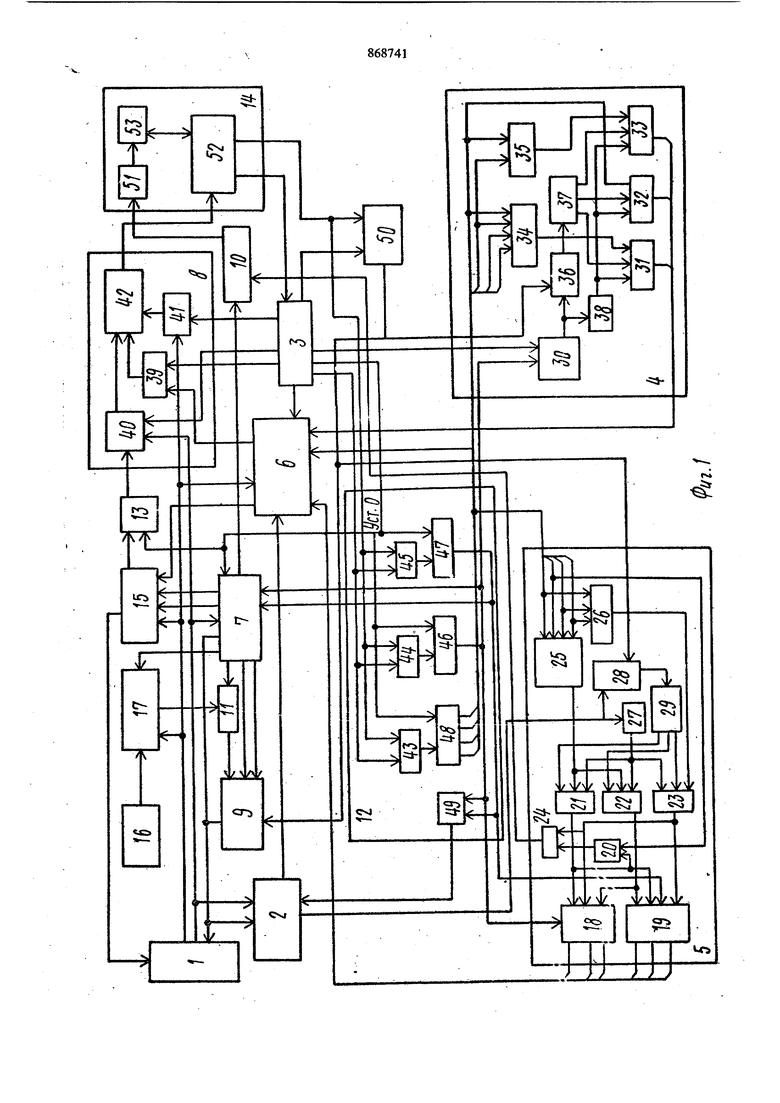

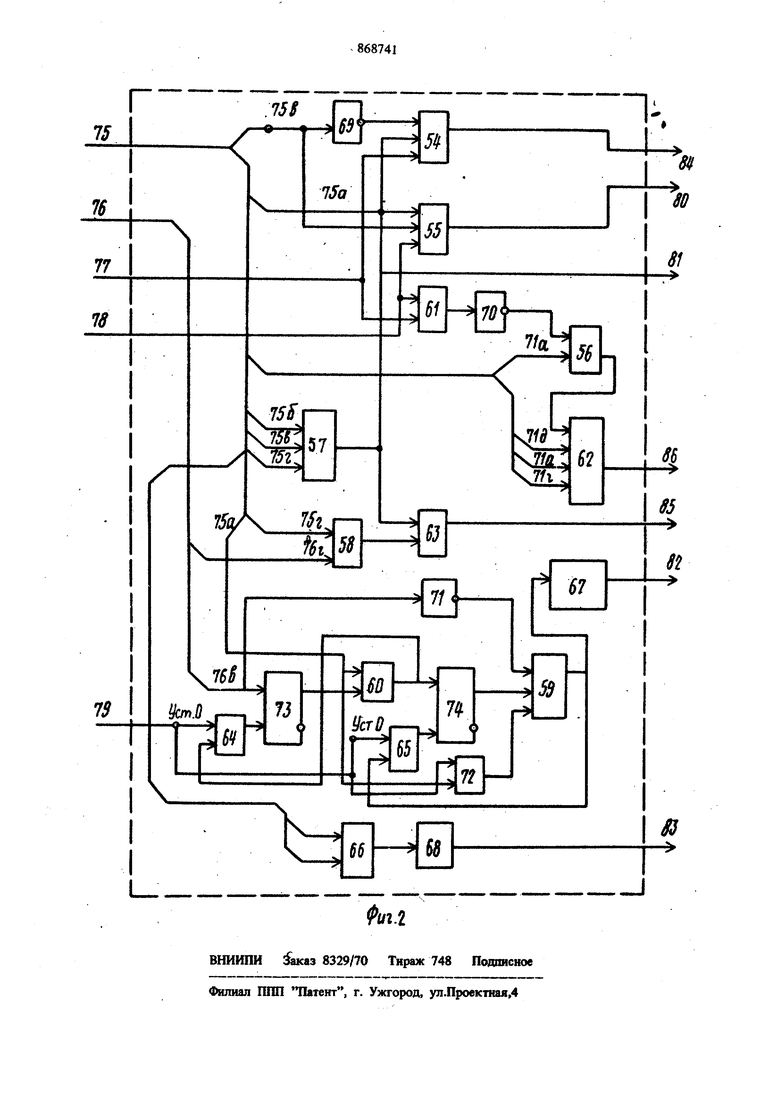

20 с первым входом коммутатора, второй вход которого подключен к первому выходу буферного регистра обмена, а выход - к первому входу второй цифровой вычислительной маиш3ны, и блок формирования сигнала прерьгоания, выход которого подключен ко второму входу второй цифровой вычислительной машины, введены блок анализа состояния, два блока формирования тактовых импульсов, группу элементов И, блок формирования сигналов штравления обмена, блоки управления чтением и записью 5 и элемент ИЛИ, причем первый вход и второй выход буферного регистра обмена подключены соответственно к первому и второму входам блока контроля по модулю, первый и второй входь блока анализа состояния соединены соответственно с первым и вторым входами первого блока формирования тактовых импульсов, вторым выходом и первым входом первой цифровой вычислительной машины, второй вход которой соединен со вторым выходом блока контроля по модулю, третий и четвертый входы которого подключены соответственно к первому и второму выходам блока анализа состояния, третий выход которого соединен с третьим входом блока сравнения адресов, четвертый и пятый - соответственно с первым и вторым входами регистра управляющего слова, а шестой и седьмой выходы - соответственно с первыми входами элемента ИЛИ и блока фор мирования сигнала прерывания, вторым входом подключенного к выходу блока управления чтением, третий вход коммутатора соединен с первым входом блока анализа состояния, третий вход регистра управляющего слова подключен к выходу элемента ИЛИ, вторым входом соединенного с выходом блока сравнения адресов, группа входов регистра управляющего слова подклююна к выходам элементов И группы и первым группам входов блоков управления чтением и записью, вторая группа входов которого соединена с первой группой входов регист ра обмена, второй группой входов блока управ ления чтением и группой вь1ходов блока формирования сигналов направления обмена, первый второй и третий выходы второго блока формирования тактовых импульсов подклн чены соответственно к четвертому, пятому и шестому входам коммутатора, четвертый и пятый выходы - соответственно к первому и второму вхо дам блок формирования сигналов направления обмена, третий вход которого соединен со вторым входом буферного, регистра обмена, первыми входами элементов И группы и первым выходом второй цифровой вычислительной машины, второй выход которой подключен ко входу второго блока формирования тактовых импульсов, шестым выходом подключенного к пер вому входу блока управления записью,; седьМЬ1М выходом - ко вторым входам элементов И группы, а пятым выходом - ко йорому вхс ду триггера контроля, первый и второй выходы блока формирования сигналов направления обмена соединены соответственно с третьим и четвертым входами блока анализа состояния и первым и вторым входами блока управления чтением, а третий выход - с третьим входом первого блока формирования тактовых импульсов, первый выход котррого подключен к третьему входу буферного регистра обмена, а второй выход - к третьему входу блока управления чтением, группа выходов которого соединена со второй группой входов буферного регистра обмена, четвертым входом соединенного с пятым входом блока анализа состояния и восьмым выходом второго блока формирования тактовых импульсов, а третьей группой входов - с группой .выходов блока управления записью, второй вход которого подключен ко второму выходу блока формирования сигналов направления обмена, седьмой вход коммутатора соединен с первым входом буферного регистра обмена. При этом блок управления чтением содержит два шифратора, выходы которых являются группой выходов блока, первые входы соединены с первым входом первого и выходом второго элементов И, вторые входы - с выходом третьего элемента И, третьи входы - соответственно со вторым и первым входами , блока, а четвертые - входы - с выходом четвертого элемента И и первым входом первого элемента ИЛИ, второй вход и выход которого соеданены соответственно с выходом первого элемента И и выходом блока, первые входы второго, третьего и четвертого элементов И подключены через элемент задержки к третьему входу блока, вторые выходы - к соответствующим выходам дешифратора, соединенного входом с выходом счетчика, вход и группа входов которого соедашены .1 соответственио с третьим входом и первой группой входов блока, третьи входы второго и третьего элементов И подключены к выходу второго элемента ИЛИ, первый, второй, третий и четвертый входы которого подключены ко второй группе входов рлока, третий вход четвертого элемента И соединен с выходом третьего элемента ИЛИ, входы которого подключены соответственно к первому, третьему и четвертому входам второго элемента ИЛИ. Кроме того, блок управления записью содержит счетчик, группой входов и выходов сО единенный соответственно с первой группой входов блока и входом дешифратора, а вхо дом - с выходом первого элемент;а И и через элемент задержки с первыми входами второго, третьего и четвертого элементов И, вторые входы которых подключены соответственно к выходам дешифратора, а третьи входы соответственно к выхо и первому входу первого элемента ИЛИ и выходу второго элемента ИЛИ, входас nejffloro элемента И являются соответственно первым и вторым входами блока, входы первого элемента ИЛИ подключены к бсютветствуюшим входам второй группы входов блока, входы второго элемента ИЛ соединены соответственно с первым н вторым входами neinoro элемента ИЛИ, выходы второ го, третьего н четвертого элементов И являются группой выходов блока. Причем блок формирования шгналов направ ления обмена содержит группу элементов И, входы которых подключены соответственно к первому и третьему входам блока, а выходы к информационным входам регистра формата, выходы которого являются группой выходов блока, а вход сброса подключен ко второму входу блока и входам сброса первого и второ го триггеров направления обмена, информацион ными входами соединенных соответственно с выходами первого и второго элементов И, а выходами - соответственно с первым и troрым входами элемента ИЛИ и вторым и первым выходами блока, первые входы первого и второго элементов И соединены с первым входом блока, а вторые входы - с третьим входом блока. Кроме того, блок анализа состояния содержит четыре элемента НЕ, семь элементов И, шесть элементов ИЛИ, два элемента задержки и два триггера, причем первый вход первого элемента И соединен с выходом первого элемента НЕ, второй вход - с первым входом блока, а третий вход - с четвертым входом блока и первым входом первого элемента ИЛИ .входы второго элемента И подключены соответственно к первому и третьему входам блока, второй вход первого элемента ИЛИ соединен с третьим входом блока, а выход - череэ второй элемент НЕ с первым входом третьего элемента И, выход которого соединен с одним входом второго элемента ИЛИ, а второй вход с первым входом блока, входы второго элемента ИЛИ подключены соответственно к первому входу блока, а выход является седьмым выходом блока, входы четвертого элемента И являются первым входом блока, а выход соединен со вторым выходом блока н первым входом третьего элемента ИЛИ, выход которого является шестым выходом блока, а второй вход соединен с выходом пятого элемента И, первый и второй входы которого по 1слючеш 1 соответственно к первому и второму входам блока, выходы первого и второго элементов И соединены соответственно с пятым и первым выходами блока, выход шестого эле мента И через первый элемент задержки соеди нен с третьим выходом блока, первый вход через третий элемент НЕ соединен со вторым входом блока и первым входом первого .триггера, второй вход - с выходом второго триггера, а третий вход через четвертый элемент НЕ соединен с первым входом седьмого элемента И и первым входом блока, первый вход второго тртггера соединен с выходом седьмого элемента И и первым входом четвертого элемента ИЛИ, а второй вход - с выходом пятого элемента ИЛИ, первым входом подключенного к выходу шестого элемента И, а вторым входом - ко второму входу четвертого элемента ИЛИ, входу сброса четвертого элемента НЕ и пятому входу блока, второй вход седьмого элемента И подключен к выходу первого триггера, входы шестого элемента ИЛИ подключены к первому входу блока, а выход череэ второй элемент задержки соединен с четверть1м выходом блока. На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - функциональная схема блока анализа состояния. Устройство (фиг. 1) включает канал 1 первой цифровой вычислительной машины, блоки 2 и 3 формирювания тактовых импульсов, блок 4 управления записью, блок 5 управления чтением, буферный регистр 6 обмена, блок 7 ана-. лиза состояния, коммутатор 8, регистр 9 управляющего слова, блок 10 формирования сигналов прерьшания, элемент ИЛИ 11, блок 12 формирования сигналов направления обмена, триггер 13 контроля, вторую (микро- или мини) ЭВМ 14, блок 15 контроля по модулю, регистр 16 адреса и блок 17 сравнения адресов. Блок 5 управления чтением содержит шифраторы 18 и 19, элементы И 20-23, элементы ИЛИ 24, 25 и 26, элемент 27 задержки, счет шк 28 и дешифратор 29. Блок 4 управления записью содержит элементы И 30-33, элементы ИЛИ 34 и 35, счетчик 36, дешифратор 37и элемент 38 задержки. Коммутатор 8 состоит из трех элементов И 39, 40 и 41 групп и группы элементов ИЛИ 42. Блок 12 формирования сигналов направления обмена включает элементы И 43 группы, два элемента И 44 и 45, два триггера 46 и 47 направления обмена, регистр 48 формата и элемент ИЛИ 49. В составе устройства (фиг. 1) выделены элементы И 50 группы, а в составе ЦВМ 14 - блок 51 прерьтаний, канал 52 и процессор 53. Блок 7 анализа состояшчя (фиг. 2) содержит элементы И 54 - 60, элементы ИЛИ 61-66, элементы 67 и 68 задержки, элементы НЕ 6972, триггеры 73 и 74, входы 75-79 и выходы 80-86 блока. . Устройство работает следующим образом. Устройство должно обеспечить связь з мверсальной ЦВМ-1 (например ЕС ЭВМ), находящейся на верхнем уровне сложной иерархической системы управления, и мини- микро) ЭВМ 14, например 24-разрядной мигш-ЭВМ Элект ника К-200, находящейся на нижнем уров,не этой системы зшравления. ЭВМ как верхнего, так и нижнего уровня могут юшциировать обмен.

Мини- (микро) ЭВМ по отношению к универсальной ЭВМ можно рассматривать как активное внешнее устройство, поэтому операции ввод или вывод означают соответствующую передачу информации по отношению к универсальной ЭВМ.

При описании работы устройства используется стандартная терминология обозначения сигналов, принятых в системе ЕС ЭВМ и изложенных в ОСТ 4 ГО 304.000.;

ЕС ЭВМ как инициатор обмена начинает вЫ борку устройства и мини-ЭВМ 14. Сигналы начальной выборки интерфейса ввода-вьшода (, ВБР-К, АДР-К) поступают с выхода канала 1 (выходная управляющая шина интерфейса ввода-вывода, ШИН УПР-К) ра первый вход блока 7. При этом сигнал с выхода элемента И 57 поступает на второй вход блока 17. В этот же момент с первого выхода канала I (выходная информационная шина интерфейса ввода-вывода ЕС ЭВМ, ШИН-К) на второй вход блока 17 поступает код адреса. Если при этом происходит сравнение адресов, то на выходе блока 17 появляется сигнал, устанавливающий через элемент ИЛИ 11 регистр 9 в состояние, соответствующее подключенному устройству.

Одновременно в блоке 7 входной сигнал ВБР-К (четвертая шина первого входа) посггупает через элемент ИЛИ 62 на первый вход блка 10, который формирует сигнал, прерьшающий работу мини-ЭВМ и информирующий по следнюю и требовании обмена со стороны ЕС ЭВМ. По данному сигналу прерывания мини-ЭВ через канал. 52 выдает информацию адреса, которая поступает на второй вход буферного регистра 6, а также управляющие сигналы, которые поступают Б блок 3. С выхода блока 3 выдается тактовый управляющий сигнал на вход буферного регистра 6, что обеспечивает запоминание в буферном регистре адреса.

После этого мини-ЭВМ через KBHaj 52 выдает на вход блока 3 управляющие сигналы, а на вход группы элементов И 50 - управляющую информацию. По сигналу блока 3 упраВ

ляющая информация проходит в регистр 9 и переводит последний в состояние, соответствующее выдаче в канал 1 сигнала запроса на передачу информации адреса. Блок 2 генерирует управляющий тактовый сигнал на третий вход буферного регистра 6, в результате чего байт служебной информации (в данном случае адрес) передается через блок 15, где формируется контрольный разряд но нечетности на вход канала 1 (входная информационная шина интерфейса ввода-вывода ЕС ЭВМ, ШИН-А).

В ответ на выходной сигнал регистра 9 канал 1 генерирует новое состояние выходных управляющих шин (УПРК-1 на пятой шине первого входа блока 7). Сигнал, который через элемент ИЛИ 62 поступает в блок 10, вызывает прерьшание мини-ЭВМ. По данному сигналу прерывания на первом выходе канала 52 появляются управляющие сигналы, которые поступают на вход блока 3, в результате чего на выходе этого блока появляется разрешающий сигнал на элементы И 41. Код команды обмена, который в этот момент поступает с выхода канала на другие входы элементов И 41, через элементы ИЛИ 42 вьщается на вход канала 52. Далее мини-ЭВМ через канал 52 и элементы И 50 снимает запрос на передачу адреса.

Аналогично передаче адреса мини-ЭВМ осуществляет передачу байта состояния в буфер ный регистр 6, но переводит регистр 9 в состояние, соответствующее запросу на передачу в канал байта состояния. Поступая на вход блока 2, этот сигнал вызьтает на первом выходе генерацию тактирующего сигнала дая передачи байта состояния в канал 1. В ответ на сигнал запроса передачи байта состояния канал 1 изменяет состояние выходных управляющих шин, на одной из которых появляется единичный потенциал (ИНФ-К), свидетельству0 ющий о приеме каналом байта состояния.

Указанный сигнал (ИНФ-К, 71 а) поступает по первой шине первого входа блока 7 на элемент ИЛИ 66 и через элемент задержки 68 проходит на третий вход регистра 9, который:.

5, переходит в состояние снятия запроса на передачу байта состояния (УПРА: 0). При поступлении указанного сигнала из канала 1 на вход блока 2 заканчивается генерация тактирующего (жгнала на первом выходе блока 2. Одновре0 менно состояние выходной управляющей шииы канала 1 (ИНФ-К) поступает на второй вход элемента И 62, на другом входе которого в этот момент имеется разрешаиший сигнал эле,. мента НЕ 70, вход которого соединен с выходом элемента ИЛИ 61, запрещенного по обоим входам, так как триггеры 46 и 47 находятся в исходном нулевом состоянии. Выходной сигнал элемента И 56 через элемент ИЛИ 62 по- / ступает в блок 10, на вь1ходе которого появляется сигнал, прерывающий работу мини-ЭВМ. По сигналу прерывания мини-ЭВМ генерирует на выходах канала управляющие сигналы и управляющую информацию, которая через элементы И 50 поступает на вход регистра 9, в результате чего последний переходит в состояние, соответствующее отключенному устройству от канала 1 (РАБ-А: 0), Сопрягаемые ЦВМ оказьшаются расчлененными и могут осуществлять связь с.другими устройствами системы. 2. Передача данных. Для передачи слова мини-ЭВМ на вы ходах канала 52 генерирует управляющие сигналы и управляющую информацию, которая поступает на вход регистра 9, в результате чего последний переводится в состояние, соответствующее запросу устройства в канала 1 на передачу байтов данных (ТРБА; 1). Указан ный сигнал с выхода регистра 9 открывает по второму входу элемент И 58. В ответ на указанный сигнал канал 1 изменяет состояние выходных управляющих шин, информавдя о котором в виде единичного сигнала поступает на первый вход элемента И 58. В результате на выходе этого элемента появляется сигнал, который через элемент ИЛИ 63 поступает на первый вход элемента ИЛИ 11. Выходной сигнал элемента ИЛИ 11 переводит регистр 9 в состояние, соответствующее устройству, подклю ченному к каналу 1 (РАоА: 1). Одновремен1Ю через элемент ИЛИ 62 на вход блока 10 поступает сигнал, по которому на выходе блока 10 появляется выходной еигнал, информирующий мини-ЭВМ о подключении устройства к каналу 1. По сигналу прерывания мини-ЭВМ, генерируя уп()авляющие сигналы и управляющую информацию, через канал 52 снимает запрос на передачу байтов данных в регистре 9 (ТРБА: передает в буферный регистр 6 код адреса и . устанавливает запрос на передачу адреса в канал 1 (АДРА; 1). В ответ на этот сигнал канал 1 изменяет состояние выходных управляющих щии, информащш о котором через блоки 7 на выхоДе блока 10 генерирует сигна прерьшающий работу мини-ЭВМ. По сигналу прерывания мини-ЭВМ через канал 52 снимает запрос на передачу адреса. Далее мини-ЭВМ генерирует на одном из вы ходов канала 52, соединенном со входом блока 3, управляющие сигналы таким образом, чт на четвертом выхода блока 3 появляется управляющий тактирующий сигнал, который пере письтает управляющую информацию с первого выхода канала 52 в регистр 48 и триггеры 46 и 47. Данная управляющая информация содержит сведення о формате подключенной лошнЭВМ н выполняемой операции обмена. В соот110ветствии с выходными сигналами регистра 48 и триггеров 46 и 47 устройство орга шзует согласование (приведение) форматов сопрягаемых ЭВМ, т.е. адаптация устройства под конкретную мини- (микро-) ЭВМ осуществляется самой же мини- (мнкро-) ЭВМ. Например, при операции ввода и разрядности подключенной мини-ЭВМ, равной 24, после указанной выще операшш триггер 46 находится в единичном состояшш. Кроме того, активен также один (четвертый) из быходов регистра 48, указьшающий на необходимость преобразования 24-разрядного формата в байтовый. С этого момента на выходе элемента ИЛИ 49, соединенного по входам с выходами триггеров 27 и 28, появляется потенциальный сигнал, который поступает на третий вход блока 2, блокируя выдачу сигнала с первого выхода блока 2 и разрешая вьщачу сигнала на. Т11етий вход блока 5. Кроме того, выходной (еди шчный) сигнал триггера 27 блокирует элемент И 56 через элементы ИЛИ 61 и НЕ 70. В результате на время передачи данных запрещается прохождение через элементы И 56 и ИЛИ 62 на вход блока 9, что свидетельствует о получении каналом 1 байта данных (сигнал квитирования, ИНФ-К). Устройство осуществляет передачу байтов данных в блок-мультиплексном режиме, т.е. упаковка и распаковка одного блока, равного длине слова мики- (микро-) ЭВМ, выполняются без вмешательства ЭВМ. Это обеспечивается блоками 4 и 5 управления записью и чтением буферного регистра 6. Процедура состоит в следующем. Мини-ЭВМ по одному из выходов канала 52 генерирует управляющие сигналы, которые сопровождают 24-разрядные слова дан-, ных, выставляемые по другому выходу канала 52, соединенному с одним из входов буферного регистра 6. В результате поступления управляющих сигналов на вход блока 3 на шестом выходе последнего и входе элемента И 30 появляется тактирующий сигнал. На другом входе этого элемента с выхода триггера 4, находящегося в единичном состоянии, имеется разрешающий сигнал. Сигнал с выхода элемента И 30 поступает в качествесчетного импульса иа вход счетчика 36 и на вход элемента 38 задержки. Состояние счетчика 36 дешифруется дешифратором 37, в результате чего.элемент И 33 возбуждается сигналом с выходов дешифратора 37, элемента 38 задержки и элемента ИЛИ 34. В результате на выходе элемента И 33 формируется сигнал, который поступает по третьей группе входов в качестве управляющего сигнала в буферный регистр 6, в результате чего в последний записывается 24-разрядное слово. Далее мини-ЭВМ через канал 52 и элементы И 50 переводит регистр в состошше запроса канала 1 на передачу одного байта информаПИИ (ИнФА : 1). Указанный сигнал поступает в блок 2, в результате чего на втором его входе, соединенном со входами счетчика 28 и элемента 27 задержки, генерируется тактовый сигнал. В ответ на сигнал-запрос передачи байта данных канал I изменяет состояние выходных управляющих шин таким образом, что на одной из них появляется единичный потенциал - сигнал ответа канала на передачу байта данных (ИНФ-К). Информация состояния выХОДН1ЫХ управляющих шин передается в блок 2 и блок 7. По указанному сигналу заканчивается генерация выходного тактового импульса блока 2. Одновременно в блоке 7 зтот же сигнал через первый вход логического элемента ИЛИ 66 поступает на элемент 68 задержки, выходной сигнал которого поступает на третий вход регистра 9, в результате чего в последнем снимается запрос на передачу одного байта данных (ИНФА : 0). Выходной тактовый сигнал блока 2 в качестве счетного импульса поступает на вход счетчика 28 и элемент 27 задержки. Состояние счетчика дешифрируется дешифратором 29 и разрешает выдачу сигнала на выходе элемента И 21. Выходной сигнал элемента И 21 поступает на первые входы шифраторов 18 и 19. При этом шифратор 18 стробирован сигналом с выхода триггера 46, в то время как шифратор 19 блокирован. В результате на одном из выходов шифратора 18, соединенном сосоответ ствующим входом буферного регистра 6, появляется сигнал, по которому первый байт инфор мации с выхода буферного регистра 6 через блок 15 поступает на входную информационную шину. Таким образом, осушествляется передача 1-го байта 24-разрядного слова миниЭВМ. Сигнал запроса на передачу байта данных поступающих в канал 1 с одного из выходов регистра 9 (ИНФА : 1), одновременно поступает в блок 7 на первый вход триггера 73. 8результате элемент И 60 открывается и при поступлении на другой его вход сигнала квитирования из канала 1 на выходе появляется отгнал, который устанавливает триггер 74 в единичное состояние и переводит через элемент ИЛИ 64 в нулевое состояние триггер 73 (триггер 73, элементы И 60 и ИЛИ 64 образуют формирователь). Элемент И 59 оказывается открытым по второму входу. В MOMeiiT отсутствия сигнала запроса на передачу байта данных, поступающего из регистра 9(ИНФА : 0), и отсутствия сигнала квитирова1шя канала 1 (ИНФК : 0) первый и третий входы элемента И 59 оказьшаются также открытыми. Импульс с выхода элемента И 59 через элемент ИЛИ 65 переводит триггер 74 в исходное состояние (триггер 74, элементы И 59 и ИЛИ 65 образуют формирователь). Выходной импульс элемента И 59 через элемент 112 67 задержки в качестве выходного сигнала блока 7 поступает в регистр 9 и переводит его в состояние запроса канала 1 на передачу следующего (второго) байта данньи (ИНФА : 1). Рассмотренная логика работы блока 7 позволяет повторно генерировать импульсы установки запроса на передачу данных в канал 1 при наличии первоначально программно-установленного запроса. С выхода элемента И 22 импульсы поступают на вторые входы шифратора 18, в результате чего на выходе шифратора генерируется управляющий сигнал, по которому передается в канал 1 2-ой байт информации. 3-ий байт информации передается при появлении на одном из входов пшфратора 18 выходного сигнала логического элемента И 23, который по одному из входов разрешается выходным сигналом элемента ИЛИ 26, входы которого соединены с выходами регистра формата, единичное состояние которых указывает на обработку соответственно 8-, 12- и 24-разрядных слов мини(микро-) ЭВМ. Выходной сигнал логического элемента И 23 через элемент ИЛИ 24 поступает на вход блока 10, в результате чего работа мини-ЭВМ прерывается. По сигналу прерывания мини-ЭВМ через канал 52 и элементы И 50 переводит регистр 9 в состояние, соответствующее отключению устройства от канала 1 (РАБА : 0). При этом счетчики 28 и 36 переходят в исходное (нулевое) состояние. После отключения от канала 1 устройство ждет со стороны мини-ЭВМ нового асинхронного сигнала для передачи очередного слова данных, т.е. перевода регистра 9 в состояние , соответствующее запросу, в канал 1 на передачу байтов данных. 3. Выход из связи. Окончание передачи данных и выход из связи может производиться как по инициативе универсальной ЭВМ, так и по инициативе миниЭВМ. Если инициатива окончания передачи данных принадлежит ЕС ЭВМ, то после очередной распаковки и передачи 24-разрядного слова выходная управляющая шина канала 1 переходит в такое состояние, которое, указывает миниЭВМ на окончание передачи данных (УПРК: 17. Информация об этом состоянии в виде единичного сигнала (71д) поступает через пятую шину первого входа и элемент ИЛИ 62 в блок 10, что вызывает прерывание работы мини-ЭВМ. По данному сигналу прерывания мини-ЭВМ через канал 52 и элементы И 50 переводит устройство в состояние отключения от канала 1 (РАБА : 0). Кроме того, через элементы И 44 и 45 мини-ЭВМ переводит в исходное (нулевое) состояние регистр 48 формата и триггеры 46 и 47. Далее мини-ЭВМ переходит к выдаче стандартных байтов (или байта) состояния окончания обмена. Для этого мини-ЭВМ 13 устанавливает связь, на передачу байта состоя ш с каналом 1, как и в случае передачи байта данных. После прерывания работы по сигналу, постзшающему от канала 1, мини-ЭВМ через канал 52 выдает в блок 3 управляющие сигналы и байт состояния с признаком окончания обмена, который поступает на один из входов буферного регистра 6. Выходной сигнал блока 3 осуществляет запись байта состояния в буферный регистр 6. Далее мини-ЭВМ через канал 52 и элементы И 50 переводит регистр 9 в состоя1ше запроса канала 1 на передачу байта конечного состояния (УПРА : 1), что вызывает генерацию на выходе блока 2 управляющего тактирующего сигнала (66), осуществляющего передачу байта конечного состояния из буферного регистра 6 через блок 15 на один из входов (входная информационная щкна) канала 1. По окончании передачи конечного байта состояния или нескольких байтов состояний сштается, что операция ввода заверщена. Выход из связи по инициативе МИ1Ш-ЭВМ происходит аналогично, за исключо нием того, что это осуществляется на одном из тактов передачи слова данных, когда вместо очередного слова данных мини-ЭВМ передает байт конечного состояния. Следует отметить, что на каждый сигнал пре рывания мини-ЭВМ через канал 52 генерирует управляющие сигналы, которые вызывают появление на выходе блока 3 уп5ивляющих тактирующих сигналов, которые открывают элементы И 40, в результате чего информация о состоянии выходных управляющих тин канала 1 и триггера 13, регистрирующего некорректность информации, передается для анализа через элементы ИЛИ 42 в канал 52. II. Инициатор обмена ЕС ЭВМ. Вывод данны При выполнении операции выход этапы вхождения в связь и выхода из связи выполняются аналогично операции ввод. Процедура передачи данных осуществляется следующим образом. После установления связи с каналом 1 на передачу байтов данных мини-ЭВМ получает сигнал прерывания, свидетельствующий, что такая связь уста ювлена. По данному сигналу прерывания указанным способом осуществляется настройка устройства со стороны мини-ЭВМ на выполнение операции вывод с заданными форматами, в данном случае это преобразование байтов в 24-разрядное слово данных мини ЭВМ. В результате один из выходов регистра 48, указывающий на 24-разрядный формат, активен, триггер 12 находится в единичном состоянии. Далее мини-ЭВМ через канал 52 и элементы И 50 переводит регистр 9 в состояни соответствующее запросу канала 1 на передачу одного байта информации (ИНФА : 1). 14 Указанное состояние регнст в 9 передается на входы канала 1, блока 7 и блока 2. В ответ канал 1 изменяет состояние выходных управляющих шин (ИНФК: 1), информация о котором поступает на входы блока 2 и блока 7. в результате чего на выходе блока 2 появляется управляюи0ш тактирующий сигнал, который поступает на входы 28 и элемента 27 задержки. При этом счетчик 28 переводится в единичное сосгояние. После дешифрации состояния счетчика децшфратором 29 элемент И 21, открытый сигналами на других, формирует сигнал на первых входах цшфраторов 18 и ). При этом цшфратор 19 по одному из входов разрещен выходным сигналом триггера 47, а щифратор 18 запрещен выходным сигналом триггера 46, так .чак осу|цествляется операция вывод. В результате на одном из выходов цшфратора 19 появляется сигнал, который поступает на один из входов буферного регистра б и переписывает в него с 1 ыходных информационmix шин канала 1 первый байт данных. Блок 7 обрабатывает сигналы запроса и ответа аналогичным образом. Выходной сигнал блока 7 поступает на один из входов регистра 9 и снимает запрос на передачу байта да1ШЫХ.Указанное состояние регистра 9 уттравляющего слова передается на входные управляющие шины канала I, в результате чего канал 1 изменяет состояние выходных управляющих шин (ИНФК: 0), а блок 7, регистрируя исходное состояние, вырабатывает сигнал, поступающий на вход регистра 9, и переводит последний в состоя1ше, соответствующее запросу устройства на передачу очередного байта данных (ИНФА: 1). Передача в буферный регистр 6 второго и третьего байтов данных осуществляется аналотчным образом. Отличие состоит в том, что счетчик 28 последовательно переходит в состоя1ше, в результате чего по одним из входов последовательно открываются элементы И 22 и 23. По другим «ходам эти элементы открыты выходным сигналом элемента 27 задержки. По третьему входу логический элемент И 22 открыт выходным сигналом элемента ИЛИ 25. Выходной сигнал элемента И 22 поступает на второй вход шифратора 19, в результате чего на выходе последнего появляется управляющий сигнал, который поступает на вход буферного регистра б и переписывает в него второй байт данных. При передаче третьего байта данных элемент И 23 открывается выходным сигналом элемента ИЛИ 26, входы которого подключены к выходам регистра 23 и на одном из который в данный момент находится единичный потенциал, свидетельствующий о преобразовании байтовой информации в 24-разрядное слово данных МИНИ-ЭВМ. Выходной жгнал элемента И 23 появляется на третьем входе шифратора 19 что приводит к появлению на выходе последнего управляющего сигнала, поступающего в буферный регистр 6 для переписи с выходных информагдаонных шин канала 1 третьего байта ванных.

Одаовременно выходной сжгнал элемента И 23 через элемент ИЛИ 24 поступает на второй вход блока 10, в результате чего на выходе последнего появляется сигнал, прерываюицш работу мини-ЭВМ. По данному сигналу прерывания мини-ЭВМ, через канал 52 генерирует управляющие сигналы, которые поступают на вход блока 3, который открывает элементы И 39, и упакованная информация с одного из выходов буферного регистра б через элементы И 39 и элементы ИЛИ 42 поступает на вход канала 52, после чего цикл передачи слова в мини-ЭВМ может быть повторен.

III. Инициатор обмена мини-ЭВМ. .

При выполнении операций ввода-вьшода по инициативе мини-ЭВМ универсальная ЭВМ периодически вьшолняет специальную диагностическую операцию (в терминологии ЕС ЭВМ : Проверить ввод-вьшод). Через устройство в мини-ЭВМ пересылается указанная диагностическая команда, в соответствии с которой организуется передача в универсальную ЭВМ служебной информации запроса (в системе ЕС ЭВМ - это байт состояния Внимание)(v Принятый байт служебной информации запроса ан лизируется операционной системой ЕС ЭВМ, пос- лё чего со стороны ЕС ЭВМ начинается выполнение командп ввода-вывода, которая обеспечивает передачу необходимого массива служебной информации в ЕС ЭВМ, в котором содержится требование мини-ЭВМ выполнить ту или иную .операцию ввода-вывода над тем или иным массивом данных. По окончании передачи массива служебной информации ЕС ЭВМ вьшолняет затребованную операцию обмена со стороны мини-ЭВМ. Техническая реализация такой тактики с помощью предлагаемого устройства по существу не отличается от реализации операций ввода-вывода данных по инициативе ЕС ЭВМ.

1У. Выполнение операций ввода-вывода

с произвольной мини- (микро-) ЭВМ.

Устройство позволяет организовать связь и передачу данных между универсальной ЭВМ (например типа ЕС ЭВМ) и рядом произвольных мини-(микро-) ЭВМ. Разрядность шин данных интерфейса ввода-вьшода современных мини-(микро-) ЭВМ, как правило, имеет следующие значения: 8, 12, 16 и 24. Поэтому, исходя из практической направленности, а также соображений минимизации аппаратуры, устройство обеспечивает передачу информации межт/ йппынпй 4RM и МИНИ-(МИКОО-) ЭВМ с одним из указанных форматов. При работе какойлибо конкретной пары ЭВМ устройство легко адаптируется модульным сокращением буферного регистра 6 обмена, что приводит к минимизации оборудования. При этом предполагается, что сопрягаемые ЭВМ для связи с внешними устройствами имеют системы прерываний.

Рассмотрим кратко особенности работы предлагаемого устройства при сопряжении универ сальной ЭВМ (нап1жмер ЕС ЭВМ) с мини-(микро-) ЭВМ, имеющими разрядность шин данных интерфейса ввода-вывода, отличную от 24.

Если формат данных мини-(кткро-) ЭВМ равен 8, то миии- (микро-) ЭВМ через регистр 9 настраивает устройство таким образом, что после появления управляющего онгиала на одном из выходов шифратора 18 в случае операции ввода информации в ЕС ЭВМ или на одном из выходов шифратора 19 в случае операции вьшода информации из ЕС ЭВМ одновременно с передачей первого байта даииых элемент И 20 оказьтается открытым .выходными сигналами и соответствующим выходом регистра 48, который соответствует 8-ра:зрядиому формату шии данных интерфейса ввода-вывода юсни(микро-) ЭВМ. Выходной сигнал логического элемента И 20 через элемент ИЛИ 24 поступает на второй вход блока 10 и далее в качестве сигнала пре1 |1ваиия в мини-(NoiKpo-) ЭВМ.

0 Если разрядность шии данных интерфейса ввода-вьшода равна 12, то при передаче слов такого формата в устройстве осуществляется приведение значений разрядности шин данных интерфейсов универсальной ЭВМ и миш1-(мик5 ро-) ЭВМ, т.е. по прерывании мини- (микро-) ЭВМ выдает два 12-разрядных спавя, которые упаковьгеаются устройством в 24-разрядное слово, а затем организуется побайтная передача данных в ЕС ЭВМ.

..

Если миии-(микро-) ЭВМ имеет 16-разрядный формат данных иа шинах интерфейса, то за одно обращение к мини-ЭВМ устройство организует передачу в. ЕС ЭВМ только двух байт.

Таким образом, этапы вхождения в связь.

и выхода из связи как трудно стандартизируемые процецуры устройство позволяет реализовать с помощью систем прерываний на уровне Q программируемой логики, напртмер, в системе команд МИКИ-ЭВМ, а передачу данных, к которым к тому же предъявляются высокие требования по (Ыстродействию, реализовать аппаратно. Возможность хранения н интерпретации предлагаемым устройством командной информации ЭВМ обеспечивает передачу данных между универсально } ЭВМ и произвольной сернйно выпускаемой мини (микро-) ЭВМ в блокмультиплексном режиме, позволяющем соче17

тать гибкость системы с возможностью увеличения скорости передачи данных между ЭВМ. Формула изобретения Устройство для сопряжения двух цифровых вычислительных машин, содержащее регистр управляющего слова, выходом соединенный с первым входом первой щ{фровой вычислительной машинь, первый выход которой подключен к первому входу блока сравнения адресов, соединенного вторым входом с выходом регистра адреса, и к первому входу блока контроля по модулю, первый выход которого соединен с первым входом триггера контроля, выходом соединенного с первым входом коммутатора, второй вход которого подключен к первому выходу буферного регистра обмена, а выход - к первому входу второй цифровой вычислительной машины, и блок формирования сигнала прерывания, выход которого подключен ко второму входу вт1.рой цифровой вычислительной машины, отличающееся тем, что, с целью расширения области применения устройства, в него введены блок анализа состояния, два блока формирования тактовых импульсов, группу элементов И, блок формирования сигналов направления обмена, блоки управления чтением и записью и элемент ИЛИ, причем первый вход и второй выход буферного регистра обмена подключены соответственно к первому и второму входам блока контроля по модулю первый и второй входы блока анализа состояния соединены соответственно с первым и вторым входами первого блока формирования тактовых импульсов, вторым выходом и пер; вым входом первой цифровой вычислительной машины, второй вход которой соединен со вторым выходом блока контроля по модулю, третий и четвертый входы которого подключены соответственно к первому и второму выходам блока анализа состояния, третий выход которого соединен с третьим входом блока сравнения адресов, четвертый и пятый выходы - соответственно с первым и вторым входами регистра управляющего слова, а шестой и седьмой выходы - соответственно с первыми входами элемента ИЛИ и блока формирования шгнала прерывания, вторым входом подключенного к выходу блока управления чтением, третий вход коммутатора соеданен с первым входом блока анализа состояния, третий вход регистра управляющего слова подключен к выходу элемента ИЛИ, вторым входом соединенного с выходом блока сравнения адресов, группа входов регистра управляющего слова подключеиа к выходам элементов И группы и первым группам входов блоков управления чтением и записью, вторая группа входов которого соединена с первой группой входов регистра обмена, второй груптюй вхо6874118

дов блока управления чтением и группой выходов блока формирования сигналов направления обмена, первый, второй и третий выходы второго блока формирования тактовых импуль5 сов подключены соответственно к четвертому, пятому и шестому входам коммутатора, четвертый и пятый выходы - соответственно к первому и второму входам блока форКтрования сигналов направления обмена, третий вход

10 которого соединен со вторым входом буферного регистра обмена, первыми входами элементов И группы и первым выходом второй цифровой вычислительной мапшны, второй выход которой подключеч ко входу второго блоtS ка .формирования тактовых импульсов, шестым выходом подключенного к первому входу блока управления Зй.тисью, седьмым выходом - ко вторым входам элементов И группы, а пятым выходом - ко второму входу триггера

20 контроля, первый и второй выходы блока формирования сигналов направления обмена соединены соответственно с третьим и четвертым входами блока анализа состояния и первым и вторым входами блока управления чтением, а

25 третий выход - с третьим входом первого блока формирования тактовых импульсов, первый выход которого подключен к третьему входу буферного регистра обмена, а второй выход - к третьему входу блока управления чте1шем, группа выходов которого соединена

30 со второй группой входов буферного регистра обмена, четвертым входом соединенного с пятым входом блока анализа состояния и восьмым выходом зторого блока формирования тактовых импульсов, а третьей группой вхо дов - с группой выходов блока управления записью, второй вход которого подключен ко второму выходу блока формированиу сигналов направления обмана, седьмой вход коммутатора соединен с первым входом буферного ре40

гистра обмена.

блока, а четвертые входы - с выходом четвертого элемента И и первым входом первого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом первого элемента И и выходом блока, первые входы

второго, третьего и четвертого элементов И подключены через элемент задержки к третьему входу блока, вторые выхода 1 - к соответствующим выходам дешифратора, соединенного входом с выходом счетчика, вход и группа входов которого соединены соответственно с третьим входом и первой группой входов блока, треты входы второго и третьего элементов И подключены к выходу второго элемента ИЛ первый, второй, третий и четвертый входы которого подключены ко второй группе входов блока, третий вход четвертого элемента И соединен с выходом третьего элемента ИЛИ, вхо ды которого подключены соответственно к пер вому, третьему и четвертому входам второго элемента ИЛИ. 3.Устройство по п. 1, о т л и ч ю щ ее с я тем, что блок управления записью содержит счетчик, группой входов и выходов соединенный соответственно с первой группой входов блока и входом дешифратора, а входом - с выходом перпого эпемента И и череэ элемент эадержки - с первым : входами второ го, третьего и четвертого элементов И, вторые входы которых подключены соответственно к выходам дешифратора, а третьи входы - со ответственно к выходу и первому входу перво го элемента ИЛИ и выходу второго элемента ИЛИ, входы первого элемента И являются соответстве шо первым и вторым входами блока входы первого элемента ИЛИ подключены к соответствующим входам второй группы входов блока, входы второго элемента ИЛИ соединены соответственно с первым и вторым входами первого элемента ИЛИ, выходы второго, третьего и четвертого элементов являются группой входов &1ока. 4.Устройство по п. 1, о т л и ч а ю ш ее с я тем, что блок формирования сигналов направления обмена содержит группу элементов И, входы которых подключены соответственно к первому и третьему входам блока, а выходы - к информационным входам регистра формата, выходы которого являются группой выходов блока, а вход сброса подклю чеи ко второму входу блока и входам сброса первого и второго триггеров направления обмена, информадионными входами соединенных соответственно с выходами первого и второго элементов И, а выходами - соответственно с первым и вторым входами элемента ИЛИ и вторым и первым выходами блока, первые входы nepijoro и второго элементов И соеданены с первым входом блока, а вторые входы-с третьим входом блока. 5.Устройство по п. 1, о т л и ч а ю щ ее с я тем, что блок аналиэа состояния содержит четыре элемента НЕ, семь элементов И шесть элементов ИЛИ, два элемента задержки 120 и два триггера, причем первый вход первого злемента И соединен с выходом первого эпемента НЕ, второй вход - с первым входом блока, а третий вход - с четвертым входом блока и первым входом первого элемента ИЛИ, входы ; второго; элемента И подключены соответственно к первому и третьему входам блока, Ьторой. вход первого элемента ИЛИ соединен с третьим входом блока, а выход - череэ второй элемент НЕ с первым входом третьего элемента И, выход которого соединен с одним входом второго эпемента ИЛИ, а второй вход - с первым входом блока, входы второго элемента ИЛИ по;ослючены соответствешю к первому входу блока, а выход является седьмым выходом блока, входы четвертого эпемента И являются первым входом блока, а выход - со вторым выходом блока и первым входом третьего элемента ИЛИ, выход которого является шестым выходом блока, а второй вход соединен с выходом пятого элемента И, первый и второй входы которого подключены соответственно к первому и второму входам блока, выходы первого и второго элементов И соединены соответственно с пятым и первым выходами блока, выход шестого элемента И череэ первый элемент эадержки соединен с третьим выходом блока, первый вход через третий элемент НЕ соединен со втортлм входом блока и первым входом первого триггера, вто1ЮЙ вход - с выходом второго триггера, а трет1Й вход череэ четвертый элемент НЕ соединеи с первым входом седьмого элемента И и первым входом блока, первый вход второго триггерт соеданен с выходом седьмого элемента И и первым входом четвертого элемента ИЛИ, а второй вход - с выходом пятого элемента ИЛИ, первым входом подключенного к выходу шестого элемента И, а вторым входом - ко второму входу четвертого элемента ИЛИ, входу сброса четвертого элемента НЕ и пятому входу блока, второй вход седьмого элемента И подключен к выходу первого триггера, входы шестого элемента ИЛИ подключены к первому входу блока, а выход череэ второй элемент эадержки совФ нен с четвертым выходом блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СХИСР 1 628482, л. G 06 F 3/04, 1975. 2.Авторское свидетельство СССР по заявке U 2815714/18-24, кл. G 06 F 3/04, 1979 (прототип).

Авторы

Даты

1981-09-30—Публикация

1979-10-22—Подача