i

(Л

лов, блок 6 управления, блок 7 ключей, блок 8 свертки, блок 9 сравнения, дополнительный блок 10 сравнения, интегратор 11, аналоговый элемент 12 памяти, формирователь 13 по- роговьпс уровней, счетчик 14 импульсов. В устройстве производится изменение уровня порога детектора качества в соответствии с изменением параметров канала связи, что позволяет за счет сравнения характеристик некоторого числа наиболее вероятных сообщений уменьшить влияние изменения параметров канала связи на помехоустойчивость приема. Дополнительное к авт. св. № 915272. 1 з.п. ф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема сигналов, закодированных с избыточностью | 1987 |

|

SU1501297A1 |

| Устройство для приема сигналов, закодированных с избыточностью | 1988 |

|

SU1605275A2 |

| Устройство для статистического обнаружения дискретных сигналов в каналах связи с межсимвольной интерференцией | 1986 |

|

SU1363485A2 |

| Устройство для статистического обнаружения дискретных сигналов в каналах связи с межсимвольной интерференцией | 1984 |

|

SU1170621A2 |

| Устройство для статистического обнаружения дискретных сигналов в каналах связи с межсимвольной интерференцией | 1990 |

|

SU1811007A2 |

| СПОСОБ ИДЕНТИФИКАЦИИ ОБЪЕКТОВ И УСТАНОВКА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2010 |

|

RU2450363C2 |

| УСТРОЙСТВО ИТЕРАТИВНОГО ДЕКОДИРОВАНИЯ БЛОКОВЫХ ТУРБОКОДОВ И SISO ДЕКОДЕР ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2012 |

|

RU2504901C2 |

| ПРИЕМНОЕ УСТРОЙСТВО С ДВУХЭТАПНЫМ ПОИСКОМ ШУМОПОДОБНОГО СИГНАЛА ПО ЧАСТОТЕ И ЗАДЕРЖКЕ | 2001 |

|

RU2209478C2 |

| Устройство для приема двоичных сигналов | 1989 |

|

SU1709550A1 |

| ДИСКРЕТНЫЙ СОГЛАСОВАННЫЙ ФИЛЬТР | 2014 |

|

RU2589404C2 |

Изобретение относится к технике связи и может использоваться дпя помехоустойчивости приема дискретных сигналов. Цель изобретения - повьшение помехоустойчивости приема в каналах с переменными параметрами. Устройство содержит первьпй 2 и второй 3 решающие блоки, детектор 4 качества, формирователь 5 гипотетических сигна

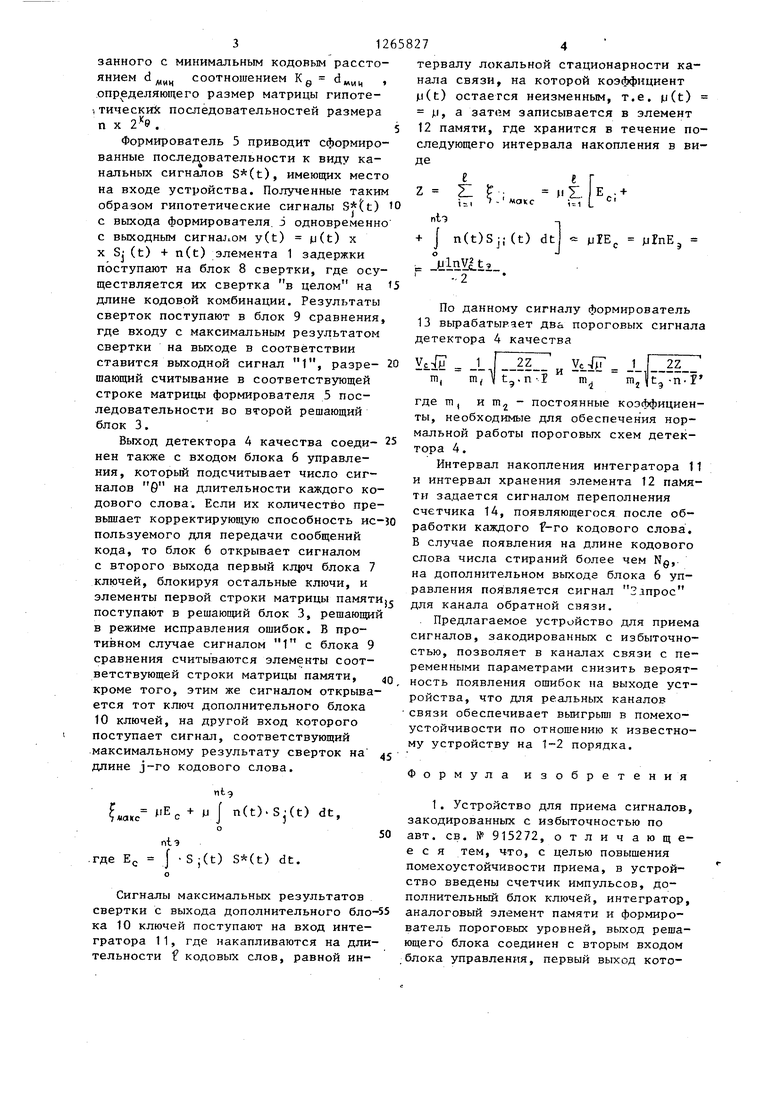

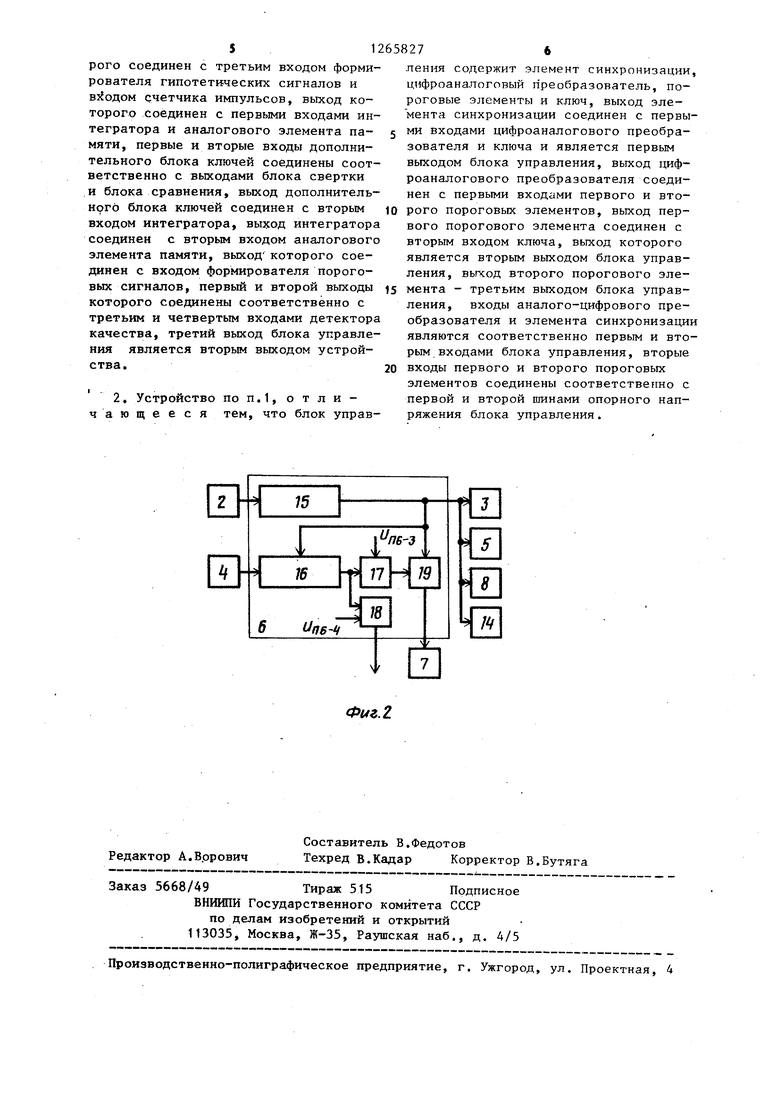

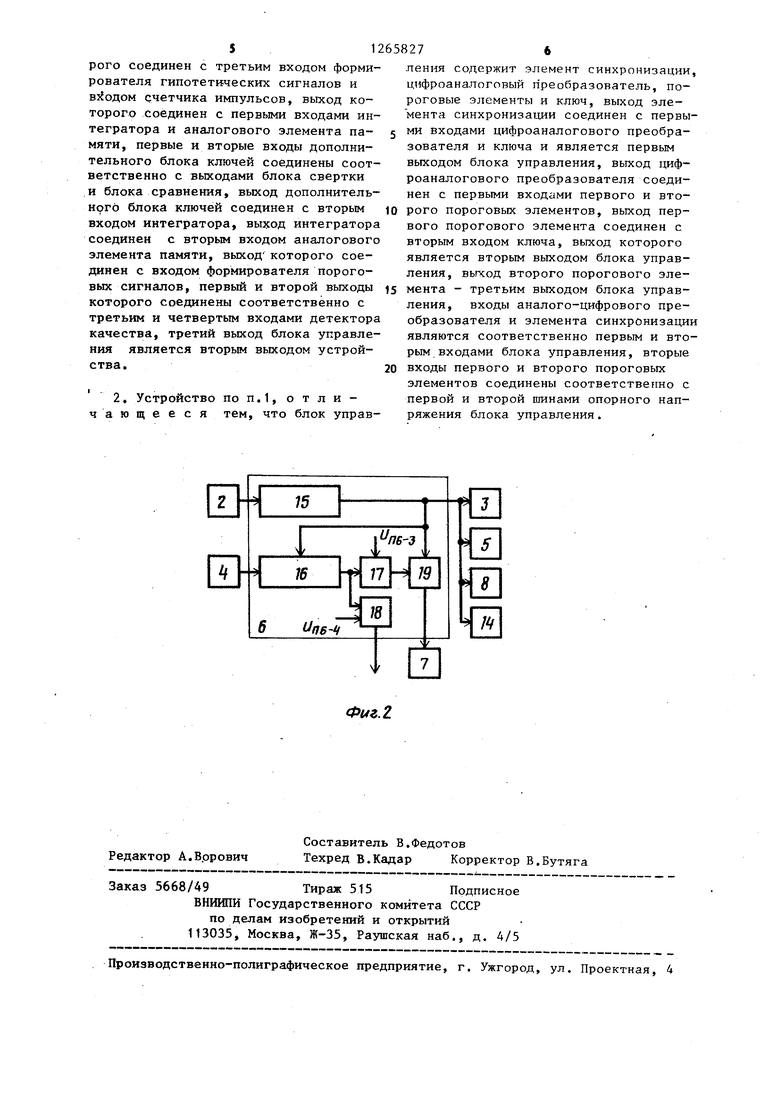

Изобретение относится к технике связи, может использоваться для помехоустойчивого приема дискретных сигналов и является усовершенствованием устройства по авт. св. № 915272. Цель изобретения - повьшение помехоустойчивости приема в каналах с переменными параметрами. На фиг.1 представлена структурная схема устройства; на фиг.2 - структурная схема блока управления устрой0,тва. Устройство содержит элемент 1 задержки, первый 2 и второй 3 решающие блоки, детектор 4 качества, формирователь 5 гипотетических сигналов, блок 6 управления, блок 7 ключей, блок 8 свертки, блок 9 сравнения, дополнительный блок 10 ключей, интегратор 11, аналоговый элемент 12 памяти формирователь 13 пороговых зфовней и счетчик 14 импульсов. Блок 6 управления содержит элемент 15 синхронизации, цифроаналоговый преобразователь 16, первый 17 и второй 18 пороговые элементы и ключ 19. Устройство работает следующим образом. На вход устройства поступают искаженные помехами двоичные сигналы, уровень которых изменяется в зависимости от коэффициента передачи канала связи. Первый решающий блок 2 принимает решение по каждому элементу с задержкой на один такт рабочей частоты дискретного Канала связи t, и оши бается тем чаще, чем интенсивней помехи в канале связи и чем меньше его коэффициент передачи. Одновременно с работой решающего блока 2 детектор 4 качества принимает решение о надежно сти принятия решения блоком 2 по каж дому элементу избыточного кодового слова. В начальный момент времени блок 6 управления по принятой двоичной последовательности специальной конфигурации с выхода решающего блока 2 и сигналам детектора 4 качества определяет границы кодовых слов (цикл), что соответствует появлению на его выходах сигналов определяющих начало и конец обрабатываемых кодовых слов решающим блоком 3, формирователем 5 гипотетических сигналов, блоком 7 ключей и блоком 8 свертки. При недостаточной надежности принимаемого элемента блоком 2 детектора 4 качества сигнал входформирователя 5 гипотетических сигналов, который формирует в виде строк матрицы гипотетические последовательности следующим образом. Если синхронно с поступлением решения об элементе (1 или О) сигнал 0 с детектора 4 качества не поступает, то в столбце матрицы памяти формирователя 5 гипотетических сигналов записывается решение, принятое решающим блоком 2. Если же сигнал 9 поступил, элемент, поступакяций с блока 2, во внимание не принимается и в столбце матрицы записывается равное количество О и 1, в верхней половине строк матрицы - О, в нижней I . При поступлении следующего сигнала 0 на длине того же кодового слова в очередном столбце матрицы заполняются в каждой из половинок строк разбитой пополам в верхней части строк О, ав нижней - 1, и так каждый раз с приходом очередного сигнала 9 на длительности кодового слова, до разрешенного числа стираний Kg, связанного с минимальным кодовым рассто янием d „„„ соотношением К d„„ц MUU V- . определяющего размер матрицы гипоте1 тически с последовательностей размера п X . Формирователь 5 приводит сформиро ванные последовательности к виду канальных сигналов S(t), имеюпщх мест на входе устройства. Полученные таки образом гипотетические сигналы (t) с выхода формирователя, 3 одновременн с выходным сигншюм y(t) jj(t) X X S; (t) + n(t) элемента 1 задержки поступают на блок 8 свертки, где осу ществляется их свертка в целом на длине кодовой комбинации. Результаты сверток поступают в блок 9 сравнения где входу с максимальным результатом свертки на выходе в соответствии ставится выходной сигнал 1, разретающий считывание в соответствз щей строке матрицы формирователя 5 последовательности во второй решающий блок 3. Выход детектора 4 качества соединей также с входом блока 6 управления, который подсчитывает число сигналов б на длительности каждого ко дового слова. Если их количество пре вьшает корректирующую способность ис пользуемого для передачи сообщений кода, то блок 6 открывает сигналом с второго выхода первый кл|оч блока 7 ключей, блокируя остальные ключи, и элементы первой строки матрицы памят поступают в решающий блок 3, решающи в режиме исправления ошибок. В противном случае сигналом 1 с блока 9 сравнения считываются элементы соответствующей строки матрицы памяти, кроме того, этим же сигналом открывается тот ключ дополнительного блока 10 ключей, на другой вход которого поступает сигнал, соответствующий максимальному результату сверток на длине j-ro кодового слова. (J I n(t). Г iE S(t) dt. Vwaicc .где EC I S ;(t) S(t) dt. Сигналы максимальных результатов свертки с выхода дополнительного блока 10 ключей поступают на вход интегратора 11, где накапливаются на длительности f кодовых слов, равной интервалу локальной стационарности канала связи, на которой коэффициент y(t) остается неизменным, т.е. fj(t) ).|, а затем записывается в элемент 12 памяти, где хранится в течение последующего интервала накопления в видег z i: ; i 1 nt-Э-, nt-Э I n(t)Sji(t) dtj MlE рГпЕ, t VlnY|.t, .,2 По данному сигналу формирователь 13 вырабатывает два пороговых сигнала детектора 4 качества IL 1 J 2Z 1 т, т, V t.п -Г m, m. i -э 2 - постоянные коэффициенты, необходимые для обеспечения нормальной работы пороговых схем детектора 4. Интервал накопления интегратора 11 и интервал хранения элемента 12 памяти задается сигналом переполнения счетчика 14, появляющегося после обработки каждого f-ro кодового слова. В случае появления на длине кодового слова числа стираний более чем NQ, на дополнительном выходе блока 6 управления появляется сигнал Запрос для канала обратной связи. Предлагаемое устройство для приема сигналов, закодированных с избыточностью, позволяет в каналах связи с переменными параметрами снизить вероятность появления ошибок на выходе устройства, что для реальных каналов связи обеспечивает выигрьш в помехоустойчивости по отношению к известному устройству на 1-2 порядка. Формула изобретения 1. Устройство для приема сигналов, закодированных с избыточностью по авт. св. № 915272, отличающееся тем, что, с целью повышения помехоустойчивости приема, в устройтво введены счетчик импульсов, доолнительный блок ключей, интегратор, налоговый элемент памяти и формироатель пороговых уровней, выход решащего блока соединен с вторым входом лока управления, первый выход кото512рого соединен с третьим входом формирователя гипотетических сигналов и взводом счетчика импульсов, выход которого соединен с первыми входами интегратора и аналогового элемента пательного блока ключей соединены соответственно с выходами блока свертки ,и блока сравнения, выход дополнительН9ГО блока ключей соединен с вторым входом интегратора, выход интегратора соединен с вторым входом аналогового элемента памяти, выход которого соединен с входом формирователя пороговых сигналов, первый и второй выходы которого соединены соответственно с третьим и четвертым входами детектора качества, третий выход блока управления является вторым вькодом устройства. 2. Устройство по п.1, о т л и чающееся тем, что блок управФиг.2 27 ления содержит элемент синхронизации, цифроаналоговый преобразователь, пороговые элементы и ключ, выход элемента синхронизатдии соединен с первыми входами цифроаналогового преобразователя и ключа и является первым выходом блока управления, выход цифроаналогового преобразователя соединен с первыми входами первого и второго пороговых элементов, выход первого порогового элемента соединен с вторым входом ключа, выход которого является вторым выходом блока управления, выход второго порогового элемента - третьим выходом блока управления, входы аналого-цифрового преобразователя и элемента синхронизации являются соответственно первым и вторым входами блока управления, вторые входы первого и второго пороговых элементов соединены соответствеггно с первой и второй шинами опорного напряжения блока управления.

| Авторское свидетельство СССР № 915272, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-10-23—Публикация

1985-01-02—Подача