ю а сд со

со

о

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1981 |

|

SU976499A1 |

| Коммутатор | 1981 |

|

SU974579A1 |

| Коммутатор | 1981 |

|

SU976500A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для счета импульсов | 1990 |

|

SU1734109A1 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1986 |

|

SU1363224A1 |

| Устройство для контроля электропотребления | 1986 |

|

SU1310844A1 |

Изобретение относится к электроизмерительной те.хпике и может быть использовано в коммутатора.х измерите.тыю-информационп1 1х систем. Цель - расширение фупкциональны.х возможностей коммутатора. Д.1я этого в многоканальный коммутатор по авт. св. № 1182658 дополнительно введен1 1 два блока сравнения, блок уставо| чис.ш измерений, счетчик, триггер, два y.ieMoiiTa ИЛИ, фор ировате.11 .1ьсов и о.чок .laнрета. В ycTpoiicTBC предусматривается возможность задапия скорости , .bi. времени задержки син.хроимглмьсо огносительно тактовых импу.пьсов .i.ui каж. кана.та индпвидуа,пьно с учетом его б1)1стро действия и в широком времепиом диапазоне. автоматическое и.х перек.иочеиие. Это дас возможность использования комм тато|1ных п.шт с раз.1ичными тинами у.1ектронн1)1х ключей, возможность нроизно.-ibHoio чис.1а измерений на замкнчтом Kana.ie с четом первого и пос,1едук)П1его ii3 Kpeiiiiii. 1Ч) обеспечивает мнснчжратпые измерения на капа.те с MaKcima.ihHoii скорост 1о опроса. 1 ил.

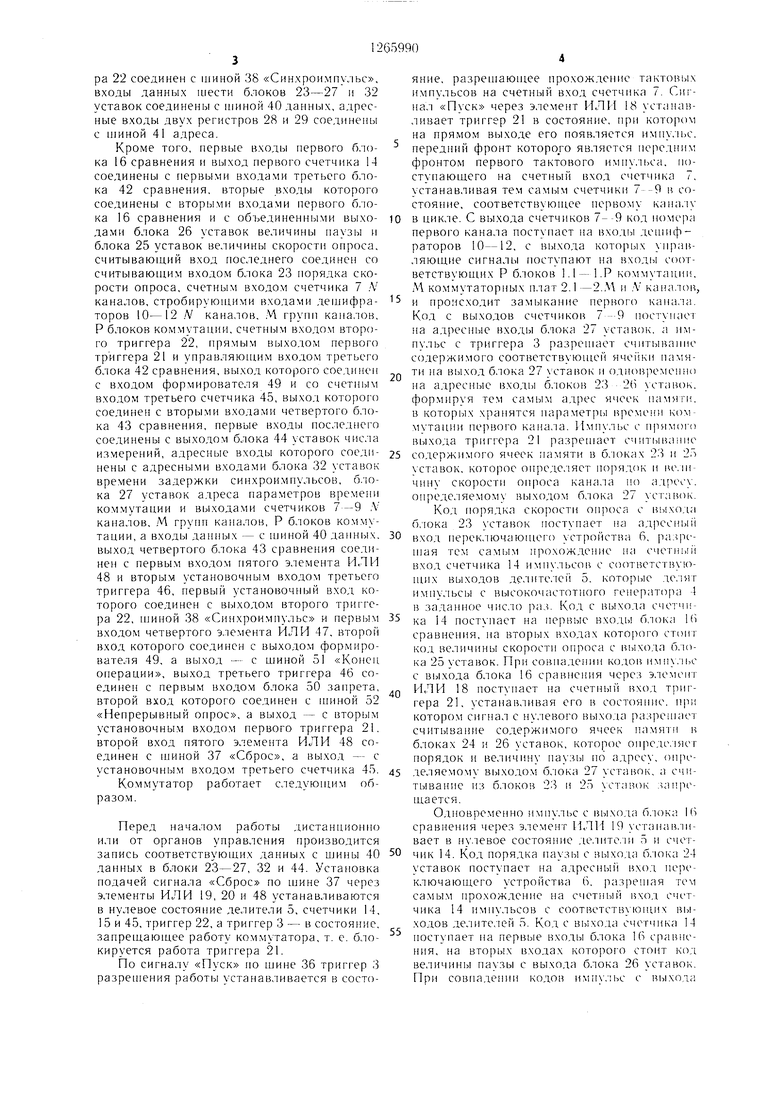

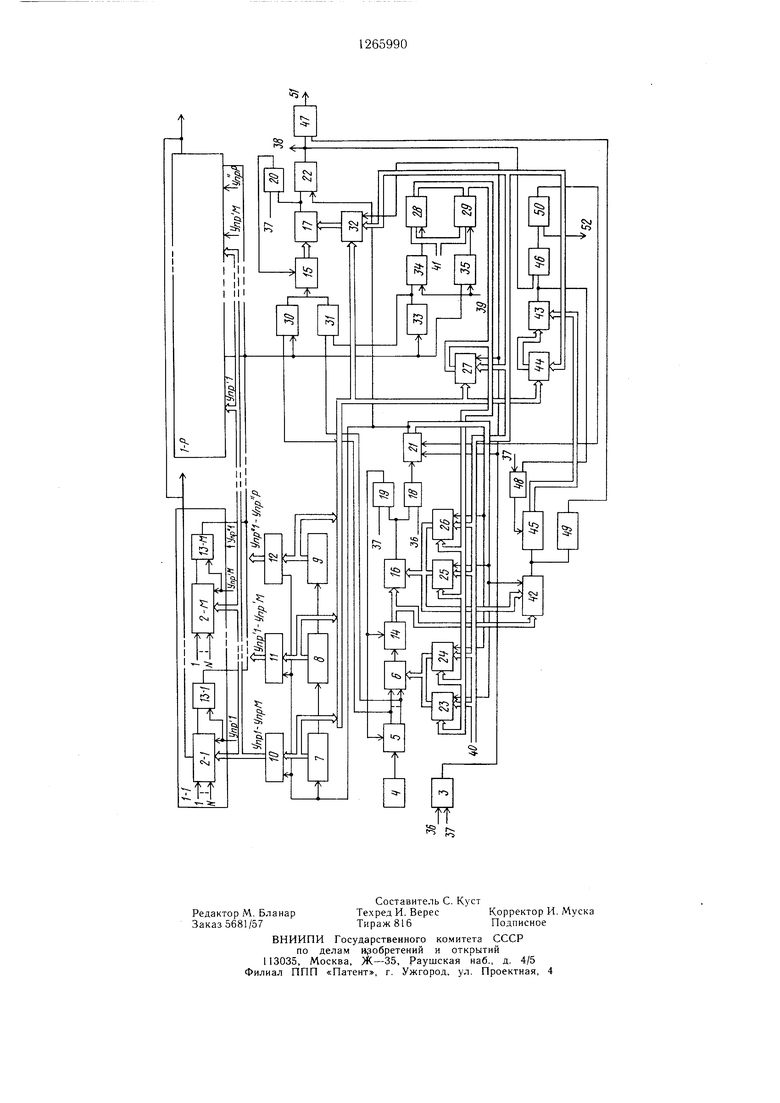

NJ Изобретение относится к электроизмерительной технике, в частности к коммутаторам измерительных информационных систем, и является усовершенствованием известного устройства по авт. св. № 1182658. Цель изобретения - расширение функциональных возможностей за счет обеспечения произвольного числа измерений на замкнутом канале с учетом первого и последующего измерения. На чертеже представлена функциональная схема коммутатора. Коммутатор содержит Р блоков 1.1 - 1.Р коммутации, состоящих из М коммутаторных плат 2.1-2.М коммутации входных измерительных сигналов, посредством которых объединены по выходу группы из N каналов, триггер 3 разрешения работы, последовательно соединенные задающий высокочастотный генератор 4, делитель 5, переключающее устройство 6, последовательно соединенные счетчики 7-9, дешифратор 10 /V каналов, дешифратор 11 М групп каналов, дешифратор 12.Р блоков коммутации, выходы дешифраторов при этом соединены с управляющими входами соответствующих Л каналов, М групп каналов, Р блоков коммутации. М управляемых формирователей 13.1 -13.М по числу Р блоков коммутации, два счетчика 14 и 15, два блока 16 и 17 сравнения, три элемента ИЛИ 18-20, два триггера 21 и 22, блок 23 уставок порядка скорости опроса, блок 24 уставок порядка паузы. блок 25 уставок величины скорости опроса, блок 26 уставок ,. величины паузы, блок 27 уставок адреса параметров времени коммутации, два регистра 28 и 29, два дополнительных управляемых формирователя 30 и 31, блок 32 уставок времени задержки синхроимпульсов, инвертор 33, два элемента И 34 и 35, шины «Пуск 36 и «Сброс 37, «Синхроимпульс 38, «Фиксированная скорость 39, шина 40 данных, шина 41 адреса. третий 42 и четвертый 43 блоки сравнения. блок 44 уставок числа измерений, третий счетчик 45, третий триггер 46, четвертый 47 и пятый 48 элементы ИЛИ, формирователь 49, блок 50 запрета, шины «Конец операции 51, «Непрерывный опрос 52. При этом выход переключающего устройства 6 соединен со счетным входом первого счетчика 14, выход которого соединен с первыми входами первого блока 16 сравнения, вторые входы которого соединены с объединенными выходами блока 25 уставок величины скорости опроса и блока 26 уставок величины паузы, выход первого блока 16 сравнения соединен с первыми входами первого 18 и второго 19 элементов ИЛИ, вторые входы элементов ИЛИ 18 и 19 соединены с шинами «Пуск 36 и «Сброс 37 соответственно, выходы элементов ИЛИ 18 и 19 соединены со счетным входом первого триггера 21 и установочными входами делителей 5 и первого счетчика 14 соответственно, примой выход первого триггера 21 соединен со счетным входом счетчика 7 /V каналов, стробирующими входами дешифраторов 10- 12 Л каналов, М групп каналов, Р блоков коммутации, со счетным входом второго триггера 22 и со .считывающими входами блока 23 уставок порядка скорости опроса и блока 25 уставок величины скорости опроса, инверсный выход первого триггера 21 соединен со считывающими входами блока 24 уставок порядка паузы и блока 26 уставок величины паузы, объединенные выходы блока 23 уставок порядка скорости опроса и блока 24 уставок порядка паузы соединены с адресными входами переключающего устройства 6, выходы счетчиков 7-9 N каналов, М групп каналов, Р блоков коммутации соединены с адресными входами блока 32 уставок времени задержки синхроимпульсов и с адресными входами блока 27 уставок адреса параметров времени коммутации, выход которого соединен с выходами первого 28 и второго 29 регистров и с адресными ,входами блоков уставок порядка 23 и величины скорости опроса 25, блоков уставок порядка 24 и величины паузы 26, считывающие входы блоков уставок адреса параметров времени коммутации 27 и времени задержки синхроимпульсов 32 соединены с выходом триггера 3 разрешения работы и с установочным входом первого триггера 21, входы М управляемых формирователей 13.1 -13.М в каждом блоке коммутации Р соединены с выходами признака типа коммутаторной платы соответствующих М коммутаторных плат, управляющие входы - с выходами дещифратора 11 М групп каналов, а объединенные выходы - с управляющим входом первого дополнительного управляющего формирователя 30, входом инвертора 33, первым входом второго элемента И 35, выход инвертора 33 соединен с первым входом первого элемента И 34 и управляющим входом второго дополнитель-ного управляемого формирователя 31, объединенные вторые входы первого 34 и второго 35 элементов И соединены с шиной 39 «Фиксированная скорость, выход первого элемента И 34 соединен с управляющим входом первого регистра 28, выход второго элемента И 35 соединен с управляющим входом второго регистра 29, входы первого 30 и второго 31 дополнительных управляемых формирователей соединены с выходами делителей 5, а объединенные выходы - со счетным входом второго счетчика 15, выход которого соединен с первыми входами второго блока 17 сравнения, вторые входы которого соединены с выходом блока 32 уставок времени задержки синхроимпульсов, а выход - с установочным входом второго триггера 22 и вторым входом третьего элемента ИЛИ 20, первый вход которого соединен с шиной 37 «Сброс, а выход - с установочным входом второго счетчика 15, выход второго триггеpa 22 соединен с тиной 38 «Синхроимпульс, входы данных шести блоков 23-27 и 32 уставок соединены с шиной 40 данных, адресные входы двух регистров 28 и 29 соединены с шиной 41 адреса.

Кроме того, первые входы первого б.юка 16 сравнения и выход первого счетчика 14 соединены с первыми входами третьего блока 42 сравнения, вторые входы которого соединены с втор1)1ми входами первого блока 16 сравнения и с объединенными выходами блока 26 уставок величины иаузы и блока 25 уставок величины скорости опроса, считывающий вход последнего соединен со считывающим входом блока 23 порядка скорости опроса, счетным входом счетчика 7 Л каналов, стробируюни-1ми входами деп ифраторов 10-12 .V каналов, М групп каналов, Р блоков коммутации, счетным входом второго триггера 22, прямым выходом первого триггера 21 и управляющим входом третьего блока 42 сравнения, выход которого соединен с входом формирователя 49 и со счетным входом третьего счетчика 45, выход которого соединен с вторыми входами четвертого блока 43 сравнения, первые входы последнего соединены с выходом блока 44 уставок числа измерений, адресные входы которого соединены с адресными входами блока 32 уставок времени задержки синхроимпульсов, блока 27 уставок адреса параметров времени коммутации и выходами счетчиков 7-9 .V каналов, М групп каналов, Р блоков коммутации, а входы данных - с шиной 40 данных, выход четвертого блока 43 сравнения соединен с первым входом пятого элемента ИЛИ 48 и вторым установочным входом третьего триггера 46, первый установочньп 1 вход которого соединен с В151ходом второго триггера 22, 38 «Синхроимпульс и первым входом четвертого элемента ИЛИ 47, второй вход которого соединен с выходом формирователя 49, а выход -- с шиной 51 «Конец операции, выход третьего триггера 46 соединен с первым входом блока 50 запрета, второй вход которого соединен с шиной 52 «Непрерывный опрос, а выход - с вторым установочным входом первого триггера 21. второй вход пятого элемента ИЛИ 48 соединен с шиной 37 «Сброс, а выход - с установочны.м входом третьего счетчика 45.

Коммутатор работает следуюи1им образом.

Перед началом работы дистанционно или от органов управления производится запись соответствуюших данных с UJHHBI 40 данных в блоки 23-27, 32 и 44. Установка подачей сигнала «Сброс по шине 37 через элементы ИЛИ 19, 20 и 48 устанавливаются в нулевое состояние делители 5, счетчики 14, 15 и 45, триггер 22, а триггер 3 - в состояние, запрешаюшее работу коммутатора, т. е. блокируется работа триггера 21.

По сигналу «Пуск но шине 36 триггер 3 разрешения работы устанавливается в состояние, разрешающее прохождение тактовых импульсов на счетный вход счетчпка 7. Сигнал «Пуск через элемент ИЛИ 18 устанавливает триггер 21 в состояние, при котором на прямом выходе его появляется импульс, передний фронт которого является передним фронтом первого тактового имцул1 са, иоступаюшего на счетпый вход счетчика 7, устанав,тивая тем самым счетчики 79 в состояние, соответствуюн1ее первому каналу в цикле. С выхода счетчиков 7--9 код номера первого канала поступает на входы дешифраторов 10-12, с выхода которых нравляющне сигналы поступают на BXCXTI I соответствуюших Р б,поков 1.1- 1.Р коммхтации, Л коммутаторных п.чат 2.1 -2.. и .-Y каналов, и про:1Сходит замыкание первого канала. Код с выходов счетчиков 7-9 постунаег на адресные входы б,чока 27 уставок, а импульс с триггера 3 разрешает считывание содержимого соответствующей памяти на В1)1ход блока 27 ycTaiiOK и одн(време11Н() на адресные вход1)1 б,1оков 23 2(i уставок, формируя тем самым адрес ячеек памяти. в KOTOpiiix хранятся параметр)1 времени KONIмутации первого канала. Импульс с прямого выхода триггера 21 разрешает счит1,1вание содержимого ячеек памяти в б.юках 23 и 25 уставок, которое определяет порядок и ве.шчииу скорости опроса канала но ад|нчу. определяемому В1)1ходом блока 27 хставок. Код порядка скорости опроса с выхода блока 23 уставок поступает на адресиы вход переключающего устройства 6, разре1пая тем самым прохождение на счетньи вход счетчика 14 импульсо с соответствуюших выходов де,1ителеГ1 5, которые деляг .1ьсы с высокочастотного генерато 1а 4 в заданное число раз. Код с выхода счетчика 14 постхпает на первые входы блока 1в сравнения, иа вторых входах которого стоиг код величины скорости опроса с выхода блока 25 уставок. Пр11 совпадении кодов импу. с выхода блока 16 сравнения через элемсиг ИЛИ 18 поступает на счетный вход триггера 21, устанавливая его в состояние, при котором сигнал с ну,1евого выхода разреи1ает считывание содержимого ячеек памяти в б,юках 24 и 26 уставок, которое опредоляег порядок и величину паузы но адресу, on ieделяемом выходо б,1ока 27 уставок, а считыванне блоков J.шается.

Одновременно имиу.тьс с выхода блока 16 сравнения через э,1емент ИЛИ 19 устанавливает в нулевое состояние делите.1И 5 и счетчик 14. Код порядка пауз с выхода б,1ока 24 уставок поступает на адресньп вход нереключаюшего устройства 6, разрешая тем самым прохождеппе на счетный вход счетчика 14 импульсов с соответствуюших выходов делителей 5. Код с В1 1хода счетчика 14 поступает па первые входы блока 16 сравнения, на вторых входах которого стоит код величины паузы е выхода блока 26 уставок. Ири совпадении кодов имиу,1ьс с выходи

блока 16 сравнения через элемент ИЛИ 18 поступает на счетный вход триггера 21, устанавливая его в состояние, при котором сигнал с прямого выхода разрешает считывание содержимого ячеек памяти в блоках 23 и 25 уставок, и передний фронт которого является .передним фронтом второго тактового импульса, поступающего на вход счетчика 7. Одновременно импульс с выхода блока 16 сравнения через элемент ИЛИ 19 устанавливает в нулевое состояние делители 5 и счетчик 14.

Таким образом, происходит формирование первого тактового импульса, длительность которого состоит из величины скорости опроса первого канала и величины паузы между размыканием первого канала и замыканием второго. Передний фронт второго тактового импульса на счетном входе счетчика 7 изменяет его состояние на +1, что приводит к замыканию следующего канала и изменению адреса ячейки памяти в блоке 27 уставок, тем самым на выходе блока 27 уставок появляется код адреса ячеек памяти блоков 23-26 уставок, в которых хранятся параметры времени коммутации следующего канала. Сформированные описанным способом тактовые импульсы с прямого выхода триггера 21 поступают на стробирующие входы дешифраторов 10-12, обеспечивая замыкание каналов на время скорости опроса и размыкание предыдущего канала до замыкания следующего на время паузы. Это позволяет избежать одновременного замыкания двух каналов, когда предыдущий еще не разомкнулся, а последующий уже замкнулся, что может привести к выходу из строя соответствующих датчиков на входах коммутируемых каналов.

Таким образом происходит коммутация каналов с индивидуальной скоростью опроса, что позволяет максимально использовать быстродействие каждого канала, автоматическое переключение скорости опроса и паузы для каждого канала, дает возможность одновременно использовать разные типы

коммутаторных плат, например одновременно контактные и бесконтактные.

В случаях, когда требуется опрашивать все каналы с одинаковой скоростью или все каналы контактных плат с одной скоростью, а все каналы бесконтактных плат с другой, предусмотрен режим с «фиксированной скоростью.

В коммутаторных платах 2.1-2.М задается специальный сигнал - признак типа коммутаторной платы, например для коммутаторных контактных плат это может быть сигнал логический «О, а для бесконтактных коммутаторных плат - сигнал логическая «1. Этот сигнал с выхода коммутаторных плат поступает на соответствующие входы М управляемых формирователей 13.1 -13.М в каждом из Р блоков 1.1 - 1.Р коммутации.

управляющие входы которых соединены с соответствующими выходами дешифратора 11, что позволяет сигналу «Признак коммутаторной платы проходить на объединенный выход М управляемых формирователей 13.1 - 13.М во всех Р блоках 1.1 - 1.Р коммутации только в момент опроса данной коммутаторной платы. При наличии на объединенных входах элементов И 34 и 35 сигнала «Фиксированная скорость, поступающего с щины 39, в зависимости от сигнала «Признак типа коммутаторной платы проходит сигнал с входа или выхода инвертора 33 на управляющие входы первого или второго регистров 28 и 29, по которому на выходе соответствующего регистра формируется адрес ячейки памяти блоков 23-26 уставок, где хранятся параметры порядка и величины скорости опроса, порядка и величины паузы для контактной или бесконтактной платы коммутации соответственно. Адреса этих ячеек памяти поступают на адресные входы регистров 28 и 29 с щины 41 адреса перед началом работы или могут быть установлены постоянными, например регистр 28 может хранить адрес нулевой ячейки блоков 23-26 уставок, а регистр 29 - адрес первой ячейки.

Источником возникновения управляющих сигналов включения канала и формирования сигналов «Конец операции или «Синхроимпульс являются тактовые импульсы с первого триггера 21.

В зависимости от сигнала «Признак типа коммутаторной платы на управляющих входах дополнительных управляемых формирователей 30 и 31, на счетном входе второго счетчика 15 появляются импульсы с соответствующего выхода делителей 5. Код с выхода второго счетчика 15 поступает на первые входы блока 17 сравнения, на вторых входах которого присутствует код величины задержки синхроимпульсов относительно тактовых импульсов из ячейки памяти блока 32 уставок, адрес которой задается кодом с выхода счетчиков 7-9, т. е. для каждого канала по соответствующему адресу записан код величины задержки синхроимпу.пьсов в блоке 32 уставок. На счетный вход второго триггера 22 поступают тактовые импульсы с выхода первого триггера 21, передний фронт которых устанавливает второй триггер 22 в состояние, запрещающее начинать измерение на скоммутированном канале до окончания в нем переходных процессов. При совпадении кодов импульс с выхода второго блока 17 сравнения через элемент ИЛИ 20 устанавливает второй счетчик 1.5 в нулевое состояние и по установочному входу переводит второй триггер 22 в состояние, разрешающее начинать измерение на скоммутированном канале через время, определяемое временем задержки, считанном из блока 32 уставок, индивидуальное для каждого канала, т. е. сигналы «Синхроимпульс формируются с задержкой относительно тактовых импульсов с учетом быстродействия каждого канала и проходят на шину 38 и через элемент ИЛИ 47 - на шину 51. Таким образом, в случае непрерывного опроса, сигнал «Конец операции на шине 51 (или «Синхроимпульс на шине 38) формируется с задержкой по отношению к переднему фронту тактовых импульсов и обеспечивается автоматическое изменение этой задержки, что дает возможность использовать в одном коммутаторе коммутаторные платы с различными типами ключей. Коммутатор в режиме с многократным опросом работает следующим образом. Сигнал «Пуск через элемент ИЛИ 18 устанавливает первый триггер 21 в состояние, при котором на прямом выходе его появляется импульс, передний фронт которого является передним фронтом первого тактового импульса, поступающего на счетный вход счетчика 7, устанавливая тем самым счетчики 7-9 в состояние, соответствующее адресу первого канала в цикле. С выхода счетчиков 7-9 код номера первого канала поступает на входы дешифраторов 10-12, с выхода которых управляющие сигналы поступают на входы соответствующих Р блоков 1.1 - 1.Р коммутации, М коммутаторных плат 2.1-2.М и N каналов, и происходит замыкание первого канала. Импульс с прямого выхода первого триг гера 21 разрешает считывание содержимого ячеек памяти в блоках 23 и 25 уставок, которое определяет порядок и величину скорости опроса первого канала по адресу, определяемому выходом блока 27 уставок. Дальше формирование первого тактового импульса, длительность которого состоит из величины скорости опроса и величины паузы на этапе формирования величины скорости опроса осуществляется аналогично описанному. Одновременно передний фронт первого тактового импульса с первого триггера 21 устаналивает второй триггер 22 в состояние, запреща.ющее начинать измерение на скоммутированном канале до окончания в нем переходных процессов. Через время, определяемое временем задержки, считанном из блока 32 уставок, второй триггер 22 устанавливается описанным способом в состояние, разрешающее начинать измерение на скоммутированном канале. Этот сигнал через элемент ИЛИ 47 появляется на шине 51, как сигнал первого из.мерения на скоммутированном канале. Одновременно сигнал с выхода второго триггера 22 поступает на установочный вход третьего триггера 46, сигнал с выхода которого через блок 50 запрета ири отсутствии на его втором входе сигнала «Непрерывный опрос поступает на установочный вход первого триггера 21, блокируя его работу. Таким образом, при совпадении кода с первого счетчика 14 и кода величины скорости опроса с выхода блока 25 уставок, импульс с выхода первого блока 16 сравнения через элемент ИЛИ 18 не переворачивает первый триггер 21 в состояние, при котором сигнал с инверсного выхода его разрешает считывание ,содержимого ячеек памяти в блоках 24 и 26 уставок, которое определяет порядок и величину )i по адресу, определяемому выходом блока 27 уставок. По-прежнему сигнал с прямого выхода первого триггера 21 разрешает считывание содержимого из тех же ячеек памяти блоков 23 и 25 уставок и одновременно разрешает работу третьего б,юка 42 сравнения. В момент совпадения кода первого счетчика 14 и кода величины скорости опроса первого канала с выходов б,юка 25 уставок велич1шы скорости опроса на выходе третьего блока 42 сравнения ноявляется импульс, поступающий на формирователь 49, которьп по его переднему фронту формирует импу.п.с, который через элемент ИЛИ 47 поступает на шину 51 в виде второго импу,1ьса «Конец операции, разрешая второе измерение на замкнутом канале. Поскольку первый триггер 21 находится в прежнем состоянии, на выход третьего блока 42 сравнения в моменты совпадения кода первого счетчика 14 и кода ве.чичины скорости опроса появляется пос.1едовате.1ьность импульсов, поступающих на iiniiiy 51 и определяющих последующие измерения на том же канале. Одновременно эта последовательность импульсов с выхода трет:,его блока 42 сравнения поступает на счетный вход третьего счетчика 45, код с выхода которого поступает на вторые входы четвертого блока 43 сравнения. На первых входах блока 43 стоит код числа измерений па выбранном канале с выхода блока 44 уставок, считанный из ячейки намяти по адресу, определяемому кодом счетчиков 7--9. ИМпчмьс с выхода четвертого блока 43 сравнепия, определяющий момент совпадения этих кодов и означаю ций, что на замкнчтом кана.ю произведено заданное число измерени, через элемент ИЛИ 48 сбрасывает трети счегчик 45 в нулевое состояние и устанавливает третий триггер 46 в состояние, при KOTOJMIM импульс с блока 50 запрета снимает б.юкировку с первого триггера 21, переворачивая его в состояние, ири котором сигнал с инверсного выхода разрешает считывание содержимого ячеек памяти в блоках 24 и 26 уставок, запрещает считывание из блоков 23 и 25 уставок и запрещает работх третьего блока 42 сравнения. После формирования паузы перн1 1Й три гер 21 устанавливается в состояние, при котором сигнал с его прямого выхода разрешает считывание содержимого ячеек памяти в блоках 23 и 25 уставок и работу третье|-о блока 42 сравнения. Одновременно персдн фронт этого сигнала является передним фронтом второго тактового импульса, поступающего на вход счетчика 7 и второго триггера 22, обеспечивая замыкание второго канала и формирование сигнала первого и последующих измерений на втором канале, аналогично описанному.

Таким образом, в коммутаторе расширены функциональные возможности за счет задания скорости опроса, паузы и времени задержки синхроимпульсов относительно тактовых импульсов для каждого канала индивидуально с учетом его быстродействия, возможности автоматического переключения скорости опроса, паузы и времени задержки синхроимпульсов, что дает возможность одновременно использовать в коммутаторе коммутаторные платы с различными типами ключей.

При возможности произвольного числа измерений на замкнутом канале с учетом первого и последующего измерений, что позволяет производить многократные измерения на канале с максимальной скоростью опроса.

Формула изобретения

Коммутатор по ав. сЪ. № 1182658, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены два блока сравнения, блок уставок, числа измерений, счетчик, триггер, два элемента ИЛИ, формирователь, блок запрета, при этом первые входы первого блока сравнения и выход первого счетчика соединены с первыми входами третьего блока сравнения, вторые входы которого соединены с вторыми входами первого блока сравнения и

с объединенными выходами блока уставок величины паузы и блока уставок величины скорости опроса, считывающий вход последнего соединен со считывающим входом блока порядка скорости опроса, счетным входом

счетчика /V каналов, стробирующими входами дешифраторов /V каналов, М групп каналов, Р блоков коммутации, счетным входом второго триггера, прямым выходом первого триггера и управляющим входом третьего блока сравнения, выход которого соединен с входом формирователя и со счетным входом третьего счетчика, выход которого соединен с вторыми входами четвертого блока сравнения, первые входы последнего соединены с выходом блока уставок числа

измерений, адресные входы которого соединены с адресными входами блока уставок времени задержки синхроимпульсов, блока уставок адреса параметров времени коммутации и выходами счетчиков /V каналов,

М групп каналов, Р блоков коммутации, а входы данных - с щиной данных, выход четвертого блока сравнения соединен с первым входом пятого элемента ИЛИ и вторым установочным входом третьего триггера, первый установочный вход которого соединен с выходом второго триггера, щиной «Синхроимпульс и первым входо.м четвертого элемента ИЛИ, второй вход которого соединен с выходом формирователя, а выход - с щиной «Конец операции, выход третьего триггера соединен с первым входом

блока запрета, второй вход которого соединен с щиной «Непрерывный опрос, а выход - с вторым установочным входом первого триггера, второй вход пятого элемента ИЛИ соединен с шиной «Сброс, а выход - с установочным входом третьего счетчика.

| Авторское свидетельство СССР № 1182658, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

Авторы

Даты

1986-10-23—Публикация

1985-05-22—Подача