1

Изобретение относится к электроизмерительной технике, в частности, к коммутаторам измерительных информационных систем,

Известны коммутатрры измерительных сигналов, содержащие блоки коммутации входных измерительных каналов и устройство управления коммутатора. Блок коммутации входных измерительных сигналов объединяет по выходу группу входных каналов и подключается к измерительному прибору (аналого-цифровому преобразователю, цифровому вольтметру), Устройство управления коммутатора соответственно содер кит счетчики и дешифраторы кана.лов и групп каналов, задающий генератор тактовой частоты опроса каналов 11.

Однако такие коммутаторы обеспечивают низкую скорость опроса каналов, особенно при контактной коммутации.

Наиболее близким к предлагаемому по технической сущности является комму v татор, содержащий М коммутаторных плат коммутации входньк измерительных

сигналов, каждая из которых Ъ1эъединяет по выходу группу из N каналов и устройство управления, содержащее сч€ тчики }vl каналов в группе к М групп каналов, выходы которых соединены со входами дешифраторов N каналов в грутше и М групп каналов, выходы которых соединены с yиpaвлiцoщими входами коммутаторных плат, что определяет выбор одной определенной коммутаторной платы и одного

10 канала на ней, задающий генератор, выходHbie импульсы которого поступают на счетный вход счетчика N каналов в груп пе при работе в циклическом режиме и на входы записи счетчиков N1 каналов в

IS группе и М rpymi каналов при работе в адресном режиме | 2 .

Однако известное устройство имеет недостаточную скорость опроса каналов

20 коммутатора в адресном ре5киме.

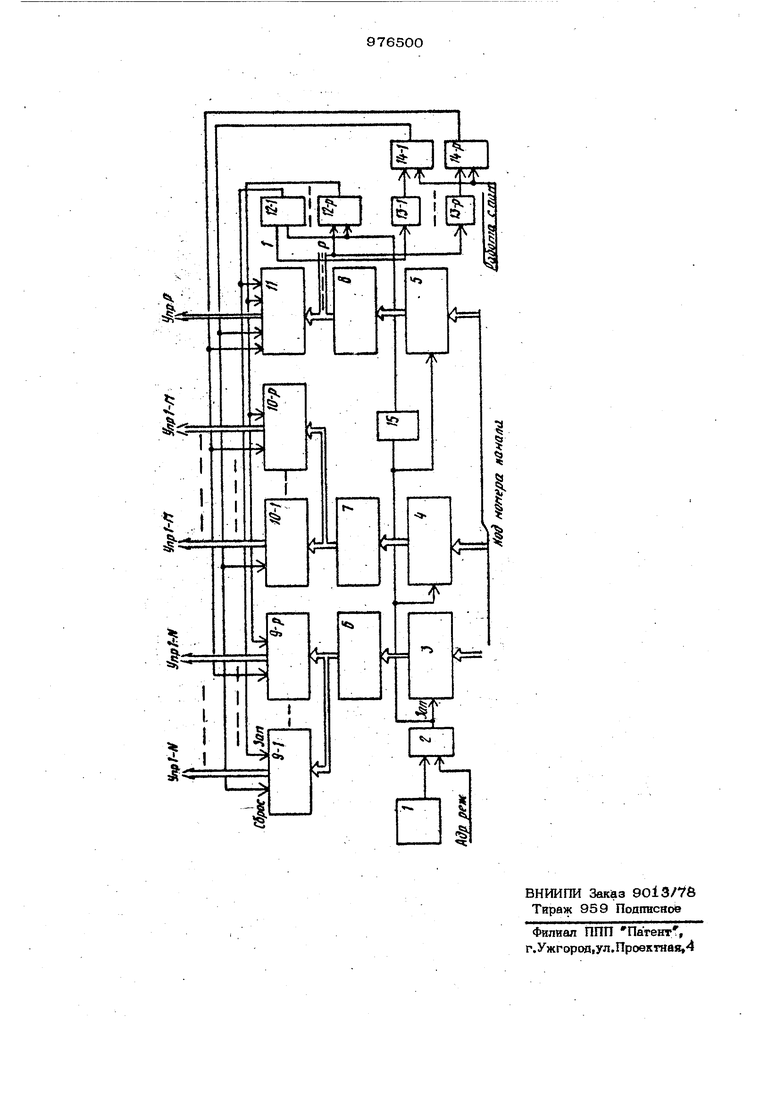

Цель изобретения- повышение скорости опроса каналов коммутатора в адресном режиме. Поставленная цель достигается трем, что в коммутатор, содержащий последовательно соединенные счетчик и дешифратор N каналов в группе, счетчик и дешифратор М групп каналов, задающий генератор и элемент И адресного режима, введены последовательно соединенные счетчик и дешифратор Р блоков ком чгта- ции, каяодьй из которых содержит М груп каналов, запоминак-ших регистров Ы кана лов в группе по числу Р блоков комму та Ш1И, Р запоминающих регистрюв М групп каналов, запоминающий регистр Р блоков коммутации, Р элементов И записи, Р элементов Jl сброса, Р инвертеров и блок временной задержки, при этом запоминаю щие регистры М каналов в группе, М групп каналов и Р блоков коммутации последовательно соединены с соответст вующими дешифраторами, одни входы Р элементов И записи объединены мезкду собой и соединены с выходом блока временной задержки, другой вход с одним из выходов дешифратора Р блоков коммутации от 1нсч до Р и входом одного из Р инверторов, а выходы со входами записи соответствующих запоминающих регистров М каналов в группе и М групп каналов от 1-го до Р и Р входами записи запоминающего регистра Р блоков коммутации, выходы Р инверторов соединены с одним входом Р элементов И сброса, другие входы которых объединены между собой и соединены с шиной признака Таёота с памятью а выходы соединены с входами сброса соответствующих запоминающих регистров N каналов в группе и М групп каналов от 1-го до Р и Р входами сброса запоминающего регистра Р блоков коммутации, выход за дающего генератора соединен с одним входом элемента И адресного режима, другой вход которой соединен с шиной признака адреснохю режима, а выход с объединенными входами записи счетчиков N каналов в группе, М каналов и. Р блоков коммутации и входом блока временной задержки. На чертеже представлена функциональная схема предлагаемого устройства. Устройство содержит задающий генератор 1, выходные тактовые импульсы Которого поступают на элемент И 2 совпадения с признаком адресного режима, счетчики 3-5 К| номера каналов в группе, М групп каналов и Р блоков коммуочацик cooTBeTCTBeifflo, имеющие входы для записи кода номера канала в группе, номера группы каналов и номера блока коммутации, дешифраторы 6-8 Ы номера каналов в группе М групп каналов и Р блоков коммутации соответственно, преобразующие код, поступающий от соответствующих счетчиков 3-5, запоминающие регистры 9-1-9-Р, 10-1-10-Р, 11 номера канала в группе, М групп каналов по числу блоков коммутации Р и запоминающий регистр Р блоков коммутапни, вькодные сигналы которых являются управляющими сигналами включения ключей коммутаторных плат определенной группы, элементы И 12 1-12-Р записи, инверторы 13-1-13-Р, элементы Иt 14-1-14-Р сброса, блок 15 временной задержки, обеспечивающий задержку тактовых импульсов задающего генератора 1, Предлагаемое устройство работает следующим образом, В адресном. режиме работы коммутатора счетчики 3-5 N номера каналов в группе, М групп каналов и Р блоков коммутации по входу записи устанавливаются в положение, соответствующее заданному адресу, выбранному вручную или дистанционно. Сигнал записи в адресном режиме вырабатьшается по тактовым ик 1 льсам задающего генератора 1 и через элемент И 21 проходит на объединегаи,1е входы записи всех счетчиков 3-5. Эти счетчики, в частном случае, могут представлять собой единый счетчик, младшие разряды которого предназначены для выбора номера канала в группе, следующие для выбора номера группы каналов (номера коммутаторной платы), а старшие для выбора номера блока коммутации. Блок коммутации представляет собой набор из. М rpyim каналов или М коммутаторнькс плат, таких блоков коммутации может быть Р. Дешифраторы 6-8 N номера канала в группе, М групп каналов и Р блоков коммутации преобразуют код соответствующих счетчиков 3-5 в управляющие сигналы включения каналов коммутатора, поступающие предварительно ija вход запоминающих регистров 9-11. Устройство содержит запоминающие регистры для запоминания кода номера выбранного канала. Р регистров 9-1-9-Р служат для запоминания кода номера канала в группе Ы . Р регистров 10-1-10-Р служат для запоминания кода номера группыканалов М. Один регистр 11 служиг дня запоминания номера блока коммутации Р. С выхода регистра управл5пощие сигналы поступают непосредственно на включение ключей коммутаторных плат.

Запись в регистра 9-1-9-Р, iO-1-lOР и 11 производится по тактовым импульсам задающего генератора 1, прохоД5Ш1ИМ через блок 15 временной задержки. Временная задержка дает возможность отработать таким узлам устройства, как счетчики 3-5 и дешифраторы 6-8 прежде, чем производится запись кода в регистрьи

Импульсы записи проходят на входы записи региотров 9-1-0-Р и 10-1-10-Р через элементы И 12-1-12-Р записи, обеспечивающие пропускание тактовых импульсов задающего генератора 1 только при наличии сигнала выбора данного блока коммутации, одного из Р блоков. Эти сигналы выбора представляют собой Р выходных сигналов дешифратора Р блоков коммутации, которые по одному поступают на вход элементов И 12-1-12-P записи.

При выборе соответствующего блока коммутации появится сигнал записи на выходе одного из элементов И 12-1-12записи к соответственно на входе записи одного из задомищцоашх регистров N номера канала в группе к одного из запоминающих регистре М групп каналов, относящихся к данному выбранному блоку коммуташш Р.

Запоминающий регистр ИР блоков коммутации имеет Р входов записи, так как в этом регистре запись в каждый разряд осуществляется независимо - по выходному сигналу одного из элементов И 12-1-12-Р записи.

Таким образом, при выборе любого блока ко1У1муташга Р на выходе регистров возникают утфавляющие сигналы выбора блока коммутации, группы каналов в нем и номера канала в группе, что определит включение конкретного кашша в данном блоке .

Работа коммутатора может происходит в дцух режимах:, с запоминанием и .без запоминания включенного канала в одном блоке коммутации после перехода к выбору другого блока коммуташск.

В режиме без запоминания отсутствует внешний сигнал Работа с памятью, поступающий на входы элементов И 14-1-14-Р сброса в виде нулевого сиг нала. При его отсутстини на этих входах элементов И 14-1-14-Р сброса - единичный сигнал. На вторые входы поступают инвертированные выходные сигналы дешифратора 8 Р блоков коммутации с выхода инверторов 13-1-13-Р и при выборе данного блока коммутации на втором входе

соответствующего ему элемента И 14-1-14-Р сброса появляется нулевой сигнал, запрещающий сброс регистров. При переходе к другому блоку коммут 1ции Р этот сигнал становится единичным, так как с дешифратора Р блоков коммутации теперь вьщается нулевой сигнал невыбора. На втором входе элемента И 14-1-14-Р сброса также единичный , соответствующий отсутствию сиГнаМ Работа с памятью , и на выходе элемента И сброса появляется нулевой сигнал сброса регистра.

Таким образом, при переходе к другому блоку коммутации Р регистр номере канала в группе N и регистр группы каналов М, соответствующие выбранному ранее блоку коммутации Р, сбрасываются и происходит выключение ранее выбранного канала в момент пропадания сигнала выбора,

Запоминающий регистр ИР блоков коммутации имеет Р входов сброса; так как аналогично записи сброс каждого бго разряда осуществляется независимо по выходным сигналам соответствующих элементов И 14-1-14-Р сброса. При переходе к другому блоку коммутации разряд регистра И, соответствующий ранее выбранному блоку коммутации так же сбрасывается, В этом режиме без запоминания работа в адресном режиме происходит аналогично известному уст ройству одновременно включен только один канал,

В режиме с запоминанием на втором входе элемента И 14-1-14-Р сброса также появляется единичный сигнал в момент пропадания сигнала выбора дав ного блока коммутации Р, Но благодаря присутствию сигнала Работа с памятью на объединенных первых входах Элементов И 14-1-14-Р сброса поддерживает ся нулевой сигяал. Он запрещает возникновение сигнала сброса регистров в мо- мент пропадания сигнала выбсфа.

При выборе канала в каждом блоке коммутации и записи его в регистр М каналов в группе и регистр М групп каналов, соответствующие этому блоку коммутации Р регистры всех остальных блоков коммутации, в которых каналы были выбраны, остаются несброшенными, а . выбраннью ранее каналы, лвключенными до момента выбора в этих блоках коммутации каких-4шбо кругих. каналов.

Таким обрезом, режим работы с аапо минанием дает возможность включить од 1О1 еменно Р каналов по числу блоков

коммутации JP от одного устройства управления, содержащего генератор тактовых импульсов, счетчтш и дешифраторы номера канала и запомянаюпще регистрьи

формула изобретения

Коммутатор, содержащий последовательно соединенные счетчик и деитфратор каналов в группе, счетчик и дешифратор М групп каналов, задающий генератор и элемент И адресного режима, отличающийся тем, что, с целью повышения скорости опроса каналов в ад- ресном режиме, введены последовательно соединенные счетчик и дешифратор Р / блоков коммуташт, каждый из которых содержит М групп каналов, Р запоминающ регистров N каналов в группе по числу Р блоков коммутации, Р запоминающих регистров М зтзупп каналов, запоминающий регистр Р блоков коммутации, Р элементов И записи, Р элементов И сброса Р инвертеров и блок временной задержки, при этом задомина.ющие регистры Ы каналов в группе, М групп каналов и Р блоков коммутации последовательно соединены с соответствующими дешифраторами, одни входы Р элементов И записи объединены между собой и соединены с выходом блока временной задержки, другой вход с одним из выходов дешифратора Р блоксв коммутацииот 1-го до Р и входом одного из Р инверторов, а выходы,- с входами записи соответст- Е1ую11шх запоминающих регистров J/ каналов в группе и М групп каналов от l-ix до Р и Р входами згшиси запоминающего регистра Р блоков коммутации, выходы Р инверторов соединены с одним входом Р элементов И сброса, другие входы которых объединены, между собой и соединены с шиной признака Работа с памятью, а выходы соединены с -входами сброса соответствующих запоминающих регистров N каналов в группе и М групп каналов от 1-го до Р и Р входами сброса запоминающего регистра Р блоков коммуташш, выход задающего генератора соединен с одним входом элемента И адресного режима, другой вход которого соединен с шиной признака адресного реЖ11ма, а выход с объединенными входами записи счетчиков N каналов в группе, М групп каналов Jr Р блоков коммутации и входом блока временной задержки.

Источники информации, йринятые во вйимание при экспертизе

1 Долгов В. А., Гонестас Э. Ю. Коммутирующие устройства автоматических систем контроля, М,, Энергия, 1969, с. 7О-74, рис, 47.5О,

2i Коммутатор ишьа Ф7100. .ТУ-25-04-г46О-76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1981 |

|

SU976499A1 |

| Коммутатор | 1981 |

|

SU974579A1 |

| УСТРОЙСТВО АВТОВЫБОРА ДИСКРЕТНОГО КАНАЛА | 2011 |

|

RU2488222C1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Коммутатор | 1981 |

|

SU1001470A1 |

| Матричный коммутатор | 1988 |

|

SU1596342A1 |

| Коммутатор | 1980 |

|

SU884138A1 |

| Коммутатор | 1985 |

|

SU1265990A2 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

Авторы

Даты

1982-11-23—Публикация

1981-05-04—Подача