Изобретение относится к а зтоматике н цифровой вычислительной тгхнике и может быть использовано при построении преобразоватеглей для согласования системы программного управления с внешними устройствами, например с датчиком обратной связи, с шаговьм приводом, с устройствами индикации и т.д., работаюнщки в различных системах представления информации ,

Цель изобретения повьпиение быстродействия.

На фиг. 1 приведена структурная схема преобразователя, на фиг. 2 структурная схема сравнения.

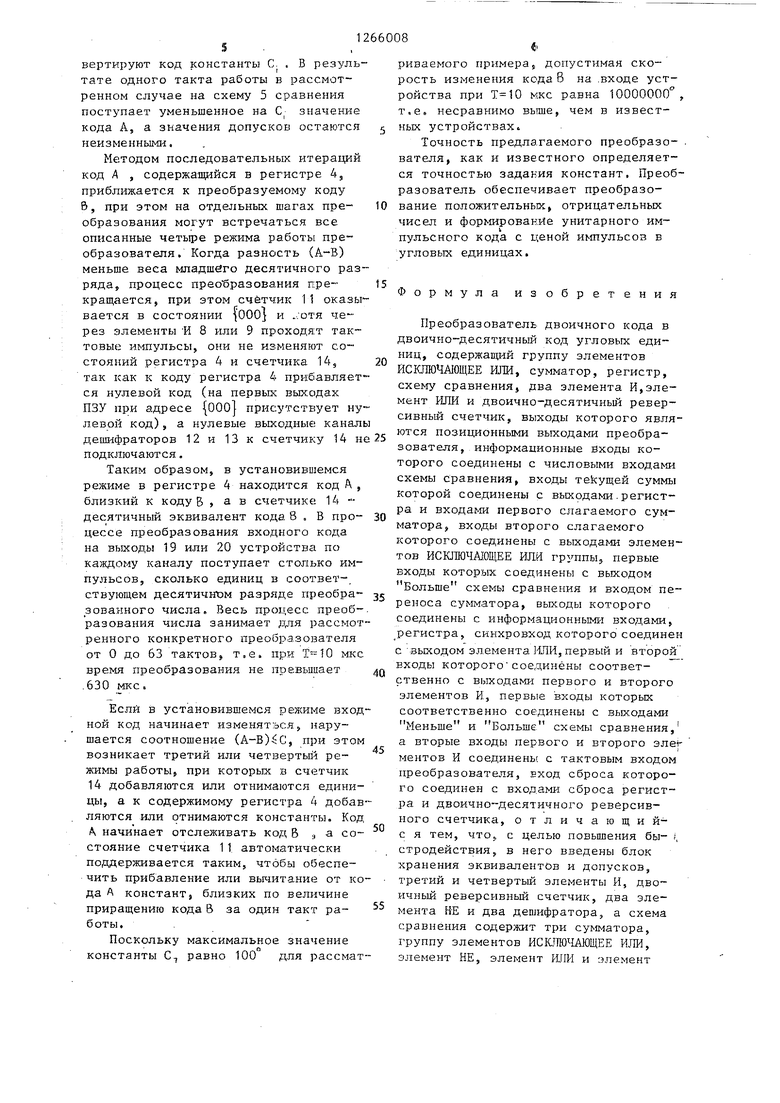

Преобразователь содержит Сфиг.1) блок 1 хранения эквивалентов и допусков, выполненный ка ПЗУ, группу элементов ИСКЛЮЧАЮЩЕЕ ИПИ 2, сумматор 3 регистр 4, схему 5 сравнения, элементы И 6-9, элемент ИЛИ 10, двоичный реверсивный счетчик 11, дешифратор 12 и 13, двоично деся1тичный реверсивный счетчик 14, информационные входы 15 преобразователя, тактовый вход 16 преобразователя, вход 17 сброса преобразователя, выходы 18 позиционного кода преобразователя, выходы 19 положительных чисел унитарного кода преобразователя, выходы 20 отрицательных чисел унитарного кода преобразователя, элементы, НЕ 21 и 22 и вход 23 логичес,кой единицы. Схема 5 сравнения содернжт (фиг.2 группу элементов ИСКШОЧ/ШЩЕЕ ИЛИ 24s элемент НЕ 25, элемент ИЛИ 26, элемент 27 запрета, входы 28 текущей суммы, числовые входы 29, входы 30 эквивалента, входы 31 допуска, выход Меньгае 32, выход Больше 33, выход Больше допуска 34, выход Мень ше допуска 35 и сумматоры 36-38. Преобразователь работает следующи образом. На входы 15 преобразователя подается двоичный п-разрядный код преоб разуемого числа в виде высоких и низких уровней напряжения. Изменение входно го кода должно происходить синхронно со срезом тактового сигнала, либо при паузе тактового сигнала, присутствующего на входе 16. Тактовый сигнал представляет последовательность импульсов с периодом Т. В ПЗУ записываются двоичные п-разрядные коды констант с,-с,, равных весам разрядов двоично-десятичкого кода. При

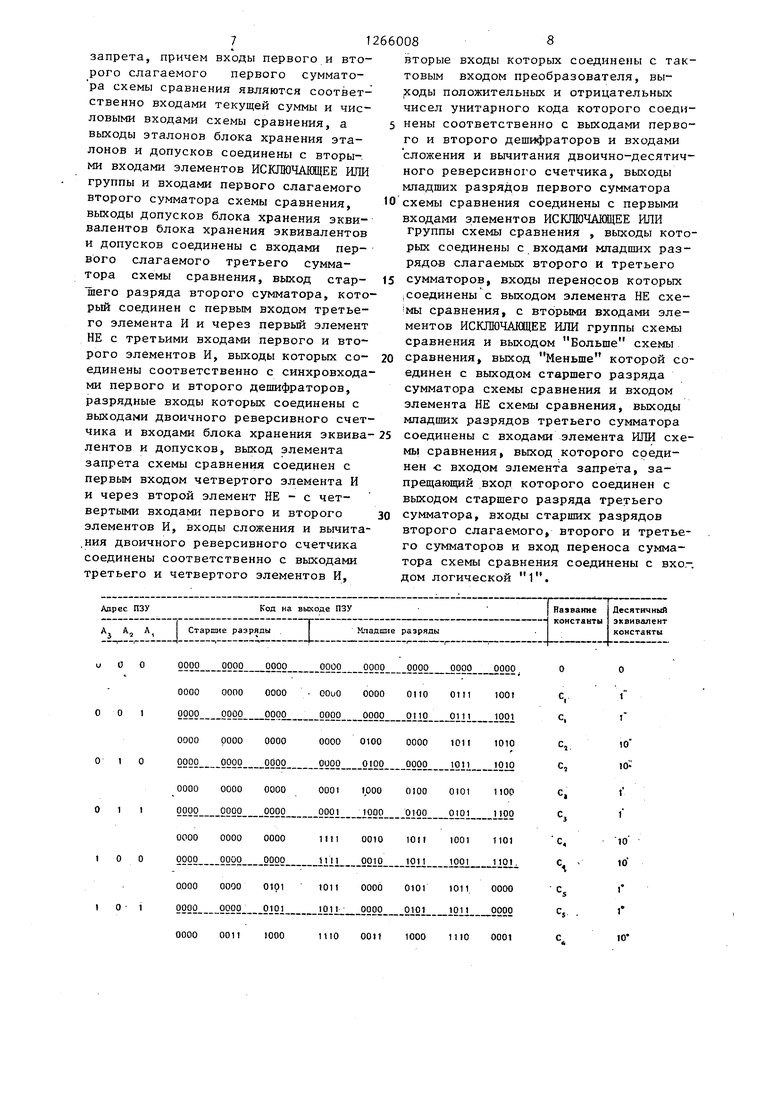

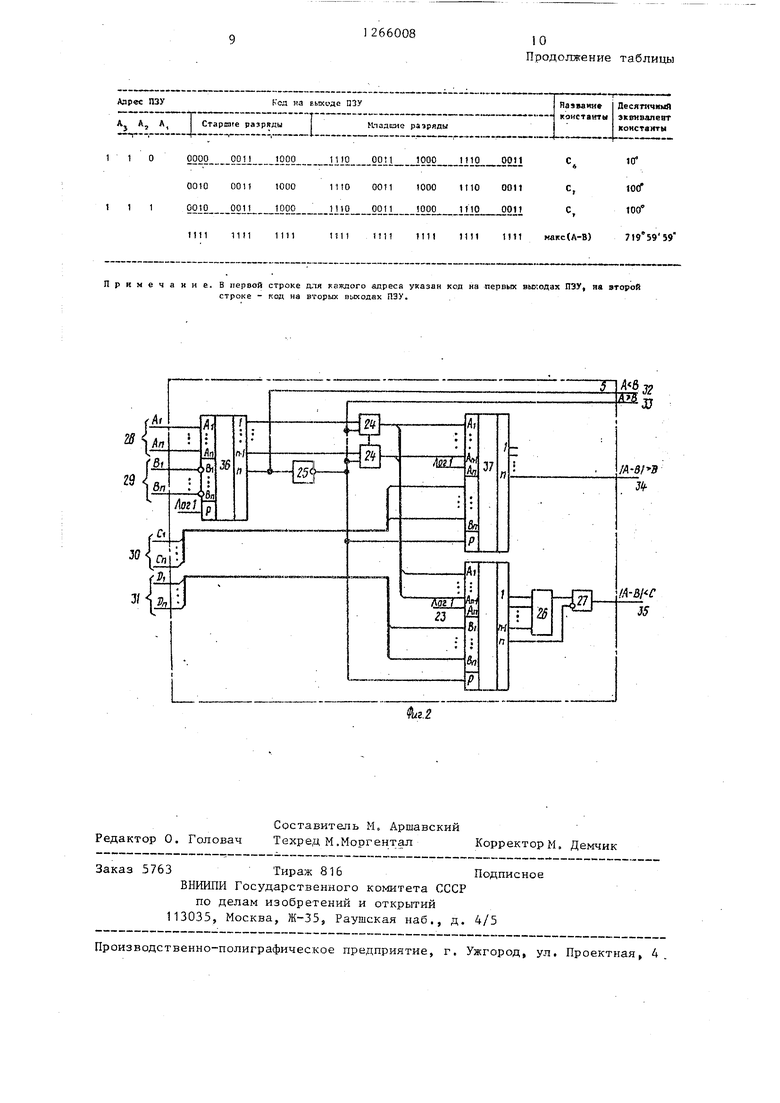

адресе ПЗУ |000 на перпьгх выходах присутствует нулевой код, а на вторых код константы С . При адресе ПЗУ {OOl} на первых выходах присутствует код константы С „ а на вторых - С.

Г 1

и т.д. -При адресе {1,1,15 на первых выходах присутствует код, константы С, а на вторых код, равный разности между допустимыми максимальными и минимальными значениями входного кода.

В таблице приведены значения записанных в ПЗУ 32-х разрядных кодов констант для преобразования 32 разрядного двоичного кода в двоичнодесятичный код градусов, минут, секунд. Старый разряд кода констант имеет вес 360 С. Старший разряд входного кода является знаковым, а предстарший имеет вес 180 , т.е. диапазон преобразуемых кодов +359° 59 59. Регистр 4 выполняется на триггерах, срабатывающих по заднему фронту стробирующего импульса на синхровходе. Сумматор 3 и регистр 4, замкнутые в кольцо, образуют накапливающий сумматор. Схема сравнения предназначена для сравнения кодов А и В без допусков и с, допусками и вьщает следующие сигналы: Больше, если А /В, Меньше если А , Больше допуска, если (А-В)D, где D - верхняя граница допуска, поступающая в виде двоичного кода с ПЗУ, Меньше допуска, если (А-В) iC, где С - нижняя граница допуска, поступающая в виде двоичного кода с ПЗУ. Сум.1атор 37 выполняет операцию вы штания кода разности из кода D, а сумматор 38 - кода разности из кода С. Если код разности отрицательный, то он поступает на входы сумматоров 37 и 38 без изменений, а если положительный, то осуществляется его преобразование в дополнительный отрицательньй код, путем подачи единичного сигнала с элемента НЕ 25 на входы переносов сумматоров 37 и 38 и на вторые входы элементов ИСКГПОЧАЖЦЕЕ ШШ 24, , которые инвертируют код разности. При (А-В) D разность на выходе сумматора 37 отрицательная, а единичный старш1;1й знаковый разряд кода разности поступает на выход Больше допуска. При 3(А-В)С разность на выходе сумматора 38 положительная и отличная от нулевого значения, при этом на выходе элемента 1ШИ 26 устанавливается единичный сигнал, а в старшем разряде разности нулевой, которые формируют на выходе элемента 27 сигнал Меньше допуска. Двоичный счетчик 11 (фиг.1) срабатывает по заднему фронту счетного импульса Двоично-десятичный счетчик 14 состоит из декад и секстад с реверсивными входа1 м, а его структура опреде ляется видом угловых единиц, двоично-десятичный код которых необходимо получить на выходе 18: код градусов, минут, секунд или код градусов, долей градусов, или код угла в тысячньпс делениях угломера или код угл в радианах и долях радиана. При этом в зависимости от выбранного способа представления отрицательных углов за висит структура счетчика. В предлагаемом устройстве исполь зуется дополнительный код для представления отрицательных углов, напри мер, код, равный -26°, на счетчике в виде кода 360 - 26 представляется . 334° . После включения питания на вход 1 преобразователя подается сигнал Сброс, устанавливающий нулевые коды в счетчике 14 и регистре 4. Состо яние счетчика 11 в момент включения питания может установиться произволь ным, при этом из ПЗУ выбираются константы С. и С-, , где i - состояние счетчика 11, На схему 5 сравнения поступают четыре двоичных кода: А - на входы А,...А код А с выхода регистра 4, - на входы В Bf преобразуемый код в, С - на входы С -1 КОД констан ты С. , Р- на входы D, .,.Ц код констан ты C,i . . В зависимости от соотношений указанных кодов могут наблюдаться четыр режима работы преобразователя. При первом режиме когда (А-B)G;, на выходе Больше допуска схемы 5 сравнения устанавливается единичный сигнал, запрещающий работу элементов 8 и 9 и разрешающий прохождение чере элемент И 6 тактового импульса с вхо да 16 на вход Т счетчика 11. Содержимое счетчика 11 увеличивается на единицу, при этом на схему 5 сравнения поступают новые значения допус ков, равные константам С 1+а При втором режиме когда (A-B)iCj , на выходе Меньше допуска схемы 5 сравнения устанавливается единичный сигнал, запрещающий работу элементов И 8 и 9 и разрешающий прохождение через элемент И 7 тактового импульса с входа 16 на вход Т счетчика 11. Содержимое счетчика 11 уменьшается на единицу, при этом на схему 5 сравнения поступают новые значения допусков, равные константам С. и С;. При третьем режиме когда С /А-В/ , А В, на выходе Меньше 5 сравнения устанавливается единичный сигнал, разрешаюш й работу элементов ИЗ, а на остальных выходах - нулевые сигналы. Тактовый импульс через элемент И 8 и разрешенный 1-й канал дешифратора 12 поступает на i-й десятичный разряд счетчика 14, увеличивая содержимое данного разряда на единицу. Кроме того, импульсньм сигнал с выхода элемента И 8 через элемент ИЛИ 10 подается на синхровход регистра 4, при этом к содержимому регистра 4 с помощью сумматора 3 прибавляется код константы, подаваемый с первых выходов ПЗУ через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 2 на , входы В,-В„ сумматора 3. В результате одного такта работы в рассматриваемом случае на схему 5 сравнения поступает новое увеличенное на С значение кода А , а значения допусков остаются неизменными. При четвертом режиме, когда С; (А-В) С.; , A.B, на выходе Больше схемы 5 сравнения устанавливается единичный сигнал, разрешающий работу элементов И 9, а на остальных выходах - нулевые сигналы. Тактовый импульс через элемент И 9 и разрешенный канал дешифратора 13 поступает йа i-й десятичный разряд счетчика 14, уменьшая содержи мое данного разряда на единицу. Кроме того, импульсный сигнал с ыхода элемента И 9 через элемент ЛИ 10 подается на синхровход регитра 4, при этом отсодержимого егистра 4 с помощью сумматора 3 выитается код константы С; . Преобраование прямого кода константы в доолнительный осуществляется подачей диничного сигнала Больше со схеы 5 сравнения на вход переноса суматора 3 и на вторые входы элеменов ИСКЛЮЧАЮЩЕЕ ИЛИ 2, которые нивертируют код константы С. . В результате одного такта работы в рассмотренном случае на схему 5 сравнения поступает уменьшенное на С значение кода А, а значения допусков остаются неизменньичи. Методом последовательных; итераций код А , содержащийся в регистре 4, приближается к преобразуемому коду В, при этом на отдельных шагах преобразования могут встречаться все описанные четыре режима работы преобразователя. Когда разность (А-В) меньше веса младшбго десятичного раз ряда, процесс преобразования Е;рекращается, при этом счётчик 11 оказы вается в состоянии fOOO и ..отя через элементы И 8 или 9 проходят тактовые импульсы, они не изменяют состояний регистра 4 и счетчика 14, так как к коду регистра 4 прибавляет ся нулевой код (на первых вы ;одах ПЗУ при адресе (ООО присутствует ну левои код), а нулевые выходные канал . г, X тл I дешифраторов 12 и 13 к счетчику 14 н подключаются. Таким образом, в установившемся режиме в регистре 4 находится код А, близкий к коду Б 3 в счетчике 14 десятичный эквивалент кода 8 . В процессе преобразования входного кода на выходы 19 или 20 устройства по каждому каналу поступает столько импульсов, сколько единиц в соответ-, ствующем десятичнх м разряде преобразованного числа. Весь процесс преобразования числа занимает р;,пя рассмот ренного конкретного преобра.зователя от О до 63 тактовJ т.е. при мкс время преобразования не превьпшет .630 МКС. Если в установившемся режиме вход ной код начинает изменяться, иаруШ ается соотношение (А-В)С, при этом возникает третий или четвертьш реж-имы работы при которых в счетчик 14 добавляются или отнимаются единицы, а к содержимому регистра 4 добав ляются или отнимаются константы. Код Л начинает отслеживать код В ,, а состояние счетчика 1 1. автоматически поддерживается таким, чтобы обеспечить прибавление или вычитание от ко да А констант} близких по величине приращению кода В за один такт работы. Поскольку максимальное значение константы С-, равно 100° для рассмат риваемого примера допустимая скорость изменения кода В на .входе устройства при МКС равна 10000000°, т,е несравнимо выше, чем в известных устройствах Точность предлагаемого преобразо- . вателя, как и известного определяется точностью задания констант. Преобразователь обеспечивает преобразование положительных, отрицательных чисел и формирование унитарного импульсного кода с ценой иьшульсоз в угловых единицах. Формула изобретения Преобразователь двоичного кода в двоично-десятичный код угловых единиц, содержащий группу злементов ИСКЛЮЧАЮЩЕЕ ИЛИ, сумматор, регистр, схему сравнения, два элемента И,элемент ИЛИ и двоично-десятичньй реверсивный счетчик, выходы которого являются позиционными выходами преобра v зователя, информационные Входы которого соединены с числовыми входами схемы сравнения, входы тekyщeй суммы которой соединены с выходами.регистра и входагда первого слагаемого сумматора, входы второго слагаемого которого соед,инены с выходами элементов ИСЮтаЧАЮЩЕЕ ИЛИ группы, первые входы которых: соединены с выходом Больше схемы сравнения и входом переноса сумматора, выходы которого соединены с инфopмaциoнньLми входами, регистра5 синхровход которого соединен с выходом элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и второго элементов И, первые входы которых соответственно соединены с выходами Меньше и Больше схемы сравнения, а вторые входы первого и второго элег ментов И соединень. с тактовым входом преобразователя, ЕХОД сброса которого соединен с входами сброса регистра и двоично-десятичного реверсивного счетчика, отличающийс я тем, что,, с целью повьш ения бы- ;, стродействия, в него введены блок хранения эквивалентов и допусков, третий и четвертый элементы И, двоичный реверсивный счетчик, два элемента НЕ и два дешифратора, а схема сравнения содержит три сумматора, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ, элемент ИЛИ и элемент 71 запрета, причем входы первого и второго слагаемого первого сумматора схемы сравнения являются соответственно входами текущей суммы и числовыми входами схемы сравнения, а выходы эталонов блока хранения эталонов и допусков соединены с вторыми входами элементов ИСКПЮЧАЩЕЕ ИЛИ группы и входами первого слагаемого второго сумматора схемы сравнения, выходы допусков блока хранения эквивалентов блока хранения эквивалентов и допусков соединены с входами первого слагаемого третьего сумматора схемы сравнения, выход стар шего разряда второго сумматора, кото рый соединен с первым входом третьего элемента И и через первьй элемент НЕ с третьими входами первого и второго элементов И, выходы которых соединены соответственно с синхровхода ми первого и второго дешифраторов, разрядные входы которых соединены с выходами двоичного реверсивного счет чика и входами блока хранения эквива лентов и допусков, выход элемента запрета схемы сравнения соединен с первым входом четвертого элемента И и через второй элемент НЕ - с четвертыми входами первого и второго элементов И, входы сложения и вычита ,ния двоичного реверсивного счетчика соединены соответственно с выходами третьего и четвертого элементов И, 088 вторые входы которых соединены с тактовым входом преобразователя, вырсоды положительных и отрицательных чисел унитарного кода которого соединены соответственно с выходами первого и второго дешифраторов и входами сложения и вычитания двоично-десятичного реверсивного счетчика, выходы младших разрядов первого сумматора схемы сравнения соединены с первыми входами элементов ИСКПЮЧАЩЕЕ ИЛИ группы схемы сравнения , выходы которых соединены с входами младших разрядов слагаемых второго и третьего сумматоров, входы переносов которых I соединены с выходом элемента НЕ сравнения, с вторыми входами элементов ИСКЛЮЧАКЩЕЕ ИЛИ группы схемы сравнения и выходом Больше схемы сравнения, выход Меньше которой соединен с выходом старшего разряда сумматора схемы сравнения и входом элемента НЕ схемы сравнения, выходы младших разрядов третьего сумматора соединены с входами элемента ИЛИ схемы сравнения, выход которого соединен с входом элемента запрета, запрещающий вход которого соединен с выходом старшего разряда третьего сумматора, входы старших разрядов второго слагаемого, второго и третьего сумматоров и вход переноса сумматора схемы сравнения соединены с входом логической 1.

266008

10

Продолжение таблицы

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано при построении преобразователей для согласования системы программного управления с внешними устройствами, например с датчиком обратной связи, с шаговым приводом, с устройствами индикации и т.д., работающими в различных системах представления информации. Цель изобретения - повышение быстродействия, что достигается благодаря введению в преобразователь блока 1 хранения эквивалентов и допусков двух элемейтов И 3,9,двоичного реверсивного счетчика 14,двух элементов НЕ 21,22 и двух дешифраторов 12,13 с соответствующими функциональными S связями. Преобразователь обеспечива(Л ет преобразование положительных, отрицательных чисел и формирование уни -( тарного импульсного кода с ценой им в угловых единицах. 2 ил, пульсов 1 табл. KD О 05 00

Примечание. В первой строке гия каждого адреса указан коя на первых ПЗУ, на второй строке - код на вторых выходах ПЗУ.

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1980 |

|

SU970354A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1983 |

|

SU1124282A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-23—Публикация

1984-12-17—Подача