i W

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано в устройствах обработки и вывода числовой информации.

Цель изобретения - упрощение преобразователя .

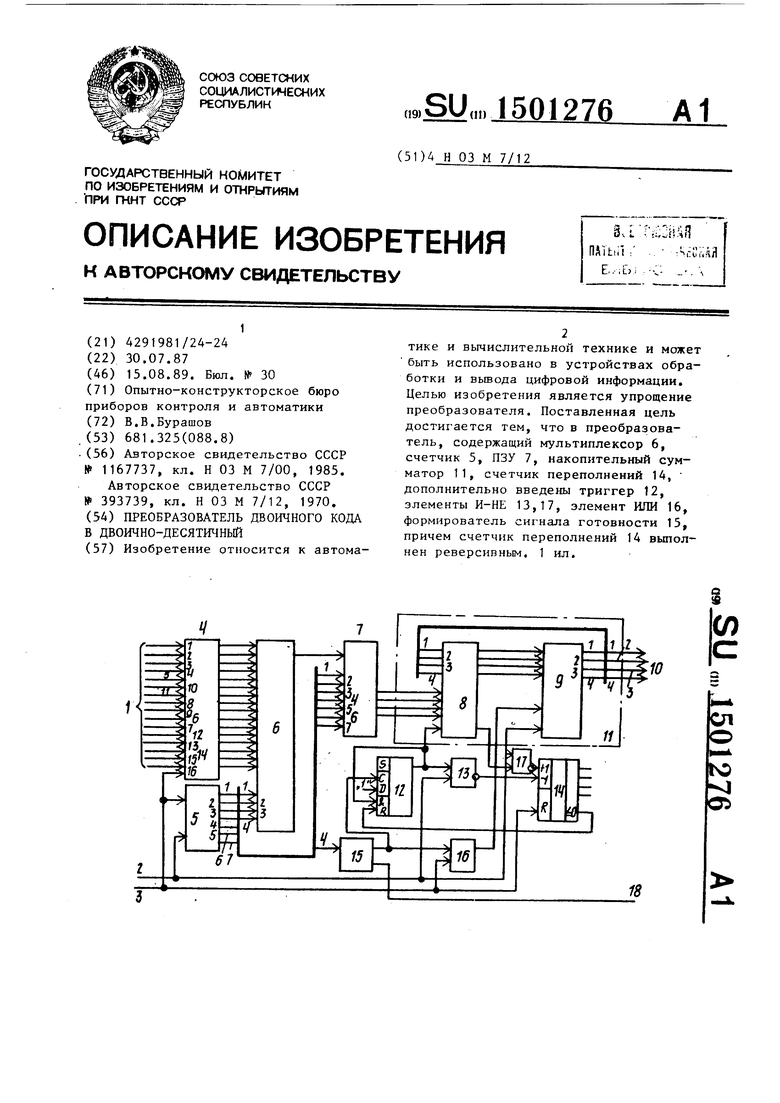

На чертеже приведена структурная схема преобразователя.

Устройство содержит информационные Ьходы 1 преобразователя, такто- вьй вход 2 преобразопателя, установочный вход 3 преобразователя, регистр 4, счетчик 5, ко -1мутатор 6, выполненный на мультиплексоре, формирователь 7 эталонного кода, выполненный на ПЗУ, сумматор 8, регистр

9сумматора, информационные выхода

10преобразователя, накопительный сумматор 11, образованный из сумматора 8 и регистра 9 сумматора, триггер 12, элемент И-НЕ 13, счетчик 14 переполнений, формирователь 15 сигнала готовности, выполненный на од- новибраторе, элемент ИЛИ 16, элемент И-НЕ 17 и выход 18 готовности преобразователя.

Преобразователь работает следующим образом.

Импульс начальной установки, поступающий на вход 3, производит запись входного двоичного кода с информационных входов 1 в регистр 4 и установку в нулевое состояние счетчика 5, регистра 9, сумматора 11, триггера 1 2 и счетчика 14 переполнений. По переднему фронту тактовых импульсов, поступающих на вход 2, происходит запись выходно1 о кода сумматора 8 в регистр 9, а по заднему фронту этих импульсов - изменение состояния счетчика 5 импульсов на единицу. Код младших разрядов 1-4 с выхода счетчика 5 задает адрес ячейки ПЗУ 7, Б которой хранится двоично-десятич- Hbtfi эквивалент единицы соответствующего разряда входного двоичног о числа, появившегося на выходе мультиплексора 6. Наличие 1 в этом разряде является условием появления кода эквивалента на выходах ПЗУ 7, О в соответствующем разряде входного двоичного числа блокирует ПЗУ либо по входу Выборка кристалла, либо по старшему разря ду адресной шины ПЗУ, задавая область, в которой во всех ячейках записаны нули. Двоично-десятичный сумматор 8 служит

5

0

5

0

5

0

5

0

5

для суммирования выхохиюго кода ПЗУ 7 с содержим1)м регистра 9 сумматора на также преобразования. Таким образом, к концу цикла преобразования, длительность которого опре- д« ляется числом разрядов входного двоичного числа, на информационных выходах 10 формируется число, равное сумме всех единичных тетрад двоично-десятичных эквивалентов входного двоич}1ого числа. На выходе формирователя 15 образуется сигнал готовности декады, который может быть использован для разрешения приема кода единичной тетрады двоично-десятичного числа оконечным устройством. По заднему фронту этого сигнала, прошедшего через элемент ИЛИ 16, регистр 9 сумматора рбнуляется, после чего он готов к преобразованию следующей декады.

Единицы переноса, появившиеся в результате суммирования эквивалентов единиц двоично-десятичного числа, подсчитываются счетчиками 14 переполнений.

Следующий цикл преобразования аналогичен описанному и отличается тем, что выходными разрядами 5-7 счетчика 5 задаются области адресов ячеек ПЗУ 7, в которых хранятся двоично-десятичные эквиваленты десятков, сотен, тысяч, десятков тысяч соответствующих разрядов входного двоичного числа, а также добавлением к сумме числа единиц переноса, появившихся в результате суммирования в предыдущем цикле.

В этом -случае счетчик 14 работает следующим образом.

Сигналом готовности с выхода формирователя 15 триггер 12 устанавливается в единичное состояние и разрешает прохождение тактовых импульсов с входа 2 через элемент И-НЕ 13 на вычитающий вход счетчика 14, импульс с выхода обнуления счетчика 14 устанавливает триггер 12 в нулевое состояние, в результате чего элемент И-НЕ 13 закрывается и запрещает прохождение тактовых импульсов на вычитающий вход счетчика 14. Таким образом, пока триггер 12 находится в единичном состоянии, по каждому такту осуществляется суммирование единиц переноса из младшей декады в старшую.

Число циклов преобразования определяется разрядностью входной инфор5I 50 1 2

мации и равно числу дноичпсм-десятич- ныхдекад пресОратораиного дпоичисл о числа, фи преобразовании 16-разряд,- ного двоичного кола оно равно пяти.

Формула и 3 t) б р е т е н и я

Преобразопатсль дг(тич11ог(5 кода в двоично-десятичный, содержащий ком.мутатор, формирователь эталонного кода, накопительный сумматор, счетчик переполнений и счетчик, выходы которого соединены с адресными входами формирователя эталонного кода, информационный вход которого соедине с выходом коммутатора, а выходы формирователя эталонного кода соединены с информационными входами накопительного сумматора, разрядные выходы которого соединены с информационными выходами преобразователя, тактовый вход которого соединен с тактовыми входами накопительного сумматора и счетчика, выходы младшей группы разрядов которого соединены с управляющими входами коммутатора, а вход

сброса счетчика соединен с установочным входом преобразователя и входом сброса счетчика переполнений, о т

лью упрощения преобразователя, он содержит регистр, триггер, формирователь сигнала готовности, первый и второй элементы И-НЕ и элемент ИЛИ, причем формирователь эталонного кода выполнен на ПЗУ, счетчик переполнений выполнен реверсивным, а коммутатор

o

2

0

5

0

5

766

выполнен на мультиплексоре, информационные входы которого соединены с выходами рет истра, иифетрмационные входы и установочн 1Й вход которого соединены с соответствующими входами преобразователя, выход готовности которого соединен с первым выходом формирователя сигнала готовности, второй выход которого соединен с первым входом элемента ИПИ и с синхровходом триггера, выход которого соединен с входом переноса накопительного сумматора, первым входом сброса триггера и первым входом первого элемента И- НЕ, второй вход которого соединен с тактовым входом преобразователя, а выход первого элемента И-НЕ соединен с входом декремента счетчика переполнений, вход инкремента которого соединен с выходом второго элемента И-НЕ, первый вход которого соединен с выходом переполнений накопительного сумматора, а второй вход второго элемента И-НЕ соединен с тактовым входом преобразователя, вход логической единицы которого соединен с D- входом триггера, второй вход сброса которого соединен с выходом обнуления счетчика переполнений, выход четвертого разряда счетчика соединен с входом формирователя сигнала готовности, установочный вход преобразователя соединен с втopы ; входом элемента ИЛИ, выход которого соединен со входом сброса накопительного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| Преобразователь двоичных кодов угла и дальности в двоично-десятичные коды | 1987 |

|

SU1432782A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1986 |

|

SU1349008A2 |

| Преобразователь двоичного кода в двоично-десятичный код градусов, минут, секунд | 1978 |

|

SU780000A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах обработки и вывода цифровой информации. Целью изобретения является упрощение преобразователя. Поставленная цель достигается тем, что в преобразователь, содержащий мультиплексор 6, счетчик 5, ПЗУ 7, накопительный сумматор 11, счетчик переполнений 14, дополнительно введены триггер 12, элементы И-НЕ 13,17, элемент ИЛИ 16, формирователь сигнала готовности 15, причем счетчик переполнений 14 выполнен ревирсивным. 1 ил.

Авторы

Даты

1989-08-15—Публикация

1987-07-30—Подача