Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано в измерительных и управляющих системах.

Цель изобретения - повьшение быстродействия преобразователя при преобразовании группы кодов и расширение его функциональных возможностей путем обеспечения преобразования в коды различных весомозначных систем счисления.

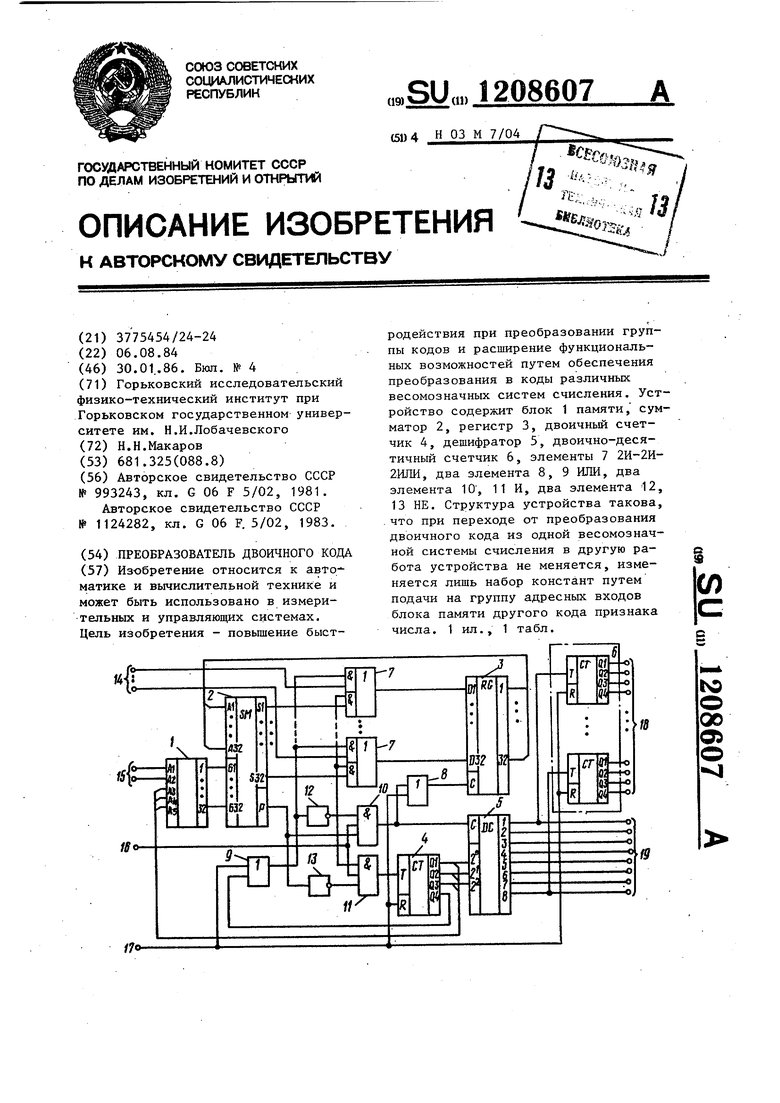

На чертеже представлена функциональная схема преобразователя двоичных кодов.

Преобразователь содержит блок 1 памяти,сумматор 2, регистр 3, двоичный счетчик 4, дешифратор 5, двоично-десятичный счетчик 6, элементы 7 2И-2И-2ИЛИ, первый и второй элементы 8, 9 ИЛИ, первый и второй элементы 10, 11 И, первый и второй элементы 12, 13 НЕ, информационные входы 14, управляющие входы 15, тактовый вход 16, вход 17 сброса, а также первые и вторые выходы 18, 19

Выходы сумматора 2 соединены с первыми входами соответствующих элементов 7 2И-2И-2ИЛИ, вторые входы которых являются информационными входами 14 устройства, а выходы подключены к соответствующим информационным входам регистра 3, выходы которого соединены с соответствующими первыми входами сумматора 2, вторые входы которого соединены с выходами блока 1 .памяти, пер-вые адресные входы которого являются управляющими входами 15 устройства. Тактовый вход 16 устройства соеди- нен с первыми входами элементов 10, 11 И, вторые входы которых объединены с третьими входами элементов 7 2И 2И-2ИЛИ и подключены к выходу первого элемента 12 НЕ, вход которого объединен с четвертыми входами элементов 7 2И-2И-2ИЛИ и подключен к выходу второго элемента 9 ИЛИ. Выход переноса сумматора 2 соединен с третьим входом первого элемен- , та 10 И и через второй элемент 13 НЕ с третьим входом второго элемента 11 И, выход которого подключен к счетному входу двоичного счетчика 4. Выход первого элемента 10 И соединен с тактовым входом дешифратора 5 и первым входом первого элемента 8 ИЛИ, второй вход которого

объединен с первым входом второго элемента 9 ИЛИ и входами обнуления счетчиков 4, 5 и подключен к входу 17 сброса. Второй вход второго элемента 9 ИЛИ соединен с выходом старшего разряда двоичного счетчика 4, выходы остальных разрядов которого подключены к вторым адресным входам блока 1 памяти и входам дешифратора 5, выходы которого, являющиеся вторыми выходами 19 устройства, подключены к соответствующим счетным входам двоично-десятичного счетчика 6, выходы которого являются первыми выходами 18 устройства.

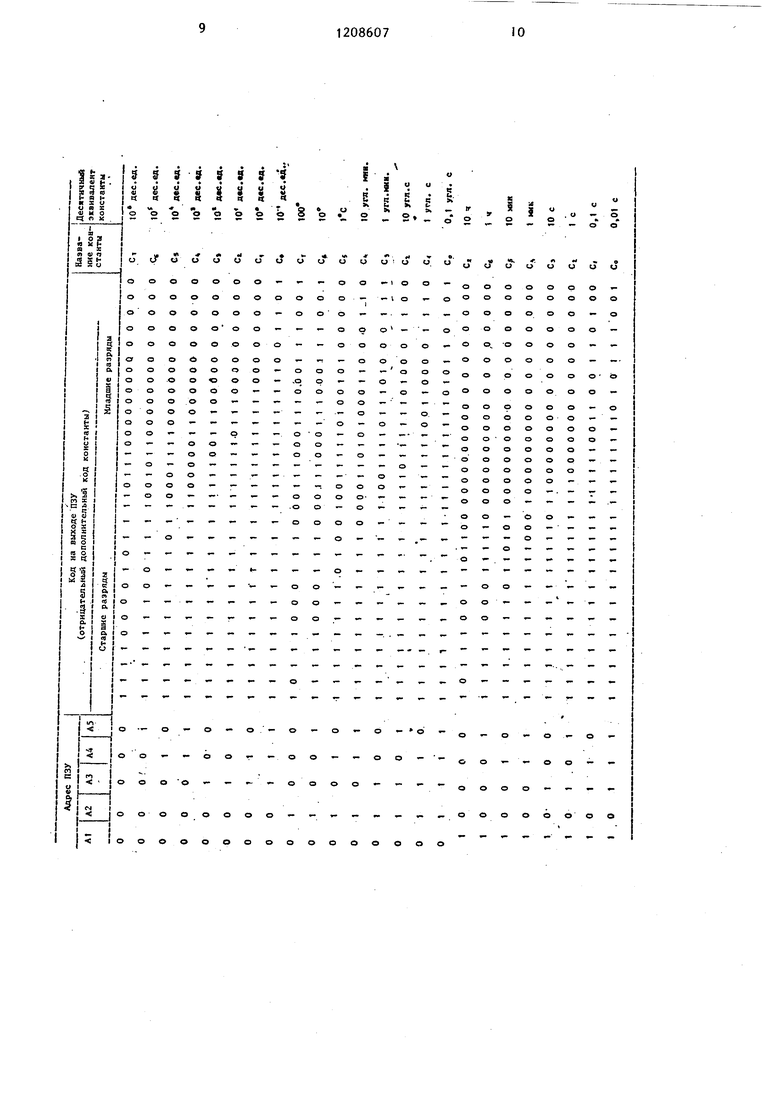

На вход 14 преобразователя подается двоичный N-разрядный код преобразуемого числа, на вход 15 - двоичньй М-разрядный код управления, а на вход 16 - последовательность тактовых импульсов с периодом Т. Сумматор 2 и регистр 3 имеют по N разрядов, двоичный счетчик 4 - т+1 разрядов, двоично-десятичный счетчик 6 содержит 2 тетрад, каждая из которых является 4-разрядным двоичным счетчиком. ДешифратЬр 5 имеет m входов и 2 выходов и выполнен с синхро- вХодом. Регистр 3 и счетчик 4 выполнены на триггерах, срабатывающих по заднему фронту входных управляющих сигналов. Блок 1 памяти представляет собой постоянное запоминающее устройство ( ПЗУ) и имеет М +т входов и выходов. В нем записано двоичных -разрядных кодов, соответствующих константам, необходи- MbjM для работы преобразователя. Константы разбиваются на 2 групп по 2 констднт в каждой. Число групп определяет число различных весомозначных систем счисления, в которые может быть преобразовано двоичное число, а число констант 2 - число разрядов весомозначной системы. Константы GO ... равны весам весомозначной системы. В ПЗУ записаны двоичные дополнительные коды отрицательных значений констант. Для приведенного примера выполнения устройства , , . Устройство обеспечивает преобразование двоичных чисел в десятичную систему счисления с весом 9-го разряда двоичного кода, равным 1 десятичной единице, в десятично-шестидесятиричную систему (в код угловых единиц: градусы, угловые минуты.

угловые секунды) с весом старшего 32-го разряда двоичного кода равным 180 , десятично-шестидесятиричную

систему (в код временных единиц: ч асы, минуты, секунды, десятые и сотые доли секунд) с весом 16 разряда равным ,1 с.

В таблице приведены значения двоичных кодов, записанных в ПЗУ, и соответствующие им веса разрядов весомозначной системы для трех видов преобразования.

Преобразователь двоичных кодов работает следующим образом.

После включения питания состояния регистра 3 и счетчика 6 могут быть произвольными, а состояние счетчика 4 устанавливается автоматически таким, что на выходе старшего разряда присутствует единичный сигнал. Если при включении питания старший разряд счетчика 4 устанавливается в нуль, то при отсутствии сигнала Сброс на входе 17 происходит досчет счетчика 4 до состояния, при котором на выходе старшего разряда появляется единичный сигнал.

Этот единичный сигнал, проходя через элемен 9 ИЛИ, разрешает работу верхних по чертежу элементов совпадения в элементах V 2И-2И-2ИЛИ а после инвертирования элементом 12 НЕ запрещает прохождение такто импульсов через элементы 10, 11 И.

Запуск преобразователя производится подачей на вход 17 сигнала Сброс, на входы 14 - двоичного кода преобразуемого числа, а на входы 15 - двоичного кода управления (признака числа). Сигнал Сброс, проходя через элемент 8 ИЛИ, записывает в регистр 3 (двоичный код преобразуемого числа и сбрасывает счетчики 4 и 6 в нулевые состояния, а признак числа, присутствующий в течение всего цикла преобразования, подается на первые адресные входы блока 1 памяти, обеспечивая выбор группы констант из ПЗУ для заданного вида преобразования .

После окончания сигнала Сброс на выходах счетчиков 4 и 6 устанавливаются нулевые сигналы. На выходе элемента 9 ИЛИ устанавливается нулевой сигнал, запрещающий работу верхних по чертежу элементов совпадения в элементах 7 2И-2И-2ИЛИ, а

208607 .

на выходе элемента 12 НЕ устанавли- : вается единичный сигнал, разрешающий i работу элементов 10, 11 И и нижних по чертежу элементов совпадения в элементах 2И-2И-2ИЛИ, обеспечивающих связь выходов сумматора 2 с входами регистра 3. На вторые адресные входы блока 1 памяти со счетчика 4 подается код 000, выбирающий код константы С для заданного вида преобразования . Отрицательный дополнительный код константы С поступает на сумматор 2, на другие входы которого подается с выхода регистра 3 15 двоичный код АО преобразуемого числа. Сумматор формирует код А,

10

0

5

0

АО т Р этом, если разность А, больше или равна нулю, на выходе переноса сумматора 2 устанавливается единичный сигнал, если А меньше нуля - нулевой сигнал. Единичный сигнал переноса разрешает работу элемента 10 И, через которьш проходит тактовый импульс с входа 16 преобразователя. Импульс с выхода первого элемента 10 И, проходя через элемент 8 ИЛИ, записывает в регистр 3 код разности А и, проходя через первый канал дешифратора 5, переключает старшую тетраду двоично- десятичного счетчика 6 в состояние 0001. Одновременно с выхода дешифратора 5 импульс поступает на выход 19, с которого снимается унитарный код.

в следующем такте работы сумматор 3 вычисляет разность Aj А - С т . Если на выходе переноса сумматора 2 единичный сигнал, то в ре- . гистр 3 записывается код А, в старшую тетраду двоично-десятичного счетчика 6 добавляется единица, а на выход 19 унитарного кода выдается еще один импульс. Процесс формирования старшего десятичного разряда длится до тех пор, пока на выходе переноса сумматора 2 не появится нулевой сигнал, означающий, что содержимое регистра 3 меньше значения константы С7. При этом разрешается прохождение тактового импульса через I второй элемент 11 И на счетный вход счетчика 4. На выходе счетчика 4 появляется код 0001, который включает второй канал дешифрато- 5 ра 5 и выбирает из ПЗУ код константы Cg. Процесс формирования разрядов двоично-десятичного кода повторяется , при этом счетчик 4 последо0

5

0

вательно проходит состояния от 0000 до 1000, а в ПЗУ производится последовательный перебор всех восьми констант заданного преобразования. Тетрады двоично-десятичного счетчика 6 заполняются импульсами, которою одновременно поступают на выход 19 унитарного кода. В конце преобразования в старшей тетраде двоично-де- сятичного счетчика 6 будет содержаться двоичньй код, равный целому числу констант С в преобразуемом числе, в предстаршей тетраде - двоичный код, равньш целому числу кон- стант Cg в остатке от вычитания констант С из преобразуемого числа и т.д. Код в регистре 3 в процессе преобразования уменьшается, в конце преобразования остается код меньший чем значение константы С. На выход 19 унитарного кода вьщаются импульсы, число которых в каждом канале равно числу единиц соответствующего двоично-десятичного разря- да числа. С переходом счетчика 4 в состояние 1000 процесс преобразования заканчивается, при этом единичный сигнал со старшего разряда счетчика 4, проходя через эле- мент 9 ИЛИ, разрешает работу верхних по чертежу элементов совпадения в элементах 7 2И-2И-2ШШ, обеспечивающих связь информационных входов преобразователя с входами регистра 3. На выходе первого элемента 12 НЕ устанавливается нулевой сигнал, запрещающий работу элементов 10, 11 И и нижних по чертежу элементов совпадения в элементах 7 2И-2И-2ИЛИ. Двоично-десятичньм код, поступающий на выходы 18 преобразователя, сохраняется flo нового цикла преобразования, который наступает с приходом сигнала Сброс, двоичного кода нового преобразуемого числа и его признака.

Структура преобразователя такова, что при переходе от преобразо- вания двоичного кода из одной весо- мозначной системы счисления в другую работа элементов преобразовател не меняется, изменяется лишь набор констант путем подачи на группу адресных входов блока памяти другого кода признака чис ла.

Формула изобретения

Преобразователь двоичного кода, содержащий сумматор, регистр, два элемента НЕ, два элемента И, первый элемент ИЛИ и двоично-десятичный счетчик, выходы которого являются первыми выходами преобразователя, а вход обнуления подключен к входу сброса преобразователя, тактовый вход преобразователя соединен с первыми входами элементов И, вторые входы которых подключены к выходу первого элемента НЕ, выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого подключен к тактовому входу регистра, выходы которого соединены с соответствующими первыми входами сумматора, выход переноса которого через второй элемент НЕ подключен к третьему входу второго элемента И отлич.ающийся тем, что, с целью повышения быстродействия при преобразовании группы кодов и расширения функциональных возможностей путем обеспечения преобразования в коды различных весомозначных систем счисления, в него введены двоичньй счетчик, дешифратор, второй элемент РШИ, элементы 2И-2И-2ИЛИ по числу разрядов сумматора и блок памяти, первые адресные входы которого являются управляющими входами преобразователя, выходы блока памяти соединены с соответствующими вторыми входами сумматора, выходы которого подключены к первым входам соответствующих элементов 2И-2И-2ИЛИ вторые входы которых являются информационными входами преобразователя, выходы подключены к соответствующим информационным входам регистра, третьи входы элементов 2И-2И-2ИЛИ объединены и подключены к выходу первого элемента НЕ, вход которого объединен с четвертыми входами элементов 2И-2И-2ИЛИ и подключен к выходу второго элемента ШШ, первый вход которого объединен с вторым входом первого элемента ИЛИ и входом обнуления двоичного счетчика и подключен к входу сброса преобразователя, второй вход элемента ШШ соединен с выходом старшего разряда двоичного счетчика, счетньй вход которого подключен к выходу второго элемента И,

а выходы разрядов, кроме старшего, подключены к вторым адресным входам блока памяти и входам дешифратора, выходы которого подключены к соответствующим счетным входам двоично-десятичного счетчика и являются вторыми выходами преобразователя, а тактовый вход подключен к выходу первого эле- мента И, третий вход которого соединен с выходом nepeHqpa сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1990 |

|

SU1725399A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU883893A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

Изобретение относится к авто- матике и вычислительной технике и может быть использовано в измерительных и управляющих системах. Цель изобретения - повышение быстродействия при преобразовании группы кодов и расширение функциональных возможностей путем обеспечения преобразования в коды различных весомозначных систем счисления. Устройство содержит блок 1 памяти, сумматор 2, регистр 3, двоичный счетчик 4, дешифратор 5, двоично-десятичный счетчик 6, элементы 7 2И-2И- 2ИЛИ, два злемента 8, 9 ИЛИ, два злемента 10, 11 И, два злемента 12, 13 НЕ. Структура устройства такова, .что при переходе от преобразования двоичного кода из одной весомознач- ной системы счисления в другую работа устройства не меняется, изменяется лишь набор констант путем подачи на группу адресных входов блока памяти другого кода признака числа. 1 ил., 1 табл. (Л 18 (О о 00 Од

| Преобразователь двоичного кода угла в двоично-десятичный код градусов | 1981 |

|

SU993243A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1983 |

|

SU1124282A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-01-30—Публикация

1984-08-06—Подача