ю J:3

J3

f

9

ll

Э

|-t

1 г

s«

(Л

00 00

со сд о сд

15

16

D

с|одержа1ций группу элементов ИСКЛЮЧАЮ- 11|ЕЕ ШШ 1, сумматор 2., регистр.3, с|хему сравнения 4, элементы И 5,6, э лемент ИЛИ 7, двоично-десятичный ре- версивньш счетчик 9, дополнительно

введены коммутатор 14, постоянное поминающее устройство 15, регистр последовательного приближения 16, счетчик 17, одновибратор 18, элемент И 19. 1 табл. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1986 |

|

SU1349008A2 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1983 |

|

SU1124282A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1501276A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1985 |

|

SU1322482A1 |

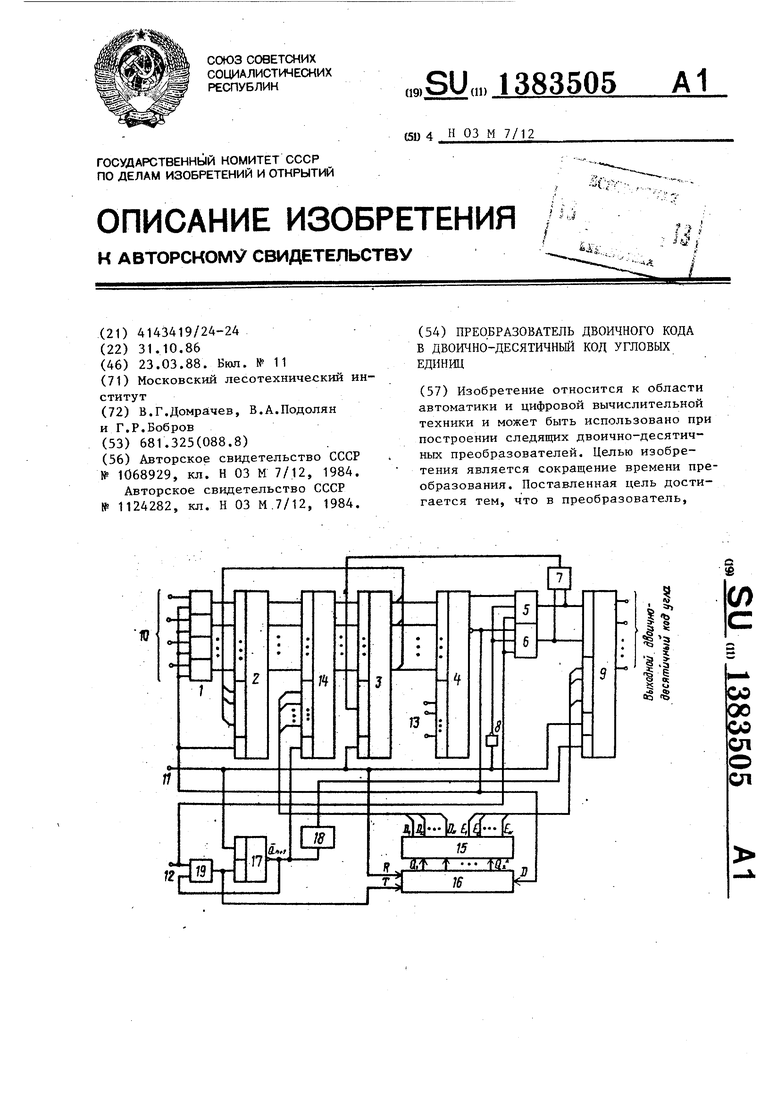

Изобретение относится к области автоматики и цифровой вычислительной техники и может быть использовано при построении следящих двоично-десятичных преобразователей. Целью изобретения является сокращение времени преобразования. Поставленная цель достигается тем, что в преобразователь.

i.1

Изобретение относится к автомати- к|е и вычислительной технике и может б|ыть использовано в системах автоматического управления, сбора информации, к|онтроля производственных процессов д|пя визуальной оценки в угловых еди- постоянных и изменяющихся угло- величин, представляемых в двоич- нЬм цифровом коде.

Целью изобретения является сокра- прение времени готовно.сти преобразователя к ,

На чертеже приведена блок-схема предлагаемого преобразователя.

Преобразователь содержит группу 1 э}лементбв ИСКЛЮЧАЮЩЕЕ ИЛИ, сумматор 2 р|егистр 3, схему 4 сравнения кодов, э лементы И 5 и 6, элемент ИЛИ 7, эле- НЕ 8, двоично-десятичный ревер- с1ивньй счетчик 9, вход 10 коНстанты йреобразователя, вход 11 сброса пре- о бразователя, тактовьй вход 12 пре- фразователя, информа11;ионньй вход 13 феобразователя, коммутатор 14, по- cJTOHHHoe запоминающее устройство 15, р егистр 16 -последовательного прибли- ения, счетчик 17, одновибратор 18, з-лемент И 19.

Для достижения указанной цели в г(редлагаемом преобразователе исполь- дуется комбинированньй алгоритм получения эквивалента входного кода, который начинается п тактами последовательного приближения (поразрядно, начиная со старшего разряда), а про- должается следящим режимом работы до сравнения кодов в схеме 4.

Преобразователь работает следующим образом.

Сигналом по входу .11 сброса, по- данным вследствие включения питания или независимо от этого, устанавлива- «;тся в исходное состояние регистр 3,

а также двоично-десятичный реверсив- ньм счетчик 9, регистр 16 последовательного приближения и счетчик 17. Первый вслед за этим тактовый импульс с входа 12 тактовых импульсов проходит через элемент И 19, поскольку второй его вход подключен к инверсному выходу счетчика 17, находящегося в единичном состоянии. С выхода элемента И 19 тактовый импульс следует на тактовый вход регистра 16 последовательного приближения, на выходах которого устанавливается код 01, . . 1, (см. таблицу), соответствующий первой половине полного угла. Этот код в качестве адреса поступает на постоянное запоминающее устройство 15, где записаны две группы слов: D - коды которых соответствуют двоично-десятичному коду разрядности N угловой меры, Е - коды которых соответствуют двоичному коду разрядности N угловой меры. Код D из постоянно- .го запоминающего устройства через коммутатор 14 поступает на вход регистра 3, откуда импульсом с выхода элемента ИЛИ 7 перезаписывается на первый вход схемы 4 сравнения и на вход сумматора 2. Выход сумматора 2 подключен к второму входу коммутатора 14, который при наличии единичного уровня на выходе счетчика 17 отключает его от входа регистра 3.

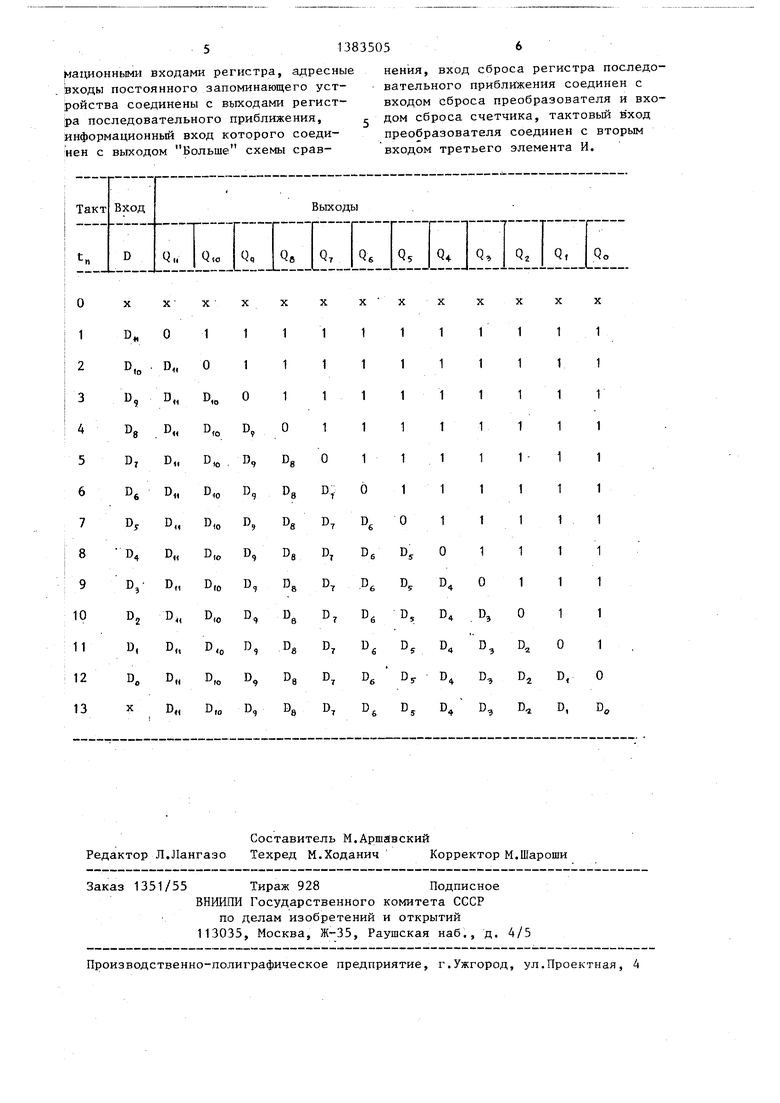

В таблице приведены переходы регистра прследовательного приближения.

На втором выходе схемы 4 сравнения вырабатывается единичньй сигнал, если код на входе 13 больше кода D, и нулевой, если код на входе 13 меньше кода D. Сигнал сравнения записывается в старший разряд регистра 16 последовательного приближения по приходу на его тактовый вход второго тактового импульса (см. табллцу). По второму тактовому .импульсу с входа 12, аналогично описанному, происходит определение квадранта, в котором находится угол, эквйвалеЕТТный входному коду. При этом в регистре 16 формируется два равряда кода D.

По третьему, четвертому и т.д. импульсам определяются октант, шестнадцатая и т.д. части полного угла, в которых находится значение определяемого .угла. При этом на выходах D и Е постоянного запоминающего устройства 15 формируются коды, хранящиеся по адресам, соответствующим указанньм долям полного угла в две- ичном и двоично-десятичном кодах.

Практически нет необходимости. в количестве разрядов, определяемых последовательньм приближением, большим четырех, поэтому целесообразно для управления переходом к следящему режиму работы воспользоваться выходом третьего разряда Q счетчика 17. По приходу с тактового входа 12 пятого тактового импульса на выходе счетчика 17 формируется нулевой сигнал и элемент И 19 закрывается. По нулевому уровню на выходе счетчика 17 коммутатор 14 отключает от входа регистра 3 выход D постоянного запоминающего устройства 15 и подключает выход сумматора 2 к входу регистра 3,

По спаду логического уровня на выходе счетчика 17 однови.братором 18 вырабатывается импульс, управлякнций записью двоично-десятичного кода угловых единиц Е с выхода постоянного запоминающего устройства 15 в двоич но-дееятйчньм реверсивный счетчик 9 по его информационным входам.

Таким образом, блок-схема преобразователя приходит в соответствие, необходимое для работы его в следяще режиме и, начиная с шестого тактовог импульса, преобразователь функционирует в полном соответствии с описанием его работы, приводимым для известного устройства, однако в пределах 1/6 части полного угла. ;

Время, необходимое для вхождения преобразователя в следящий режим в этом случав соответственно в 16 раз меньше, чем на полном угле.

Формула изобретения

Преобразователь двоичного кода в двоично-десятичный код.угловых еди0

5

0

5

0

5

0

5

0

5

ниц, содержащий сумматор, pei-истр, схему сравнения, первый и второй элементы И, элемент ИЛИ, двоично-десятичный реверсивный счетчик, элемент НЕ и группу элементов ИСКЛЮЧАРЦЕЕ Ш1И, первые входы элементов ИСЮ1ЮЧА10ЩЕЕ ИЛИ группы соединены с входом константы преобразователя, вторые входы соединены с выходом Больше схемы сравнения и с входом переноса сумматора, первые входы которого соединены с выходами элементов ИСЮ1ЮЧАЮЩЕЕ ИЛИ группы,, вторые, входы сумматора соединены с выходами регистра и с первыми входами схемы сравнения, вторые входы которой соединены с информационным входом преобразователя, вход сброса которого соединен с входами сброса регистра и двоично-десятичного реверсивного счетчика, выходы которого являются выходами преобразователя, тактовьБ вход которого соединен с первыми входами первого и второго элементов И, вторые, входы которых соединены соответственно с выходами Меньше и Больше схемы сравнения, а третьи входы первого и второго элементов И через элемент НЕ подключены к входу сброса преобразователя, вько- ды первого и второго элементов И соединены соответственно с входами инкремента и декремента двоично-десятичного реверсивного счетчика и к первому и второму входам первого элемента ИЛИ, выход которого соединен с входом записи регистра, отличающийся тем, что, с целью сокращения времени преобразов а.ния, в него введены коммутатор, постоянное запоминающее устройство, одновибра- тор, счетчик, третий элемент И и регистр последовательного прибл11жения, тактовый вход которого соединен с выходом третьего элемента И и с синхро- входом счетчика, выход которого соединен с первым входом третьего элемента И, с управляющим входом коммутатора и через одновибратор с входом записи двоично-десятичного реверсивного счетчика, информационные входы которого подключены к группе выходов двоично-десятичного кода постоянного запоминающего устройства, группа выходов двоичного кода которого соединена с первой группой входов коммутатора, вторая группа входов которого соединена с выходами сумматора, а выходы коммутатора соединены с инфор5 13835056

мационными входами регистра, адресныенения, вход сброса регистра последойходы постоянного запоминающего уст-нательного приближения соединен с

ройства соединены с выходами регист-входом сброса преобразователя и последовательного приближения,г дом сброса счетчика, тактовый йход

информационньш вход которого соеди-преобразователя соединен с вторым

нен с выходом Больше схемы срав-входом третьего элемента И.

| Преобразователь двоичного кода в двоично-десятичный код градусов,минут и секунд | 1982 |

|

SU1068929A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1983 |

|

SU1124282A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-31—Подача