ю

Oi

4

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1981 |

|

SU1086426A1 |

| Вычислительное устройство | 1981 |

|

SU1115047A2 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1053105A1 |

| Оптический модуль для сложения и вычитания | 1990 |

|

SU1775719A1 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU1179369A1 |

| Однородная вычислительная структура | 1985 |

|

SU1251104A1 |

| Однородная вычислительная структура для @ разложения матриц | 1984 |

|

SU1249531A1 |

Изобретение относится к области вычислительной техники, может быть применено в спецпроцессорах или в комплексе с цифровой вычислительной машиной для оперативного вычисления групповой операции и является усовершенствованием известного устройства, описанного в авторском свидетельстве № 1206774. Целью изобретения является расширение функциональных возможностей устройства за счет вычисления частного от деления парных произведений на одно число. Указанная цель достигается за счет того, что в устройство, содержащее сумматоры, коммутаторы, сумматоры по модулю два, элементы НЕ, матрицу элементов И, элементы И, элементы ИЛИ, введес ны дополнительные матрицы элементов И. 1 и л. (Л

К) Изобретение относится к вычислительной технике и может быть применено в спецпроцессорах или в комплек се с цифровой вычислительной машиной для оперативного вычисления групповой операции. По основному авт.свл1Р 1206774 известно множительно-делительное уст ройство содержащее п-1 сумматоров, п-разрядность операндов п-1 групп коммутаторов, первую группу элементов И, первую группу элементов ИЛИ, первую группу элементов запрета, при чем первый информационный вход i-ro коммутатора j-и группы (,..,,п-1; ,...,п) соединен с входом i-ro разряда первого операнда устройства, первый вход К-го разряда 1-го сумматора (,n+l; ,..., п-2) , соединен с выходом (К-1)-го разряда (1+1)-го сумматора, матрицу элементов И, п-й сумматор, группу элементов НЕ, группы сумматоров по модулю два, вторые rpynnfci элементов И, ИЛИ и запрета, причем выход т-го коммутатора j-й группы (,...,п+1) соединен с первым входом соответствукще jp сумматора по модулю два соответствующей группы, выходы 1-го элемен та ИЛИ первой группы и элемента И первой группы соединены с выходами i-ro разряда устройства, выход каждого элемента запрета пер. вой группы соединен с управляющим входом соответствующего элемента зап рета второй группы, управляющие входы коммутаторов j-й группы соединены с выходом (j+1)-ro элемента И второй группы, второй информационный вход К-го коммутатора j-и группы соединен с входом (К-1)-го разряда первого операнда устройства, вторые входы сумматоров по модулю два j-й группы соединены с выходом (j+l)-ro элемен;Та запрета второй группы и первым входом первого разряда j-ro суммато;ра, выходы сумматоров по модулю два j-й группы соединены с вторыми входами соответствующих разрядов j-ro сумматора, первые входы элементов И с . строки матрицы соединены с входом 1-го разряда второго операнда устройства, вторые входы элементов И i-ro столбца матрицы подключены к входу i-ro разряда третьего операнда устройства, выходы элементов И j-ro столбца матрицы соединены с третьими входами соответствующих разрядов j-ro сумматора входы разрядов перво ГО операнда устройства через соответствующие элементы НЕ группы соединены с первыми входами соответствующих . разрядов п-го сумматора, вторые входы которых соединены с выходами соответствующих элементов И п-го столбца матрицы, третий вход первого разряда п-го сумматора соединен с шиной единичного потенциала устройства, первьй вход каждого элемента ИЛИ первой группы соединен с выходом соответствующего сумматора по модулю два п-й группы, второй вход i-ro-элемента ИЛИ первой группы соединен с первым выходом переноса (i-l)-ro сумматора, первый вход i-ro сумматора по модулю два п-й группы, первый вход i-ro элемента И первой группы и информационный вход i-ro элемента запрета первой группы соединены с выходом (i+ )-го элемента И второй группы, второй вход i-ro сумматора по модулю два п-й группы, второй вход i-ro элемента И первой группы и управляющий вход i-ro элемента запрета первой группы соединены с вторьм выходом переноса i-ro сумматора и первым входом i-ro элемента ИЛИ второй группы, второй вход которого соединен с выходом соответствующего элемента ИЛИ первой группы, а выход - с информационным входом соответствующего элемента запрета второй группы, первый вход i-ro элемента И второй группы соединен с выходом i-ro элемента ШШ первой группы, а второй вход - с выxofioM промежуточной суммы (п+1)-го разряда (i-l)-ro сумматора. Недостатком этого устройства являются ограниченные функциональные возможности. Цель изобретения - расширение функ1Д10напьных возможностей устройства за счет вычисления частного от деления суммы парных произведений на одно число. Указанная цель достигается тем, что в {«ножительно-делительное устройство дополнительно введены S-1 дополнительных матриц элементов И (S - количество парных произведений) , причем первые входы элементов И i-и строки р-й дополнительной матрицы (,2,i..,5-1) соединены с входом i-ro райряда (2р+2)-го операнда устройства, вторые входы элементов И i-ro столбца р-й дополнительной матрицы подключены к входу i-ro разряда (2р+3)-го операнда

устройства, выходы элементов И каждого столбца каждой дополнительной матрицы подключены к входам соответствующих разрядов соответствующего сумматора.

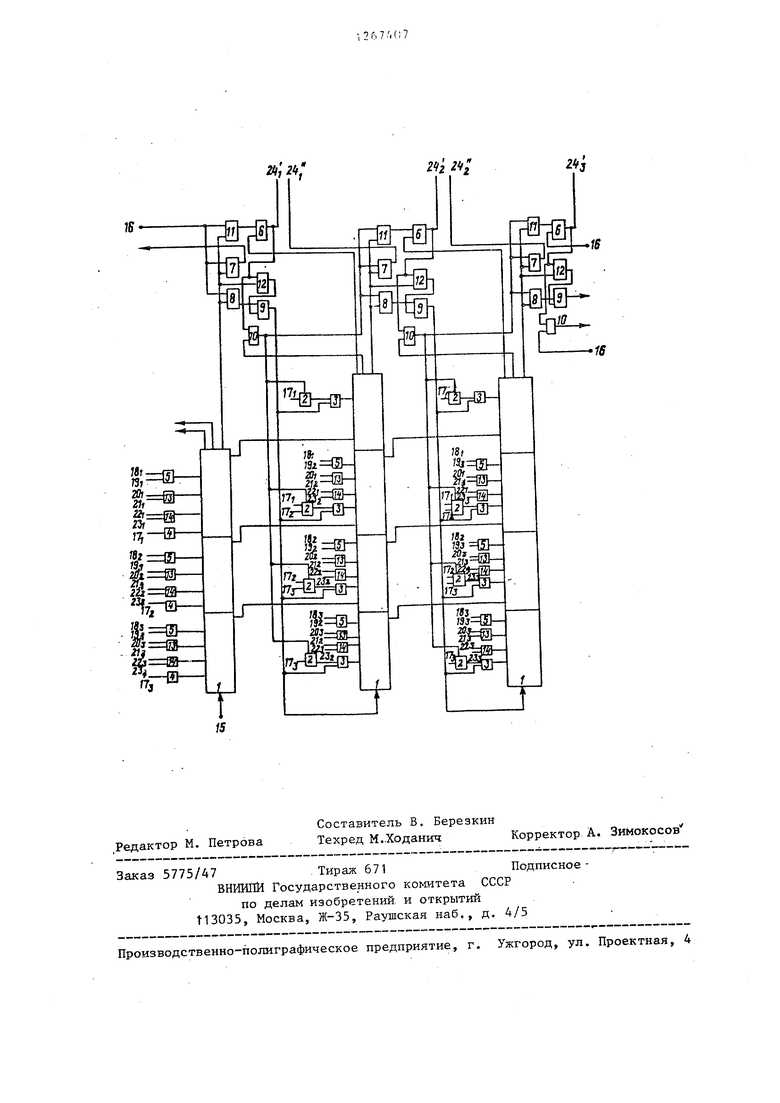

На чертеже представлена схема множительно-делительного устройства для случая, когда , .

Устройство содержит сумматоры 1, коммутаторы 2 групп, сумматоры 3 по модулю два первой и второй групп, элементы НЕ 4 группы, матрицу элементов И 5, элементы ИЛИ 6 первой группы, элементы И 7 первой группы, элементы 8 запрета первой группы, элементы 9 запрета второй группы, элементы И 10 второй группы, сумматоры 11 по модулю два третьей группы, элементы ИЛИ 12 второй группы, дополнительную матрицу элементов И 13 дополнительную матрицу элементов И 14, шину 15 единичного потенциала, Инну 16 нулевого потенциала, входы

17-23 соответственно первого, второго, третьего, четвертого, пятого, шестого и седьмого операндов, значения разрядов результата снимаются с выходов 24.

Работу устройства при вычислении функции

, + + ХзУз

(1)

,

представленной как , + + + - О и записанной в разрядной форме

W X

V V

-.У.

(2)

- ZOC о. Ч-

поясним на конкретном примере,

V / г i-tfc 4/11 где Ус (У Vs ... ; S 1,2,3;

.(,..

о (0 о ...о ) - разрядные векторы, .

представляющие собой изображения у. , а и О соответственно; 51 ется, что (i 1 и вычислительный про цесс продолжается аналогично (4)-(6) Если в результате j-ro вычисления а при поспо выражению ледующем (i+1)-M вычислении по выраV т I i J ч //;, л .,./ I. жению. (5) вектор 2 : i U2- (5 У, - -3 : ) болйпе или равен удвоенному вектору z, т.е. выполняет ся неравенство S . I - 2z м1(7) то далее выражение (5) реализуете, с удвоенным вектором z,. значение .о считается равным нулю сх 0, а к значению о1 1 добавляется единица. Фактически значение j-ro разряда вектора Z проставляется в двоичной избыточной системе счисления, т.е. Z может принимать значения 0,1,2. Критерием выполнения второго случая при (3+1)-й реализации выражений (4)-(6) положено следующее: « 1 и значение старшего разряда вектора S также должно быть равно единице при равенстве единице старшего разряда вектора z. Устройство работает следующим образом. При подаче на шины 18, 20 и 22 значений разрядов соответственно век торов х , 2, хз, на шины 19, 21 и 23 значений разрядов соответственно векто.ров у,., у , у , а на шину 17 значений разрядов вектора z в схеме протекает переходный процесс. После окончания переходного процесса в устройстве на выходе п-го сумматора 1 по выражению (5) образуется вектор , который поступает на вход (n-l)-ro сумматора 1, а на выходе переноса старшего разряда п-го сумматора 1 в соответствии с (4) образуется значение с старшего разряда искомого вектора d, , которое поступает на выход 24. Далее на вход (n-l)-ro сумматора 1 поступают век-.. торы xW, , У и zp31 J в котором по выражению (5) образуется вектор х а на выходе пере носа его старшего разряда образуется нулевой или единичный сигнап, который в соответствии с (4) поступа ет на выход 24 второго разряда. Аналогично образуется значение «д. 76 Если на выходе 24 i-ro разряда значение ci 0, а на первом выходе переноса (i-l)-ro сумматора 1 образуется единичный сигнал, то он поступает на выход ,24 i-ro разряда, т.е. 1 в этом случае сх 1. Если на выходе 24 i-ro ра.зряда образовался единичный сигнал , а на выходе промежуточной суммы (i-l)-ro сумматора 1 образовался также единичный сигнал, что характеризует выполнение (7), то выражение (5) в (i-1)-M сумматоре 1 реализуется с удвоенным вектором z . При этом на соответствующих выходах 24 образуются значения соответственно , . 0. Использование дополнительных матриц элементов И, предназначенных для формирования дополнительных частичных произведений, отличает данное устройство от прототипа, в котором реализуется вычисление только функции xy/z, в предлагаемом же устройстве реализуется вычисление частного от деления скалярного произведе-. НИН двух векторов на произвольное число. Формула изобрете.ния Множительно-делительное устройство по авт.св. № 1206774, отличающееся тем, что, с целью расширения функциональных возможностей за счет вычисления частного от деления суммы парных произведений на одно число, устройство содержит S-1 дополнительных матриц элементов (S количество парных произведений), причем первые входы элементов И i-й строки р-й дополнительной матрицы (,...,S-1) соединены с входом i-ro разр-яда (2р+2)-го операнда устройства, вторые входы элементов И i-ro столбца дополнительной матрицы подключены к входу i-ro разряда (2р+3)го операнда устройства, выходы эле ентов И каждого столбца каждой дополнительной матрищ) подключены ко входам соответствующих разрядов соответствующего сумматора.

| Авторское свидетельство СССР № 1206774, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-30—Публикация

1981-06-18—Подача