операнда устройства соответственно, первый вход каждого элемента ИЛИ первой группы соединен с выходом соответствующего сумматора /по модулю два п-и группы, второй вход 1-го элемента ИЛИ первой группы соединен с первым выходом переноса (1-1)-го сумматора, первый вход 1-го сумматора по модулю два п-й группы и первый вход 1-го элемента И первой группы соединены с выходом (i+1)-ro элемента И второй группы, второй вход 1 -го сумматора по модулю два п-й группы.

второй вход 1-го элемента И первой группы и первый вход i-го элемента ИЛИ второй группы соединены с вторым выходом переноса i-ro сумматора, второй вход каждого элемента ИЛИ второй группы подключен к выходу соответствующего элемента ИЛИ первой группы, первый вход i-ro элемента И второй группы соединен с выходом соответствующего элемента ИЛИ первой группы, а второй вход - с выходом промежуточной суммы (п+1)-го разряда (f-1)го сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1981 |

|

SU1115047A2 |

| Матричный вычислитель | 1983 |

|

SU1137464A1 |

| Множительно-делительное устройство | 1981 |

|

SU1267407A2 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1053105A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1315971A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Устройство для вычисления зависимости @ = @ + @ + @ | 1981 |

|

SU1019446A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1987 |

|

SU1413627A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Устройство для параллельного формирования адресов | 1990 |

|

SU1734097A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, Содержащее п-1 сумматоров, (п - разрядность операндов), п -1 групп коммутаторов, первую группу элементов И, первую группу элементов ИЛИ, причем первый информационный вход -го коммутатора J-и группы (,...,п-1; 1 1,... ,h) соединен с входом i-го разряда первого операнда устройства, первый вход К-го разряда в-го сумматора (,...,n-Hi, в 1,...,П-2) соединен с выходом (К-1)-го разряда (И+1)-го сумматора, отличающ ее с я тем, что, с целью повьшения быс,тродействия при вычислении функции ct x/г, устройство содержит матрицу элементов И, п-и сумматор, группу элементов НЕ, группы сумматоров по модулю два, вторые группа элементов И, ИЛИ, причем выход т-го коммутатора j-й группы (,... ,п +1) соединен с первым входом соответствующего сумматора по модулю два соответствующей группы, выходы л-го элемента ИЛИ первой группы и (i-l)-ro элемента И первой группы соединены с выходами 1 -го разряда устройства, управляющие входы коммутаторов j-й группы соединены с выходе (j+1)-ro элемента И второй группы, второй ин-. формационный вход К-го коммутатора j-й группы соединен с входом (К-1)го разряда первого операнда устройства, вторые входы сумматоров по модулю два j-й группы соединены с выходом (j+1)-ro элемента ИЛИ второй группы и первым входом первого разряда j-ro сумматора, выходы сумматоров по модулю два у-й группы соединены с вторыми входами соответствующих разрядов j-ro сумматора, первые Входы элементов И j-го столбца матрицы соединены с входом j-ro разрядд (Л второго операнда устройства, второй вход р-го элемента И j-ro столбца с |матрицы (,...,n-j) соединен с входом ()-ro разряда второго операнда устройства, выход с},-го элемента И и-го столбца матрицы ( 1,...,п-С) соединен с третьим входом (-И)-го разряда (g + D-ro сумматора, оо о входы -разрядов первого операнда устройства через соответств ощие элемен4: td ты НЕ группы соединены с первыми вхо-t дами соответствукящх разрядов п-го Oi сумматора, вторые входы и (и-2)-. го разрядов п-го су№«атора соединены с входами п-го и (n-l)-ro разрядов второго операнда устройства соответственно, второй вход первого разряда п-го сумматора соединен с шиной единичного потенциала устройства, выход элемента И (n-l)-ro столбца матрищ соединен с третьим входом п-го разряда сумматора, третий вход первого разряда первого сумматора соединен с входом первого разряда второго

Изобретение относится к вычислительной технике и может быть применено в спецпроцессорах или в комппексе с цифровой вычислительной машиной для оперативного вычисления зависи

мостио --- 1 например, в системах

автоматического управления динамическими объектами или технологическими процессами,

Известно вычислительное устройство, предназначенное для деления двоичных чисел, содержащее п параллельных (h+2)-разрядных сумматора, (п+1)-разрядные преобразователи прямого кода в дополнительный, причем выход каждого |-го разряда -го сумматора (,2,..,,n, ,2,...,n) соединен с первым входом (н-1)-го разряда (}+1)-го сумматора, первые входы первого сумматора подключены к входам первого операнда устройства, вторые входы разрядов сумматоров подключены к соответствующим выходам преобразователей, информационные входы которых подключены к входам второго операнда устройства, управляющие входы преобразователей начиная со второго,соединены с выходами знаковых разря дов предьщущих сумматоров которые также являются выходами устройства Cl3.

Недостатком этого устройства является oтнodитeльнo невысокое быстродействие. Кроме того, это устройство не может производить операции деления.

2

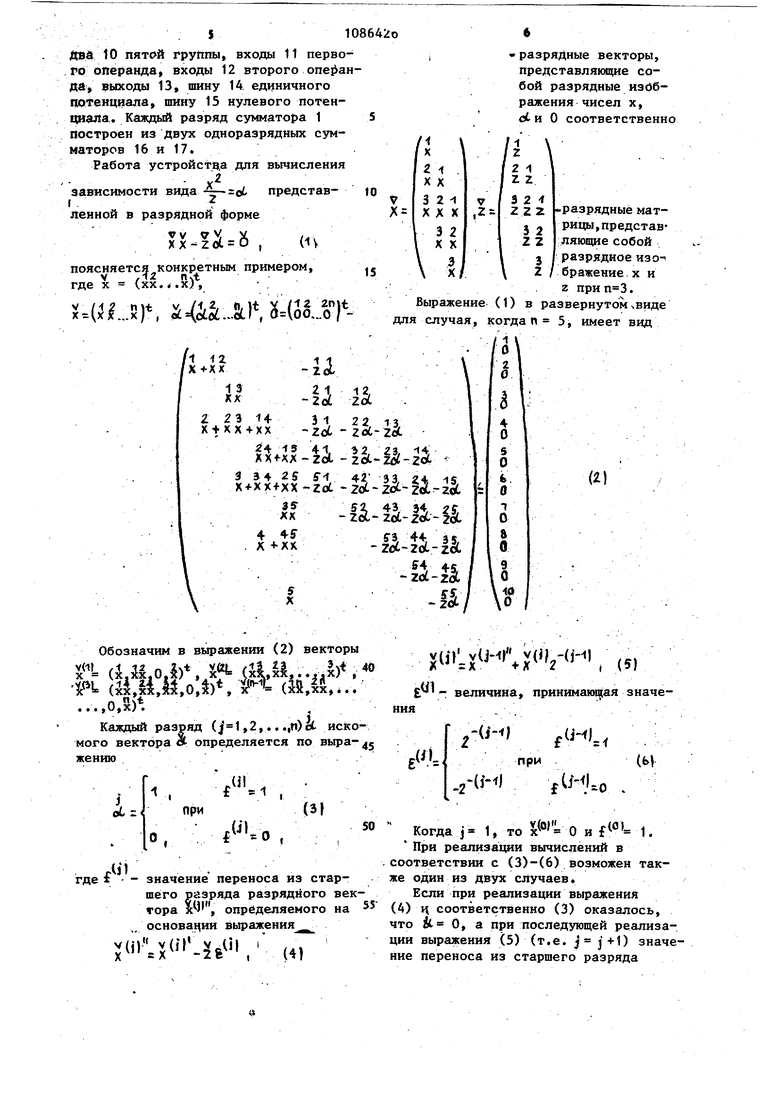

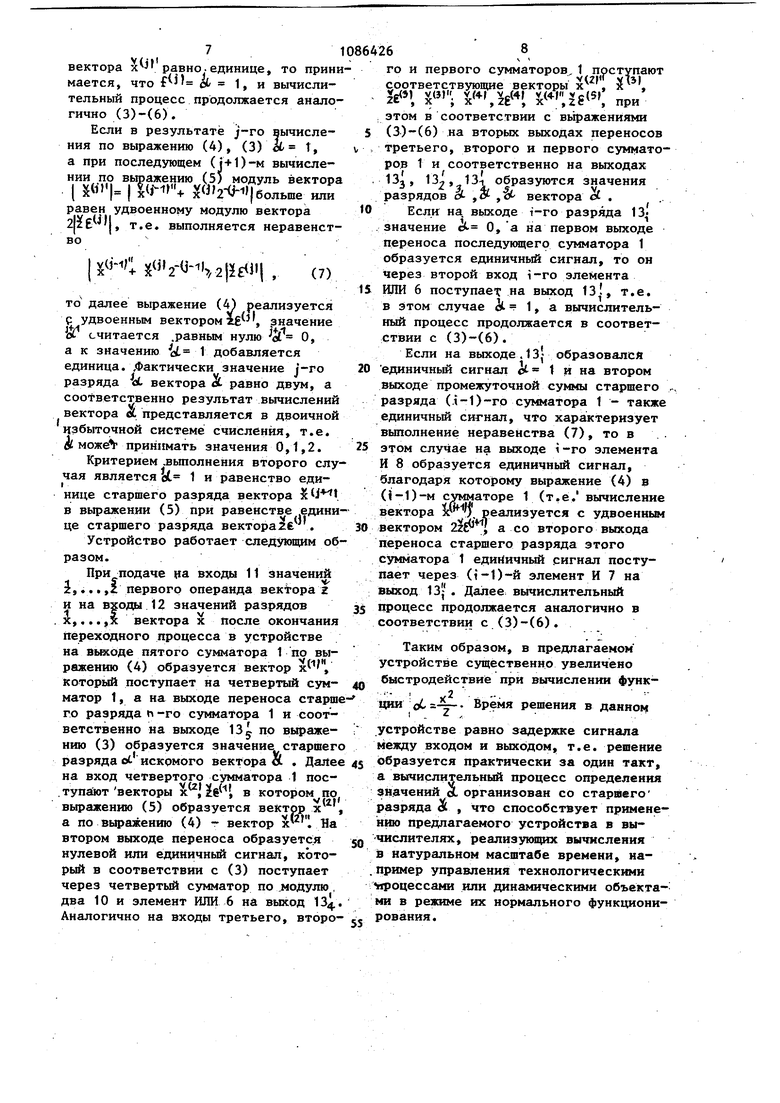

Наиболее близким к предлагаемому по технической сущности является вычислительное устройство, предназначенное для умножения и деления, содержащее П-1 сумматоров (п - разрядность операндов), П-1 групп коммутаторов, группы элементов запрета, И и ИЛИ, причем первый информационны вход i-ro коммутатора j-и группы (j 1,... ,h-1; .1 1,...,h) соединен с входом 1-го разряда первого операнда устройства, первыйвход К-го разряда Р -го сумматора (,... ,П + 1 -, ,...,п-2) соединен с выходом (К-1)-го разряда (8+1)-го сумматора, выходы переполнения сумматоров являются выходами первой группы устройства, выходы старших разрядов сумматоров и выходы всех разрядов первого сумматора являются выходами второй группы устройства, входы разрядов второго операнда соединены с первыми входами соответствующих элементов И группы, информационные входы элементов запрета группы соединены с выходами переполнения соответствующих сумматоров, вторые входы элементов И группы и управляющие входы элементов запрета группы подключены к управляющему входу устройства, выходы элементов И группы и элементов запрета группы соединены с входами соответствующих элементов ИЛИ группы, выходы которых подключены к вторым информационным входам коммутаторов соответствующих групп, управляющие входы которых подключены к управляющему входу устройства 2. Недостатком этого устройства йиляется невысокое быстродействие л. - х2 при вычислении функции связанное с тем, что результат этой операции приходится вычислять в два этапа. Цель Изобретения - повышение (быстродействия ycTpoftqTsa при выу2числении функции -i- .: Указанная цель достигается тем, что в вычислительное устройство, содержащее п-1 сумматоров, (п - разряд ность операндов), п-1 групп коммутаторов, первую группу элементов И, первую группу элементов ИЛИ, причем первый информационный вход i-ro коммутатора .j-й группы (j 1,... ,n-tv ,...,n) соединен с входом i-ro разряда первого операнда устройства вход К-го разряда С-го сумматора (K-2,...,n + 1i С 1,...,Г1-2) соединен с выходом (К-1)-го разряда (6+1)-го сумматора,дополнительно вве дены матрица элементов И, П-и сумматор, группа элементов НЕ, группы сумматоров по модулю два, вторые группы элементов И, ИЛИ, причем выход 1Т1-ГО коммутатора j-й группы (,,.. ,0 + 1) соединен с первым входом соответствующего сумматора по модулю два соответствующей группы, выходы -го элемента ИЛИ первой группы и (i-l)-ro элемента И первой группы соединены с выходами i-ro раз ряда устройства, управляющие входы коммутаторов j-й группы соединены с выходом (j+1)-ro элемента И второй группы, второй информационный вход К-го коммутатора j-й группы соединен с входом (К-1)-го разряда первого операнда устройства, вторые входы сумматоров по модулю два j-и группы соединены с выходом (j+1)-ro элемента ИЛИ второй группы и первым входом первого разряда j-ro сумматора, выходы сумматоров по модулю два j-й группы соединены с вторыми входами соответствующих разрядов j-ro сумматора, первые входы элементов И j-ro столбца матрицы соединены с входом j-ro разряда второго операнда устройства, второй вход р-го элемента И j-ro столбца матрицы (,... ,fi-j) соединен с входом (j+1)-ro разряда второго операнда устройства, выход с,-го элемента И -го столбца матри164 цы (,. .. ,п-Р) соединен, с третьим, входом Ц + 1)-го разряда (8 + 1)-го сумматора, входы разрядов первого операнда устройства через соответствующие элементы НЕ группы соединены с первыми входами соответствующих разрядов п-го сумматора, вторые входы ti-ro и (п-2)-го разрядов И-го сумматора соединены с входамию-го и (п-1)-го разрядов второго операнда устройства соответственно, второй вход первого разряда п-го сумматора соединен с шиной единичного потенциала устройства, выход элемента И (п-1)-го столбца матрицы соединен с третьим входом tt-ro разряда сумматора, третий вход первого разряда первого сумматора соединен с входом первого разряда второго операнда устройства соответственно, первмй вход каждого элемента ИЛИ первой группы соединен с выходом соответствующего сумматора по модулю два п-и группы, второй вход i-го элемента ИЛИ первой группы соединен с первым выходом переноса (i-l)-ro сумматора, Первый вход t-ro сумматора по модулю два п-й группы и первый вход i-ro элемента И первой группы соединены с выходом О + О-го элемента И .второй группы, второй вход 1-го сумматора по модулю два п-и группы, второй вход i-го элемента И первой группы и первый вход i-ro элемента ИЛИ второй группы соединены с вторым выходом переноса -го сумматора, второй вход каждого элемента ИЛИ второй группы подключен к выходу соответствующего элемента ИЛИ первой группы, первый вход i-го элемента И второй грулпы соединен с выходом соответствующего элемента ИЛИ первой группы, а второй вход - с выходом промежуточной суммы (п+1)-го разряда (i-1)го сумматора. На фиг.1 представлена схема вычислительного устройства (для случая ); на фиг.2 - схема одного разряда сумматора. Вычислительное устройство содеряонт сумматоры 1, коммутаторы 2 групп, матрицу элементов И 3, сумматоры по модулю два 4 первой, второй, третьей и четвертой групп, элементы НЕ 5 группы, элементы ИЛИ 6. первой группы, элементы И 7 первой группы, элементы И 8 второй группы, элементы ИЛИ 9 второй группы, сумматоры по модулю 51 Два 10 пятой группы, входы 11 первого операнда, входы 12 второго oneiiaH да, выходы 13, шину 14 единичного 1Ютенциала, шину 15 нулевого потенциала. Каждый разряд сумматора 1 построен из двух одноразрядных сумматоров 16 и 17. Работа устройства для вычисления . „2 зависимости вида представленной в разрядной форме VV vX X XX-ZO(. O , поясняется конкретным примером, V ,12 Пч1 где X (хх...х), . -UI...S), ...sci,x(5a...,iОбозначим в выражении (2) векторы

(,%о.|) ,5 АМ,.. . PU (,o,), ir (55,М,.,.

у VI )

.1

Каждый разряд (,2,.. .,п) ot искомого вектора определяется по выра- j жению rUI . f 1 О , где f - значение переноса из старшего разряда разрядного ве тора , определяемого на основании выражения v(( (,

;(Ufv(,v(i,-(H);(,,

c«l

величина, принимаю1 ая значения

ru--

(feV

при разрядные векторы, представлякщие собой разрядные изббражения чисел х, ct и О соответственно -разрядные матрицы, представляющие собой разрядное изо-i бражение. х и . Z . в развернутом .виде ап 5, имеет вид .2-( f U-.o . Когда j 1, 1. При реализации вычислений в соответствии с (3)-(6) возможен также один из случаев. Если при реализации выражения (4) н соответственно (3) оказалось, что ic О, а при последующей реализации выражения (5) (т.е. j j +1) значение переноса из старшего разряда 1 вектора х- равно-единице, то прини мается, что fJ (st 1, и вычислительный процесс продолжается аналогично (3)-(6). Если в результате j-ro вычисления по выражению (4), (3) dt Т, а при последующем (|+1)-м вычислении по вьгоажению (5) модуль вектора ((М1)больше или равен удвоенному модулю вектора , т.е. выполняется неравенствоv(H/; 5 Ш2-и-1|, , (7) то далее выражение (4) реализуется е удвоенным вектором , .значение У- считается .равным нулю о1 - О, а к значению {i 1 добавляется единица. ,Фактически значение j-ro разряда cL вектора d равно двум, а соответственно результат вычислений вектора at представляется в двоичной избыточной системе счисления, т.е. fiiможё принимать значения 0,1,2. Критерием .вьшолнения второго слу чая является dt 1 и равенство единице старшего разряда вектора в вьфажении (5) при равенстве едини це старшего разряда вектора26 . Устройство работает следующим об разом. При подаче на входы 11 значений Jj...,2 первого операнда вектора г и на входы 12 значений разрядов . ,... ,х вектора х после окончания йереходного процесса в устройстве на выходе пятого сумматора 1 по выражению (4) образуется вектор , который поступает на четвертый сумматор 1, а на выходе переноса старш го разряда и-го сумматора 1 и соответственно на выходе 13с по выражению (3) образуется значение старшег разряда otискомого вектора & . Дале на вход четвертого сумматора 1 пос. TynaioTвекторы х ,, в котором по выражению (5) образуется вектор х а по выражению (4) - вектор На втором выходе переноса образуется нулевой или единичный сигнал, который в соответствии с (3) поступает через четвертый сумматор по .модулю , два 10 и элемент ИЛИ 6 п& выход 13 Аналогично на входы третьего, второ го и первого сумматоров, 1 поступают v(2| ЧЪ| соответствующие векторы х , х , |e(J) v(3... v((4 v(4r;vg(5 „р„ этом а соответствии с вь1ражениями (3)-(6) на вторых выходах переносов третьего, второго и первого сумматоров 1 и соответственно на выходах 13, 132 1 образуются значения разрядов ct ,№ , вектора cf- , Если на. выходе i-ro разряда 13 1J / значение О, а на первом выходе переноса последукнцего сумматора 1 образуется единичный сигнал, то он через второй вход i-ro элемента ИЛИ 6 поступает на выход 13, т.е. в этом случае ct 1, а вычислительный процесс продолжается в соответствии с (3)-(6). Если на выходе. 13- образовался единичный сигнал о 1 и на втором выходе промежуточной суммы старшего , разряда (л-1)-го сумматора 1 - также единичный сигнал, что хара ктеризует выполнение неравенства (7), то в этом случае на выходе -го элемента И 8 образуется единичный сигнал, благодаря которому выражение (4) в (i-l)-M сумматоре 1 (т.е. вычисление вектора реализуется с удвоенным вектором а со второго выхода переноса старшего разряда этого сумматора 1 единичный сигнал поступает через (1-1)-й элемент И 7 на выход 13| . Далее вычислительный процесс продолжается аналогично в соответствии с О)-(6). Таким образом, в предлагаемом устройстве сзш;ественно увеличено быстр од ействи е при вычислении функВДшВремя решения в данном ( fустройстве равно задержке сигнала между входом и выходом, т.е. решение образуется практически за один такт. а вычислительный процесс определения значений л. организован со старшего разряда , что способствует применению предлагаемого устройства в вычислителях, реализующих вычисления в натуральном масштабе времени, например управления технологическими мроцессами или динамическими объектами в режиме их нормального функционирования.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для деления двоичных чисел | 1978 |

|

SU748410A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Множительно-делительное устройство | 1980 |

|

SU920712A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-15—Публикация

1981-03-25—Подача