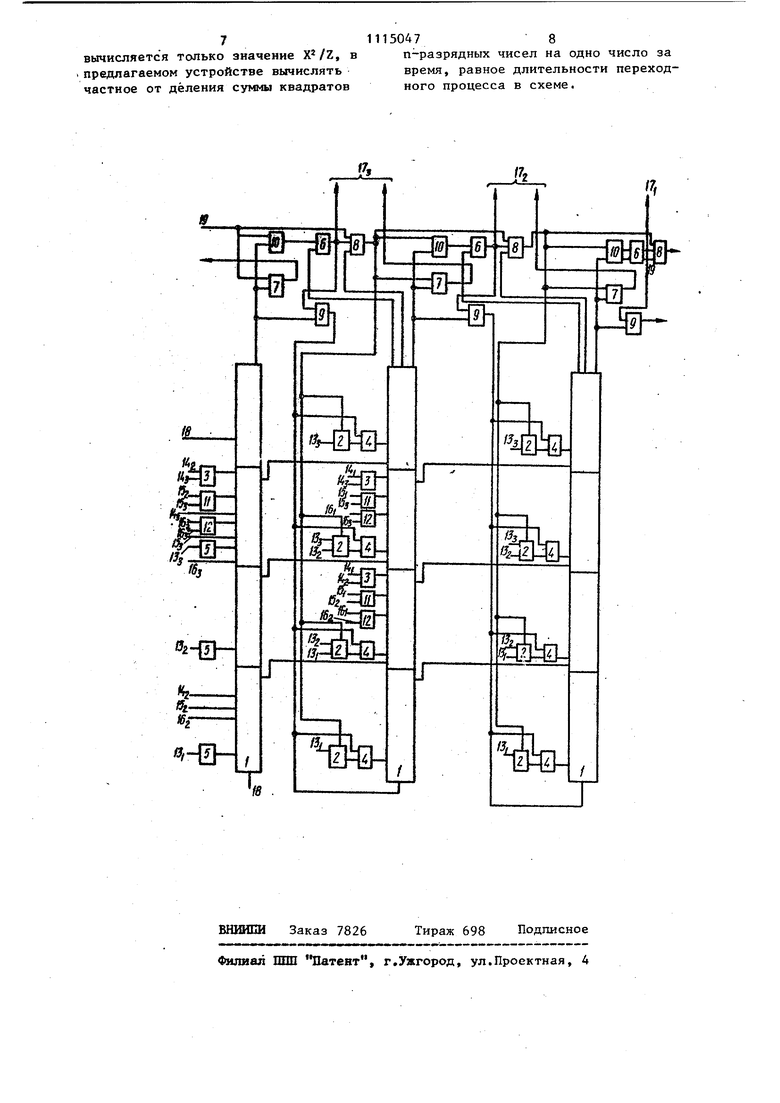

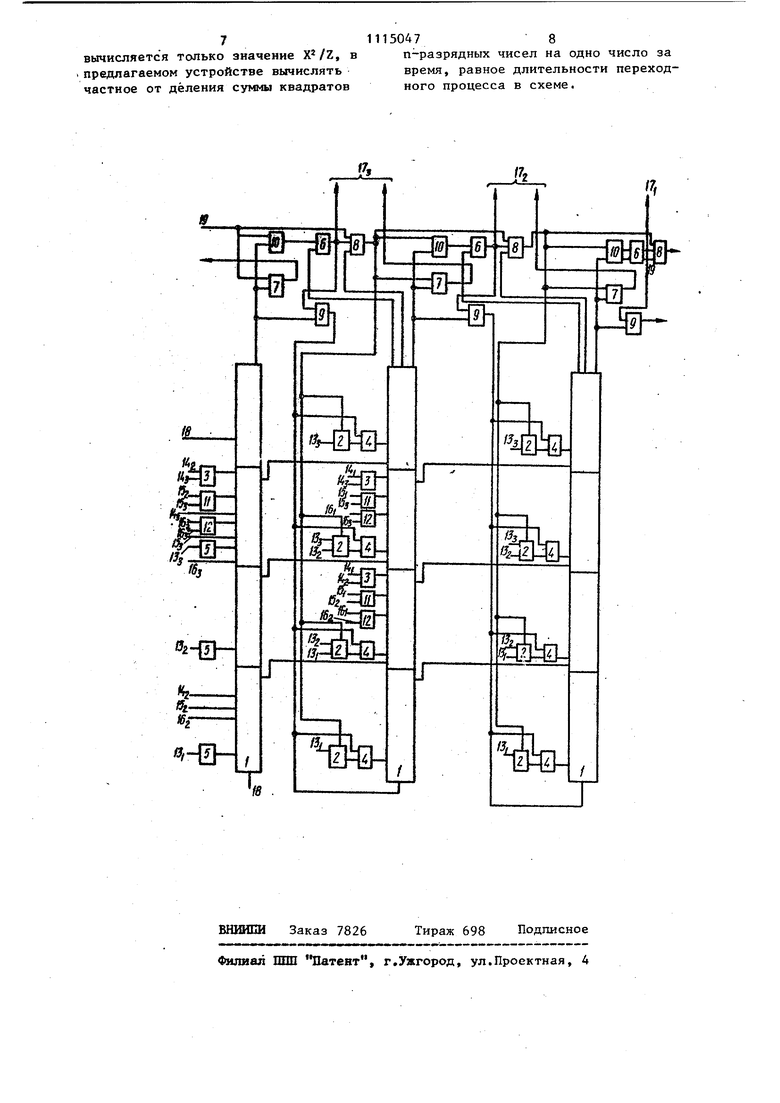

4 41 Изобретение относится к вычислительной технике и может быть примет нено в качестве спецпроцессора в ком плексе с цифровой вычислительной машиной или в специализированных вычис лительных устройствах для оперативнрго вычисления групповой операции ZxVz. По основному-авт.св. № 1086426 известно вычислительное устройство, содержащее (п-1) сумматоров (п-разрядность операндов), (п-1) групп коммутаторов, первую группу элементов И, первую группу элементов ИЛИ, причем первый информационный вход i-ro коммутатора j-й группы (, ..., п-1, . ,..,,п) соединен с входом i-ro разряда первого операнда устройства, первый вход К-го разряда ,(j-ro сумматораТк 2,..., п+1; 6 1, ..., п-2) соединен с выходом (К-1)-г разряда ( + 1)-го сумматора, а также матрицу элементов И, п-й сумматор, группу элементов НЕ, группу сумматоров по модулю два, вторые группы эле ментов И, ИЛИ, причем выход т-го коммутатора j-й группы (,...,п+1) соединен.с первым входомсоответствующего сумматора по модулю два соот ветствующей группы, выходы i-ro элемента ИЛИ первой группы и (i-l)-ro элемента И первой группы соединены с выходами i-ro разряда устройства, управляющие входы коммутаторов j-й группы соединены с выходом (j+1)-ro элемента И второй группы, второй ин формационный вход К-го коммутатора j-й группы соединено входом К-1 -го разряда первого операнда устройства вторые входы сумматоров по модулю два j-й группы соединены с выходом (j+1)-ro элемента ИЛИ второй группы и первым входом первого разряда j-ro сумматора, выходы сумматоров по модулю два j-й группы соединены с вторыми входами соответствующих разрядов j-ro сумматора, первые вхо ды элементов И j-ro столбца матрицы соединены с входом j-ro разряда вто рого операнда устройства, второй вход р-го элемента И j-ro столбца матрицы (,..., n-j) соединен с входом (j+10-го разряда второго one ранда устройства, выход q-ro элемента И 2-го столбца матрицы (, ...,п-) соединен с третьим входом (q+1)-ro разряда (8+1)-го сумматора, входы разрядов первого операнда устройства через соответствующие элементы НЕ группы соединены с первыми входами соответствующих разрядов п-го сумматора, вторые входы п-го и (п-2)-го разрядов п-го сумматора сое- динены с входами п-го и (п-1.)-го разрядов второго операнда устройства соответственно, второй вход первого разряда п-го сумматора соединен с шиной единичного потенциала устройства, выход элемента И (п-1)-го столбца матрицы соединен с третьим входом п-го разряда сумматора, третий вход первого разряда первого суммато-ра соединен с входом первого разряда второго операнда устройства соответственно, первьш вход каждого элемента ИЛИ первой группы соединен с выходом соответствующего сумматора по модулю два п-й группы, второй вход 1-го элемента ИЛИ первой группы соединен с первым выходом переноса (i-l)-ro сумматора, первый вход i-ro сумматора по модулю два i-й группы и первый вход i-ro элемента И первой группы соединен с выходом (i+1)-ro элемента И второй группы, второй вход i-ro сумматора по модулю два i-й группы, второй вход i-ro элемента И первой группы и первый вход i-ro элемента ИЛИ второй группы соединен с вторым выходом переноса i-ro сумматора, второй-вход каждого элемента ИЛИ второй группы подключен к выходу соответствующего элемента ИЛИ первой группы, первый вход i-ro элемента И второй группы соединен с выходом соответствующего элемента ШШ первой группы, а второй вход - с выходом промежуточной суммы (п+1)-го разряда (i-1)-го сумматора Г ДНедостатком известного устройства являются ограниченные функциональные возможности из-за того, - , нем невозможны вычисления вида xV/Z Целью изобретения является расширение функциональных возможностей устройства путем вычисления частного от деления суммы квадратов на одно число. Поставленная цель достигается тем, что в вычислительное устройство введены (S-1) дополнительных матриц элементов И (S - количество возводи3мых в квадрат чисел), причем первые входы элементов И j-ro столбца г-й дополнительной матрицы (,2,..., S-1) соединены с входом j-ro разряда (г+2)-го операнда устройства, вто рой вход р-го элемента И j-ro столбца г-й дополнительной матрицы соединен с входом (j+1)-ro разряда (г+2)-го операнда устройства выход q-ro элемента И t -го столбца г-й дополнительной матрицы соединен с (г+3)-м входом (q+1)-ro разряда (+1)-го сумматора. На чертеже приведена схема предлагаемого вычислительного устройства для случая, когда , . Устройство содержит сумматоры 1, коммутаторы 2 групп, матрицу элементов И 3, сумматоры 4 по модулю два первой и второй групп, элементы НЕ 5 группы, элементы ИЛИ 6 первой группы, элементы И 7 первой группы, элементы И 8 второй группы, элементы ИЛИ 9 второй группы, сумматоры 10 по модулю два третьей группы, дополнительные матрицы элементов И 11 и 12, входы 13 первого операнда, входы 14 второго операнда, входы 15 третье го операнда, входы 16 четвертого операнда, выходы 17, шину 18 единичного потенциала и шину 19 нулевого п тенциала . Работу процессора групповых опера ций, реализующего вьршсление зависимости Ц +Ц +Ц+... +Х|- +.. . +Х|г2 0 представленной в виде f X.....4Xj..... 47 4 и записанной в разрядной форме V V/ V ЛТ/ V V X,X + ...ajXj...tXgXg-ZoE, 0 . (2) ПОЯСНИМ на конкретном примере, где разрядные векторы, представляюц е со бой разрядные изображения чисел XV, ot, 0;/ разрядные матрицы, представляющие собой разрядное изображение чисел X I и Z соответственно при п 3. Запишем вьфажение (2) в развернутом виде для случая, когда , и .

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1981 |

|

SU1086426A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1053105A1 |

| Множительно-делительное устройство | 1981 |

|

SU1267407A2 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Устройство для возведения в квадрат,извлечения квадратного корня,умножения и деления | 1981 |

|

SU1059571A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Матричное устройство для умножения | 1981 |

|

SU999044A1 |

| Устройство для вычисления зависимости @ = @ + @ + @ | 1981 |

|

SU1019446A1 |

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО по авт. св. №1086426, отличающееся тем, что, с целью расширения функциональных возможностей путем вычисления частного от деления суммы квадратов на одно число, в устройство введены (S-1) дополнительных матриц элементов И (S - количество возводимых в. квадрат чисел), причем первые входы элементов И j-ro столбца г-й дополнительной матрицы (г-1,..., S-1) соединены с входом j-ro разряда (г+2)-го операнда устройства, второй вход р-го элемента И j-ro столбца г-й дополнительной матрицы соединен с входом (j+1)-ro разряда (г+2)-го операнда устройства , выход q-ro элемента И ,Е -го столбца г-й дополнительной матрицы соединен с (г+3)-м входом (q-H)-ГО разряда (В + 1)-го сумматора. (/) С

Обозначим в выражении (3) векторы

х;

0.

о 50

где - значение переноса из старшего разряда вектора л , определяемого на основании выражений Каждый i-й разряд (,2,...,п) искомого вектора ot определяется по 1; О Р ,2,3,,..,n, (4) х-....(i) г;;(| :;и). v «) Цх( .2(х ;Л.... v(a,р(2).(,(srv(3, v(|v(a) , v(;p(H,:(H(v,,v,,j,p(,, величина, принимающая значения когда . , О При реализации вычислений в соответствии с (4)-(6) возможен также один из двух случаев. Если при 1-й реализации вьфажения (5)соответственно (4) оказалось, чт оС О, а при последующей реализации вьражения (5) (т.е. ,1)значение переноса из старшего разряда в выражении (5) вектора ,. (i+1) iO -i/v(iH) v(itij v(i4i| S A 2 K + л t-...--л равно единице, то принимается, что W 1 ивычислительный процесс продол кается аналогично (4)-(6). Если в результате i-ro вычислителя по вьтражению о 1, а при последу щем (i+D-M вычислении по выражению (5) вектор v,)-.|J(H.)vOH)jUH)j Дольше или равен удвоенному вектору Z, т.е. вьшолняется неравенство ., (7) то далее вьгражение (5) реализуется с,удвоенным вектором л, , значение оС считается равньм нулю Ы О, а значению ot 1 добавляется единица. Фактически значение i-ro разряда ot вектора с представляется в двоично избыточной системе счисления, т.е. о(. может принимать значения 0, 1, 2 В основу критерия выполнения вто рого случая или 1-й реализации выраж ний (4)-(6) положено следующее: оС g значение старшего разряда вектора S также должно бьпь равно единице при равенстве единице старшего разряда вектора Z. При этом, если значение переноса со старшего разря7«да вектора равно единице, то принимается at Oj-.C 1, и вычислительный процесс продолжается в соответствии с (4)-(6). Работа устройства происходит следующим образом. При подаче на входы 13 значений разрядов Z , Z ,... , вектора и на входы 14-16 соответственно разрядов Х, Х , X, Х Х| и Xj, Х|, Х векторов X,, X,, и Х после окончания переходного процесса в устройстве на выходе п-го сумматора fo выражению (5) образуется вектор , который поступает на второй сумматор 1, а на выходе переноса старшего разряда сумматора 1 и, соответственно, на выходе 17 образуется значение старшего разряда Ьб , искомого вектора оС . Далее на вход второго сумматора 1 поступают V (2.1 Хд и Ze , в сотором to выражению (5) образуется вектор , а на выходе переноса старшего разряда его - нулевой или единичный сигнал, который в соответствии с (4) поступает на выход 17 Аналогично на входы третьего, второго и первого сумматоров 1 посту (2) пают соответственно векторы X ; Ze, при этом в соответствии с выражениями (4)-(6) на выходе переноса первого сумматора 1 и, соответственно, на выходе 17 образуется значение разряда искомого вектора d . Если на выходе 17- значение , а на выходе переноса старшего разряда последующего сз матора 1 образуется единичньй сигнал, то он поступает ра.выход 17, т.е. в этом случае oi 1. Если на выходе 17 образовался единичный сигнал d 1, а на выходе промежуточной суммы старшего разряда (i-l)-ro сумматора 1 - также единичный сигнал, то в этом случае на соответствующем выходе 17 образуется единичный сигнал,, благодаря которому вьфажение (5) в (1-1)-м сумматоре 1 реализуется с удвоенным вектором Z . При этом на выходе переноса старшего разряда (i-l)-ro сумматора 1 образуется единичный сигнал, поступающий на выход 17.. Далее вычислительный процесс продолжается аналогично в соответствии с (4)-Сб). Использование дополнительных матриц элементов И, а также новых связей между ними, позволяет, в отличие от известного устройства, в котором 7 вычисляется только значение , в предлагаемом устройстве вычислять частное от деления суммы квадратов

Р4

Д

ffi

tit fl Г

-SH

2Р4

11150478 п-разрядных чисел на одно число за время, равное длительности переходного процесса в схеме.

/5/

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Вычислительное устройство | 1981 |

|

SU1086426A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-09-23—Публикация

1981-04-27—Подача