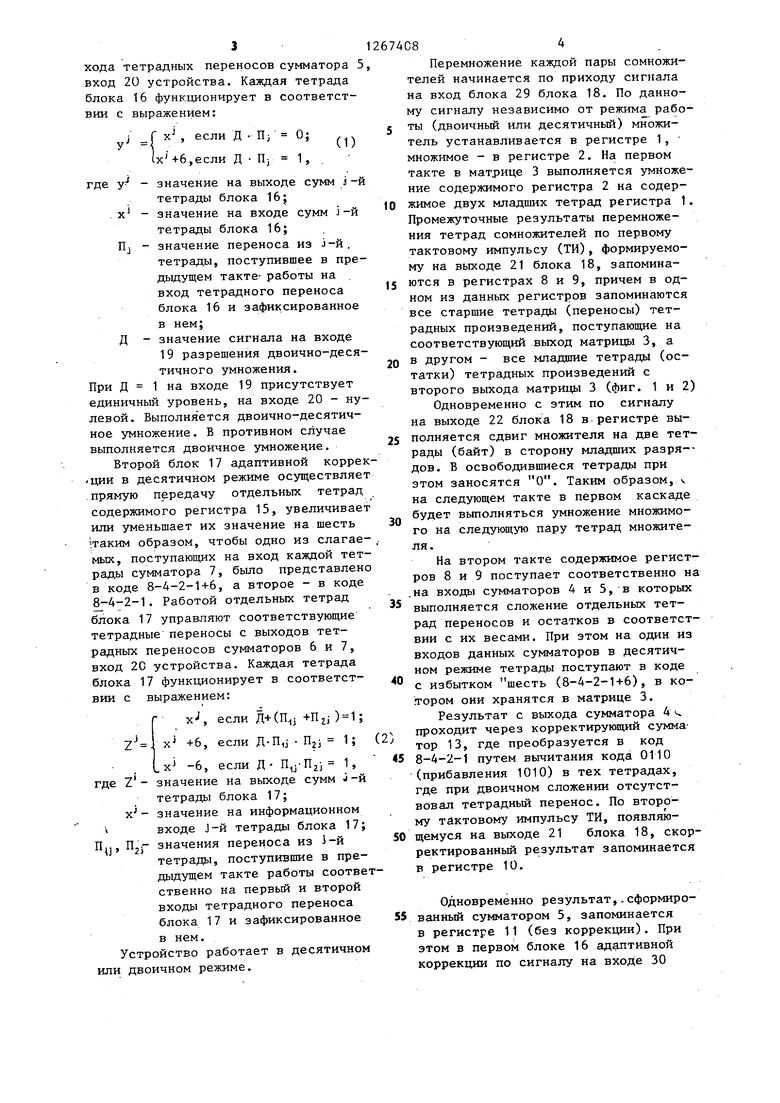

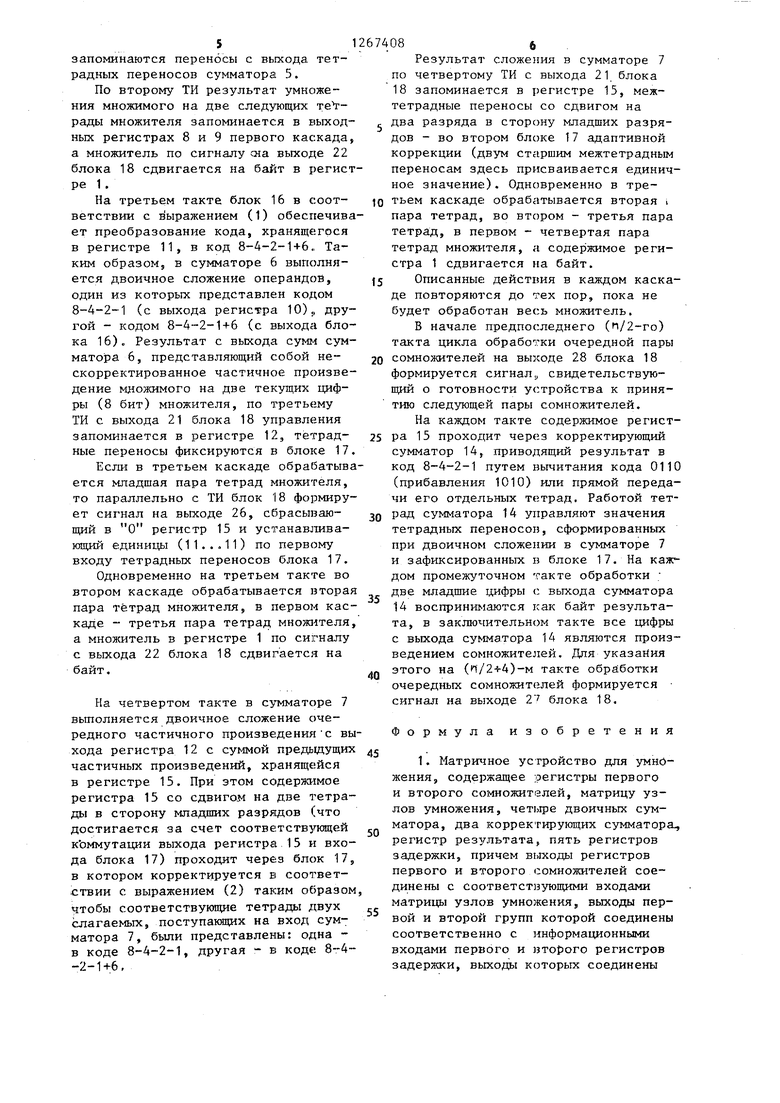

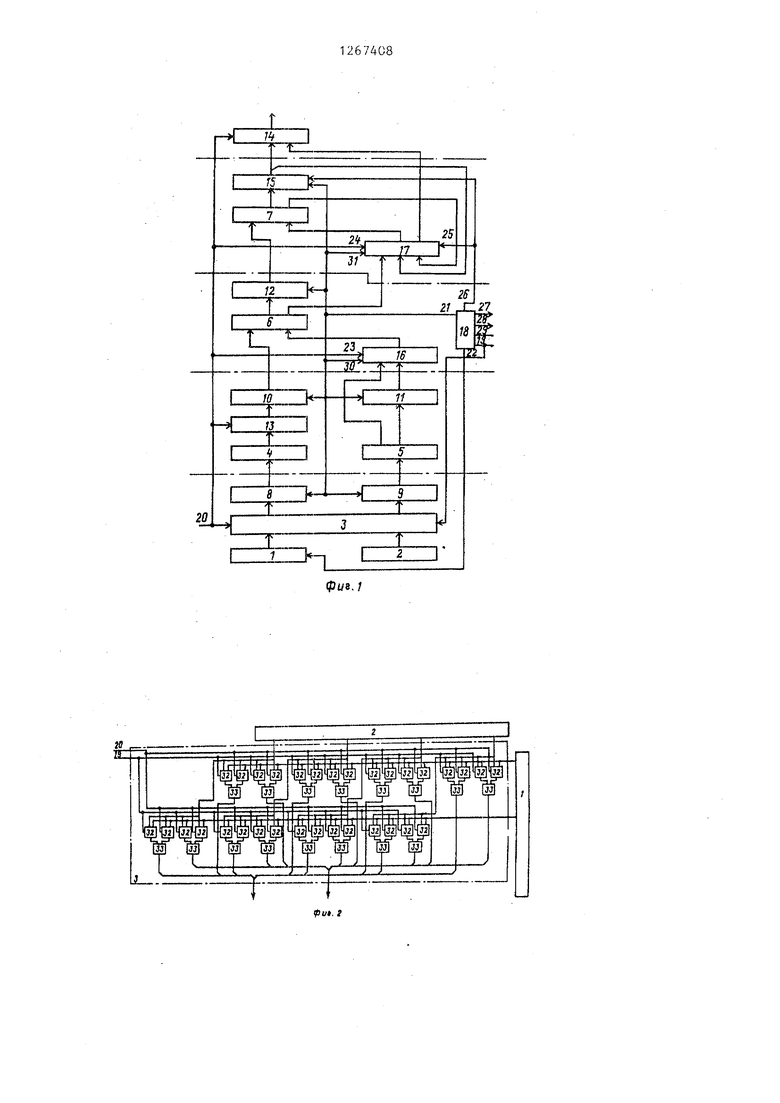

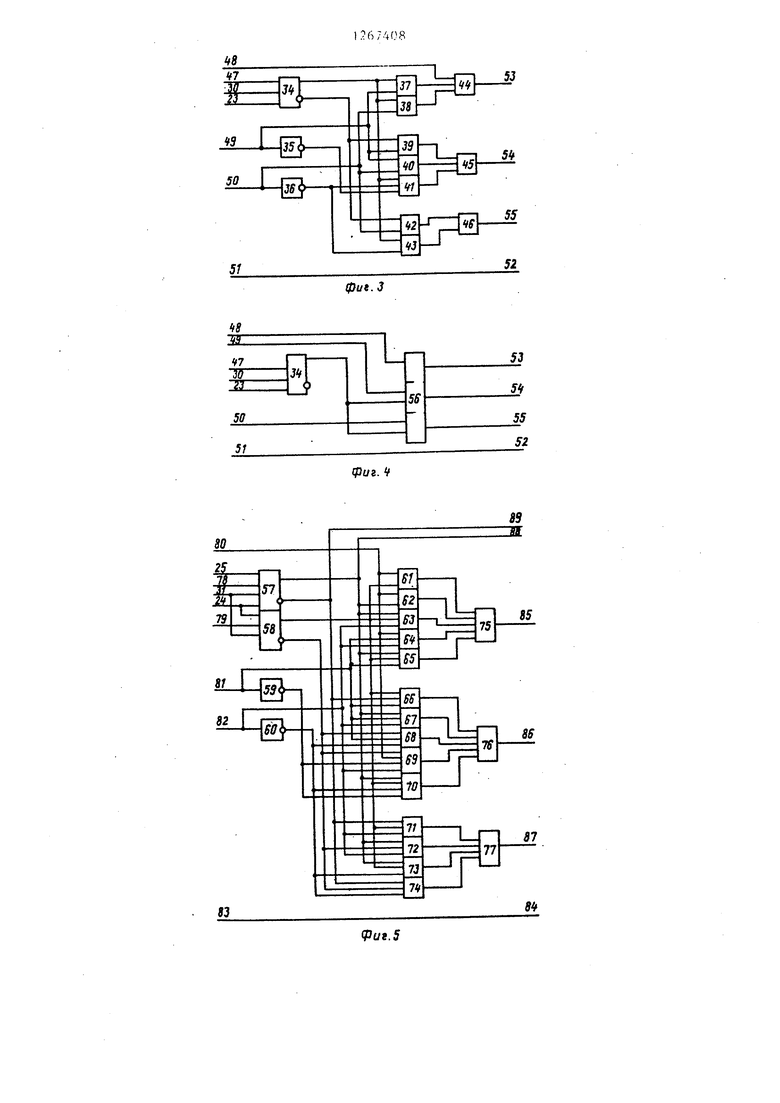

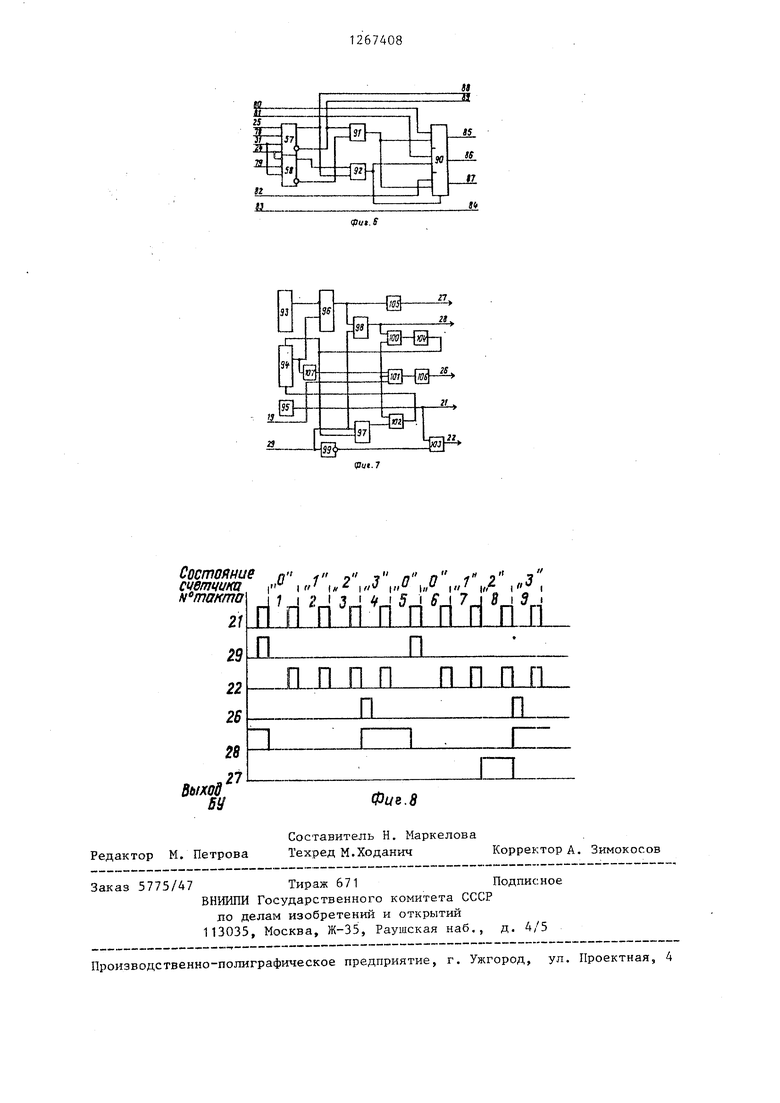

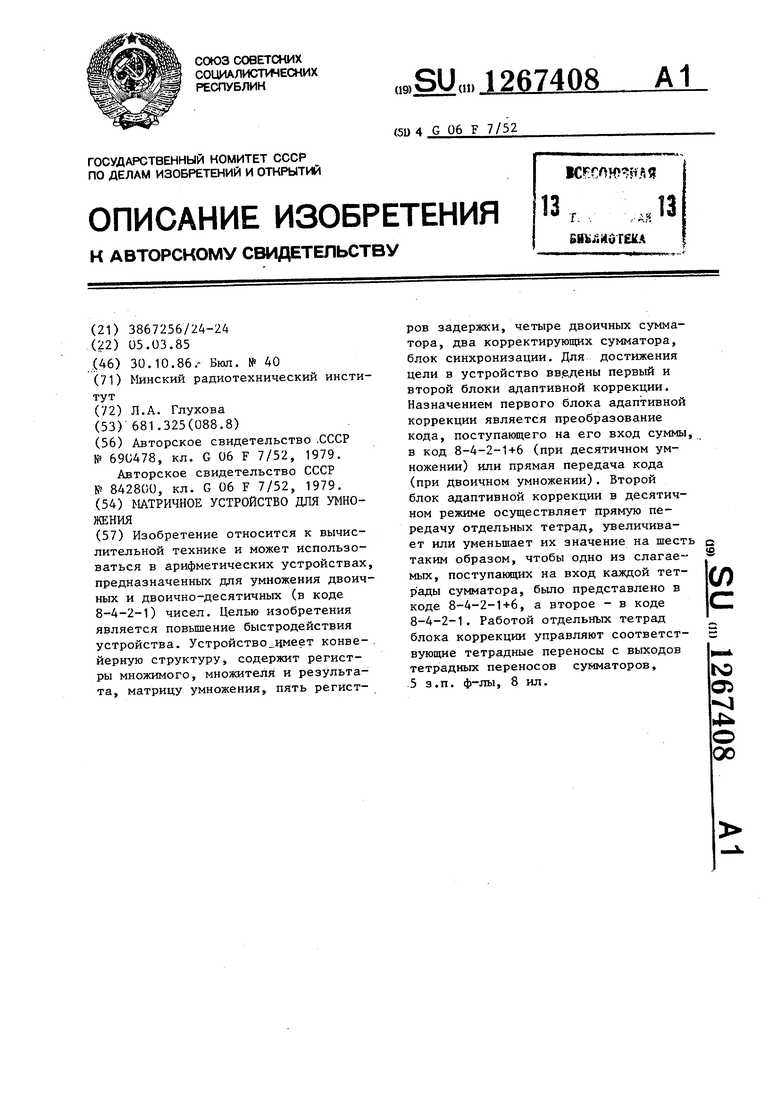

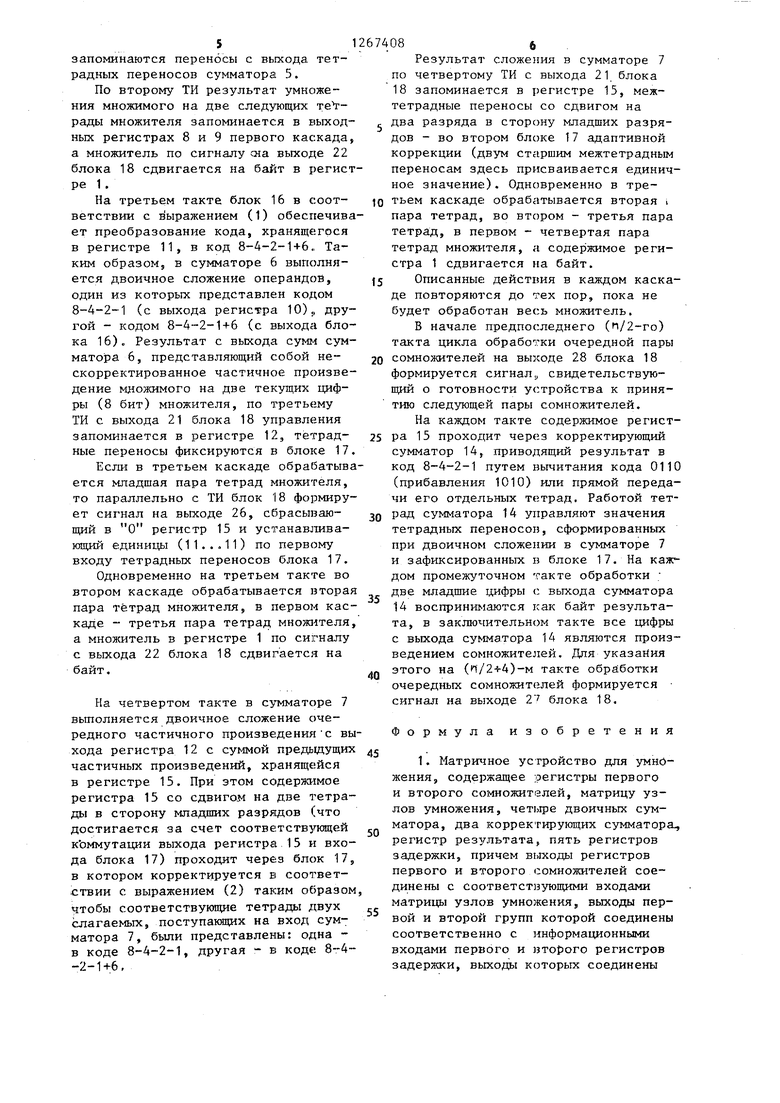

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах предназначенных для умножения двоичных и двоично-десятичных чисел, пред ставленных кодом 8-4-2-1. Цель изобретения - повгэппение быст родействия устройства. На фиг, 1 показанасхема матрично го устройства для умножения| на фиг. 2 - коммутация выходов регистро сомножителей с элементами памяти мат рицы умножения; на фиг, 3 и 4 - варианты выполнения первого блока адап тивной коррекции; на фиг. 5 и 6 варианты реализации второго блока адаптивной коррекции; на фиг, 7 схема блока синхронизации; на -Аиг 8 - временная диаграмма управля ющих сигналов. Матричное устройство для умножения (фиг. 1) содержит регистр 1 первого сомножителя, регистр 2 второго сомножителя, матрицу 3 Узлов умножения, двоичные сумматоры 4-7,, регистры 8-12 задержки, корректирующие сумматоры 13 и 14, регистр 15 результата, первый и второй блоки 16 и 17 адаптивной коррекции, блок 18 синхронизации, входы 19 и 20 раз решения двоично-десятичного и двоичного умножения устройстба, тактирующий выход 21 блока синхронизации, выход 22 управления сдвигом блока 18, входы 23 и 24 установки в О блоков 16 и 17, вход 25 установки в 1 блока 17, установочньш выход 26 блока 18, выход 27 разрешения выдачи результата блока 18, выход 28 разрешения приема блока 18, вход 29 приема устройства, тактирующие входы 30 и 31 блоков 16 и 17. Матрица 3 умножения (фиг, 2) иден тична известной матрице умножения и состоит из четырех групп элем:ентов 32 памяти (с общим количеством элементов 8п ) и элементов ИЛИ 33. На фиг. 3 приведен первый вариант схемной реализации. J-и тетрады блока. 16. Блок содерйшт триггер 34, первьй и второй элементы НЕ 35 и 36, элементы И 37-43, первый, второй и третий элементы ИЛИ 44-46, вход 47 -го разряда тетрадных переносов блока 16, информационные входы 48-51 первого, второго, третьего и четвертого разрядов J-и тетрады блока 16, выходы 52-55 четвертого, первого. второго и третьего разрядов суммы -и тетрады блока 16. На фиг. 4 приведен второй вариант схемной реализации J-и тетрады блока 16. Блок содержит двоичный трехразрядный сумматор 56. На фиг. 5 приведен первый вариант схемной реализации -и тетрады блока 17. Блок содержит первый и второй триггеры 57 и 58, первый и второй элементы НЕ 59 и 60, элементы И 61-74, первый, второй и третий элементы ШШ 15-11, входы 78 и 79 ,3-х разрядов первого и второго тетрадных переносов, информационные входы 80-83 первого, второго, третьего и четвертого разрядов J -и тетрады блока 17, выходы 84-87 четвертого,первого,второго и третьего разрядов суммы S-и тетрады блока 17, прямой и инверсный выходы 88 и 89 J-го разряда тетрадного переноса блока 17, На фиг. 6 приведен второй вариант схемной реализации -й тетрады блока 17. Блок содержит двоичный трехразрядный сумматор 90, первый и второй элементы И 91 и 92, В состав блока 18 синхронизации (фиг. 7) входят регистр 93 тактов, счетчик 94 импульсов, генератор 95 импульсов, блок 96 сравнения, второй и первый триггеры 97 и 98, элемент НЕ 99, элементы И 100-103, элементы 104-106 задержки и дешифратор 107. Работу блока управления поясняет временная диаграмма, представленная на фиг. 8. Временная диаграмма изображена для случая,, когда р 8. В исходном состоянии в регистр 93 занесено значение (у- -1), счетчик 94 импульсов и триггер 97 обнулены, триггер 98 установлен в 1. Работа устройства начинается по приходу внешнего сигнала на вход 29 приема. По его переднему фронту триггер 98 сбрасывается. По заднему фронту данного сигнала в регистры 1 и 2 принимаются сомножители, а триггер 97 устанавливается в 1. Назначением первого блока 16 адаптивной коррекции (фиг. 3 и 4) является преобразование кода, поступающего на его информационный вход, в код 8-4-2-1+6 (при десятичном умножении) или прямая передача кода (при двоичном умножении). Работой отдельных тетрад блока 16 управляют соответствукицие тетрадные переносы с выхода тетрадных переносов сумматора вход 20 устройства. Каждая тетрада блока 16 функционирует в соответствии с выражением: Г х, если Д . Hj 0; Ix +6,если Д IIj 1, где у- - значение на выходе сумм iтетрады блока 16; значение на входе сумм J-и тетрады блока 16; значение переноса из J-й. тетрады, поступившее в пре дыдущем такте- работы на вход тетрадного переноса блока 16 и зафиксированное в нем; значение сигнала на входе 19 разрешения двоично-деся тичного умножения. При Д 1 на входе 19 присутствует единичный уровень, на входе 20 - ну левой. Выполняется двоично-десятичное умножение. В противном случае выполняется двоичное умножение. Второй блок 17 адаптивной корре Ции в десятичном режиме осуществляе прямую передачу отдельных тетрад содержимого регистра 15, увеличивае или уменьшает их значение на шесть Этаким образом, чтобы одно из слагае мых, поступающих на вход каждой тет рады сумматора 7, было представлен в коде 8-А-2-1+6, а второе - в коде 8-4-2-1. Работой отдельных тетрад блока 17 управляют соответствующие тетрадные переносы с выходов тетрадных переносов сумматоров 6 и 7, вход 2С устройства. Каждая тетрада блока 17 функционирует в соответствии с выражением: г- если Д+( +11 i ) 1; +6, если Д-П, 1; LX -6, если Д- n,j-nji 1, где Z - значение на выходе сумм J-и тетрады блока 17; значение на информационном входе J-й тетрады блока 17; П., n.j- значения переноса из J-й тетрады, поступившие в предыдущем такте работы соотве ственно на первый и второй входы тетрадного переноса блока 17 и зафиксированное в нем. Устройство работает в десятичном или двоичном режиме. Перемножение каждой пары сомножителей начинается по приходу сигнала на вход блока 29 блока 18. По данному сигналу независимо от режима работы (двоичный или десятичный) множитель устанавливается в регистре 1, множимое - в регистре 2. На первом такте в матрице 3 выполняется умножение содержимого регистра 2 на содержимое двух младших тетрад регистра 1. Промежуточные результаты перемножения тетрад сомножителей по первому тактовому импульсу (ТИ), формируемому на выходе 21 блока 18, запоминаются в регистрах 8 и 9, причем в одном из данных регистров запоминаются все старшие тетрады (переносы) тетрадных произведений, поступающие на соответствующий выход матрицы 3, а в другом - все младшие тетрады (остатки) тетрадных произведений с второго выхода матрицы 3 (фиг. 1 и 2) Одновременно с этим по сигналу на выходе 22 блока 18 в регистре выполняется сдвиг множителя на две тетрады (байт) в сторону младших разря-дов. В освободившиеся тетрады при этом заносятся О. Таким образом, v на следующем такте в первом каскаде будет вьтолняться умножение множимого на следующую пару тетрад множителя. На втором такте содержимое регистров 8 и 9 поступает соответственно на на входы сумматоров 4 и 5, в которых выполняется сложение отдельных тетрад переносов и остатков в соответствии с их весами. При этом на один из входов данных сумматоров в десятичном режиме тетрады поступают в коде с избытком шесть (8-4-2-1+6), в котором они хранятся в матрице 3. Результат с выхода сумматора 4 ч проходит через корректирующий сумма тор 13, где преобразуется в код 8-4-2-1 путем вычитания кода 0110 (прибавления 1010) в тех тетрадах, где при двоичном сложении отсутствовал тетрадный перенос. По второму ТАКТОВОМУ импульсу ТИ, появляющемуся на выходе 21 блока 18, скорректированный результат запоминается в регистре 10. Одновременно результат,.сформированный сумматором 5, запоминается в регистре 11 (без коррекции). При этом в первом блоке 16 адаптивной коррекции по сигналу на входе 30 S запоминаются переносы с выхода тетрадных переносов сумматора 5. По второму ТИ результат умножения множимого на две следующих тетрады множителя запоминается в выходных регистрах 8 и 9 первого каскада, а множитель по сигналу сна выходе 22 блока 18 сдвигается на байт в регист ре 1 . На третьем такте блок 16 в соответствии с выражением (1) обеспечива ет преобразование кода, хранящегося в регистре 11, в код 8-4-2-1+6,, Таким образом, в сумматоре 6 выполняется двоичное сложение операндов, один из которых представлен кодом 8-4-2-1 (с выхода регистра 10),, другой - кодом 8-4-2-1+6 (с выхода блока 16). Результат с выхода сумм сумматора 6, представляющий собой нескорректированное частичное произведение мложимого на две текущих цифры (8 бит) множителя, по третьему ТИ с выхода 21 блока 18 управления запоминается в регистре 12, тетрадные переносы фиксируются в блоке 17 Если в третьем каскаде обрабатыва ется младшая пара тетрад множителя, то параллельно с ТИ блок 18 формирует сигнал на выходе 26, сбрасывающий в О регистр 15 и устанавливающий единицы (11...11) по первому входу тетрадных переносов блока 17. Одновременно на третьем такте во втором каскаде обрабатывается вторая пара тетрад множителя, в первом каскаде - третья пара тетрад множителя а множитель в регистре 1 по сигналу с выхода 22 блока 18 сдвигается на байт. На четвертом такте в сумматоре 7 выполняется двоичное сложение очередного частичного произведенияс вы хода регистра 12 с суммой предащущих частичных произведений, храняще йся в регистре 15. При этом содержимое регистра 15 со сдвигом на две тетрады в сторону младших разрядов (что достигается за счет соответств тощей кЪммутации выхода регистра 15 и входа блока 17) проходит через блок 17, в котором корректируется в соответствии с выражением (2) тавгим образом чтобы соответствующие тетрады двух слагаемых, поступающих на вход сумматора 7, были представлены: одна в коде 8-4-2-1, другая - в коде 8-4-2-1+6, 086 Результат сложения в сумматоре 7 по четвертому ТИ с выхода 21, блока 18 запоминается в регистре 15, межтетрадные переносы со сдвигом на два разряда в сторону младших разрядов - во втором блоке 17 адаптивной коррекции (двум старшим межтетрадным переносам здесь присваивается единичное значение). Одновременно в третьем каскаде обрабатывается вторая i пара тетрад, во втором - третья пара тетра:д, в первом - четвертая пара тетрад множителя, а содержимое регистра 1 сдвигается на байт. Описанные действия в каждом каскаде повторяются до тех пор, пока не будет обработан весь множитель. В начале предпоследнего (п/2-го) такта цикла обработки очередной пары сомножителей на выходе 28 блока 18 формируется сигнал,, свидетельствующий о готовности устройства к принятию следующей пары сомножителей. На каждом такте содержимое регистра 15 проходит через корректирующий сумматор 14 J приводящий результат в код 8-4-2-1 путем вычитания кода 0110 (прибавления 1010) или прямой передачи его отдельных тетрад. Работой тетрад сумматора 14 управляют значения тетрадных переносов, сформированных при двоичном сложении в сумматоре 7 и зафиксированных н блоке 17. На каж дом промежуточном такте обработки ; две младшие цифры с выхода сумматора 14 воспринимаются как байт результата, в заключительном такте все цифры с выхода сумматора 14 являются произведением сомножителей. Для указания этого на (И/2+4)-м такте обработки очередных сомножителей формируется сигнал на выходе блока 18, Формула изобретения 1. Матричное устройство для умножения, содержащее регистры первого и второго сомножителей, матрицу узлов умножения, четьфе двоичных сумматора, два корректирующих сумматора регистр результата, пять регистров задержки, причем В1 гходы регистров первого и второго сомножителей соединены с соответствующими входами матрицы узлов умножения, выходы первой и второй групп которой соединены соответственно с информационными входами первого и второго регистров задержки, выходы которых соединены соответственно с входами первого и второго двоичных сумматоров, выход первого двоичного сумматора соединен с входом первого корректирующего сум матора, выход которого соединен с ин формационным входом третьего регистра задержки, выход которого соединен с первым информационным входом третьего двоичного сумматора, выход суммы второго двоичного сумматора со единен с информационным входом четвертого регистра задержки, выход пятого регистра задержки соединен . с первым информационным входом четвертого двоичного сумматора, вход задания режима двоично-десятичного умножения матрицы узлов умножения является входом разрешения двоичнодесятичного умножения устройства, вход задания режима двоичного умноже ния матрицы узлов умножения является входом разрешения двоичного умножения устройства и соединен с входами синхронизации первого и второго корректирующих сумматоров, отличающееся тем, что, с целью повьппения быстродействия устройства, в неговведены первьй и второй блоки адаптивной коррекции, содержащие (п -1)и(п+1)тетрад соответственно, где и- разрядность сомножителей, и блок синхронизации, причем входы установки в О первого и второго блоков адаптивной коррекции соединены с входом синхронизации второго корректирующего сумматора, информационный вход которого соединен с вькодом регистра результата, выход старших тетрад которого соединен с информационньв входом второго блока адаптивной коррекции, выход суммы которо го соединен с вторым информационным входом четвертого двоичного сумматора, выходы суммы и тетрадных переносов которого соединены соответственно с информационным входом регистра результата и с первым входом тетрадных переносов второго блока адаптивной коррекции, второй вход тетрадных переносов которого соединен с выходом тетрадных переносов третьего двоичного сумматора, вьгход суммы которого соединен с информационным входом пятого регистра задержки, выход тетрадных переносов второго двоичного сумматора соединен с входом тетрадных переносов первого блока адаптивной коррекции, информационный вход которого соединен с выходом чет 1 088 вертого регистра задержки, выход первого блока адаптивной коррекции соединен с вторым информационным входом третьего двоичного сумматора, выход тетрадных переносов второго блока адаптивной коррекции соединен с входом тетрадных переносов второго корректирующего сумматора, тактирующий: выход блока синхронизации соединен с тактирующими входами первого, второго, третьего, четвертого и пятого регистров задержки, с тактирующим входом регистра результата и тактирующими входами первого и второго блоков адаптивной коррекции,выход управления сдвигом блока синхронизации роединен с входом разрешения сдвига регистра множителя, вход разрешения двоично-десятичного умножения устройства соединен с входом режима блока синхронизации, установочный выход которого соединен с входом установки в 1 второго блока адаптивной коррекции и входом установки в С регистра результата, вход приема устройства является входом приема блока синхронизации. 1, о т л и 2. Устройство по п, что блок синчающееся тем. хронизации устройства содержит регистр тактов, счетчик импульсов, ге-нератор импульсов, блок сравнения, два триггера, элемент НЕ, четыре элемента И, три элемента задержки и дешифратор, причем группа выходов регистра тактов соединена с первой ; группой входов блока сравнения, вторая группа входов которого соединена с группой выходов счетчика импульсов и группой входов дешифратора, выход которого соединен с первым входом , первого элемента И, выход которого соединен с входом первого элемента задержки, выход которого является установочным выходом блока, вход приема блока является входом элемента НЕ и соединен с входами установки в О и в 1 соответственно первого и второго триггеров, выход блока сравнения соединен с входом установки первого триггера и входом второго ::. -, элемента задержки, выход которого является выходом разрешения выдачи результата, выходы первого и второго триггеров соединены с первыми входами соответственно второго и третье- .го элементов И, выход генератора импульсов соединен с первым входом четвертого и вторыми входами первого. второго и третьего элементов И и является тактирующим выходом блока, вы ход первого триггера является выходо разрешения приема блока, выход второ го элемента И соединен с входом третьего элемента задержки, выход которого соединен с входами установки в О второго триггера и счетчика импульсов, выход третьего элемента И соединен с входом запуска счетчрска импульсов, вход режима блока соединен с третьим входом первого элемента И, выход элемента НЕ соединен с вторым входом четвертого элемента И выход которого является выходом управления сдвигом блока. 3. Устройство по п. 1, отличающееся тем, что J я тетрада первого блока адаптивной коррекции содержит триггер, два элемента HEs семь элементов И, три элемента ИЛИ, причем информационньш вхо триггера является входом i-ro разряда тетрадных переносов блока, тактирующий вход триггера является тактируюп(им входом блока, вход установки в О триггера является входом устаноЕ;ки в О блока, прямой выход триггера соединен с первыми входами первото, второго, третьего и четвертого элементов И, инверсный выход триггс ра соединен с первыми входами пятого и шестого элементов И, вход первого элемента ИЛИ является информационным входом первого разряда 1-й тетрады блока, информационные второго и третьего разрядов J-й тетрады являются входами первого и второго элементов НЕ соответственно, вход первого элемента НЕ соединен с вторыми входами первого и пятого элементов И и с первьм входом седьмо го элемента И, вход второго элемента НЕ соединен с вторыми входами вто рого, шестого и седьмого элементов И, выход второго элемента НЕ соединен с вторыми входами третьего и чет вертого элементов И, выход первого элемента НЕ соединен с третьим входом третьего элемента И, выходы перврго и второго элементов И соединены с вторьм и третьим входами первого элемента ИЛИ соответственно, вьпсоды третьего, пятого и седьмого элементов И соединены соответственно с пер вым, вторым и третьим входами соответственно второго элемента ИЛИ., выходы четвертого и шестого элементов И соединены с первым и вторьп входам третьего элемента ШШ, выходы первоrOj BToporo и третьего элементов ИЛИ являются выходами первого,второго и тре тьего разрядов суммы --и тетрады блока, информационный вход четвертого разряда суммы J-и тетрады блока является выходом четвертого разряда суммы J-й тетрады блока. 4. Устройство по По 1, о т л и чающееся тем, что i-я тетрада первого блока адаптивной коррекции содер вшт триггер и двоичный трехразрядньш сумматор, причем информационный вход триггера является входом j-ro разряда тетрадных переносов блока, тактирующей вход блока является тактирующи - входом триггера, вход установки в О которого является входом установки в О блока, информационные входы первого, второго и третьего разрядов J-й тетрады блока являются первыми входами двоичного трехразрядного сумматора, выход триггера соединен с вторыми входами второго и третьего разрядов двоичного трехразрядного сумматора, выходы которого являются выходами первого, второго и третьего разрядов суммы J-й тетрады блока, информационный вход четвертого разряда j-й тетрады блока является выходом четвертого разряда сум:у|ы J-й тетрады блока. 5. Устройство по п. 1, о т л ичающееся тем, что j-я тетрада, второго блока адаптивной коррекции содержит дра тр аггера,, два элемента НЕ, четырнадцать элементов И и три элемента ИЛИ, причем тактирующий вход блока является тактирующим входом первого триггера и соединен с тактирующим входом второго триггера, входы J-X разрядов первого и второго тетрадных переносов являются информационными входа -ш соответственно первого и второго триггеров, вход установки в 1 блока является входом установки в 1 первого триггера, вход установки в О которого соединен с входом установки в 1 второго триггера и является входом.установки в ноль блока, первый вход первого элемента И соединен с первыми входами первого, второго, третьего и четвертого элемен7 ов И и является информационным входом первого разряда J-й TeTpaffbi блока, информационные входы второго и третьего разрядов J-й тетрады блока являются входами соответственно первого и второго элементов НЕ, информационный вход четвертого разряда J-й тетрады блока явля ется выходом четвертого разряда суммы J-и тетрады блока, прямой выход первого триггера соединен с первыми входами пятого, шестого, седьмого, восьмого, девятого и десятого элементов И, с вторым входом второго элемента И соответственно и является прямым выходом J-го разряда тетрадны переносов блока, инверсный выход . первого триггера, соединен с первыми входами одиннадцатого,двенадцатого и тринадцатого элементов И и является инверсным выходом i-го разряда тетрадных переносов блока, прямой выход второго триггера соединен с вторыми входами первого, пятого, шестого, восьмого, десятого, одиннадцатого и двенадцатого элементов И, инверсный выход второго триггера соединен с первым входом четырнадцатого и вторыми входами четвертого, девятого и тринадцатого элементов И вход первого элемента НЕ соединен с вторыми входами третьего, седьмого и четырнадцатого и с третьими входами шестого и одиннадцатого элементов И, вход второго элемента НЕ соединен с третьими входами третьего, четвертого, пятого, седьмого, девято го и двенадцатого элементов И, выход первого элемента НЕ соединен с третьим входом восьмого и четвертым вхо дом четвертого элементовИ, выход второго элемента НЕ соединен с третьими входами десятого, тринадцатого и четырнадцатого элементов И и четвертым входом восьмого элемента И, выходы первого, второго, третьего, пятого и шестого элементов И соединены соответственно с первым, вторым, третьим, четвертым и пятым вхо дами первого элемента ИЛИ, выходы четвертого, седьмого, восьмого, оди надцатого и четырнадцатого элементо И соединены соответственно с первьш вторым, третьим, четвертым и пятым входами второго элемента ИЛИ, выходы девятого, десятого, двенадцатого и тринадцатого элементов И соединены соответственно с первым, вторым, третьим и четвертым входами третьего элемента ИЛИ, выходы первого, второго и третьего элементов ИЛИ являются соответственно выходами первого, второго и третьего разрядов суммы J-й тетрады блока. 6. Устройство по п. 1, отличающееся тем, что J-я тетрада второго блока адаптив-ной коррекции содержит два триггера, трехразрядный двоичный сумматор и два элемента И, причем тактирующий вход блока является тактирующим входом первого триггера и соединен с тактирующим входом второго триггера, J -е разряды первого и второго входов тетрадных переносов-являются информационными входами соответственно первого и второго триггеров, вход установки в 1 первого триггера является входом установки в 1 блока, вход установки в О блока является входом установки в первого триггера и соединен с входом установки в 1 второго триггера, информационные входы первого, второго и третьего разрядов J-и тетрады блока являются первыми входами двоичного трехразрядного сумматора, инверсный и прямой выходы первого триггера соединены с первыми входами первого и второго элементов И и являются соответственно инверсным и прямым выходами J-го разряда тетрадных переносов блока, прямой и инверсный выходы второго триггера соединенц соответственно с вторыми входами второго и первого элементов И, выход первого элемента И соединен с вторыми входами первого и третьего разрядов двоичного сумматора, второй вход второго разряда которого соединен с входом переноса двоичного сумматора и с выходом второго элемента И, выходы первого, второго и третьего разрядов двоичного сумматора являются выходами первого, второго и третьего разрядов суммы J-и тетрады блока, информационный вход четвертого разряда J -и тетрады блока является выходом четвертого разряда суммы J-и тетрады блока.

a .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2011 |

|

RU2475812C1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения | 1982 |

|

SU1229757A1 |

| Устройство для умножения | 1985 |

|

SU1262481A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

Изобретение относится к вычислительной технике и может использоваться в арифметических устройствах, предназначенных для умножения двоичных и двоично-десятичных (в коде 8-4-2-1) чисел. Целью изобретения является повышение быстродействия устройства. Устройство цмеет конве- . йерную структуру, содержит регистры множимого, множителя и результата, матрицу умножения, пять регистров задержки, четыре двоичных сумматора, два корректирующих сумматора, блок синхронизации. Для достижения цели в устройство вв.едеиы первый и второй блоки адаптивной коррекции. Назначением первого блока адаптивной коррекции является преобразование кода, поступающего на его вход суммы, в код 8-4-2-1+6 (при десятичном умножении) или прямая передача кода (при двоичном умножении). Второй блок адаптивной коррекции в десятичном режиме осуществляет прямую передачу отдельных тетрад, увеличивает или уменьшает их значение на шесть таким образом, чтобы одно из слагае(Л мых, поступающих на вход каждой тетрады сумматора, было представлено в коде 8-4-2-1+6, а второе - в коде 8-4-2-1. Работой отдельных тетрад блока коррекции управляют соответствующие тетрадные переносы с выходов тетрадных переносов сумматоров, ю 5 з.п. ф-лы, 8 ил. 05 4:;а

ao

25

57

Ж

58

SI

Щ-Л

83

JS.

«5

75

B6

TS

97

77

Sff

Состояние п ч ,// - „ч « ,« , , сметчика if. (2 ,,,J О ,ff ,7 2 „J

N maftmo 2

rlri-ri ri-ri ri ri riri n

гт

v

| Устройство для умножения п-разрядных двоичных кодов | 1976 |

|

SU690478A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-30—Публикация

1985-03-05—Подача