(54) Г ТРИЧНОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Устройство для умножения | 1985 |

|

SU1322266A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Устройство для умножения | 1983 |

|

SU1180881A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

Изобретение относится к вычислительной технике, именно к арифметическим устройствам, и может быть ис пользовано в цифровых вычислительных машинах для умножения десятичных и двоичных чисел. Известно матричное устройство для умножения десятичных чисел, заданных в коде 8,4,2,1, содержащее блок додачи входных сигналов множимого и множителя, входные элементы И с двумя входами, служащие для при ема различных комбинаций битов одного множителя и одного множимого, группу сумматоров для суммирования, сигналов, полученных с матричного устройства, и сигналов переноси, устройство преобразования двоичных выходных сигналов для получения выходного кода 8,4,2,1 1.. Недостаток указанного устройства его функциональная ограниченность, так как оно обеспечивает умножение только десятичных чисел. Известно также устройство для ум ножения сигн;алов, обеспечивающие умножение двух чисел, каждое из корых представлено группой разрядов, (расположенных в порядке возрастания веса.- Произведение формируется посредством двух наборов сумматоров. На первом наборе сумматоров производится формирование отдельных разрядов произведения. Результаты частичных произведений и переносы складываются на втором наборе сумматоров, выходные сигналы которых являются окончательным результатом произведений 2. Однако известное устройство обеспечивает только умножение двоичных, чисел. Наиболее близким к предлагаемому техническому решению является устройство для умножения, содержащее регистр первого сомножителя, регистр второго сомножителя, матрицу умножения, первый и второй сумматоры, причем выходы регистров первого и второго сомножителей соединены с соответствующими входами матрицы умножения 3. Это устройство также имеет ограниченные функциональные возможности, так как обеспечивает умножение только двоичных чисел. Цель изобретения - расширение функциональных возможностей устройства.

Поставленная цель достигается те что матричное устройство для умножения, содержащее регистр первого сомножителя, регистр второго сомножителя, матрицу умножения, первый и второй сумматоры, причем выходы регистров первого и второго сомножителей соединены с соответствующими входами матрицы умножения, содержит третий сумматор, накапливающий сумматор, регистры задержки, корректирующие сумматоры, при этом выходы первой группы матрицы умножения соединены соответственно с входами первого сумматора, выходы второй группы - с входами второго сумматора, выходы суммы и тетрадных переносов первого и второго сумматоров соединены соответственно с входами первого и второго корректирующих сумматоров, входы третьего и четвертого регистров задержки соединены соединены соответственно с выходами первого и второго корректирующих сумматоров, входы первой и второй-групп третьего сумматора соединены соответственно с выходами третьего регистра задержки и выходами третьего корректирующего сумматора, входы которого соединены с соответствующими выходами четвертого регистра задержки, входы четвертого корректирующего регистра задержки и четвертого корректирующего сумматора соединены соответственно с выходами третьего сумматора, а выходы-с входами накапливающего сумматора, выход результата которого является выходом произведения устройства, первый вход управления устройства соединен с входами управления корректирующих сумматоров, матрицы умножения, второй вход управления устройства соединен с соответствующим входом матрицы умножения, а также за счет того, что матрица умножения содержит четыре группы элементов памяти и две группы элементов ИЛИГр при этом входы i-ro (i О,..., п-1, где п - число первого сомножителя) разряда первого сомножителя матрицы соединены соответственно с входами первой группы (1к + 1),.... ,(i + 1)к элементов памйти первой,.,., четвертой групп (к - число разрядов второго сомножителя), входь -го разряда второго сомножителя матрицы соединены с входами второй группы (ik+(j+l) элементов памяти первой,. четвертой групп (,..., к-1) , первый и второй входы г ( i+1) (;i+1)-х элементов ИЛИ первой группы г-номер выхода элемента памяти) соединены соответственно с г-ми выходами (i+l)(j+l)-x элементов памяти первой и второй групп, первый и второй входы ; f (i4 1) ( )-х элементов ИЛИ второй Ъруппы соединены соответственно с г-ми выходами {1+1)Ц+1)элементов памяти третьей и четверто групп, выходы элементов ИЛИ первой и второй групп являются выходами соответствующих групп матриц умножения, первый вход управления матриц умножения соединен с управляющими входами элементов памяти перво и третьей групп, второй вход управления - с управляющими входами элементов памяти второй и четвертой групп.

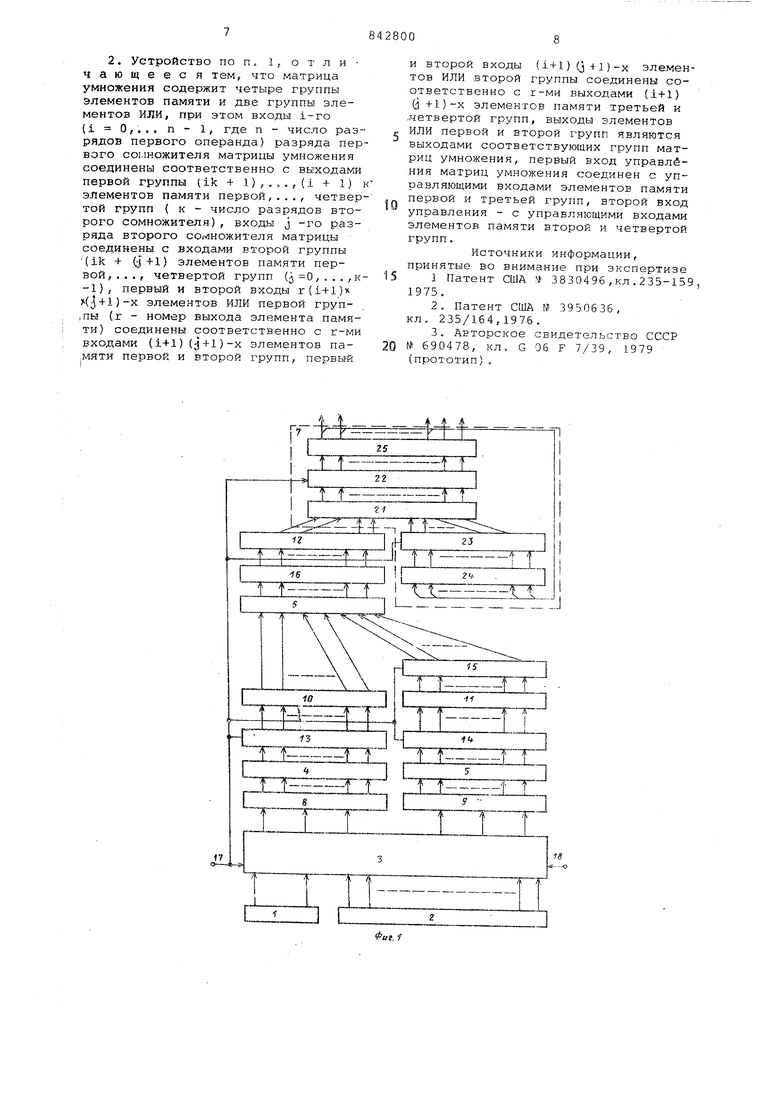

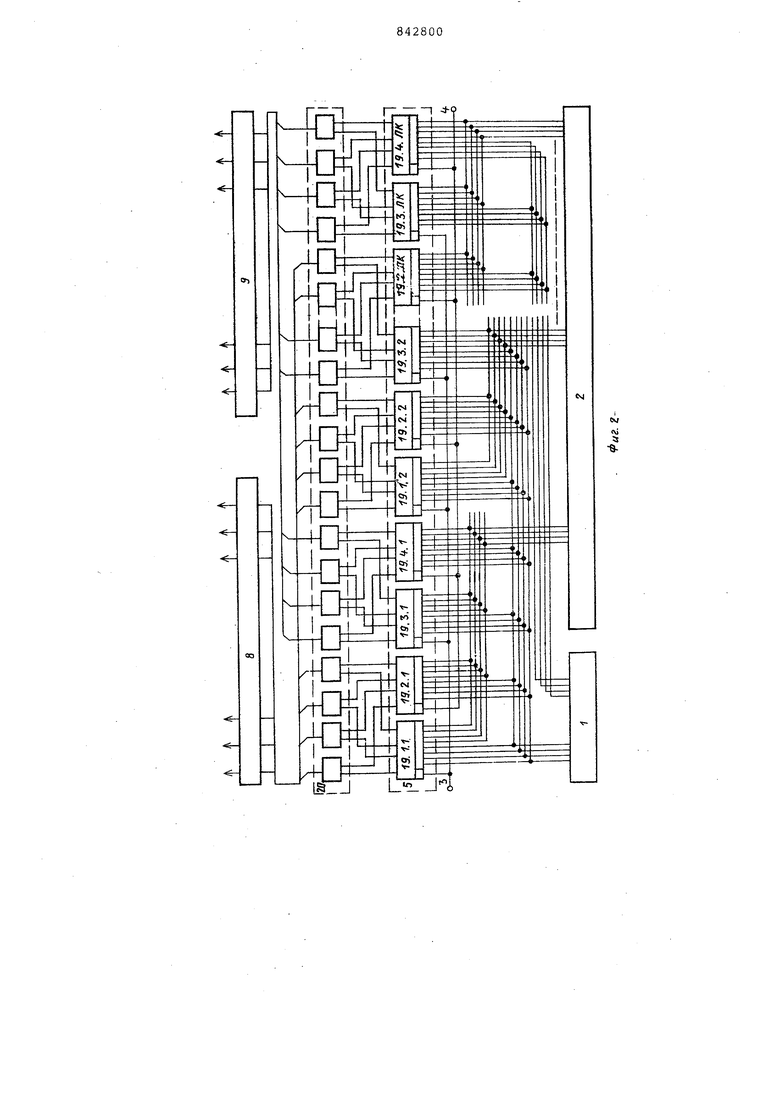

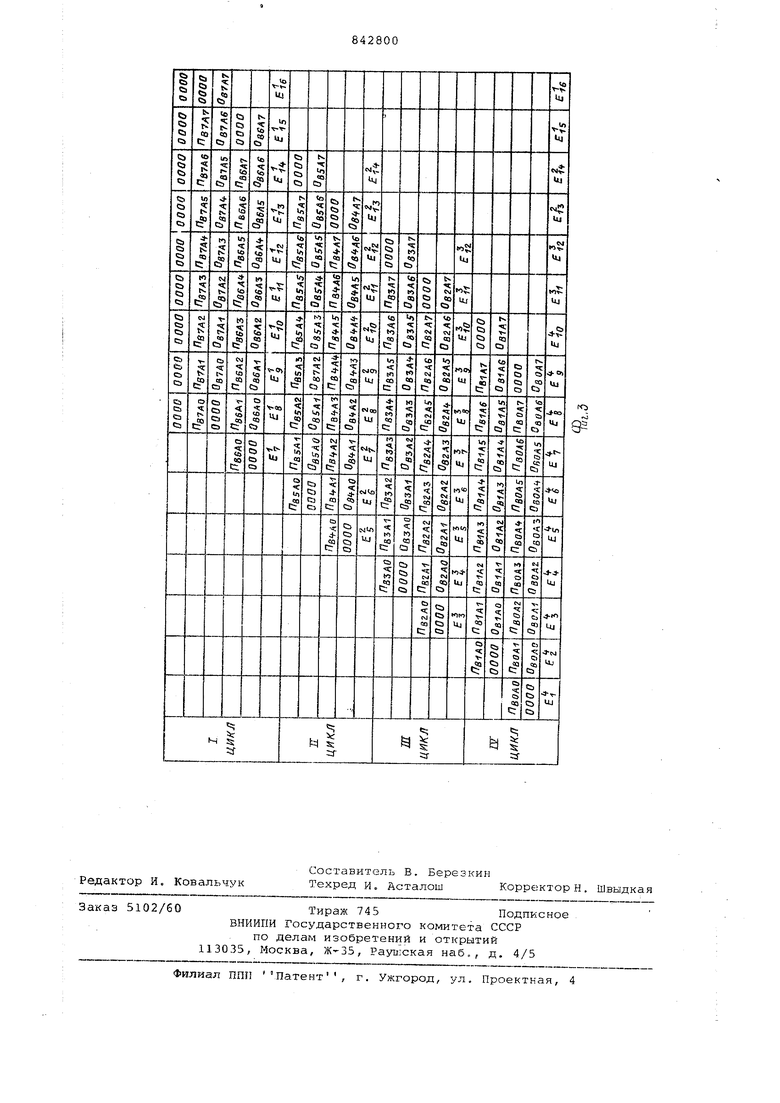

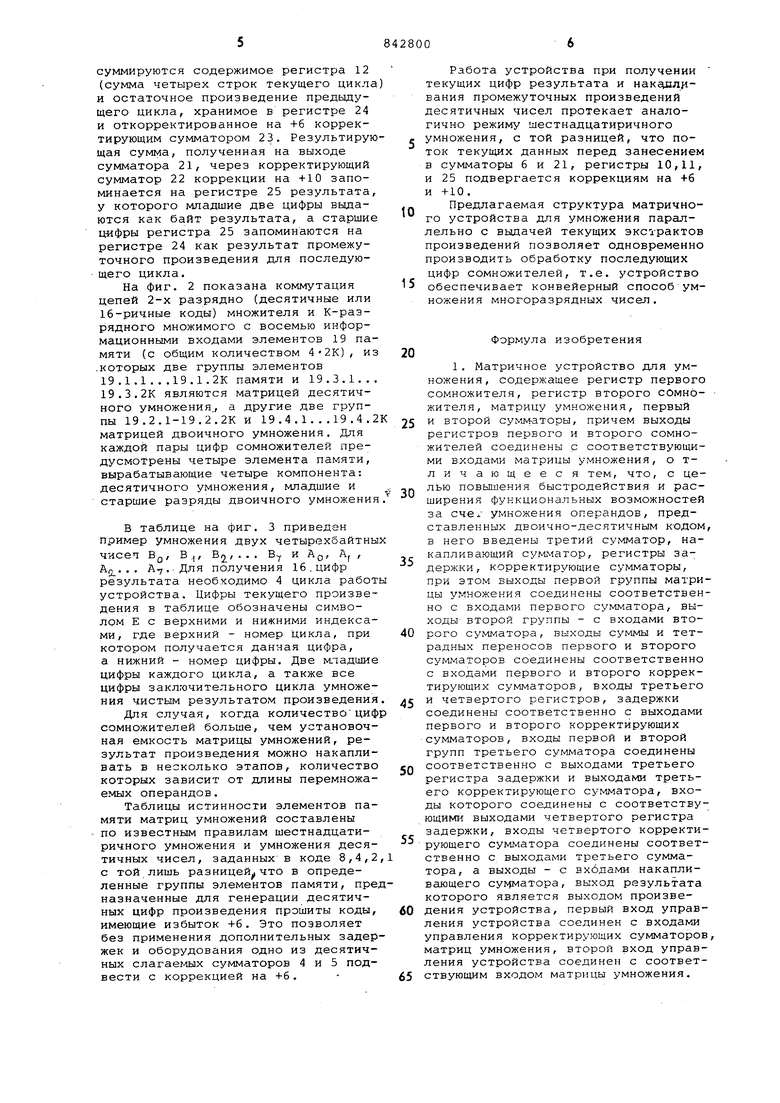

На фиг. 1 показана схема устройства для умножения; на фиг. 2 - коммутация восьмиразрядного множителя и к-разрядного множимого с информационными входами элементов памяти на фиг. 3 - таблица умножения двух 32-разрядных чисел.

Устройство содержит рехистр 1 первого сомножителя, регистр 2 второго сомножителя, матрицу 3 умножения, сумматоры 4 - б,накапливающий су мматор 7, регистры 8-12 задержки, корректирующие сумматоры 13-16, первый и второй входы 17 и 18 управлен устройства, первую группу 19.1.1... I9.1.nk элементов памяти, вторую группу 19.2.1...19.2.nk элементов памятитретью группу 19.3.1...19.3. элементов памяти, четвертую группу 19.4.1...19.4.nk элементов памяти, элементы ИЛИ 20.

Накапливающий сумматор 7 содержи сумматор 21, корректирующие сумматоры 22 и 23, регистр 24- задержки, регистр 25 результата.

Устройство работает в десятичном либо двоичном режимах.

Независимо от режима сомножители устанавливаются в регистрах 1 множителя и 2 множимого. Когда десятичный, активизируются элементы 19.1.1-19.1.KN и 19.3.1-19.3 KN памти посредством сигнала на входе 17, а на входе 18 действует блокирующий потенциал, исключающий выход двоичной информации, из элементов 19.2.1-19.2.KN и 19.4.1-19.4 KN памяти элементов ИЛИ 20.

Промежуточные результаты перемножения цифр поступают на регистры 8 и 9 задержки. Для умножения к-разрядного множимого на две цифры (8 разрядов),множителя сумматоры перво группы выполнены в виде отдельных блоков 4 и 5, на входы которых от регистров 8 и 9 поступают тетрады соответствующих весов остатков и переносов. Затем текущая сумма парных строк в режиме десятичного умножения после коррекции на +10 в сумматорах 13 и 14 запоминается на регистрах 10 и 11 и суммируется ни сумматоре 6,. результаты полученные на входе которого после коррекции в сумматоре 16 запоминаются на регистре 12 в виде суммы четырех строк таблицы умножения. На сумматоре 21 суммируются содержимое регистра 12 (сумма четырех строк текущего цикл и остаточное произведение предыдущего цикла, хранимое в регистре 24 и откорректированное на +б корректирующим сумматором 23. Результиру щая сумма, полученная на выходе сумматора 21, через корректирующий сумматор 22 коррекции на +10 запоминается на регистре 25 результата у которого младшие две цифры выдаются как байт результата, а старши цифры регистра 25 запоминаются на регистре 24 как результат промежуточного произведения для последующего цикла. На фиг. 2 показана коммутация цепей 2-х разрядно (десятичные или 16-ричные коды) множителя и К-разрядного множимого с восемью информационными входами элементов 19 па мяти (с общим количеством 4«2К), и .которых две группы элементов 19.1.1...19.1.2К памяти и 19.3.1.. 19.3.2К являются матрицей десятичного умножения., а другие две группы 19.2.1-19.2.2К и 19.4.1. . .19.4. матрицей двоичного умножения. Для каждой пары цифр,сомножителей предусмотрены четыре элемента памяти, вырабатывающие четыре компонента: десятичного умножения, младшие и старшие разряды двоичного умножени В таблице на фиг. 3 приведен пример умножения двух четырехбайтны В-, и А чисел В, AQ. . . AY.-Для получения 16 , цифр результата необ.ходимо 4 цикла рабо устройства. Цифры текущего произве дения в таблице обозначены символом Е с верхними и нижними индексами, где верхний - номер Цикла, при котором получается данная цифра, а нижний - номер цифры. Две младшие цифры каждого цикла, а также все цифры заключительного цикла умножения чистым результатом произведения Для случая, когда количество циф сомножителей больше, чем установоч ная, емкость матрицы умножений, результат произведения можно накапливать в несколько этапов, количество которых зависит от длины перемножаемых операндов. Таблицы истинности элементов памяти матриц умножений составлены по известным правилам шестнадцатиричного умножения и умножения десятичных чисел, заданных в коде 8,4,2 с той лишь разницей что в определенные группы элементов памяти, пре назначенные для генерации десятичных цифр произведения прошиты коды, имеющие избыток +6. Это позволяет без применения дополнительных задер жек и оборудования одно из десятичных слагаемых сумматоров 4 И 5 подвести с коррекцией на +6. Работа устройства при получении текущих цифр результата и нак длнвания промежуточных произведений десятичных чисел .протекает аналогично режиму шестнадцатиричного умножения, с той разницей, что поток текущих данных перед занесением в сумматоры 6 и 21, регистры 10,11, и 25 подвергается коррекциям на +6 и +10. Предлагаемая структура матричного устройства для умножения параллельно с выдачей текущих экстрактов произведений позволяет одновременно производить обработку последующих цифр сомножителей, т.е. устройство обеспечивает конвейерный способ умножения многоразрядных чисел. Формула изобретения 1. Матричное устройство для умножения, содержащее регистр первого сомножителя, регистр второго сомнржителя, матрицу умножения, первый и второй , причем выходы, регистров первого и второго сомножителей соединены р соответствующими входами матрицы умножения, о тличающееся тем, что, с целью повышения быстродействия и расширения функциональных возможностей за умножения операндов, представленных двоично-десятичным кодом, в него введены третий сумматор, накапливающий сумматор, регистры задержки, корректирующие сумматоры, при этом выходы первой группы матрицы умножения соединены соответственно с входами первого сумматора, выходы- второй группы - с входами второго сумматора, выходы суммы и тетрадных переносов первого и второго сумматоров соединены соответственно с входами первого и второго корректирующих сумматоров, входы третьего и четвертого регистров, задержки соединены соответственно с выходами первого и второго корректирующих сумматоров, входы первой и второй групп третьего сумматора соединены соответственно с выходами третьего регистра задержки и выходами третьего корректирующего сумматора, входы которого соединены с соответствующими выходами четвертого регистра задержки, входы четвертого корректирующего сумматора соединены соответственно с выходами третьего сумматора, а выходы - с вхбдами накапливающего суь матора, выход результата которого является выходом произвеения устройства, первый .вход управения устройства соединен с входами правления корректирующих сумматоров, атриц умножения, второй вход управения устройства соединен с соответтвующим входом матрицы умножения.

и второй входы (i+l)(j+l)-x элементов ИЛИ второй группы соединены соответственно с г-ми выходами (1+1) ti +1)-X элементов памяти третьей и „четвертой групп, выходы элементов ИЛИ первой и второй групп являются выходами соответствующих групп матриц умножения, первый вход управления матриц умножения соединен с управляющими входами элементов памяти первой и третьей групп, второй вход управления - с управляющими входами элементов памяти второй и четвертой групп.

Источники информации, принятые во внимание при экспертизе

1 Патент США № 3830496,кл.235-159, 1975.

40 rfQ

--€

40

Щ

M

I «ЧГ

« :s

Q.

о

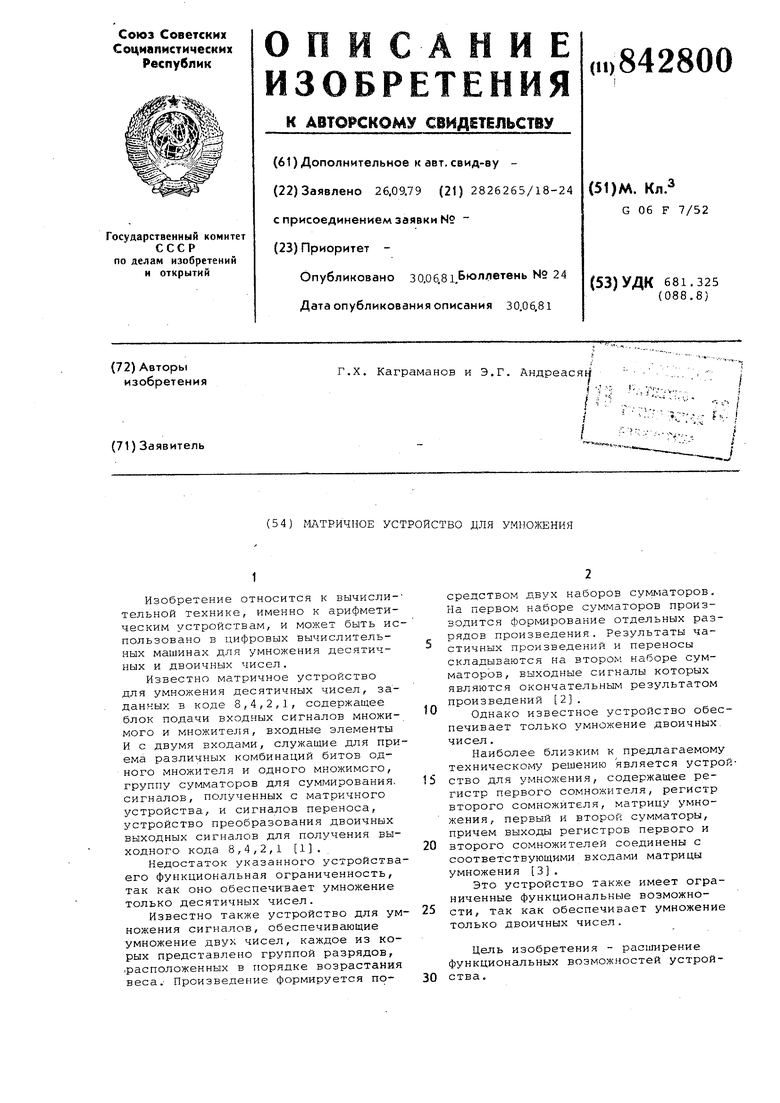

Авторы

Даты

1981-06-30—Публикация

1979-09-26—Подача