to

05

СО

о ел

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дискретной регулировки фазы | 1987 |

|

SU1430906A2 |

| Устройство для дискретной регулировки фазы | 1978 |

|

SU779904A1 |

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| Устройство для дискретной регулировки фазы | 1982 |

|

SU1027639A1 |

| Формирователь последовательности импульсов | 1985 |

|

SU1272480A1 |

| Устройство для измерения временных интервалов /его варианты/ | 1984 |

|

SU1255985A1 |

| Блок управления многофазным импульсным стабилизатором напряжения | 1987 |

|

SU1467704A1 |

| Устройство для контроля резервированного генератора | 1987 |

|

SU1457147A1 |

| Частотно-фазовый компаратор | 1977 |

|

SU794713A1 |

| Устройство программного управления антенной | 1988 |

|

SU1594487A1 |

Изобретение относится к импульсной технике и может быть использовано в системах цифровой обработки сигналов. Целью изобретения является повышение быстродействия .Для достижения цели в устройство введены D-триггеры 5 и 6 и элемент И-ИЛИ 7. Кроме того, устройство содержит 1К-триггеры 1, 3 и 4, счетчик 2. Быстродействие устройства для дискретной регулировки фазы по сравнению с прототипом повышается в 1,5 раза. Кроме того, длительность управляющих сигналов в устройстве для дискретной регулировки фазы может быть произвольной. Снизу она ограничивается минимальной длительностью импульса, необходимой для срабатывания 1К-триггера выбранной эле. ментной базы по входу С, сверху не ограничивается, если нет специальных требований по скорости сдвига фазы ( выходного сигнала. 2 ил. сл

иг/

Изобретение относится к импульсной технике и может быть использовано, в частности, в системах цифровой обработки сигналов.

Цель изобретения - повышение быстродействия устройства.

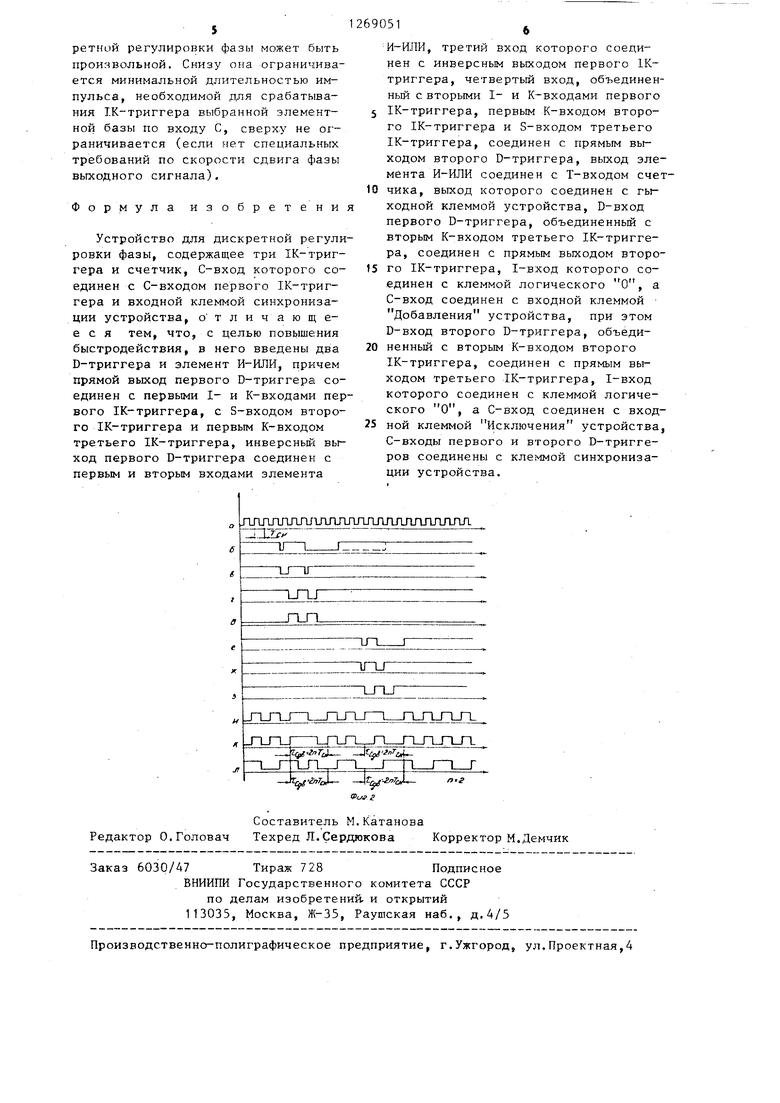

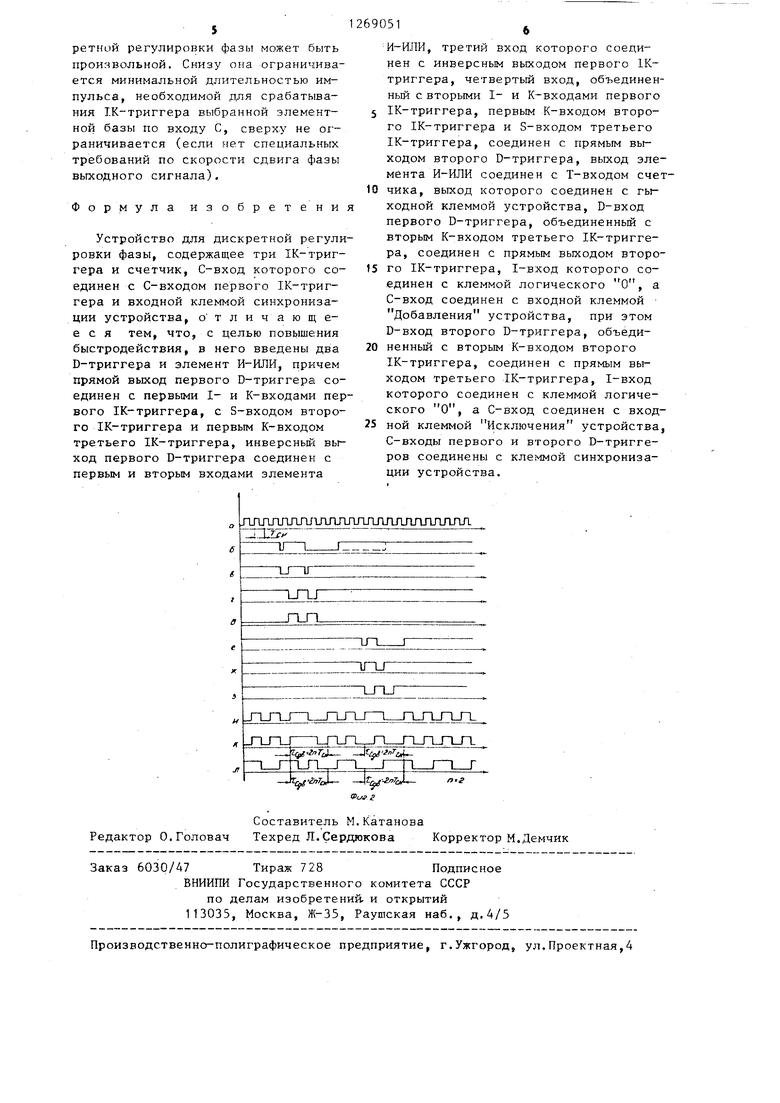

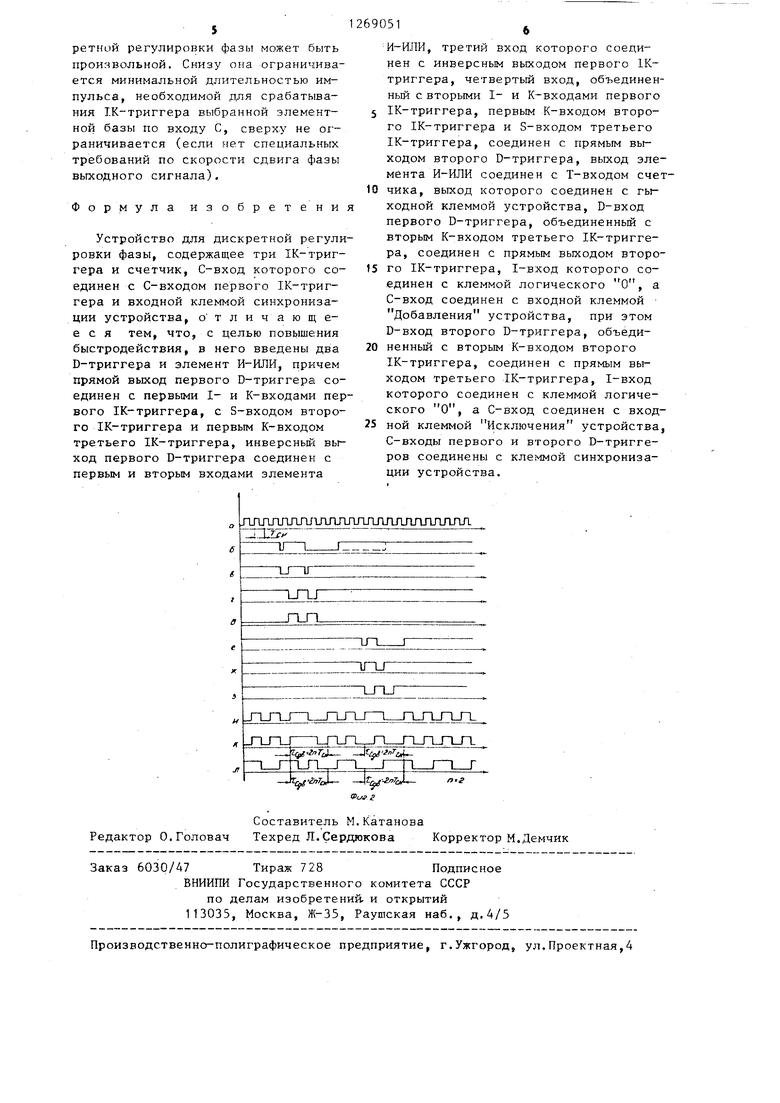

На фиг.1 приведена функциональная схема устройства; на фиг. 2 - )зременные диаграммы работы устройства.

Устройство для дискретной регулировки фазы содержит первый 1К-триггер 1, счетчик 2, второй 3 и третий 4 1К-триггеры, первый 5 и второй 6 D-триггеры, элемент И-ИЛИ 7. Прямой выходр первого D-триггера 5 соединен с первыми I- и К-входами первого . 1К-триггера 1, объединенных с S-BXOдом второго 1К-триггера 3 и первым К-входом третьего 1К-триггера 4,инверсный выход первого D-триггера 5 соединен с первым и вторь1м входами элемента И-ИЛИ 7, третий вход которого соединен с инверсным выходом первого 1К-триггера 1, а четвертый вход, объединенный с вторыми 1-й К-входами первого 1К-триггера 1,первым К-входом второго 1К-триггера 3 и S- входом третьего 1К-триггера 4, соединен с прямым выходом второго В триггера 6, выход элемента ИИЛИ 7 соединен с Т-входом счетчика 2, выход которого соединен с выходной клеммой устройства, первого D-триггера 5, объединенный с вторым К -входом третьего 1К-триггера 4, соединен с прямым выходом второго 1К-триггера 3, 1-вход которого соединен с клеммой логического О, а С-вход соединен с клеммой Добавление устройства, D-ВХОД второго D-триггера 6, объединенный с вторым К-входом второго 1К-триггера 3, соединен с прямым выходом третьего IKтриггера 4, 1-вход которого соединен с клеммой логического О, а С-вход соединен с клеммой Исключение устройства. С-входы первого 1К-триггера 1, счетчика 2, первого 5 и второго 6 D-триггеров объединены и соединены с клеммой Синхронизация устройства. I

Устройство работает следующим образом.

На С-входы первого 1К-триггера 1 счетчика 2, первого 5 и второго 6 D-триггеров поступают синхроимпульсы (эпюра ,фиг.2). Пусть в исходном состоянии на прямых выходах второго 3 и третьего 4 1К-триггеров присутствуют логические 1 (эпюрыЬи ж, фиг.2). При этом на прямых выходах первого 5 и второго 6 D-триггеров также присутствуют логические 1 (эпюры г и J , фиг.2), которые подтверждаются с приходом каждого очередного синхроимпульса и разрешают переключения первого 1К-триггера 1. Устройство

работает как обычный счетчик с коэффициентом деления 2 К. , где Кс коэффициент деления счетчика 2(эпюра Л , фиг. 2, где KCPJ 2).

При подаче на вход Добавление 6Г

(эпюра S )логического О на прямом выходе 1К-триггера 3 в ответ на перепад на его С-входе появляется логический О (эпюра 5 , фиг.2), так как на 1-входе - логический О,на

первом и втором К -входах - логические 1 (эпюры ж и , фиг.2). Логический О с выхода 1К-триггера 3 поступает на второй К -вход 1К-триггера 4, блокируя работу устройства по

входу Исключение е , Очередным синхроимпульсом этот логический О вписывается в D-триггер 5. При этом на прямом вых-оде D-триггера 5 появляется уровень логического О (эпюра г ,фиг.

2), который, поступая на S-вход IKтриггера 3, возвращает его в состояние логической 1 (эпюра Ь, фиг.2), одновременно блокируя устройство по входу Добавление S , а также, поступая на первьй К-вход 1К-триггера 4, продолжает блокировку устройства по входу Исключение е. Следующим синхроимпульсом О-триггер 5 возвращается в исходное состояние, (эпюра

2 ), так как на его D-входе в этот момент уже логическая 1 с выхода 1К-триггера 3 (эпюра 6, фиг,2). Появившаяся на прямом выходе JD-триггера 5 логическая 1 (эпюраЕ ,фиг.

2), поступая на fi-вход 1К-триггера 3 и на второй К-нход IK-триггера 4, разблокирует устройство, разрешая работу по управляющим входам Добавление S и Исключение е- устройство

возвращается в исходное состояние.

Таким образом, на прямом (инверсном) выходе D-триггера 5 в ответ на появление логического О на входе Добавление сГ устройства (эпюра cf , фиг.2) вырабатывается отрицательный (положительный) импульс, длитель1ностью в период с.инхрочастоты , j 3 строго привязанный к ее активным перепадам (эпюра Li , фиг. 2). Отрицательный импульс с прямого выхода D-триггера 5, поступая на пер вые I- и К-входы 1К-триггера 1 (эпю ра 2., фиг. 2), запрещает изменение со стояния 1К-триггера 1 при приходе очередного синхроимпульса (эпюра и фиг.2). Сигнал с инверсного выхода IKтриггера 1 (эпюра и ,фиг.2) поступает на третий вход элемента И-ИЛИ 7, где складывается с положительньм импульсом с инверсного выхода D-триггера 5 (эпюра Э ,фиг.2), поступающим на первый и второй входы элемента И-ИЛИ 7. Полученный в результате это го уровень логической 1 (эпюра к, фиг.2) поступает с выхода элемента И.-ИЛИ 7 на Т-вход счетчика 2, разрешая ему изменять свое состояние при приходе очередного синхроимпульса на С-вход (эпюрал ,фиг.2),.чего не про изошло бы на рассматриваемом такте синхрочастоты в случае, если бы на вход Добавление 5 не был бы подан логический уровень О. Таким образом, в результате подачи логического уровня О на вход Добавление S. фаза выходного сигн ла счетчика (эпюра л ) изменяется (ус коряется) на 2 Кс-г При подаче логического уровня О на вход Исключение е (эпюра е, фиг.2) на прямом выходе 1К-триггера 4 в ответ на перепад на его С-входе появляется логический О (эпюра ж, фиг.2), так как на 1-входе - логический О, на первом и вто ром К-входах - логические 1 (эпюр 6 и г , фиг.2). Логический О с выхода 1К-Триггера 4 поступает на второи К -вход 1К-триггера 5, блоки„„руя работу устройства по входу Добавление 6. Очередным синхроимпульсом этот логический О вписывается в D-триггер 6. При этом на прямом выходе D-триггера 6 появляется уровень логического О (эпюра 3 , фиг. 2), который,поступая на S-вход IKтриггера 4, возвращает его в состояние логической 1 (эпюра Ж ,фиг.2), одновременно блокируя устройство по входу Исключение е , а также, поступая на первый К-вход 1К-триггера 3, продолжает блокировку устройства .по входу Добавление S . 51 j1 Следующим синхроимпульсом D-триггер 6 возвращается в исходное состояние (эпнюра 1 , фиг.2), так как на его D-входе в этот момент уже логическая 1 с выхода 1К-триггера 4 (эпюра , фиг. 2). Появившаяся на прямом выходе D-триггера 6 логичеекая 1 (эпюра , фиг.2).поступая на S-вход 1К-триггера 4 и на второй К-вход 1К-триггера 3, разблокирует устройство, разрешая работу по управляющим входам Добавление с и Исключение е , устройство возвращается в исходное состояние. Таким образом, на прямом выходе D-триггера 6 в ответ на появление логического О на входе Исключение е устройства (эпюра е, фиг.2) вырабатывается отрицательный импульс, длительностью в период синхрочастоты TCH , строго привязанный к ее активным перепадам (эпюра , фиг. 2). Отрицательный импульс с прямого выхода 1)-триггера 6, поступая на вторые I- и К-входы 1К-триггера 1 (эпюра i , фиг.2), запрещает изменение состояния 1К-триггера 1 при приходе очередного синхроимпульса (эпюра и , фиг.2). Сигнал с инверсного выхода IKтриггера (эпюра KI , фиг. 2) поступает на третий вход элемента И-ИЛИ 7, где перемножается с отрицательным импульсом с прямого выхода D-триггера 6 (эпюра 1 , фиг.2), поступающим на четвертый вход элемента И-ИЛИ 7. Полученньш в результате этого уровень логического О (эпирак , фиг.2) поступает с выхода элемента И-ИЛИ 7 на Т- вход счетчика 2, запрещая ему изменять свое состояние при приходе очередного .синхроимпульса на С-вход (эпюра Л , фиг.2), чего не произошло бы на рассматриваемом такте синхрочастоты в случае, если бы на вход Исключение е не бьш бы подан логический уровень О. Таким образом, в результате подачи логического уровня О на вход Исключение е фаза выходного сигнала счетчика 2 (эпюра л фиг.2) изменяется (замедляется) на 27Г/2 Кс Таким образом, быстродействие устройства для дискретной регулировки фазы в 1,5 раза выше, чем у известного. Кроме того, длительность управляющих сигналов в устройстве для дискретной регулировки фазы может быть произвольной. Снизу она ограничивается минимальной длительностью импульса, необходимой для срабатывания 1К-триггера выбранной элементной базы по входу С, сверху не ограничивается (если нет специальных требований по скорости сдвига фазы выходного сигнала).

Формула изобретени

Устройство для дискретной регулировки фазы, содержащее три IK-триггера и счетчик, С-вход которого соединен с С-входом первого 1К-триггера и входной клеммой синхронизации устройства, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия, в него введены два D-триггера и элемент И-ИЛИ, причем прямой выход первого D-триггера соединен с первьми I- и К-входами первого IK-триггера, с S-входом второго 1К-триггера и первым К-входом третьего 1К-триггера, инверсньй выход первого D-триггера соединен с первым и вторым входами элемента

Г1Гшл11ггагг1ЛЛ11Г1Плллшгплллля г И-ИЛИ, третий вход которого соединен с инверсным выходом первого 1Ктриггера, четвертый вход, объединенный с вторыми I- и К-входами первого 1К-триггера, первым К-входом второго 1К-триггера и S-входом третьего 1К-триггера, соединен с прямым выходом второго D-триггера, выход элемента И-ИЛИ соединен с Т-входом счетчика, выход которого соединен с гыходной клеммой устройства, D-вход первого D-триггера, объединенный с вторым К-входом третьего 1К-триггера, соединен с прямым выходом второго 1К-триггера, 1-вход которого соединен с клеммой логического О, а С-вход соединен с входной клеммой Добавления устройства, при этом D-ВХОД второго D-триггера, объединенный с вторым К-входом второго 1К-триггера, соединен с прямым выходом третьего 1К-триггера, 1-вход которого соединен с клеммой логического О, а С-вход соединен с входной клеммой Исключения устройства, С-входы первого и второго D-триггероБ соединены с клеммой синхронизации устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для дискретной регулировки фазы | 1978 |

|

SU779904A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-11-07—Публикация

1985-07-23—Подача