Изобретение относится к импульсной техннке и может быть использовано, в частности, в системах цифровой обработки сигналов.

Известны устройства дискретной регулировки фазы, содержащие счетчик, схему сравнения кодов и схему задания кода. Изменение фазы выходных импульсов достигается изменением кода в схеме задания кода tlj.

Недостатком известных устройств является низкое быстродействие, обусловленное значительной задержкой . срабатывания сложной логической схемы сравнения кодов, что не позволяет реализовать устройство с быст родействием, максимально достижимым при выбранной элементной базе.

Наиболее близким к предлагаемому является устройство дискретной регулировки фазы, содержащее три ЗК. -триггера/ счетчик, элемент блоКировки L2I.

:Недостаток такого устройства состоит в невысоком быстродействии. Так, сдвиг фазы на Y дискретов устройство производит за время 1Гсде) Зи1 где Тца период следования синхрсимпульс ов; И - целое i положительное число.

Цель изобретения - повышение бы-стродействия при сдвиге фазы на несколько дискретов.

Поставленная цель достигается тем, что в устройство для дискретной регулировки фазы, содержащее первый,, второй и третий ЭК -триггеры, счетчик и элемент блокировки, причем 3 -входы второго и третьего ЭК -триргеров соединены с шиной логической единицы устройства, К -входы второго и третьего К .-триггеров подключены соответственно к прямому и инверсному выходам первого ЭК -триггера, а прямые выходы второго и третьего Ж -триггеров соединены с соответствующими попарно объединенными первыми и вторыми Э и К -входами первого Ж -триггера, С-вход которог подключен к С-входу счетчика и шине синхронизации устройства, а прямой выход первого ЗК -триггера подключен к управляющему входу счетчика, выход которого соединен с выхоной шиной устройства, введены два RS -триггера и два элемента И, причем :.-входы первого и второго RS -триггеров соединены соответственно с шинами исключения и добавления устройства, R-входы первого и второго R.S.-триггеров подключены к выходу элемента блокировки, прякые выходы первого и второго R5 -триггеров соединены с 5 -входами сортветственно второго и третьего -триггеров, С-входы которых подключены к выходам соответственно первого и второго элементов И, .прякие выходы второго и третьего К -тригг;еров подключены к первым вхддам соответственно первого и второго элементов И, инверсные выходы второго и третьего JK -триггеров соединены соответственно с первым и вторым входами, элемента блокировки, вторые входы первого и второго элементов И подключены к третьему-входу элемента блокировки и шине синхронизации устройства, четвертый вход элемента блокировки соединен с управляющей шиной устройства.

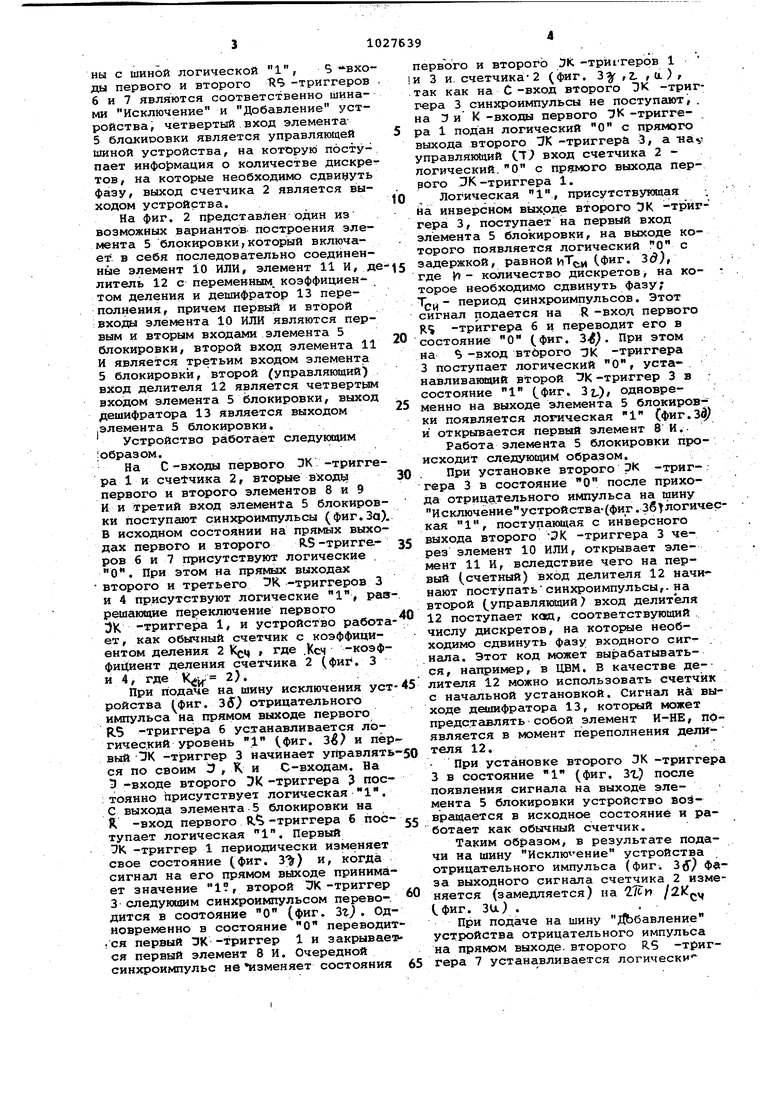

При этом элемент блокировки содержит элементы ИЛИ, И, делитель с переменным коэффициентом деления и дешифратор переполнения, причем первый и второй входы элемента ИЛИ соединены соответственно -с первым и вторым входами элемента блокировки, выход элемента ИЛИ подключен к перво1 входу элемента И, второй вход которого соединен с третьим входом элемента блокировки, выход элемента И подключен к первому входу делителя b переменным коэффициентом делени второй вход которого соединен с четвертым входом элемента блокировки, а выход делителя с переменным коэффициентом деления подключен к входу дешифратора переполнения, выход которого соединен с выходом элемента блокировки, .

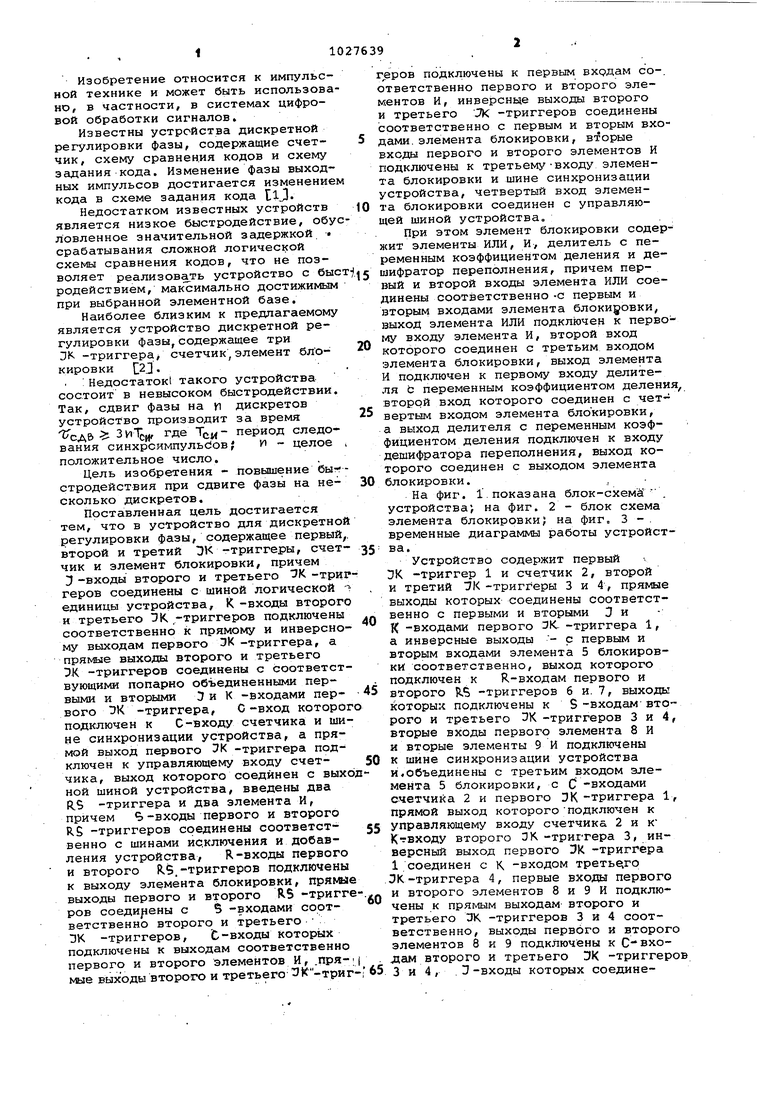

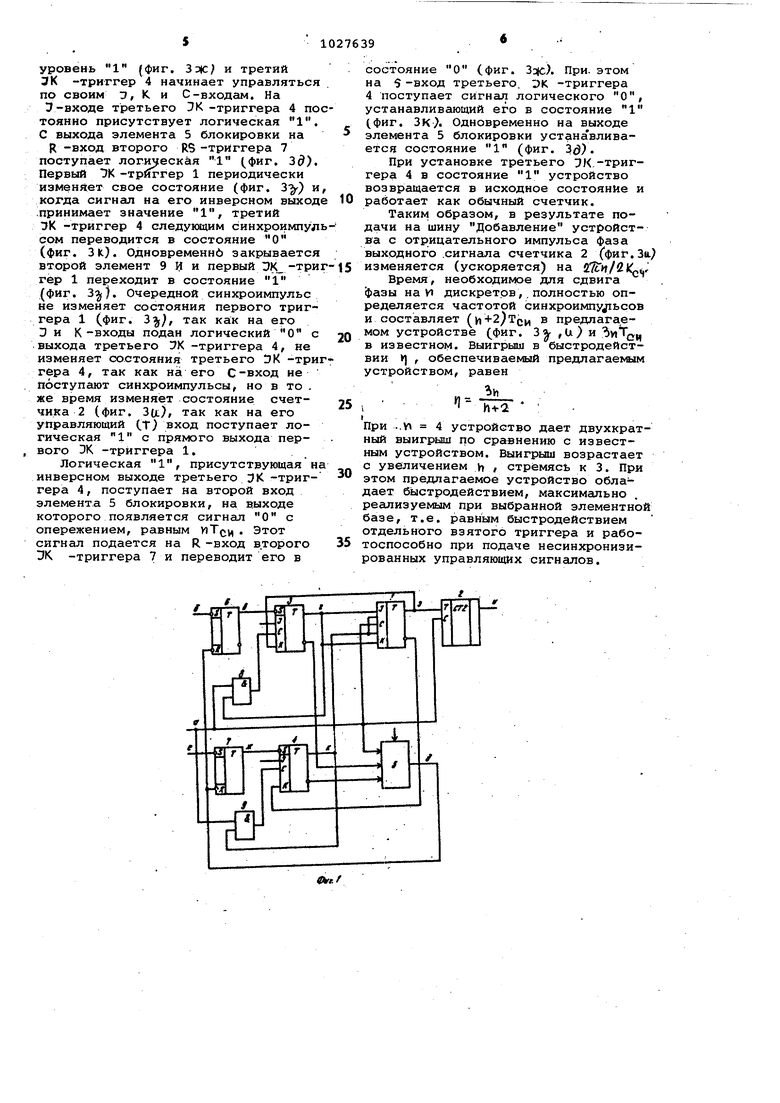

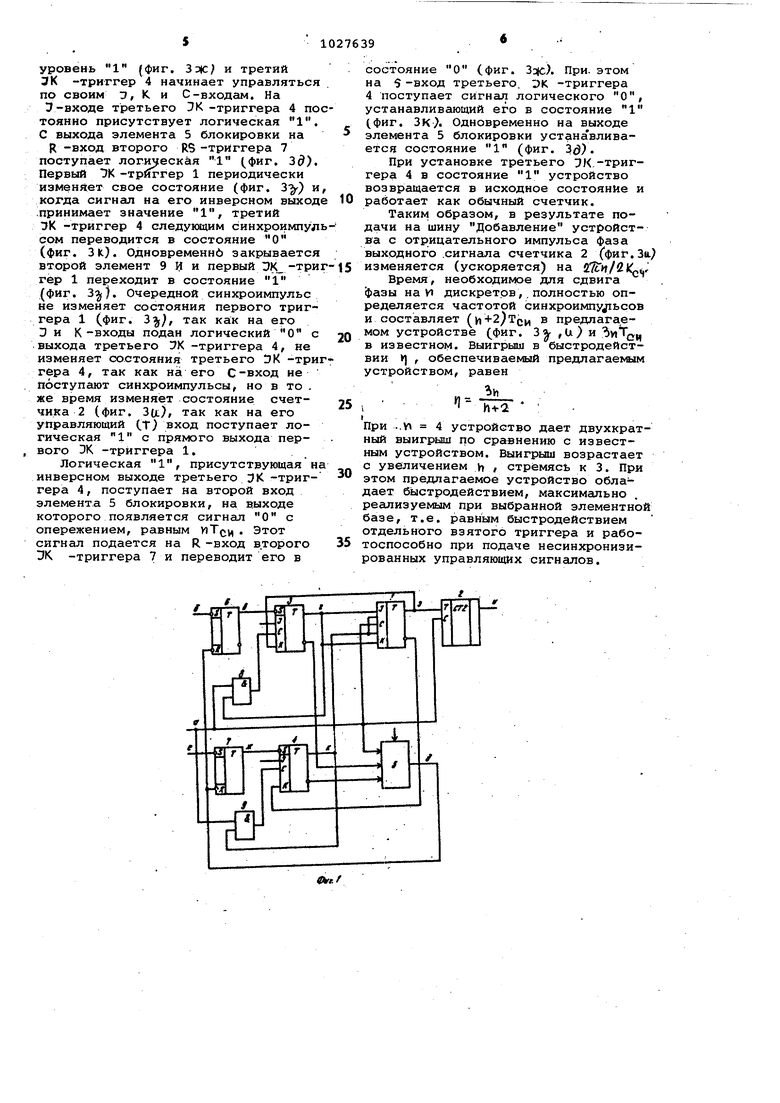

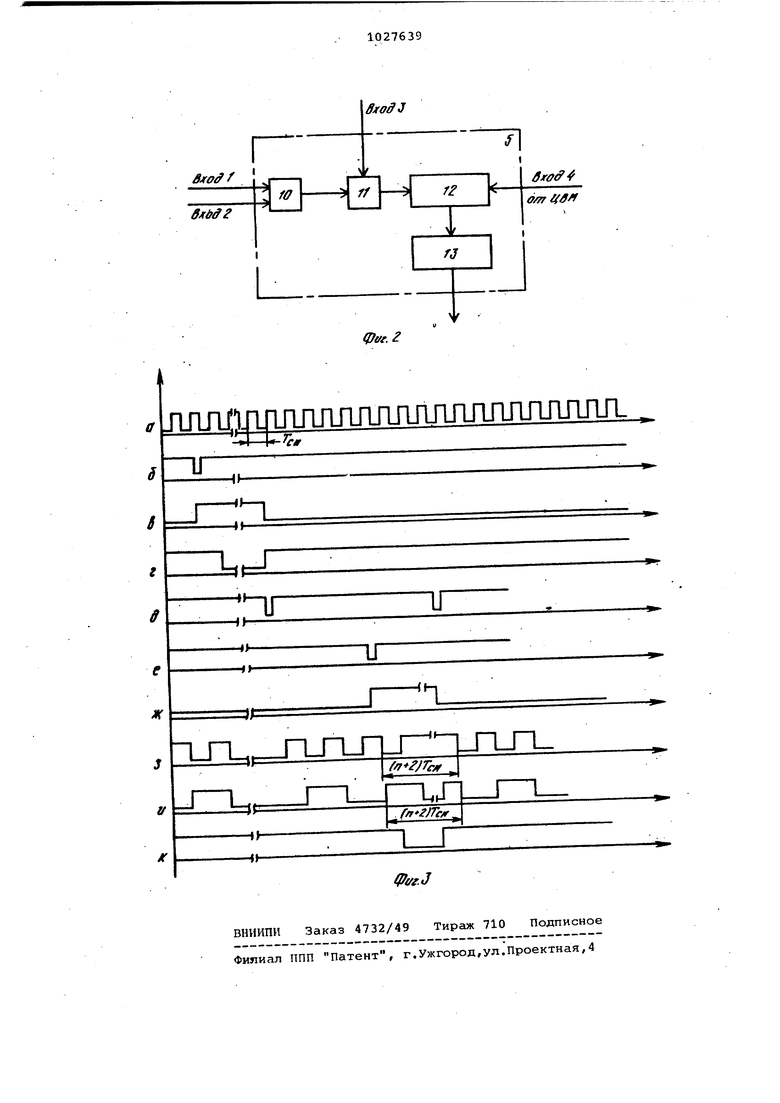

На фиг, 1. показана блок-схема, устройства) на фиг, 2 - блок схема элемента блокировки; на фиг, 3 временные диаграммы работы устройства.

Устройство содержит первый DK -триггер 1 и счетчик 2, второй и третий ЗК -триггеры 3 и 4 , прямые выходы которых соединены соответственно с первыми и вторыми 3 и К -входами первого ЭК- -триггера 1, а инверсные выходы - с первым и вторым входами элемента 5 блокировки соответственно, выход которого подключен к R-входам первого и второго R.S -триггеров 6 и. 7, выходы которых подключены к S -входамвторого и третьего ЭК -триггеров 3 и 4 вторые входы первого элемента 8 И и вторые элементы 9 И подключены к шине синхронизации устройства и.объединены с третьим входом элемента 5 блокировки, с С -входами счетчика 2 и первого DK -триггера 1 прямой выход которого подключен к управляющему входу счетчика 2 и к КТВХОДУ второго ЗК -триггера 3, инверсный выход первого ЭК -триггера 1 .соединен с К, -входом третье го ЭК-триггера 4, первые входы первого и второго элементов 8 и 9 И подключены к прямым выходам второго и третьего DK -триггеров 3 и 4 соответственно, выходы первого и второго элементов 6 и 9 подключены к С-входам второго и третьего DK -триггеро 3 и 4, . Э-входы которых соединены с шиной логической 1, S входы первого и второго Ra -триггеров 6 и 7 являются соответственно шинами Исключение и Добавление устройства, четвертый. вход элемента5 блокировки является управляющей шиной устройства, на которую поступает информация о количестве дискретов , на которые необходимо сдвинуть фазу, выход счетчика 2 является выходом устройства. На фиг. 2 представлен один из возможных вариантов построения элемента 5 блокировки,который включает в себя последовательно соединенные элемент 10 ИЛИ, элемент 11 И, де литель 12 с переменным, коэффициентом деления и дешифратор 13 переполнения , причем первый и второй входы элемента 10 ИЛИ являются первым и вторым входами элемента 5 блокировки, второй вход элемента 11 И является третьим входом элемента 5 блокировки, второй (управляющий) вход делителя 12 является четвертым входом элемента 5 блокировки, выход дешифратора 13 является выходом .элемента 5 блокировки. Устройство работает следукжщм образом. На С-входы первого ЗК -триггера 1 и счетчика 2, вторые входы первого и второго элементов 8 и 9 И и третий вход элемента 5 блокиров ки поступают синзфоймпульсы (фиг.Зо) В исходном состоянии на прямых выхо дах первого и второго Я.5-триггеров б и 7 присутствуют логические О. При этом на прямых выходах второго и третьего К -триггеров 3 и 4 присутствуют логические 1, раз решающие переключение первого ЭК -триггера 1, и устройство работ ет , как обычный счетчик с коэффициентом деления 2 , где .Кеч -коэф фициент деления счетчика 2 (фиг. 3 и 4, где К 2). При подаче на шину исключения ус ройства Гфиг. 35} отрицательного импульса на прямом выходе первого R5 -триггера б устанавливается логический уровень 1 (,фиг. Зй и пе вый 1JK -триггер 3 начинает уйравлят ся по своим iJ , К и С-входам. На Э -входе второго ЭК -триггера 3 пос тоянно присутствует логическая 1. С выхода элемента 5 блокировки на R -вход первого R -триггера 6 пос тупает логическая 1. Первый К -триггер 1 периодически изменяет свое состояние (фиг. ) и, когда сигнал на его прямом выходе принима ет значение 1, второй -триггер 3 следующим синхроимпульсом переводится в состояние О (фиг. Зг) . Од новременно в состояние О переводи .ся первый ЭК -триггер 1 и закрывае ся первый элемент 8 И. Очередной синхроимпульс не изменяет состояния первого и второго ЗК -триггеров 1 и 3 и счетчика-2 (фиг. 3,г. ,а)/ так как на С -вход второго ЭК -триггера 3 синхроимпульсы не поступают, . на 3 и К -входы первого ЭК -триггера 1 подан логический О с прямого выхода второго UK -триггера 3, а nav управляю1ций (,) вход счетчика 2 логический.О с прямого выхода первого ЛК -триггера 1. Логическая 1, присутствующая на инверсном выхрде второго ЭК -триггера 3, поступает на первый вход элемента 5 блокировки, на выходе которого появляется логический О с задержкой, равной viT,,, (.Фиг. 3), где И - количество дискретов, на которое необходимо сдвинуть фазуу Трц- период синхроимпульсов. Этот сигнал подается на R -вход первого R -триггера б и переводит его в состояние О (фиг. 3. При этом на -вход втброго DK -триггера 3 поступает логический О, устанавливаюодай второй tJK-триггер 3 в состояние 1 (фиг. З,), одновременно на выходе элемента 5 блокировки появляется логическая 1 (фиг.з4) и открывается первый элемент 8 И.. Работа элемента 5 блокировки происходит следующим образом. При установке второго К -триггера 3 в состояние О после прихода отрицательного импульса на шину Исключение устройства-{фиг .ЗбТ логическая 1, поступакицая с инверсного выхода второго 3 К -триггера 3 через элемент 10 ИЛИ, открывает элемент 11 И, вследствие чего на первый (счетный) вход делителя 12 начинают поступатьсинхроимпульсы,, на второй (управляюйщй) вход делителя 12 поступает код, соответствующий числу дискретов, на которяле необходимо сдвинуть фазу входного сигнала. Этот код может вырабатываться, например, в ЦВМ. В качестве делителя 12 можно использовать счетчик с начальной установкой. Сигнаш нА выходе дешифратора 13, который может представлять собой элемент И-НЕ, появляется в момент переполнения делителя 12. - При установке второго ЭК -триггера 3 в состояние 1 (фиг. Зг) после появления сигнала на выходе элемента 5 блокировки устройство возвращается в исходное состояние и работает как обычный счетчик. Таким образом, в результате подачи на шину Исклю ение устройства отрицательного импульса (фиг. 3) ф«за выходного сигнала счетчика 2 изменяется (замедляется) на 2.7си фиг. за) ., При подаче на шину ЙЬбавление устройства отрицательного импульса на прямом выходе, второго R5 -триггера 7 устанавливается логически уровень 1 (фиг. зж) и третий по К управлять пр своим э, к и С-входам. На : -входе третьего -триггера 4 тоянно присутствует логическая 1 С выхода элемента 5 блокировки на R -вход второго RS -триггера 7 поступает логическая 1 (фиг 3d 1 пери дич;ски изменяет свое состояние (фиг. 3-V) когда сигнал на его инверсном в™ принимает значение 1, третий сомпо следующим синхроимпу сом переводится в состояние О 1Фиг. ЗИ}. Одновременнб закрываетс ВТОРОЙ элемент 9 И и первый :JK -тр У®Р переходит в состояние Г{фиг. Очередной синхроимпульс не изменяет состояния первого тсиг гера 1 (ФИГ. , так каПа его -, ;. ., Ч- - -а// ал KdK на ( J и к-входы подан логический J И Л «,- .. . i. выхода третьего UK -триггера 4 не изменяет состояния третьего%к- ри гера 4, так как Hai его С-вход не поступают синхроимпульсы, но в то же время изменяет состояние счет ика 2 (ФИГ. за), так как на гиКс:;:Г..1 °« поступаеГ овогГВГ-триг ерГь° °« Логическая 1, присутствующаян инверсном выходе третьего /К -Диггера 4, поступает на второй вход элемента 5 блокировки, на выходе которого появляется сигнал О с опережением, равным иТои . Этот сигнал подается на R -вход второго Ж -триггера 7 и переводит его в состояние О (фиг. 3:). При этом на 5-вход третьего. :ж -триггера 4 поступает сигнал логического 0 устанавливающий его в состояние 1 (фиг. Зк;. Одновременно на выходе . -.,,. -«пивуеменно на выходе элемента 5 блокировки устанавли аэлемента 5 бллкиг,г.т,„„ выходе ется состояние 1 (фиг. 3d) При установке третьего : } -триггера 4 в состояние 1 устройств oaRo r исходное состояние и работает как обычный счетчик тт. Образом, в результате подачи на шину Добавление устройства с отрицательного импульса фаза выходного .сигнала счетчика 2 (фиг За) изменяется (ускоряется) на iTcff K Время, необходимое дая сдвига Фазы на и дискрет.ов,, полностью определяется частотой синхроимпу тьсов мом (2)Тси в предлагаемом устройстве (фиг. 3%. ,и) и в известном, выигрыш в быстродейс cTpolcTBo: Sef вГи;р1--°-:-„г: УСТРОЙСТВОМ. Выигрыш возрастает Увеличением , , стремясь к 3 KJ том предлагаемое устройство облаает быстродействием, максимально еализуемым ПРИ выбранной д1льн; А быстродействием oSSS , ованных управляющих сигналов

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный делитель частоты импульсов | 1977 |

|

SU698130A2 |

| Делитель частоты с целочисленным коэффициентом деления | 1983 |

|

SU1095414A1 |

| Синхронный делитель частоты на 11 на @ -триггерах | 1983 |

|

SU1150759A1 |

| Частотный компаратор | 1982 |

|

SU1045376A1 |

| Синтезатор частот | 1985 |

|

SU1363457A1 |

| Устройство для воспроизведения цифровой магнитной записи | 1980 |

|

SU909687A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Синтезатор частот | 1980 |

|

SU886254A2 |

| Синтезатор частот | 1976 |

|

SU799101A1 |

| Формирователь временного интервала | 1988 |

|

SU1580540A2 |

1. УСТРОЙСТВО ДЛЯ ДИСК- . РЕТНОЙ РЕГУЛИРОВКИ ФАЗЫ, содержащее первый, второй и третий tJK -триггеры, счетчик и элемент блокировки, причем 3 гвходы второго и третьего ОК -триггеров соединены с шиной ло- . рической единицы устройства, К-входы второго и третьего JK -триггеров подключены соответственно к прямому и инверсному выходам первого JK -триггера, а прямые выходсд второго и третьего ЗК -триггеров соединены с соответствующими попарно объединенными первыми и вторыми Э и К-входами первого , DK -триггера, С-вход которого подключен к С -входу счетчика и к шине синхронизации устройства, а прямой выход первого ЗК -триггера подключен к управляющему входу счетчика, выход которого соединен с выходной шиной устройства, о т л ичающееся тем, что, с целью повышения быстродействия при (Сдвиге фазы нг1 несколько дискретов, в него введены два RS-триггера и два элемента И, причем S-входы первого и .второго Я5-триггеров соединены соответственно с шинами исключения и добавления устройства, R -входы первого и второго ЯS -триггеров подключены к выходу элемента блокировки, прямые выходы первого и второго R9 -триггеров соединены с S -входами соответственно второго и .третьего ЛК -триггеров, С-входы которых подключены к выходам соответственно первого и второго элементов И,, прямые выходы второго и третьего К-триггеров .подключены .к первым входам соответственно первого и второго элементов И, инверсные выходы второго и третьего tJK -триггеров соединены соответственно с первым и вторым входами элемента блокировки, вторые входы первого и второго элементов И подключены к третьему входу элемента блокировки и к шине синхронизации устройства, червертый вход элемента блокировки соединен с управляющей шиной устройства. 2. Устройстцр по п. 1, отличающееся тем, что элемент блокировки содержит элементы ИЛИ д И, делитель с переменным коэффициентом деления, дешифратор переполнения 1Ь-4 О причем первый и второй входы элемента ИЛИ соединены соответственно с SD первым и вторым входами элемента (блокировки, выход элемента ИЛИ подключен к первому входу элемента И, .. второй вход которого с.оединен с трег :. тьим входом элемента блокировки, вы-, .ход элемента И подключен к первому входу делителя с переменным коэффициен том деления, второй вход которогр соединен с четвертым входом элемента блокировки, а выход делителя с переменным коэффициентом деления подключен к .входу дешифратора переполнения, выход которого соединен с выходом элемента блокировки.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровое устройство формирования фазового сдвига | 1974 |

|

SU516185A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для дискретной регулировки фазы | 1978 |

|

SU779904A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-07-07—Публикация

1982-03-24—Подача