первом входе больше, чем на втором; частота следования импульсов на первом входе меньше, чем на втором; частота следования импульсов на первом и втором входах равны.

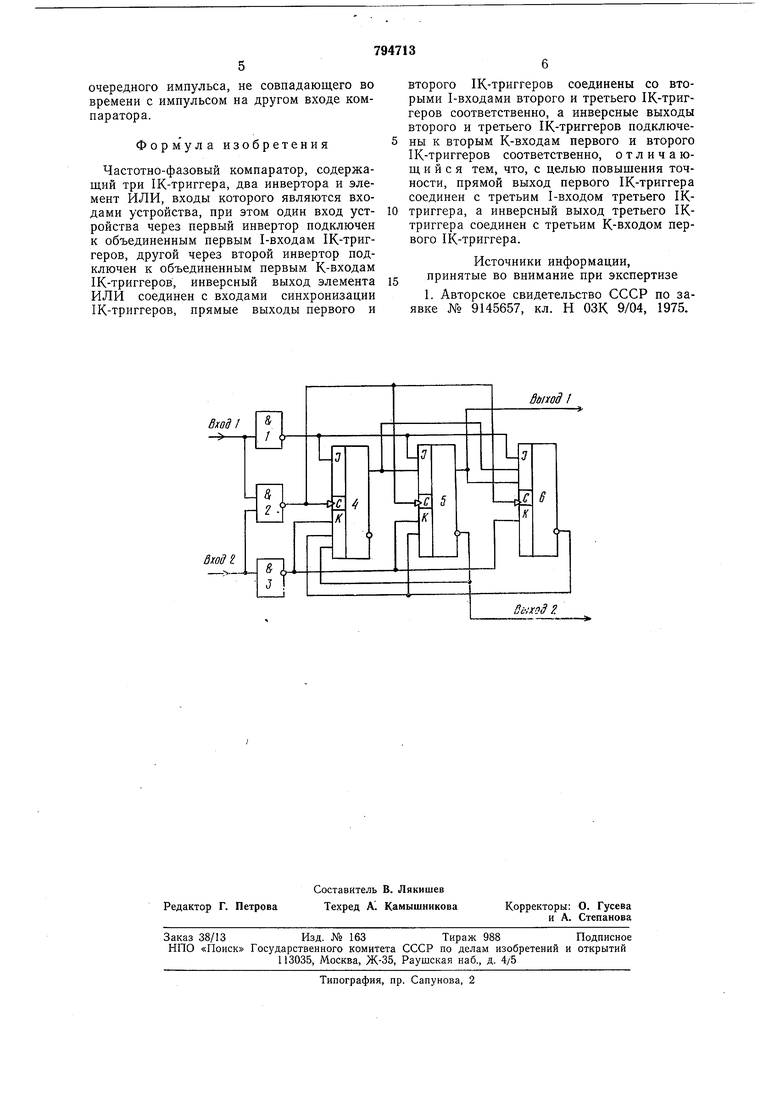

Рассмотрим работу компаратора в первом режиме. В исходном состоянии на прямых выходах 1К-триггеров 4, 5, 6 - логический «О.

Импульсы, поступаюшие на первый вход компаратора, будут переключать 1К,-триггер 4 в состояние логической «1, импульсы, поступаюш,ие на второй вход компаратора, будут возврашать lK-триггер 4 в нулевое состояние. Так как частота следования импульсов на первом входе больше, чем на втором, то периодически будет возникать ситуация, когда в промежутке времени между двумя импульсами на первом входе, на втором входе импульсов не будет Первый из этих двух импульсов вызовет установку в «1 1К-триггера 4, при этом с его прямого выхода сигнал логической «1 поступит на второй 1-вход триггера 5 и разрешит его переключение в «1.

При поступлении второго подряд импульса на первый вход 1К-триггер t установится в «1. С его инверсного выхода поступит сигнал логического «О, запреш,аюш,ий установку в «О триггера 4. Вторичное появление на первом входе двух импульсов, в промежутке между которыми не будет импульса на втором входе, приведет к установке в «1 1К-триггера 6, при этом с инверсного выхода 1К-триггера 6 на третьи К-входы 1К-триггеров 4, 5 поступит сигнал логического «О, запреш,ающий им установку в «О.

Таким образом, в режиме, когда частота следования импульсов на первом входе компаратора больше, чем на втором, 1К-триггеры 4 и 5 находятся постоянно в состоянии логической «1, а 1К-триггер 6 переключается в «1 импульсами с первого входа компаратора и в «О - импульсами со второго входа.

На прямом выходе 1К-триггера 5 (выходе компаратора) будет постоянно сигнал логической «1.

Во втором режиме работы компаратора, при частоте следования импульсов на первом входе компаратора меньшей, чем на втором, будет периодически возникать ситуация, когда в промежутке времени между двумя импульсами на втором входе компаратора, на первый вход не поступит ни одного импульса. В результате, независимо от исходного состояния компаратора, наступит момент, когда триггеры 4-6 окажутся в состоянии логического «О. При этом с прямого выхода 1К-триггера 4 на вторые 1-входы 1К-триггеров 5 и 6 поступит сигнал логического «О, запреш,аюший им установку в «1. При поступлении импульса на второй вход компаратора, 1К-триггер 4 будет устанавливаться в состояние «О, а -при поступлении импульса на первый вход компартора, Щ-триггер 4 будет возвраш,аться в состояние «1. Триггеры 5 и 6 будут постоянно находиться в состоянии «О и на прямом выходе Щ-триггера 5 (на выходе компаратора) постоянно будет сигнал логического «О.

В третьем режиме работы компаратора,

при одинаковой частоте следования импульсов на первом и втором выходах компаратора, 1К-триггер 4 установится в состояние «1, 1К-триггер 6 в состояние «О, а Щ-триггер 5 будет переключаться в состояние «1

импульсами, поступающими на первый вход, а в состояние «О импульсами, поступаюш ими на второй вход.

Таким образом, на выходе компаратора будут формироваться прямоугольные импульсы с коэффициентом заполнения, пропорциональным разности фаз сигналов на первом и втором входах компаратора.

В частности, при изменении времени задержки 3 сигнала на втором входе относительно первого входа от «О до Г (Г - период следования импульсов на первом входе) коэффициент заполнения /Сз сигнала с прямого выхода триггера 5, будет изменяться от О до 1.

При t О, 3 О, т. е. на прямом выходе 1К-триггера 5 постоянно держится сигнал логического «О. При tz Т, kz 1, т. е. на прямом выходе 1К-триггера 5 постоянно присутствует сигнал логической «1.

В режиме равенства частот триггер 4 будет постоянно находиться в состоянии «1, а триггер 6 в состоянии «О. Если триггер 4 находится в состоянии «О, те, при совпадении во времени импульсов на первом и

втором входах компаратора, триггеры 4-6 примут состояние «О, «1, «О соответственно. Приход очередного импульса на -первый вход компаратора вызовет переключение триггеров 4, 5 и 6 состояния «1, «1 и

«О, если первым поступит импульс на второй вход компаратора, то триггеры 4, 5, 6 переключатся в состояния «О, «О, «О соответственно. Аналогично, если исходными состояниями триггеров 4, 5, 6 были «1, «1, «О, то одновременное поступление импульсов на входы компаратора переключит триггеры 4, 5, 6 в состояние «1, «О, «1 соответственно. Затем, если первым во времени поступит импульс на первый вход компаратора, то триггеры 4, 5, 6 изменят свои состояния на «1, «1, «1, а если первым будет импульс на втором входе компаратора, то триггеры 4, 5, 6 примут состояния «1, «О,

«О.

Видно, что при одновременном поступлении импульсов на входы компаратора возникает кратковременное отклонение от нормальной работы компаратора, которое устраняется с приходом на любой из входов

очередного импульса, не совпадающего во времени с импульсом на другом входе компаратора.

Формула изобретения

Частотно-фазовый компаратор, содержащий три Щ-триггера, два инвертора и элемент ИЛИ, входы которого являются входами устройства, при этом один вход устройства через первый инвертор подключен к объединенным первым 1-входам 1К-триггеров, другой через второй инвертор подключен к объединенным первым К-входам 1К-триггеров, инверсный выход элемента ИЛИ соединен с входами синхронизации Щ-триггеров, прямые выходы первого и

второго Щ-триггеров соединены со вторыми 1-входами второго и третьего 1К-триггеров соответственно, а инверсные выходы второго и третьего 1К-триггеров подключены к вторым К-входам первого и второго 1К-триггеров соответственно, отличающийся тем, что, с целью повышения точности, прямой выход первого 1К-триггера соединен с третьим 1-входом третьего IKтриггера, а инверсный выход третьего IKтриггера соединен с третьим К-входом первого 1К.-триггера.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке № 9145657, кл. Н ОЗК 9/04, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дискретной регулировки фазы | 1985 |

|

SU1269051A1 |

| Синхронный делитель частоты на 18 | 1985 |

|

SU1274152A1 |

| Многофункциональное счетное устройство | 1975 |

|

SU655073A1 |

| Устройство для сравнения частот | 1985 |

|

SU1264092A1 |

| Синхронный делитель частоты на 14 | 1986 |

|

SU1368983A1 |

| Электрогидравлический следящий привод | 1985 |

|

SU1269092A1 |

| Микропроцессор | 1984 |

|

SU1164721A1 |

| Частотно-фазовый детектор | 1980 |

|

SU1040591A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОТКЛОНЕНИЯ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1990 |

|

RU2029312C1 |

| Устройство для управления положением исполнительных элементов | 1983 |

|

SU1226413A2 |

Авторы

Даты

1981-01-07—Публикация

1977-05-04—Подача