1

Изобретение относится к вычисли ельной технике и предназначено для распределения заданий процессорам.

Цель изобретения - сокращение обо рудования устройства.

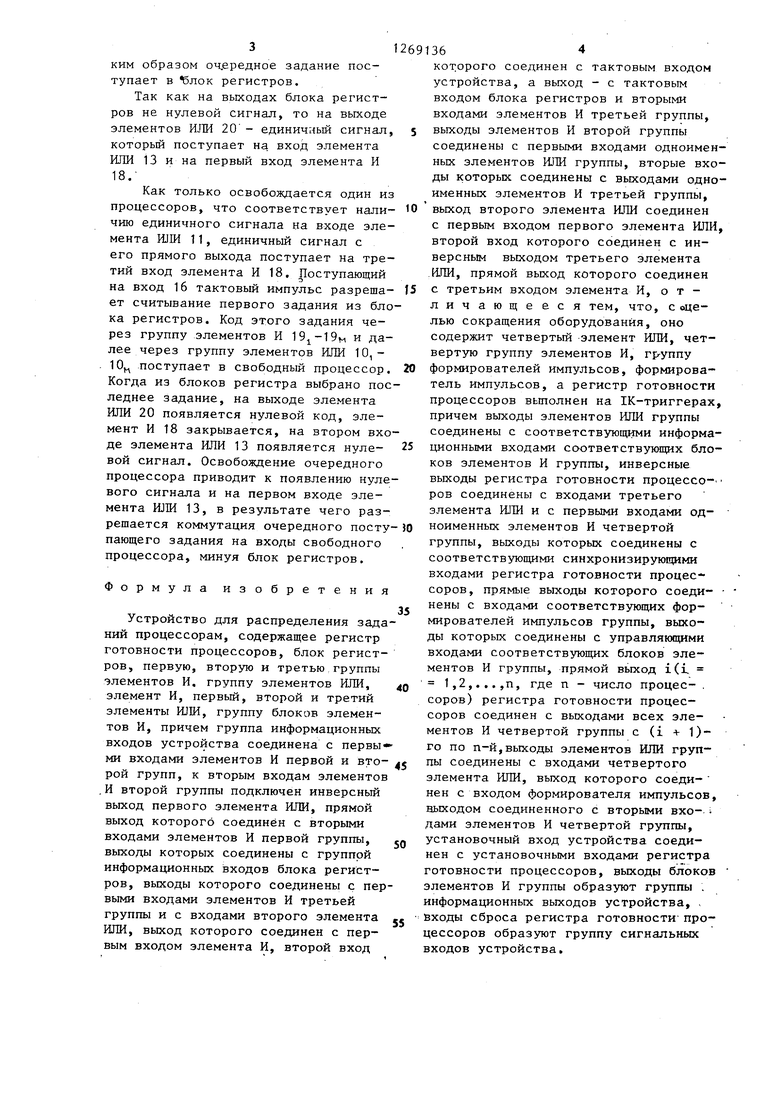

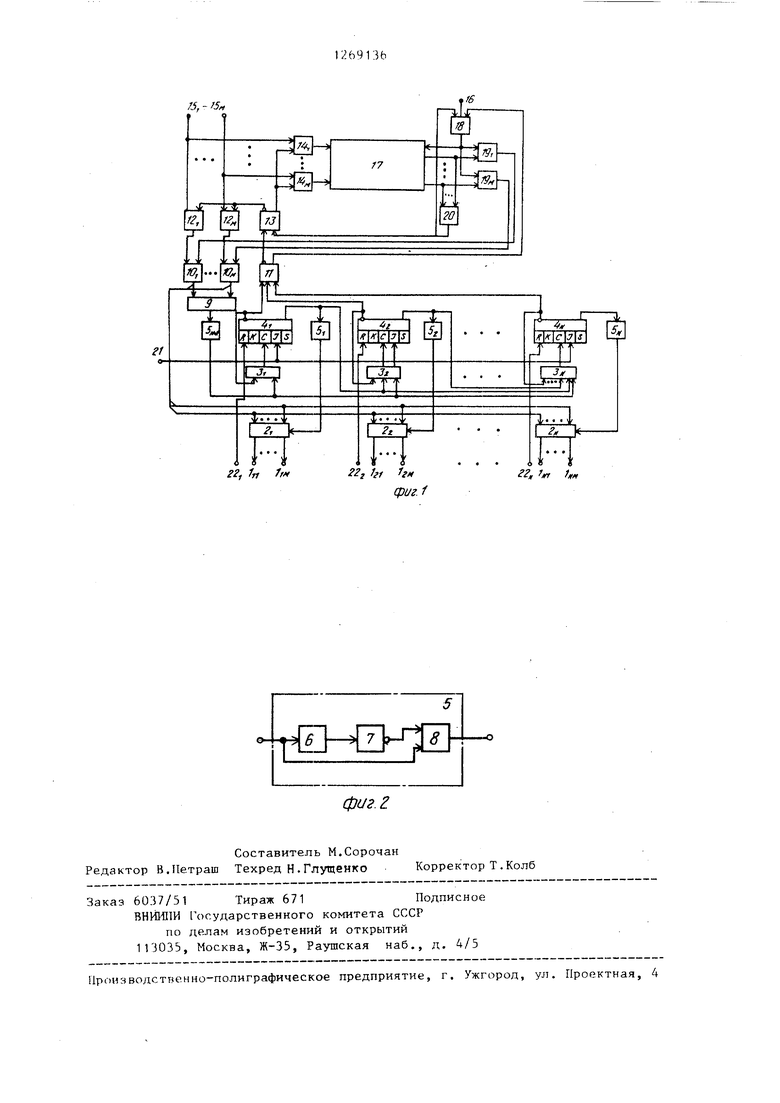

На фиг. 1 приведена структурная схема устройства для распределения заданий процессорам, на фиг. 2 схема формирователя импульсов.

Устройство для распределения заДании процессорам содержит группу информационных выходов устройства

группу.блоков Ь, -1v

1И

Ml

элементов и 2,-2, четвертую группу элементов И 3, -3, , регистр 4 готовйости процессоров, группу формирователей 5, -5fj импульсов, формирователь 5(g.i импульсов, который содержит элемент 6 задержки, элемент НЕ 7 и элемент И 8. Кроме того устройство содержит четвертый элемент ИЛИ/ 9, группу элементов ИЛИ , третий элемент ИЛИ 11, вторую группу элементов И , первый элемент ИЛИ 13, первую группу элементов И , группу информационных входов устройства, тактовый вход 16, блок 17 регистров, элемент И 18, третью группу элементов И , второй элемент ИЛИ 20, установочный вход 21, группу сигнальных входов 22,-22ц.

Устройство работает следующим образом.

В исходном состоянии процессоры свободны, 1К-триггеры 4, -4„ регистра готовности процессоров сброшены по входу К в нулевое состояние единичными сигналами готовности процессоров, поступающими на сигнальные входы , блока 17 регистров обнулен. Единичные сигналы поступают с инверсных выходов триггеров рег истра готовности на входы элемента ИЛИ 11, и с его инверсного выхода нулевой сигнал поступает на вход элемента ИЛИ 13. На втором входе этого элемента также присутствует нулевой сигнал с выхода элемента ИЛИ 20, так как на прямьпс выходах блока регистров находятся нулевые сигналы .

С инверсного выхода элемента ИЛИ 13 единичный сигнал поступает на входы группы элементов И , ° крывая ее, группа элементов И закрыта нулевым сигналом с пря: мого выхода элемента ИЛИ 13. Группа

362 .

блоков элементов И 2,-2 закрыта нулевыми сигналами с соответствующих формирователей группы.

При поступлении на входы (; устройства кода задания он проходит через открытую группу элементов И , через группу элементов ИЛИ , на соответствующие входы всех блоков элементов И группы. Кроме того, код задания с выходов группы элементов ИЛИ поступает на входы элемента ИЛИ 9, с выхода которого единичный сигнал поступает на вход формирователя 5f( импульсов. В результате этого на его выходе формируется импульс, который поступает на вторые входы элементов И группы. Элементы И закрыты нулевыми сигналами, поданными на их входы с прямых выходов предьщуших триггеров 4 -4|ч( регистра готовности процессоров, поэтому импульс проходит только через элемент И 3 группы. Так как на входы I всех триггеров регистра го;товности подан единичный потенциал, присутствующий на входе 21 устройства, триггер 4 регистра устанавливается в единичное состояние задним фронтом импульса, поступающего с выхода элемента И 3 . Единичный сигнал с прямого выхода триггера 4j поступает на управляющий вход блока элементов И 12j группы, разрешая перепись кода Зсщания в первый процессор

Второе задание, поступающее на вход устройства, аналогичным образом передается на обслуткивание второму процессору и т.д. После выполнения задания процессор устанавливает соответствующий триггер регистра готовности в нулевое состояние. Очередное задание назначается в один из свободных процессоров, начиная с первого.

Если все процессоры заняты, на входах элемента ИЛИ 11 будут нулевые сигналы, на инверсном выходе этого элемента - единичный сигнал. Этот сигнал поступает на вход элементаШШ 13, с инверсного выхода которого нулевой сигнал поступает на входы группы элементов И , закрывая их, а с прямого выхода единич:ный сигнал разрешает коммутацию кода ; задания через группу элементов И 14(14м на вход блока 17 регистров. Та3КИМ образом очередное задание поступает в лок регистров. Так как на выходах блока регистров не нулевой сигнал, то на выходе элементов ИЛИ 20 - единичный сигнал который поступает на вход элемента ИЛИ 13 и на первый вход элемента И 18.Как только освобождается один и процессоров, что соответствует нали чию единичного сигнала на входе эле мента ШШ 11, единичный сигнал с его прямого выхода поступает на тре тий вход элемента И 18, Поступающий на вход 16 тактовый импульс разреша ет считывание первого задания из бл ка регистров. Код этого задания через группу элементов И 19,-19м и далее через группу элементов ШШ 10,10 поступает в свободный процессор Когда из блоков регистра выбрано пос леднее задание, на выходе элемента ИЛИ 20 появляется нулевой код, элемент И 18 закрывается, на втором вхо де элемента ИЛИ 13 появляется нулевой сигнал. Освобождение очередного процессора приводит к появлению нуле вого сигнала и на первом входе элемента HJffl 13, в результате чего разрешается коммутация очередного посту пающего задания на входы свободного процессора, минуя блок регистров. Формула изобретения Устройство для распределения зада НИИ процессорам, содержащее регистр готовности процессоров, блок регистров, первую, вторую и третью группы элементов И. группу элементов ИЛИ, элемент И, первый, второй и третий элементы И)Ш, группу блоков элементов И, причем группа информационных входов устройства соединена с первы ми входами элементов И первой и второй групп, к вторым входам элементов .И второй группы подключен инверсный выход первого элемента ИЛИ, прямой выход которого соединён с вторыми входами элементов И первой группы, выходы которых соединены с группой информационных входов блока регистров, выходы которого соединены с пер выми входами элементов И третьей группы и с входами второго элемента ИЛИ, выход которого соединен с первым входом элемента И, второй вход 364 кот.орого соединен с тактовым входом устройства, а выход - с тактовым входом блока регистров и вторыми входами элементов И третьей группы, выходы элементов И второй группы соединены с первыми входами одноименных элементов ИЛИ группы, вторые входы которых соединены с выходами одноименных элементов И третьей группы, выход второго элемента ШШ соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с инверсным выходом третьего элемента ШШ, прямой выход которого соединен с третьим входом элемента И, о т личающееся тем, что, соцелью сокращения оборудования, оно содержит четвертый элемент ИЛИ, четвертую группу элементов И, гр-уппу формирователей импульсов, формирователь импульсов, а регистр готовности процессоров вьшолнен на 1К-триггерах, причем выходы элементов ИЛИ группы соединены с соответствующими информационными входами соответствующих блоков элементов И группы, инверсные выходы регистра готовности процессо-ров соединены с входами третьего элемента ШШ и с первыми входами одпоименных элементов И четвертой группы, выходы которых соединены с соответствующими синхронизирующими входами регистра готовности процессоров, прямые выходы которого соеди- нены с входами соответствующих формирователей импульсов группы, выходы которых соединены с управляюпщми входами соответствующих блоков элементов И группы, прямой выход i(i. 1,2,...,п, где п - число процес- . соров) регистра готовности процессоров соединен с выходами всех элементов И четвертой группы с (i 1)го по п-й,выходы элементов ШШ груп- пы соединены с входами четвертого элемента ЮТИ, выход которого соединен с входом формирователя импульсов, выходом соединенного с вторыми вхо- дами элементов И четвертой группы, установочный вход устройства соединен с установочными входами регистра готовности процессоров, выходы блоков элементов И группы образуют группы . информационных выходов устройства, входы сброса регистра готовности процессоров образуют группу сигнальных входов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1987 |

|

SU1441399A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1453406A1 |

| Устройство для распределения заданий | 1980 |

|

SU903876A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1481762A2 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1444770A1 |

| Устройство для распределения заданий вычислительной системе | 1982 |

|

SU1100623A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1524050A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1290324A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1196866A1 |

Изобретение относится к вычислительной технике и предназначено для использования в управляющих комплексах. Целью изобретения является сокращение оборудования. Распределение заданий процессорам осуществляется с учетом занятости последних. Если все процессоры заняты, то код задания записывается в блоке регистров. При освобождении процессоров коды заданий, хранящиеся в блоке регистров, поступают на распределение между процессорами. Если код очередного задания поступает в устройство в момент, когда есть свободные процессоры, то он поступает на распределение, минуя блок регистров. Задание назначается первому свободному процессору, начиная слева. Причем код задания параллельно выдается на все процессоры. Устройство для распределения заданий содержит регистр готовности процессоров, блок регистров, первую, вторую, третью и четвертую группы элементов И, груп(Л пу элементов ИЛИ, элемент И, первый, второй, третий и четвертый элементы ШШ, группу блоков элементов И, группу формирователей импульсов, формирователь импульсов. 2 ил. О5 (X) со 05

| Аналоговые и цифровые интегральные микросхемы./Иод ред | |||

| С.В.Якубовского | |||

| М.: Радио и связь, 1984, с | |||

| Устройство для вытяжки и скручивания ровницы | 1923 |

|

SU214A1 |

| Устройство для распределения заданий процессорам | 1983 |

|

SU1111165A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-07—Публикация

1985-04-24—Подача