р

N

Изобретение относится к автоматике и вычислительной технике, а именно к приоритетным устройствам для распределения заданий процессорам, и предназначено для использования в высокопроизводительных многопроцессорных и многомашинных вычислительных и управляющих системах,

Цель изобретения - повьгаение дос товерности функционирования устройства путем контроля соответствия загрузки процессоров их производительности.

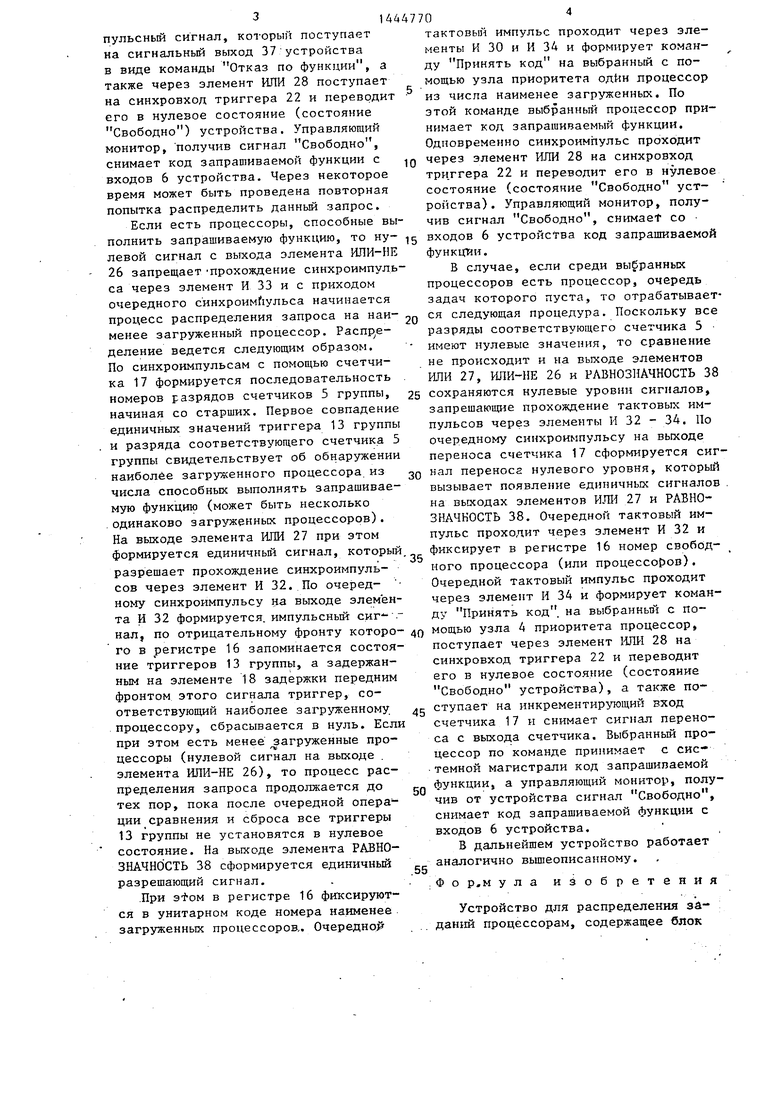

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит первую группу элементов И 1, блок 2 памяти, группу си гнальньк входов 3. - 3, Отказ процессора, узел 4 приоритета, группу счетчиков 5, вход 6 кода задания, за9РОСНЫЙ вход 7, вход 8 пуска, вход 9 сброса, кодовый выход 10 запрашиваемой функции, группу.входов fl I - 11 признака вьтолнения задания, группу сигнальных выходов 12 - 12|, группу триггеров 13, группу элементов РШИ-НЕ 14, группу мультиплексоров 15, регистр 16, счетчик 17, элемент 18 задержки, генератор 19 тактовых импульсов, формирователь 20 импульсов, триггеры 21 и 22, группы элементов И 23 и 24, группу триггеров 25, элемент 26, элементы ИЛИ 27 и 28, эле- И 29 - 34, сигнальньй выход 35, сигнальный выход 36 занятости, сиг нальный выход 37 и элемент РАВНОЗНАЧНОСТЬ 38.

Устройство работает следующим образом.

Перед началом работы подачей ну- левого импульсного сигнала на вход 9 устройств9 переводится в исходное состояние. При этом триггеры 21 и 22, триггеры 25 группы, а также счетчи- ки 5 группы переводятся в нулевое состояние. На сигнальных выходах 35 - 37, а также на выходах 12 группы - нулевые уровни сигналов. Нулевой уровень сигнала на прямом выходе триггера 22 индицирует состояние Свободно устройства и запрещает прохождение тактовьк импульсов через элементы И 30, И 32 и И 33.

Подачей единичного импульса на вход 8 триггер 21 переводится в единичное состояние (работа) и высоким уровнем сигнала на прямом выходе разрешает работу генератора 19 тактовых импульсов. Синхроимпульсы проходят

с

s

0 5 о 5

о д «

5

через элементы И 31 и ИЛИ 28 на син- хровходы триггеров 25 группы и опрашивают группу входов 3 Отказ процессора устройства, а также поступают на синхровход триггера 22 и контролируют приход сигнала Запрос н,а вход 7 устройства.

Управляющий монитор системы устанавливает на входах 6 устройства код запрашиваемой функции. На выход блока 2 памяти выдается содержимое некой строки, при этом разряды, содержащие 1, соответствуют процессорам, способным выполнить запрашиваемую функцию. Через время, определяемое быстродействием блока 2 памяти, управляющий монитор устанавливает единичный потенциальный сигнал Запрос на вход 7 усфройства. По отрицательному фронту очередного синхроимпульса триггер 22 переводится в единичное состояние и высоким уровнем сигнала разрешает прохождение тактовых импульсов через элементы И 30, И 32 и И 33. Вдиничньй сигнал с прямого выхода триггера 22 поступает также на сигнальньй выход 36 устройства (состояние Занято устройства и на вход формирователя 20 импульсов. По импульсному сигналу с вьгхода формирователя 20 импульсов счетчик 17 обнуляется, а в триггеры 13 группы заносится с выхода блока 2 памяти информация о процессорах, способных выполнить запрашиваемую функцию. При этом, если процессор неработоспособен (нулевой сигнал на инверсном выходе соответствующего триггера 25 группы) или очередь задания его переполнена (нулевой сигнял на выход переноса соответствующего счетчика 5 группы) и распределение на него нового задания может привести к потере последнего, то информация о таком процессоре н-е заносится в соответствующий триггер 13 группы и он не участвует в распределении запроса. Одновременно управляющий монитор, получив от устройства сигнал Занято, снимает сигнал Запрос с входа 7 устройства, но не снимает код запрашиваемой функции с входов 6 устройства.

Если на данной момент нет процессоров, способных выполнить запрашиг ваемую функцию, то- на выходе элемента ИЛИ-НЕ 26 формируется единичный сигнал. По очередному импульсу на выходе элемента И 33 формируется имтактовый импульс проходит через элементы И 30 и И 34 и формирует команду Принять код на выбранный с помощью узла приоритета один процессор из числа наименее загруженных. По этой команде выбранньп( процессор принимает код запрашиваемый функции. Одновременно синхроимпульс проходит через элемент ИЛИ 28 на синхровход три.ггера 22 и переводит его в нулевое

10

20

пульсныи сигнал, который поступает на сигнальный выход 37 устройства в виде команды Отказ по функции, а также через элемент ИЛИ 28 поступает на синхровход триггера 22 и переводит его в нулевое состояние (состояние Свободно) устройства. Управляющий монитор, получив сигнал Свободно, снимает код запрашиваемой функции с входов 6 устройства. Через некоторое время может быть проведена повторная попытка распределить данный запрос.

Если есть процессоры, способные выполнить запрашиваемую функцию, то ну- i входов 6 устройства код запрашиваемой левой сигнал с выхода элемента ИЛИ-НЕ функции. 26 запрещает Прохождение синхроимпульса через элемент И 33 и с приходом очередного синхроимпульса начинается процесс распределения запроса на наименее загруженный процессор. Распр е- деление ведется следующим образом. По синхроимпульсам с помощью счетчика 17 формируется последовательность номеров разрядов счетчиков 5 группы, начиная со старших. Первое совпадение единичных значений триггера 13 группы и разряда соответствующего счетчика 5 группы свидетельствует об обнаружении наиболее загруженного процессора из числа способных выполнять запрашиваемую функцию (может быть несколько .одинаково загруженных процессоров). На выходе элемента ИЛИ 27 при этом формируется единичньй сигнал, который, разрешает прохождение синхроимпульсов через элемент И 32. По очеред- ному синхроимпульсу ца выходе элемента И 32 формируется, импульсный сиг- .

нал, по отрицательному фронту которо- 40 мощью узла 4 приоритета процессор, го в регистре 16 запоминается состоя- поступает через элемент 1-ШИ 28 на ние триггеров 13 группы, а задержанным на элементе 18 задержки передним фронтом этого сигнала триггер, соответствующий наиболее загр гженному процессору, сбрасывается в нуль. Если при этом есть менее загруженные процессоры (нулевой сигнал на выходе элемента ИЛИ-НЕ 26), то процесс распределения запроса продолжается до тех пор, пока после очередной операции сравнения и сброса все триггеры 13 группы не установятся в нулевое состояние. На выходе элемента РАВНОЗНАЧНОСТЬ 38 сформируется единичньй

состояние (состояние Свободно устройства). Управляющий монитор, получив сигнал Свободно, cHUMaet со

В случае, если среди выбранных процессоров есть процессор, очередь задач которого пуста, то отрабатывается следующая процедура. Поскольку все разряды соответствующего счетчика 5 имеют нулевые значения, то сравнение не происходит и на выходе элементов ИЛИ 27, ИЛИ-НЕ 26 и РАВНОЗНАЧНОСТЬ 38

25 сохраняются нулевые уровни сигналов, запрещающие прохождение тактовых импульсов через элементы И 32 - 34. По очередному синхроимпульсу на выходе переноса счетчика 17 сформируется сиг30 кал переноса нулевого уровня, который вызывает появление единичных сигналов на вьгходах элементов ИЛИ 27 и РАВНОЗНАЧНОСТЬ 38. Очередной тактовый импульс проходит через элемент И 32 и фиксирует в регистре 16 номер свободного процессора (или процессоров). Очередной тактовый импульс проходит через элемент И 34 и формирует команду принять код, на выбранный с посинхровход триггера 22 и переводит его в нулевое состояние (состояние Свободно устройства), а также ступает на инкрементирующий вход счетчика 17 и снимает сигнал переноса с выхода счетчика. Выбранный процессор по команде принимает с сис- темной магистрали код запрашиваемой

функции, а управляющий монитор, полу35

.55

чив от устройства сигнал Свободно , снимает код запрашиваемой функции с входов 6 устройства.

В дальнейшем устройство работает аналогично вьшшописанному.

разрешающий сигнал.

.При эфом в регистре 16 фиксируются в унитарном коде номера наименее . загруженных процессоров,. Очередной

4770

тактовый импульс проходит через элементы И 30 и И 34 и формирует команду Принять код на выбранный с помощью узла приоритета один процессор из числа наименее загруженных. По этой команде выбранньп( процессор принимает код запрашиваемый функции. Одновременно синхроимпульс проходит через элемент ИЛИ 28 на синхровход три.ггера 22 и переводит его в нулевое

10

входов 6 устройства код запрашиваемой функции.

состояние (состояние Свободно устройства). Управляющий монитор, получив сигнал Свободно, cHUMaet со

0

i входов 6 устройства код запрашиваемой функции.

В случае, если среди выбранных процессоров есть процессор, очередь задач которого пуста, то отрабатывается следующая процедура. Поскольку все разряды соответствующего счетчика 5 имеют нулевые значения, то сравнение не происходит и на выходе элементов ИЛИ 27, ИЛИ-НЕ 26 и РАВНОЗНАЧНОСТЬ 38

25 сохраняются нулевые уровни сигналов, запрещающие прохождение тактовых импульсов через элементы И 32 - 34. По очередному синхроимпульсу на выходе переноса счетчика 17 сформируется сиг0 кал переноса нулевого уровня, который вызывает появление единичных сигналов . на вьгходах элементов ИЛИ 27 и РАВНОЗНАЧНОСТЬ 38. Очередной тактовый импульс проходит через элемент И 32 и фиксирует в регистре 16 номер свободного процессора (или процессоров). Очередной тактовый импульс проходит через элемент И 34 и формирует команду принять код, на выбранный с по5

мощью узла 4 приоритета процессор, поступает через элемент 1-ШИ 28 на

синхровход триггера 22 и переводит его в нулевое состояние (состояние Свободно устройства), а также поступает на инкрементирующий вход счетчика 17 и снимает сигнал переноса с выхода счетчика. Выбранный процессор по команде принимает с сис- темной магистрали код запрашиваемой

функции, а управляющий монитор, полу

чив от устройства сигнал Свободно , снимает код запрашиваемой функции с входов 6 устройства.

В дальнейшем устройство работает аналогично вьшшописанному.

Ф о р.м у л а

изобретения

Устройство для распределения заданий процессорам, содержащее блок

памяти, узел приоритета, группу реверсивных счетчиков, первую группу элементов И, первую группу триггеров, группу мультиплексоров, счетчик, элемент задержки, генератор тактовьк импульсов, при этом вход кода задания устройства соединен с адресным входом блока памяти, выходы узла приоритета соединены с первыми входами соответствующих элементов И первой группы, информационный выход счетчика соединен с адресными входами муль14Д47706

вход группы входов Отказ процессора устройства соединен с информационным входом соответствующего триггера второй группы, прямые выходы которых соединены с входами первого элемента И, выход которого является первым- сигнальным выходом устройства, инверсные выходы триггеров второй группы соединены с третьими входами соот10

ветствующих элементов И второй груп пы, вход сброса устройства соединен с нулевыми входами первого и второго триггеровJ с нулевыми входами тригветствующих элементов И второй груп пы, вход сброса устройства соединен с нулевыми входами первого и второго триггеровJ с нулевыми входами тригтиплексоров группы, входы признака

вьшолнения задания устройства соеди- 15 геров второй группы, а также с входанены с вычитающими входам1и соответст- ми сброса счЪтчиков группы, вход пусвующих счетчиков группы, информацион- ка устройства соединен с единичным

ные выходы счетчиков группы соединены входом первого триггера прямой выход

с информационными входами соответствукщих мультиплексоров группы, о т - 20

которого соединен с входом запуска генератора тактовых импульсов, первый выход которого соединен с первыми входами второго и третьего элементов И, второй выход генератора TaijTOBbix импульсов соединен с первыми входами 25 четвертого и пятого элементов И, прямой выход второго триггера является выходом занятости устройства и соединен с вторыми входами второго, четвертого и пятого элементов И, а также

личающееся тем, что, с целью повышения достоверности.функционирования путем контроля соответствия загрузки процессоров их производительности, оно дополнительно-содержит

которого соединен с входом запуска генератора тактовых импульсов, первый выход которого соединен с первыми входами второго и третьего элементов И, второй выход генератора TaijTOBbix импульсов соединен с первыми входами 25 четвертого и пятого элементов И, прямой выход второго триггера является выходом занятости устройства и соединен с вторыми входами второго, четвертого и пятого элементов И, а также

вторую группу триггеров, вторую и третью группы элементов И, регистр, первый и второй элементы ИЛИ, группу элементов ИЛИ-НЕ, первый - шестой элементы И, формирователь импульсов, ЗО с входЪм формирователя импульсов, вы- элементы РАВНОЗНАЧНОСТЬ, элемент ИЛИ- ход,которого соединен с синхровходами НЕ, первый и второй триггеры, причем выходы элементов И первой группы являются группой сигнальных выходов уст- t5oйcтвa и соединены с вычитающими входами соответствующих счетчиков

триггеров первой группы и входом сброса счетчика, запросный вход устройства соединен.с информационным

,, входом второго триггера, инверсный выход которого соединен с вторым входом третьего элемента И, выход элемен та ИЛИ-НЕ соединен с третьим входом пятого элемента И и первым входом

группы, выходы переполнения счетчиков группы соединены с первыми входами соответствующих элементов И второй, группы, информационные выходы блока

памяти соединены с вторыми входами

.

Соответствующих элементов И второй

группы, вькоды которых соединены с информационными входами соответстветствующих элементов И второй груп пы, вход сброса устройства соединен с нулевыми входами первого и второго триггеровJ с нулевыми входами триг

которого соединен с входом запуска генератора тактовых импульсов, первый выход которого соединен с первыми входами второго и третьего элементов И, второй выход генератора TaijTOBbix импульсов соединен с первыми входами четвертого и пятого элементов И, прямой выход второго триггера является выходом занятости устройства и соединен с вторыми входами второго, четвертого и пятого элементов И, а также

с входЪм формирователя импульсов, вы- ход,которого соединен с синхровходами

с входЪм формирователя импульсов, вы- ход,которого соединен с синхровходами

триггеров первой группы и входом сброса счетчика, запросный вход устройства соединен.с информационным

входом второго триггера, инверсный выход которого соединен с вторым входом третьего элемента И, выход элемента ИЛИ-НЕ соединен с третьим входом пятого элемента И и первым входом

элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с первым входом шестого элемента И, выход второго элемента И соединен с вторым входом шестого элемента И и вычитающим входом счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1990 |

|

SU1756889A1 |

| УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ ПРОЦЕССОРАМ | 1990 |

|

RU2027219C1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1441399A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1476466A1 |

| Двухканальное устройство для контроля и восстановления процессорных систем | 1986 |

|

SU1397917A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1524050A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Устройство для контроля БИС | 1984 |

|

SU1264181A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1575182A1 |

Изобретение относится к автоматике и вычислительной технике, а именно к приоритетным устройствам для распределения заданий процессорам, и предназначено для использования в высокопроизводительных многопроцессорных и многомашинных вычислительных системах. Цель изобретения - повышение достоверности функционирования путем контроля соответствия загрузки процессоров их производительности. Устройство для распределения заданий процессорам содержит блок памяти, три группы элементов И, счетчик, группу мультиплексоров, группу счетчиков, две группы триггеров, регистр, узел приоритета, группу элементов ИШ1, генератор импульсов, элемент РАВНОЗНАЧНОСТЬ, шесть элементов И, элемент задержки, формирователь импульсов, два триггера, два элемента ИЛИ, элемент ШШ-НЕ. Устройство контролирует состояние процессорных модулей, отказавший процессорный модуль регистрируется, а задание распределяется на другой, наименее загруженный процессор. 1 ил. (Л с:

вующих триггеров первой группы, пря- выход переноса счетчика соединен с

вторым входом элемента РАВНОЗНАЧНОС и инверсным входом первого элемента ИЛИ, выход которого соединен с трет

мые выходы которых соединены с входами элемента ИЛИ-НЕ, а также с информационным входом регистра, выходы которого соединены с входами узла приоритета, инверсные выходы триггеров первой группы соединены с первыми входами соответствующих элементов ИЛИ-НЕ группы, выходы мультиплексоров группы соединены с вторыми входами соответствующих элементов ШШ- НЕ группы, выходы которых соединены с первыми входами соответствующих элементов И третьей группы и прямыми входами первого элемента ИЛИ, каждый

выход переноса счетчика соединен с

вторым входом элемента РАВНОЗНАЧНОСТЬ и инверсным входом первого элемента ИЛИ, выход которого соединен с третьим

входом четвертого элемента И, 1зы- ход третьего элемента И соединен с первым входом второго элемента НЛИ, выход четвертого элемента И соединен с СИНХ15ОВХОДОМ регистра, а также через элемент задержки - с вторыми вхо- дами элементов И третьей группы, выходы которых соединены с нулевыми входами соответствующих трштеров первой группы, выход пятого элемента И является вторым сигняльным вы

| Устройство для распределения заданий процессорам | 1985 |

|

SU1269136A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1205144A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-12-15—Публикация

1987-07-27—Подача