1J

-С

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ДВИГАТЕЛЯ | 1995 |

|

RU2111608C1 |

| Цифровой модулятор | 1991 |

|

SU1800604A1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 2002 |

|

RU2216850C1 |

| Цифровой электропривод постоянного тока | 1982 |

|

SU1117809A1 |

| Многофазный импульсный стабилизатор напряжения | 1987 |

|

SU1483438A1 |

| МОДУЛЯЦИОННЫЙ РАДИОМЕТР | 2001 |

|

RU2187824C1 |

| Преобразователь напряжения с многозонной импульсной модуляцией | 1983 |

|

SU1343521A2 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ УПРАВЛЕНИЯ СИНХРОННЫМ ЭЛЕКТРОДВИГАТЕЛЕМ | 2012 |

|

RU2517423C1 |

| ФАЗОСДВИГАЮЩЕЕ УСТРОЙСТВО | 2005 |

|

RU2288532C1 |

| Устройство для управления электродвигателем постоянного тока | 1987 |

|

SU1608776A1 |

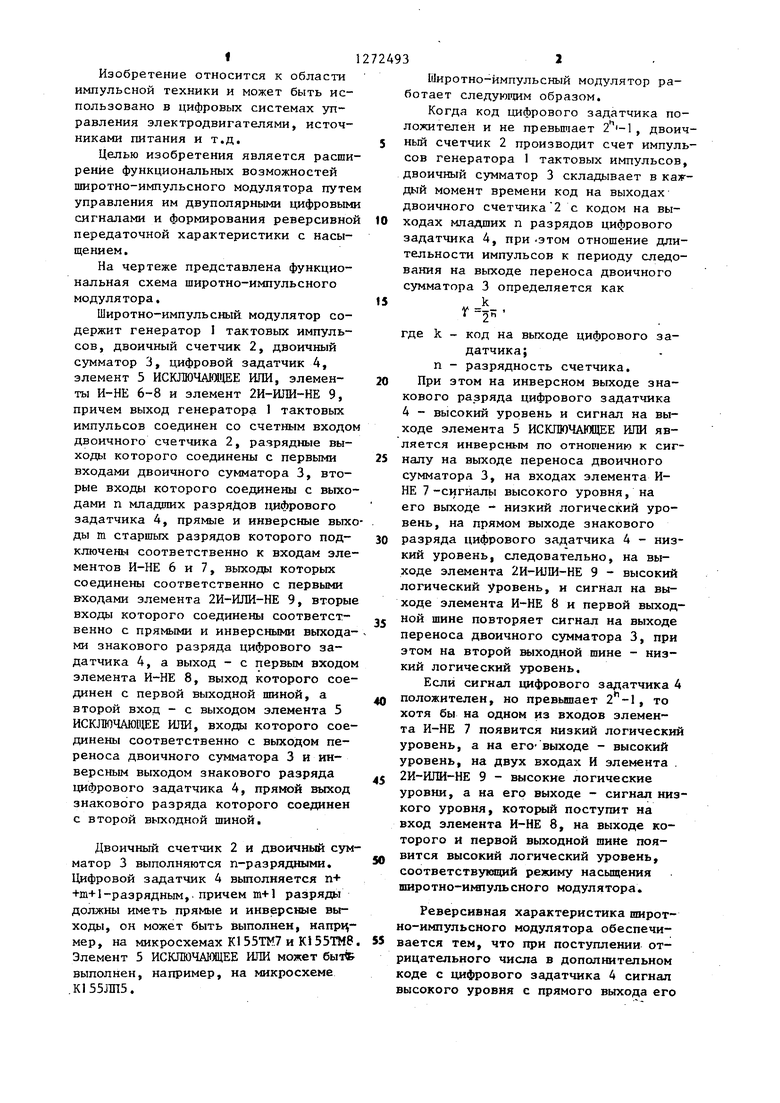

Изобретение может быть использовано в цифровых системах управления электродвигателями, источниками питания и т.п. Цель, изобретения расширение функциональных возможностей, достигается путем уп $авления широтно-импульсным модулятором двуполярными цифровыми снгиалами и формирования реверсивной передаточной характеристики с насыщением. Для этого в модулятор дополнительно введены элемент ИСЮШЧАКЩЕЕ ИЛИ 5, элементы И-НЕ 6-8 и элемент 2И-ИЛИ-НЕ 9. На чертеже также показаны: генератор 1 тактовых импульсов, двоичный счетчик 2, двоичный сумматор 3, цифровой задатчик 4, введение элемента 5 позволило получить реверсивную характеристику, а введение элементов 6-9 обеспечило релим насыщения на двух ветвях выходной характеристики. Кроме того, в модуляторе умень(Л шены потери при переключениях силовых ключей в режимах нулевого и максимального выходных сигналов. 1 ил.

-Ч

U

f/0/тра ение Изобретение относится к области импульсной техники и может быть использовано в цифровых системах управления электродвигателями, источниками питания и т.д. Целью изобретения является расши рение функциональных возможностей широтно-импульсного модулятора путе управления им двуполярными цифровым сигналами и формирования реверсивно передаточной характеристики с насыщением. На чертеже представлена функциональная схема широтно-импульсного модулятора. Широтно-импульсный модулятор содержит генератор I тактовых импульсов, двоичный счетчик 2, двоичный сумматор 3, цифровой задатчик 4, элемент 5 ИСКЛЮЧАМДЕЕ ШШ, элементы И-НЕ 6-8 и элемент 2И-Ш1И-НЕ 9, причем выход генератора 1 тактовых импульсов соединен со счетным входо двоичного счетчика 2, разрядные выходы которого соединены с первыми входами двоичного сумматора 3, вторые входы которого соединены с выхо дами п младших разрядов цифрового задатчика 4, прямые и инверсные вых ды m старшых разрядов которого подключены соответственно к входам эле ментов И-НЕ 6 и 7, выходы которых соединены соответственно с первыми в-ходами элемента 2И-ИЛИ-НЕ 9, вторы входы которого соединены соответственно с прямыми и инверсными выхода ми знакового разряда цифрового задатчика 4, а выход - с первым входо элемента И-НЕ 8, выход которого сое динен с первой выходной шиной, а второй вход - с выходом элемента 5 ИСКЛЮЧАЮПЩЕ ИЛИ, входа которого сое динены соответственно с выходом переноса двоичного сумматора 3 и инверсным выходом знакового разряда цифрового задатчика 4, прямой выход знакового разряда которого соединен с второй выходной шиной. Двоичный счетчик 2 и двоичный сум матор 3 выполняются п-разрядными. Цифровой задатчик 4 вьтолняется п+ +т+1-разрядным, причем т+1 разряды должны иметь прямые и инверсные выходы, он может быть выполнен, напрц мер, на микросхемах К1 55TM7 и К ЗЗта Элемент 5 ИСКЛЮЧАЩЕЕ ИЛИ может быт выполнен, например, на микросхеме .К155ЛП5. Широтно-импульсный модулятор работает следующим образом. Когда код цифрового задатчика положителен и не превьштает , двоичный счетчик 2 производит счет импульсов генератора 1 тактовых импульсов, двоичный сумматор 3 складывает в каждый момент времени код на выходах двоичного счетчика2 с кодом на выходах младших п разрядов цифрового задатчика 4, при -этом отношение длительности импульсов к периоду следования на выходе переноса двоичного сумматора 3 определяется как Г 5Н где k - код на выходе цифрового задатчика;п - разрядность счетчика. При этом на инверсном выходе знакового разряда цифрового задатчика 4 - высокий уровень и сигнал на выходе элемента 5 ИСКПЮЧАКЩЕЕ ИЛИ является инверсным по отноршнию к сигналу на выходе переноса двоичного сумматора 3, на входах элемента ИНЕ 7-сигналы высокого уровня, на его выходе - низкий логический уровень, на прямом выходе знакового разряда цифрового задатчика 4 - низкий уровень, следовательно, на выходе элемента 2И-Ш1И-НЕ 9 - высокий логический уровень, и сигнал на выходе элемента И-НЕ 8 и первой выходной шине повторяет сигнал на выходе переноса двоичного сумматора 3, при этом на второй выходной шине - низкий логический уровень. Если сигнал цифрового задатчика 4 положителен, но превышает , то хотя бы на одном из входов элемента И-НЕ 7 появится низкий логический уровень, а на его- выходе - высокий уровень, на двух входах И элемента . 2И-ИЛИ-НЕ 9 - высокие логические уровни, а на его выходе - сигнал низкого уровня, который поступит на вход элемента И-НЕ 8, на выходе которого и первой выходной шиНе появится высокий логический уровень, соответствующий режиму насыщения широтно-и шульсного модулятора. Реверсивная характеристика широтно-импульсного модулятора обеспечивается тем, что при поступлении отрицательного числа в дополнительном коде с цифрового задатчика 4 сигнал высокого уровня с прямого выхода его

знакового разряда поступает на вторую выходную шину, а с нее - на вход управляющего устройства для изменения направления движения исполнительного устройства. Одновременно сигнал с инверсного выхода знакового разряда цифрового задатчика 4 поступает на один из входов элемента 5 ИСКЛЮЧАЩЕЕ ИЛИ и его выходной сигнал повторяет сигнал на выходе переноса двоичного сумматора 3. При этом на входы элемента И-НЕ 6 поступают сигналы высокого уровня, на его выходе сигнал низкого уровня, следовательно на выходе элемента 2И-ИЛИ-НЕ 9 сигнал высокого уровня, а на выходе элемента И-НЕ 8 и первой выходной шине - сигнал, инвертированный относительно сигнала на выходе переноса двоичного сумматора 3.

Отношение длительности к периоду следования на выходе двоичного сумматора 3 при отрицательных кодах определяется также, как и при положительных, но так как число в дополнительном коде представляет собой дополнение до 2 , т.е.

,

где М - дополнение, соответствующее коду k, а сигнал на выходе нодулятоpa - есть инверсия сигнала на выходе переноса двоичного сумматора 3, то длительность импульса на выходе широтно-импульсного модулятора равна длительности паузы на выходе переноса двоичного сумматора 3 и определяется как

- 2 2 2 где TO - период следования импульсо t,n - длительность импульсов на

выходе переноса двоичного

сумматора 3.

Таким образом, при отрицательных числах на выходах цифрового задатчика 4 отношение длительности импульсов к периоду следования на первой выходной шине широтно-импульсного модулятора определяется делением на 2 кода цифрового задатчика 4, а на второй выходной шине установлен высокий логический уровень. Если код цифрового задатчика 4 отрицателен и по модулю превышает 2 -1, то хотя бы на один из входов элемента И-НЕ 6 поступает низкий логический уровень с выходов его старших разрядов, на выходе элемента И-НЕ 6 устанавливается высокий логический уровень, следовательно, на два входа И элемента 2И-ИЛИ-НЕ 9 поступают высокие уровни, а на его выходе устанавливается низкий уровень, поступагаций на один из входов элемента И-НЕ 8 и вызывающий появление высокого логического уровня на первой выходной шине широтно-импульсного модулятора, соответствующего насыщению на отрицательной ветви характеристики модулятора. Введение в широтно-импульсный модулятор элемента 5 ИСЮШ}ЧАЮР1ЕЕ ИЛИ позволило получить реверсную характеристику, а применение трех элементов И-НЕ и элемента 2И-ИЛИ-НЕ обеспечило режим насьш5ения на двух ветвях его выходной характеристики.

Кроме того, в тиротно-импульсном модуляторе нулевому входному сигналу соответствует выходной сигнал низкого логического уровня, а максимальному входному сигналу - выходной сигнал высокого логического уровня, что позволяет уменьшить потери при переключении силовых кличей в режимах нулевого и максимального входных сигналов.

Формула изобретения

Миротно-импульсный модулятор, содержащий соединенные последовательно генератор тактовых импульсов и двоичный счетчик, разрядные выходы которого соединены с первыми входами двоичного сумматора, вторые входы которого соединены с выходами п младших разрядов цифрового задатчика, отличающийся тем, что, с целью расширения функциональных возможностей, в него дополнительно введены три элемента И-НЕ, элемент ИСЮШЧМХЦЕЕ ИЛИ и элемент 2И-ИЛИ-НЕ, причем прямые и инверсные выходы m старших разрядов цифрового задатчика подключены соответственно к входам первого и второго элемеитов И-НЕ, выходы которых соединены с первыми входами элемента 2И-ИЛИ-НЕ вторые входы которого соединены соответственно с прямыми и инверсными выходами зиакового разряда цифрового задатчика, а выход - с первым входом третьего элемента И-НЕ, выход которого соединен с первой выходной шиной, а второй вход - с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, входы котороS12724936

го соединены соответственно с выхо- да цифрового задатчика, прямой выдом переноса двоичного сумматора и ход знакового разряда которого соес инверсным выходом знакового разря- динен с второй выходной шиной.

| Реверсивный цифровой широтно-импульсный модулятор | 1982 |

|

SU1170605A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Широтно-импульсный модулятор | 1982 |

|

SU1095385A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-11-23—Публикация

1985-04-08—Подача