Изобретение относится к импульсной технике и может быть использовано в преобразователях систем управления.

Целью изобретения является расширение области применения за счет обеспечения управления цифровым модулятором транзисторных ключей в силовой цепи асинхронного двигателя.

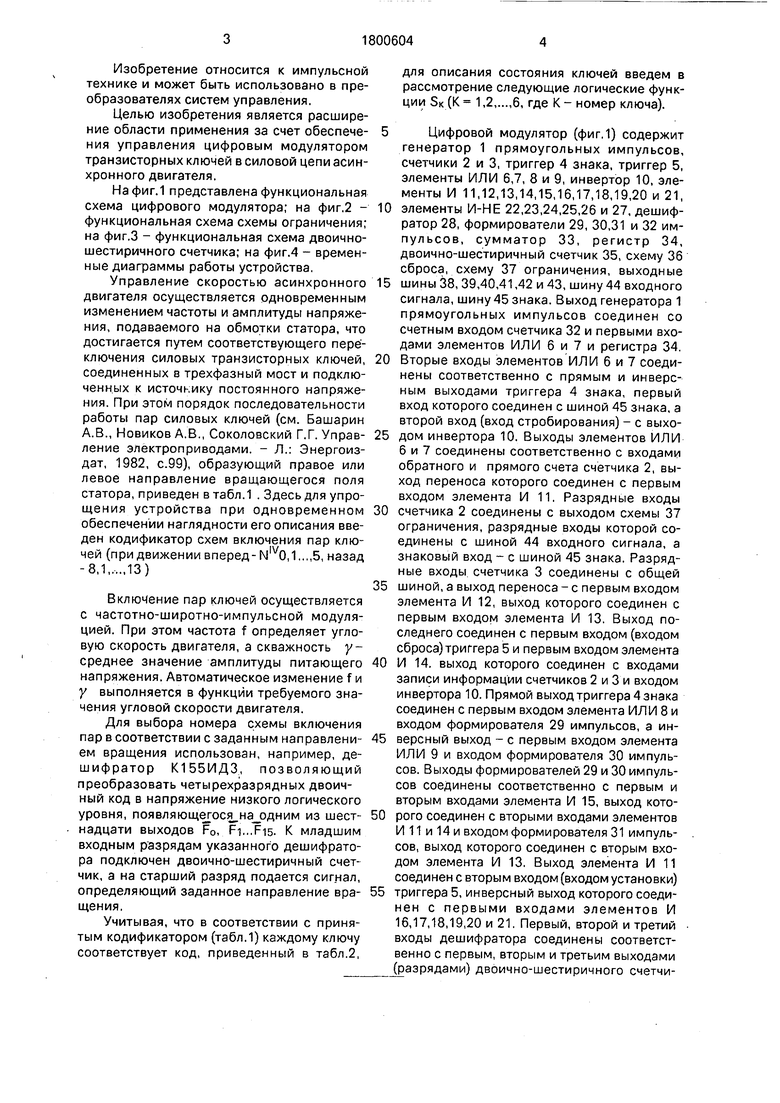

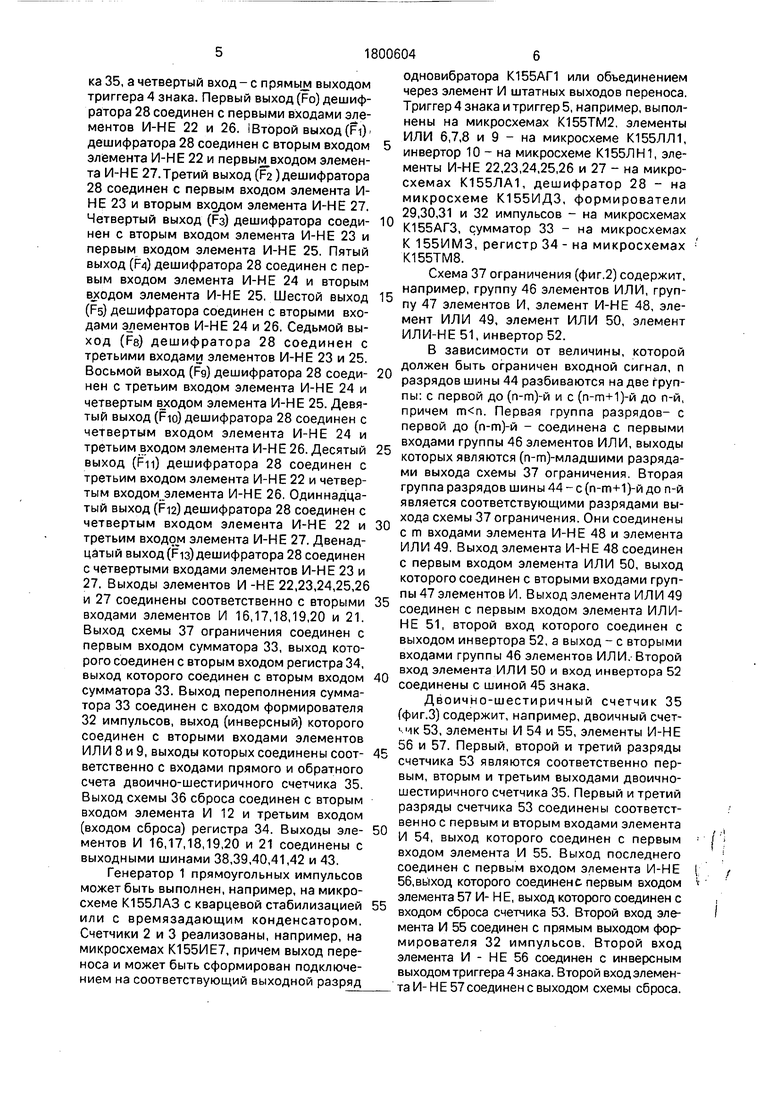

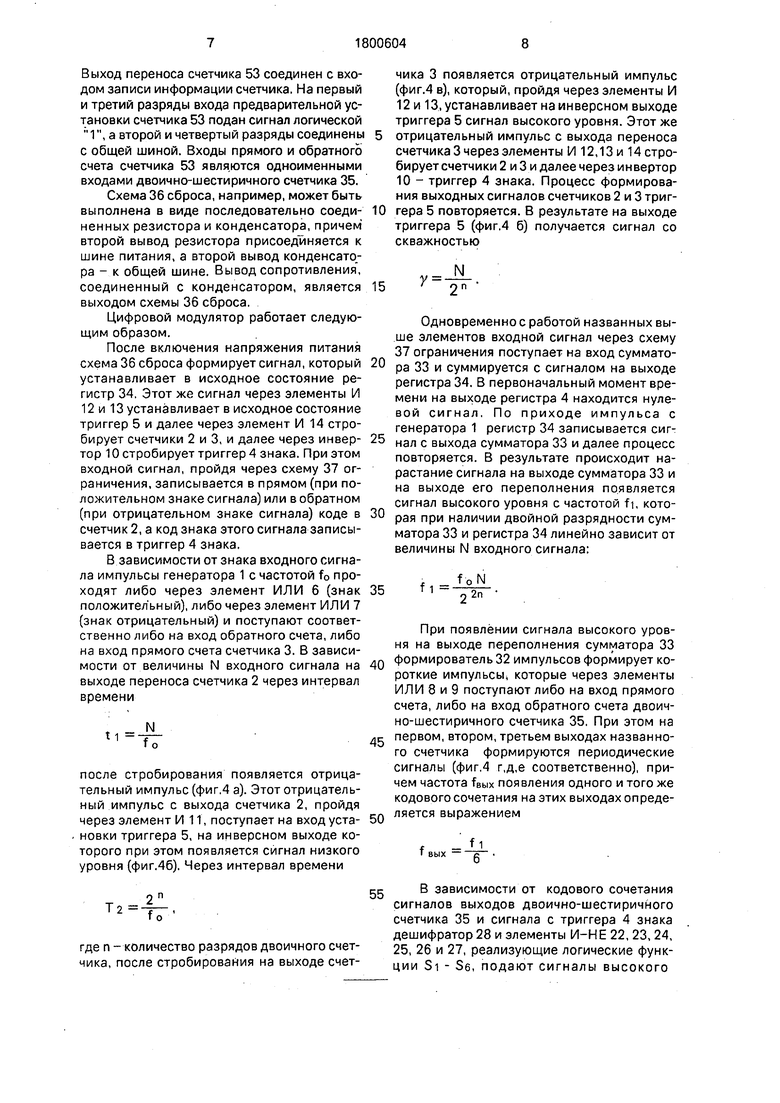

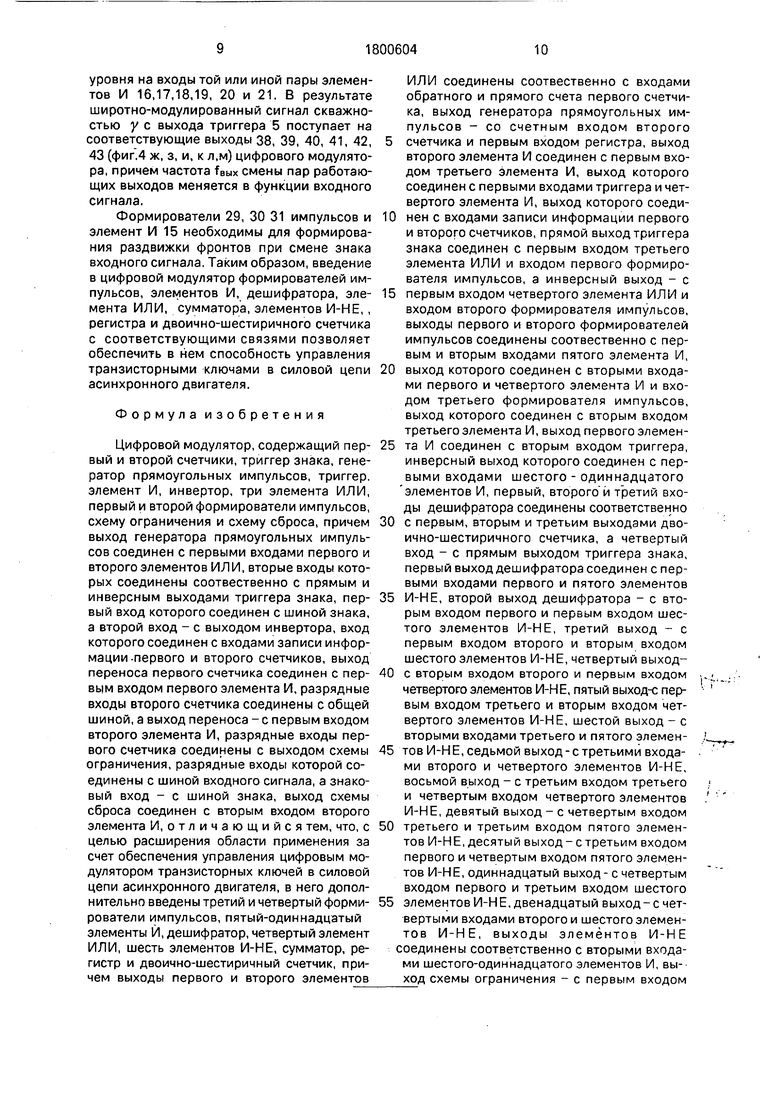

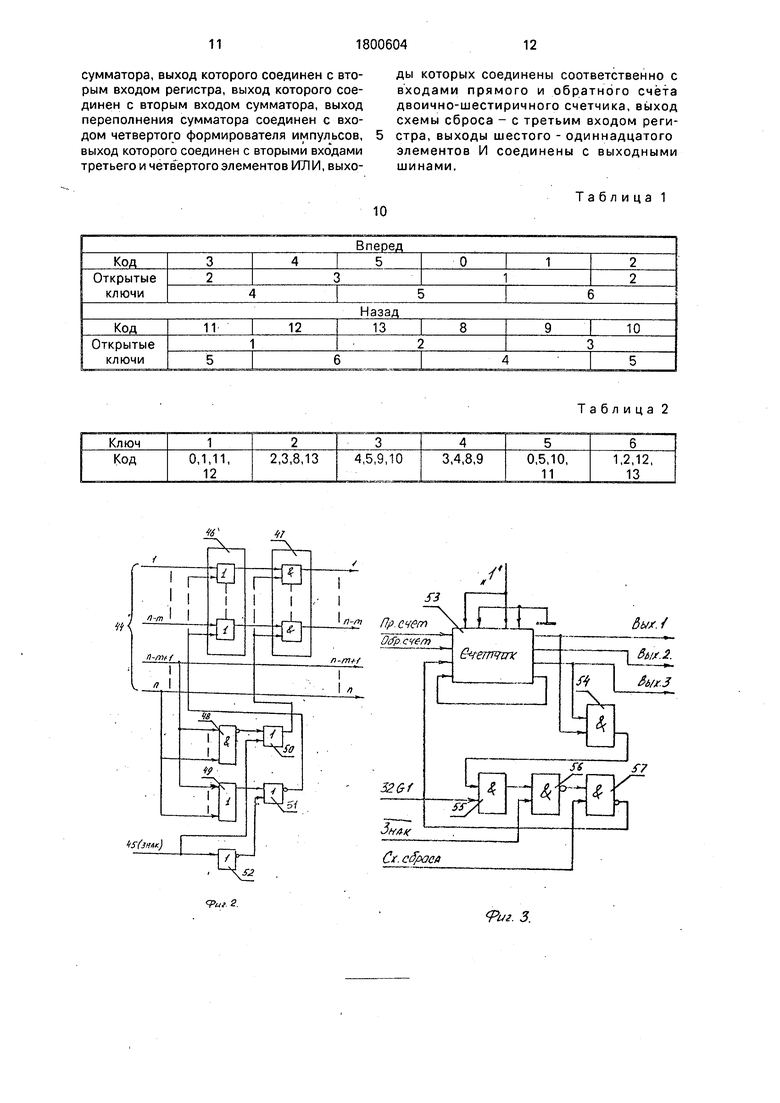

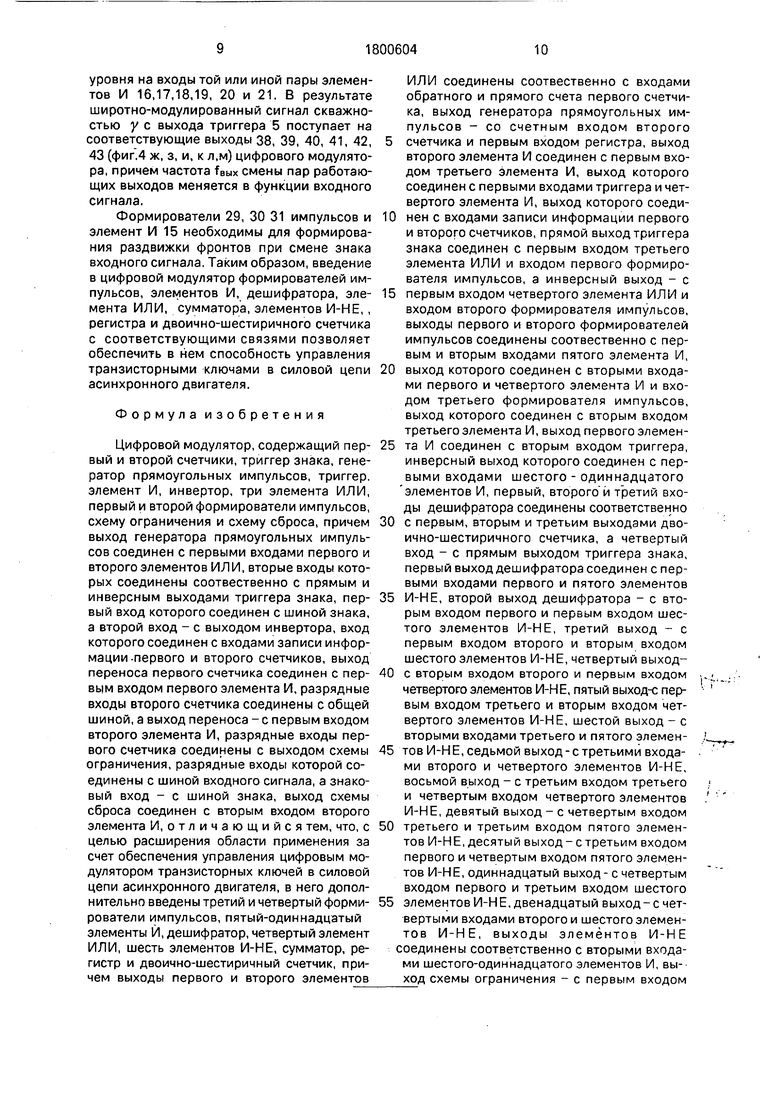

На фиг.1 представлена функциональная схема цифрового модулятора; на фиг.2 - функциональная схема схемы ограничения; на фиг.З - функциональная схема двоично- шестиричного счетчика; на фиг.4 - временные диаграммы работы устройства.

Управление скоростью асинхронного двигателя осуществляется одновременным изменением частоты и амплитуды напряжения, подаваемого на обмотки статора, что достигается путем соответствующего переключения силовых транзисторных ключей, соединенных в трехфазный мост и подключенных к источнику постоянного напряжения. При этом порядок последовательности работы пар силовых ключей (см. Башарин А.В., Новиков А.В., Соколовский Г.Г. Управление электроприводами. - Л.: Энергоиз- дат, 1982, с.99), образующий правое или левое направление вращающегося поля статора, приведен в табл.1 . Здесь для упрощения устройства при одновременном обеспечении наглядности его описания введен кодификатор схем включения пар ключей (при движении вперед- N 0,1...,5, назад -8,1,,..,13)

Включение пар ключей осуществляется с частотно-широтно-импульсной модуляцией. При этом частота f определяет угловую скорость двигателя, а скважность у- среднее значение амплитуды питающего напряжения. Автоматическое изменение f и у выполняется в функции требуемого значения угловой скорости двигателя.

Для выбора номера схемы включения пар в соответствии с заданным направлением вращения использован, например, дешифратор К155ИДЗ, позволяющий преобразовать четырехразрядных двоичный код в напряжение низкого логического уровня, появляющегося на одним из шестнадцати выходов Fo, Fi..,Fi5. К младшим входным разрядам указанного дешифратора подключен двоично-шестиричный счетчик, а на старший разряд подается сигнал, определяющий заданное направление вращения.

Учитывая, что в соответствии с принятым кодификатором (табл.1) каждому ключу соответствует код, приведенный в табл.2,

для описания состояния ключей введем в рассмотрение следующие логические функции SK (К 1,2,...,6, где К - номер ключа).

Цифровой модулятор (фиг.1) содержит генератор 1 прямоугольных импульсов, счетчики 2 и 3, триггер 4 знака, триггер 5, элементы ИЛИ 6,7, 8 и 9, инвертор 10, элементы И 11,12,13,14,15,16,17,18,19,20 и 21,

элементы И-НЕ 22,23,24,25,26 и 27, дешифратор 28, формирователи 29, 30,31 и 32 импульсов, сумматор 33, регистр 34, двоично-шестиричный счетчик 35, схему 36 сброса, схему 37 ограничения, выходные

шины 38,39,40,41,42 и 43, шину 44 входного сигнала, шину 45 знака. Выход генератора 1 прямоугольных импульсов соединен со счетным входом счетчика 32 и первыми входами элементов ИЛИ 6 и 7 и регистра 34.

Вторые входы элементов ИЛИ 6 и 7 соединены соответственно с прямым и инверсным выходами триггера 4 знака, первый вход которого соединен с шиной 45 знака, а второй вход (вход стробирования) - с выходом инвертора 10. Выходы элементов ИЛИ 6 и 7 соединены соответственно с входами обратного и прямого счета счетчика 2, выход переноса которого соединен с первым входом элемента И 11. Разрядные входы

счетчика 2 соединены с выходом схемы 37 ограничения, разрядные входы которой соединены с шиной 44 входного сигнала, а знаковый вход - с шиной 45 знака. Разрядные входы счетчика 3 соединены с общей

шиной, а выход переноса - с первым входом элемента И 12, выход которого соединен с первым входом элемента И 13. Выход последнего соединен с первым входом (входом сброса) триггера 5 и первым входом элемента

И 14. выход которого соединен с входами записи информации счетчиков 2 и 3 и входом инвертора 10. Прямой выход триггера 4 знака соединен с первым входом элемента ИЛИ 8 и входом формирователя 29 импульсов, а инверсный выход - с первым входом элемента ИЛИ 9 и входом формирователя 30 импульсов. Выходы формирователей 29 и 30 импульсов соединены соответственно с первым и вторым входами элемента И 15, выход которого соединен с вторыми входами элементов И 11 и 14 и входом формирователя 31 импульсов, выход которого соединен с вторым входом элемента И 13. Выход элемента И 11 соединен с вторым входом (входом установки)

триггера 5, инверсный выход которого соединен с первыми входами элементов И 16,17,18,19,20 и 21. Первый, второй и третий входы дешифратора соединены соответственно с первым, вторым и третьим выходами (разрядами) двоично-шестиричного счетчика 35, а четвертый вход- с прямым выходом триггера 4 знака. Первый выход (Fo) дешифратора 28 соединен с первыми входами элементов И-НЕ 22 и 26. I Второй выход (R) дешифратора 28 соединен с вторым входом элемента И-НЕ 22 и первым входом элемента И-НЕ 27.Третий выход (F2)дешифратора 28 соединен с первым входом элемента И- НЕ 23 и вторым входом элемента И-НЕ 27. Четвертый выход (Рз) дешифратора соеди- нен с вторым входом элемента И-НЕ 23 и первым входом элемента И-НЕ 25. Пятый выход (F/i) дешифратора 28 соединен с первым входом элемента И-НЕ 24 и вторым входом элемента И-НЕ 25, Шестой выход (Fs) дешифратора соединен с вторыми входами элементов И-НЕ 24 и 26. Седьмой выход (Fe) дешифратора 28 соединен с третьими входами элементов И-НЕ 23 и 25. Восьмой выход (Fg) дешифратора 28 соеди- нен с третьим входом элемента И-НЕ 24 и четвертым входом элемента И-НЕ 25. Девятый выход (Ею) дешифратора 28 соединен с четвертым входом элемента И-НЕ 24 и третьим входом элемента И-Н Е 26. Десятый выход (FH) дешифратора 28 соединен с третьим входом элемента И-НЕ 22 и четвертым входом элемента И-НЕ 26. Одиннадцатый выход (Fi2) дешифратора 28 соединен с четвертым входом элемента И-НЕ 22 и третьим входом элемента И-НЕ 27. Двенадцатый выход (Р|з) дешифратора 28 соединен с четвертыми входами элементов И-НЕ 23 и 27. Выходы элементов И-НЕ 22,23,24,25,26 и 27 соединены соответственно с вторыми входами элементов И 16,17,18,19,20 и 21. Выход схемы 37 ограничения соединен с первым входом сумматора 33, выход которого соединен с вторым входом регистра 34, выход которого соединен с вторым входом сумматора 33. Выход переполнения сумматора 33 соединен с входом формирователя 32 импульсов, выход (инверсный) которого соединен с вторыми входами элементов ИЛИ 8 и 9, выходы которых соединены соот- ветственно с входами прямого и обратного счета двоично-шестиричного счетчика 35. Выход схемы 36 сброса соединен с вторым входом элемента И 12 и третьим входом (входом сброса) регистра 34. Выходы эле- ментов И 16,17,18,19,20 и 21 соединены с выходными шинами 38,39,40,41,42 и 43.

Генератор 1 прямоугольных импульсов может быть выполнен, например, на микросхеме К155ЛАЗ с кварцевой стабилизацией или с времязадающим конденсатором. Счетчики 2 и 3 реализованы, например, на микросхемах К155ИЕ7, причем выход переноса и может быть сформирован подключением на соответствующий выходной разряд

одновибратора К155АГ1 или объединением через элемент И штатных выходов переноса. Триггер 4 знака и триггер 5, например, выполнены на микросхемах К155ТМ2. элементы ИЛИ 6,7,8 и 9 - на микросхеме К155ЛЛ1, инвертор 10 - на микросхеме К155ЛН1, элементы И-НЕ 22,23,24,25,26 и 27 - на микросхемах К155ЛА1, дешифратор 28 - на микросхеме К155ИДЗ, формирователи 29,30,31 и 32 импульсов - на микросхемах К155АГЗ, сумматор 33 - на микросхемах К 155ИМЗ, регистр 34 - на микросхемах К155ТМ8.

Схема 37 ограничения (фиг.2) содержит, например, группу 46 элементов ИЛИ, группу 47 элементов И, элемент И-НЕ 48, элемент ИЛИ 49, элемент ИЛИ 50, элемент ИЛИ-НЕ 51, инвертор 52.

В зависимости от величины, которой должен быть ограничен входной сигнал, п разрядов шины 44 разбиваются на две группы: с первой до (п-т)-й и с (п-т+1)-й до п-й, причем . Первая группа разрядов- с первой до (п-т)-й - соединена с первыми входами группы 46 элементов ИЛИ, выходы которых являются (п-т)-младшими разрядами выхода схемы 37 ограничения. Вторая группа разрядов шины 44 - с (п-т+1)-й до п-й является соответствующими разрядами выхода схемы 37 ограничения. Они соединены с m входами элемента И-НЕ 48 и элемента ИЛИ 49. Выход элемента И-НЕ 48 соединен с первым входом элемента ИЛИ 50, выход которого соединен с вторыми входами группы 47 элементов И. Выход элемента ИЛИ 49 соединен с первым входом элемента ИЛИ- НЕ 51, второй вход которого соединен с выходом инвертора 52, а выход - с вторыми входами группы 46 элементов ИЛИ.- Второй вход элемента ИЛИ 50 и вход инвертора 52 соединены с шиной 45 знака.

Двоично-шестиричный счетчик 35 (фиг.З) содержит, например, двоичный счет- ик 53, элементы И 54 и 55, элементы И-НЕ 56 и 57. Первый, второй и третий разряды счетчика 53 являются соответственно первым, вторым и третьим выходами двоично- шестиричного счетчика 35. Первый и третий разряды счетчика 53 соединены соответственно с первым и вторым входами элемента И 54, выход которого соединен с первым входом элемента И 55. Выход последнего соединен с первым входом элемента И-НЕ 56,выход которого соединен с первым входом элемента 57 И- НЕ, выход которого соединен с входом сброса счетчика 53. Второй вход элемента И 55 соединен с прямым выходом формирователя 32 импульсов. Второй вход элемента И - НЕ 56 соединен с инверсным выходом триггера 4 знака. Второй вход элемента И- НЕ 57соединен с выходом схемы сброса.

Выход переноса счетчика 53 соединен с входом записи информации счетчика. На первый и третий разряды входа предварительной установки счетчика 53 подан сигнал логической 1, а второй и четвертый разряды соединены с общей шиной. Входы прямого и обратного счета счетчика 53 являются одноименными входами двоично-шестиричного счетчика 35.

Схема 36 сброса, например, может быть выполнена в виде последовательно соеди- ненных резистора и конденсатора, причем второй вывод резистора присоединяется к шине питания, а второй вывод конденсатора - к общей шине. Вывод сопротивления, соединенный с конденсатором, является выходом схемы 36 сброса.

Цифровой модулятор работает следующим образом.

После включения напряжения питания схема 36 сброса формирует сигнал, который устанавливает в исходное состояние регистр 34. Этот же сигнал через элементы И 12 и 13 устанавливает в исходное состояние триггер 5 и далее через элемент И 14 стро- бирует счетчики 2 и 3, и далее через инвер- тор 10 стробирует триггер 4 знака. При этом входной сигнал, пройдя через схему 37 ограничения, записывается в прямом (при положительном знаке сигнала) или в обратном (при отрицательном знаке сигнала) коде в счетчик 2, а код знака этого сигнала записывается в триггер 4 знака,

В зависимости от знака входного сигнала импульсы генератора 1 с частотой f0 проходят либо через элемент ИЛИ 6 (знак положительный), либо через элемент ИЛИ 7 (знак отрицательный) и поступают соответственно либо на вход обратного счета, либо на вход прямого счета счетчика 3. В зависимости от величины N входного сигнала на выходе переноса счетчика 2 через интервал времени

11

N

после стробирования появляется отрицательный импульс (фиг.4 а). Этот отрицательный импульс с выхода счетчика 2, пройдя через элемент И 11, поступает на вход уста- новки триггера 5, на инверсном выходе которого при этом появляется сигнал низкого уровня (фиг.4б). Через интервал времени

чика 3 появляется отрицательный импульс (фиг.4 в), который, пройдя через элементы И 12 и 13, устанавливает на инверсном выходе триггера 5 сигнал высокого уровня. Этот же отрицательный импульс с выхода переноса счетчика 3 через элементы И 12,13 и 14 стробирует счетчики 2 и 3 и далее через инвертор 10 - триггер 4 знака. Процесс формирования выходных сигналов счетчиков 2 и 3 триггера 5 повторяется. В результате на выходе триггера 5 (фиг,4 б) получается сигнал со скважностью

У--М-. оп

Одновременно с работой названных выше элементов входной сигнал через схему 37 ограничения поступает на вход сумматора 33 и суммируется с сигналом на выходе регистра 34. В первоначальный момент времени на выходе регистра 4 находится нулевой сигнал. По приходе импульса с генератора 1 регистр 34 записывается сигнал с выхода сумматора 33 и далее процесс повторяется. В результате происходит нарастание сигнала на выходе сумматора 33 и на выходе его переполнения появляется сигнал высокого уровня с частотой fi, которая при наличии двойной разрядности сумматора 33 и регистра 34 линейно зависит от величины N входного сигнала:

f 1

f0N о 2п

При появлении сигнала высокого уровня на выходе переполнения сумматора 33 формирователь 32 импульсов формирует короткие импульсы, которые через элементы ИЛИ 8 и 9 поступают либо на вход прямого счета, либо на вход обратного счета двоично-шестиричного счетчика 35. При этом на первом, втором, третьем выходах названного счетчика формируются периодические сигналы (фиг.4 г,д,е соответственно), причем частота feyx появления одного и того же кодового сочетания на этих выходах определяется выражением

т вых

f 1

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 2002 |

|

RU2216850C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАНИЯ ЧАСТОТЫ | 2016 |

|

RU2644070C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ДВИГАТЕЛЯ | 1995 |

|

RU2111608C1 |

| Цифровой модулятор для преобразователя частоты | 2021 |

|

RU2762287C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ ДВУХФАЗНОГО АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 1997 |

|

RU2126198C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ УПРАВЛЕНИЯ СИНХРОННЫМ ЭЛЕКТРОДВИГАТЕЛЕМ | 2012 |

|

RU2517423C1 |

| Цифровой модулятор для преобразователя частоты | 2021 |

|

RU2774161C1 |

| Цифровой модулятор для управления синхронным двигателем | 2019 |

|

RU2711049C1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1990 |

|

SU1777168A1 |

| Цифровой модулятор | 1991 |

|

SU1798907A1 |

Изобретение относится к импульсной технике и может быть использовано в преобразователях систем управления для управления цифровым модулятором, транзисторных ключей в силовой цепи асинхронного двигателя. Цифровой модулятор содержит генератор 1 прямоугольных импульсов, счетчики 2 и 3, триггер 4 знака, триггер 5, элементы ИЛИ 6, 7, 8 и 9, инвертор 10, элементы И 11, 12, 13, 14, 16, 17, 18, 19, 20 и 21, элементы И-НЕ 22, 23, 24, 25, 26 и 27, дешифратор 28, формирователи 29, 30, 31 и 32 импульсов, сумматор 33, регистр 34, двоично-шестеричный счетчик 35, схему 36 сброса, схему 37 ограничения, выходные шины 38, 39, 40, 41, 42 и 43, шину 44 входного сигнала, шину 45 Знака. 2 табл., 4 ил.

Т2

2JL fo

где п - количество разрядов двоичного счетчика, после стробирования на выходе счет

В зависимости от кодового сочетания сигналов выходов двоично-шестиричного счетчика 35 и сигнала с триггера 4 знака дешифратор 28 и элементы И-НЕ 22, 23, 24, 25, 26 и 27, реализующие логические функции Si - Зб, подают сигналы высокого

уровня на входы той или иной пары элементов И 16,17,18,19, 20 и 21. В результате широтно-модулированный сигнал скважностью у с выхода триггера 5 поступает на соответствующие выходы 38, 39, 40, 41, 42, 43 (фиг.4 ж, з, и, к л,м) цифрового модулятора, причем частота fBbix смены пар работающих выходов меняется в функции входного сигнала.

Формирователи 29, 30 31 импульсов и элемент И 15 необходимы для формирования раздвижки фронтов при смене знака входного сигнала. Таким образом, введение в цифровой модулятор формирователей импульсов, элементов И, дешифратора, элемента ИЛИ, сумматора, элементов И-НЕ,, регистра и двоично-шестиричного счетчика с соответствующими связями позволяет обеспечить в нем способность управления транзисторными ключами в силовой цепи асинхронного двигателя.

Формула изобретения

Цифровой модулятор, содержащий первый и второй счетчики, триггер знака, генератор прямоугольных импульсов, триггер, элемент И, инвертор, три элемента ИЛИ, первый и второй формирователи импульсов, схему ограничения и схему сброса, причем выход генератора прямоугольных импульсов соединен с первыми входами первого и второго элементов ИЛИ, вторые входы которых соединены соотвественно с прямым и инверсным выходами триггера знака, первый вход которого соединен с шиной знака, а второй вход - с выходом инвертора, вход которого соединен с входами записи информации-первого и второго счетчиков, выход переноса первого счетчика соединен с первым входом первого элемента И, разрядные входы второго счетчика соединены с общей шиной, а выход переноса - с первым входом второго элемента И, разрядные входы первого счетчика соединены с выходом схемы ограничения, разрядные входы которой соединены с шиной входного сигнала, а знаковый вход - с шиной знака, выход схемы сброса соединен с вторым входом второго элемента И, отличающийся тем, что, с целью расширения области применения за счет обеспечения управления цифровым модулятором транзисторных ключей в силовой цепи асинхронного двигателя, в него дополнительно введены третий и четвертый формирователи импульсов, пятый-одиннадцатый элементы И, дешифратор, четвертый элемент ИЛИ, шесть элементов И-НЕ, сумматор, регистр и двоично-шестиричный счетчик, причем выходы первого и второго элементов

ИЛИ соединены соотвественно с входами обратного и прямого счета первого счетчика, выход генератора прямоугольных импульсов - со счетным входом второго

счетчика и первым входом регистра, выход второго элемента И соединен с первым входом третьего элемента И, выход которого соединен с первыми входами триггера и четвертого элемента И, выход которого соеди0 нен с входами записи информации первого и второго счетчиков, прямой выход триггера знака соединен с первым входом третьего элемента ИЛИ и входом первого формирователя импульсов, а инверсный выход - с

5 первым входом четвертого элемента ИЛИ и входом второго формирователя импульсов, выходы первого и второго формирователей импульсов соединены соотвественно с первым и вторым входами пятого элемента И,

0 выход которого соединен с вторыми входами первого и четвертого элемента И и входом третьего формирователя импульсов, выход которого соединен с вторым входом третьего элемента И, выход первого элемен5 та И соединен с вторым входом триггера, инверсный выход которого соединен с первыми входами шестого - одиннадцатого элементов И, первый, второго и третий входы дешифратора соединены соответственно

0 с первым, вторым и третьим выходами двоично-шестиричного счетчика, а четвертый вход - с прямым выходом триггера знака, первый выход дешифратора соединен с первыми входами первого и пятого элементов

5 И-НЕ, второй выход дешифратора - с вторым входом первого и первым входом шестого элементов И-НЕ, третий выход - с первым входом второго и вторым входом шестого элементов И-НЕ, четвертый выход0 с вторым входом второго и первым входом четвертого элементов И-НЕ, пятый выход-с первым входом третьего и вторым входом четвертого элементов И-НЕ, шестой выход - с вторыми входами третьего и пятого элемен5 тов И-НЕ, седьмой выход-с третьими входами второго и четвертого элементов И-НЕ, восьмой выход - с третьим входом третьего и четвертым входом четвертого элементов И-НЕ, девятый выход - с четвертым входом

0 третьего и третьим входом пятого элементов И-НЕ, десятый выход-с третьим входом первого и четвертым входом пятого элементов И-НЕ, одиннадцатый выход- с четвертым входом первого и третьим входом шестого

5 элементов И-НЕ, двенадцатый выход-с четвертыми входами второго и шестого элемен- тов И-НЕ, выходы элементов И-НЕ соединены соответственно с вторыми входами шестого-одиннадцатого элементов И, выход схемы ограничения - с первым входом

сумматора, выход которого соединен с вторым входом регистра, выход которого соединен с вторым входом сумматора, выход переполнения сумматора соединен с входом четвертого формирователя импульсов, выход которого соединен с вторыми вхо дами третьего и четвертого элементов ИЛ И, выхо46

47

Puf. 2.

ды которых соединены соответственно с входами прямого и обратного счёта двоично-шестиричного счетчика, выход схемы сброса - с третьим входом реги- стра, выходы шестого - одиннадцатого элементов И соединены с выходными шинами.

10

Таблица 1

Таблица 2

Фиг. 3.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой широтно-импульсный модулятор | 1987 |

|

SU1478316A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-03-07—Публикация

1991-04-01—Подача