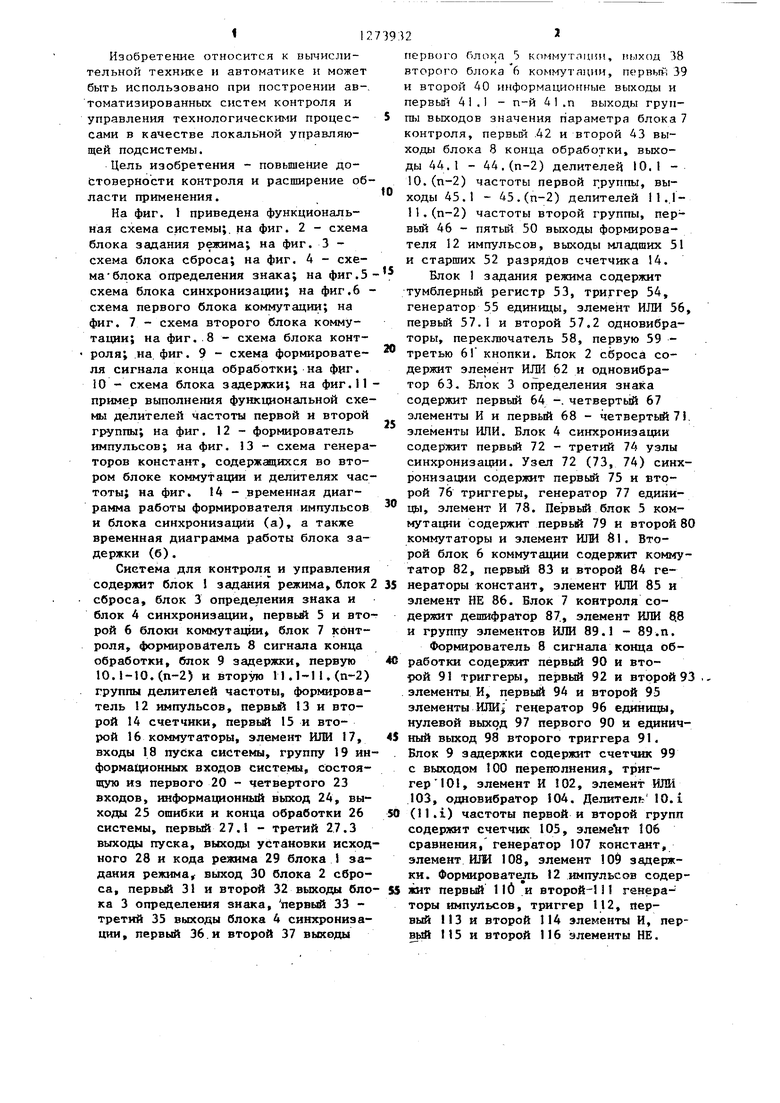

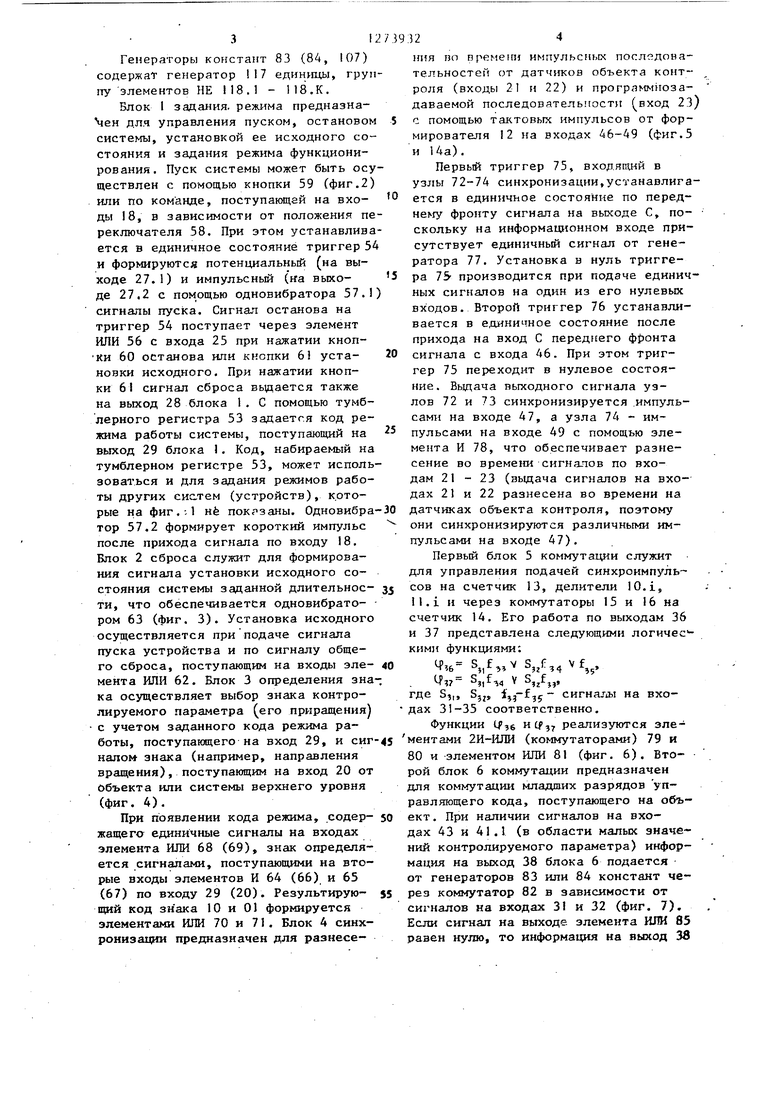

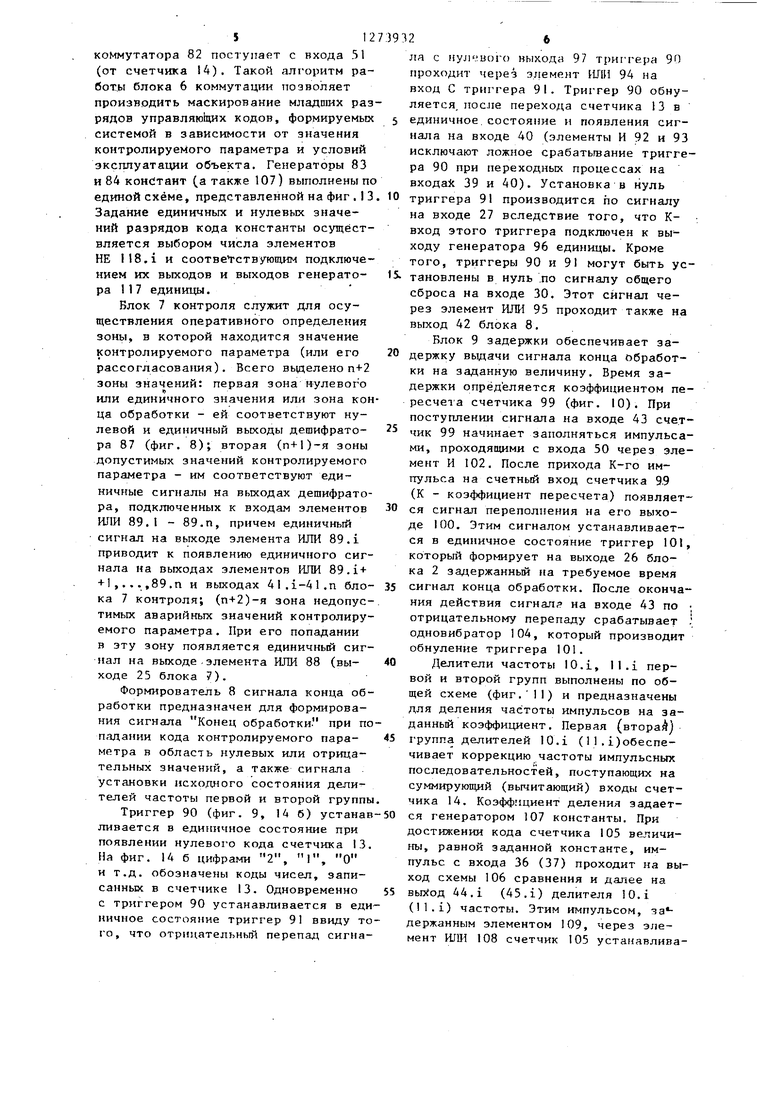

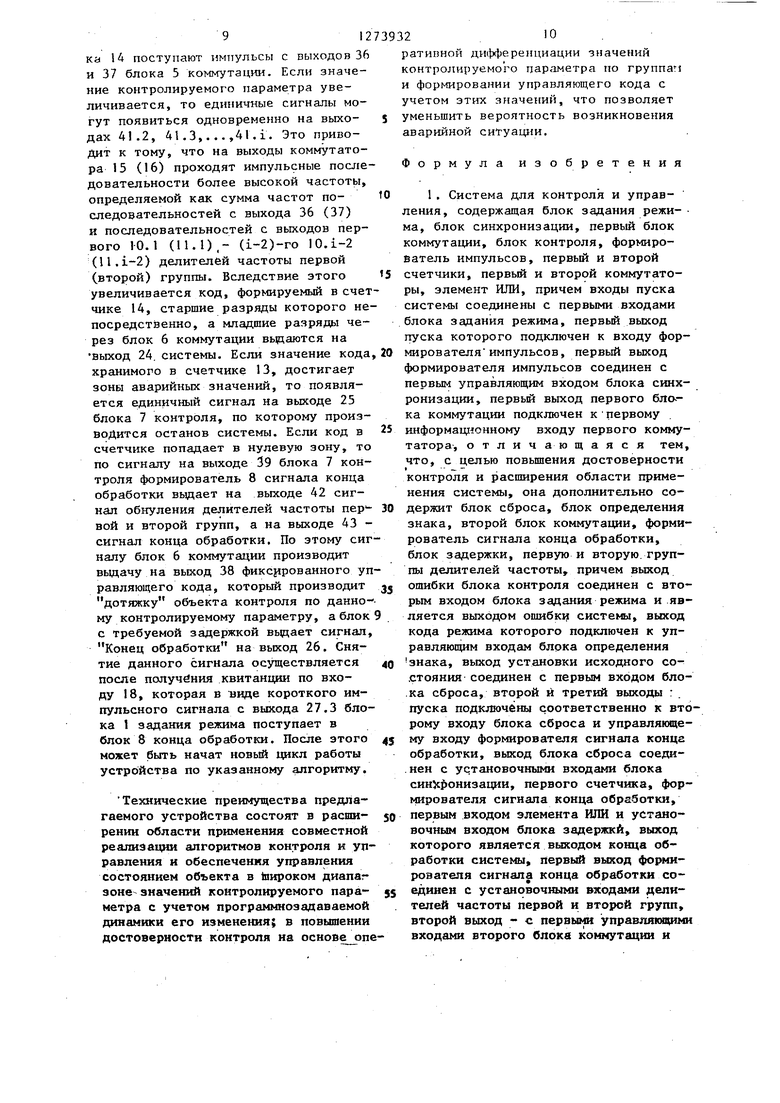

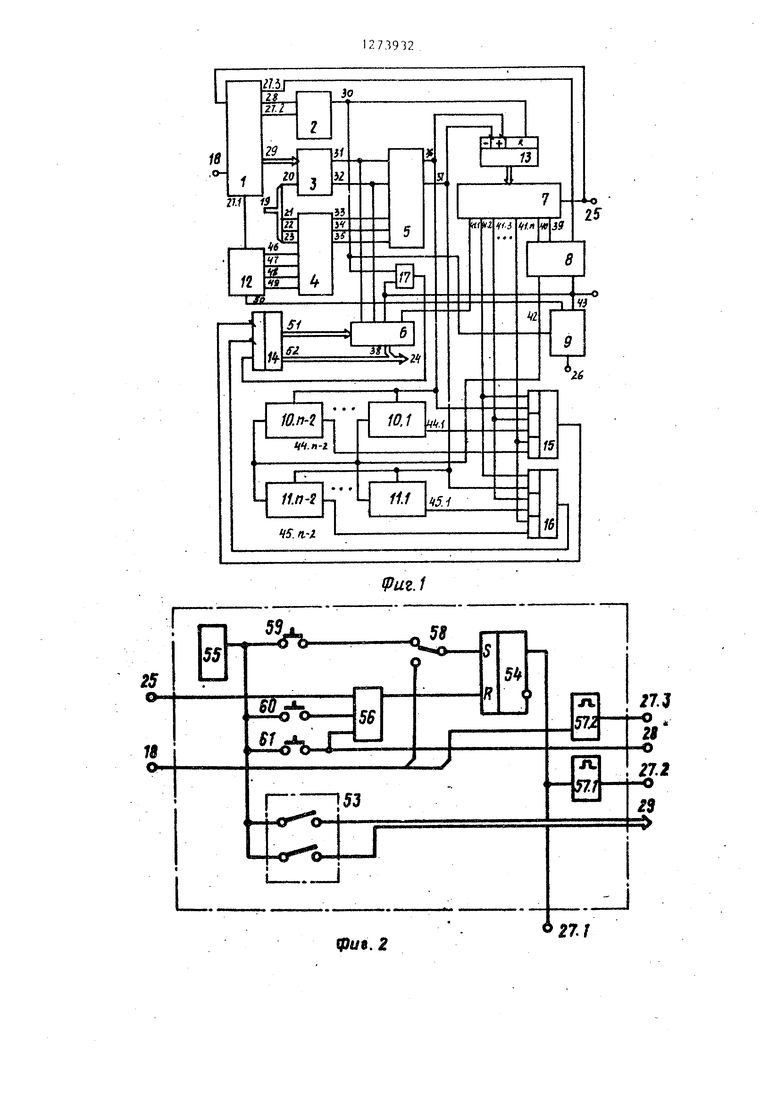

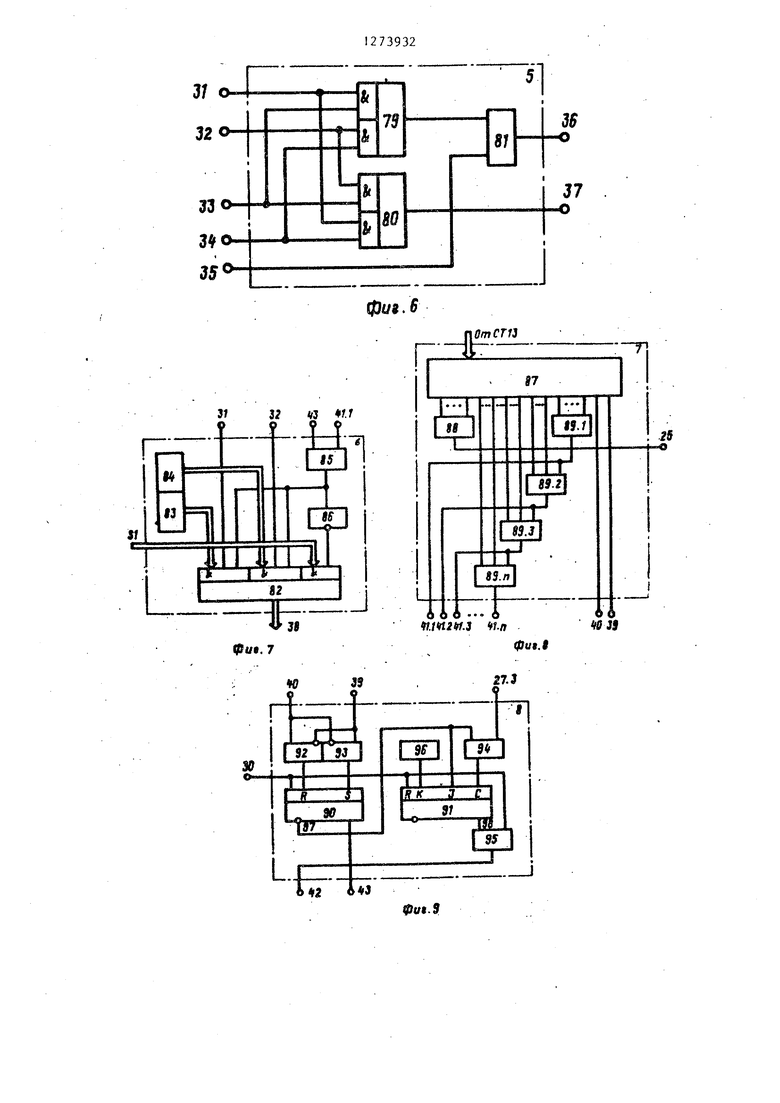

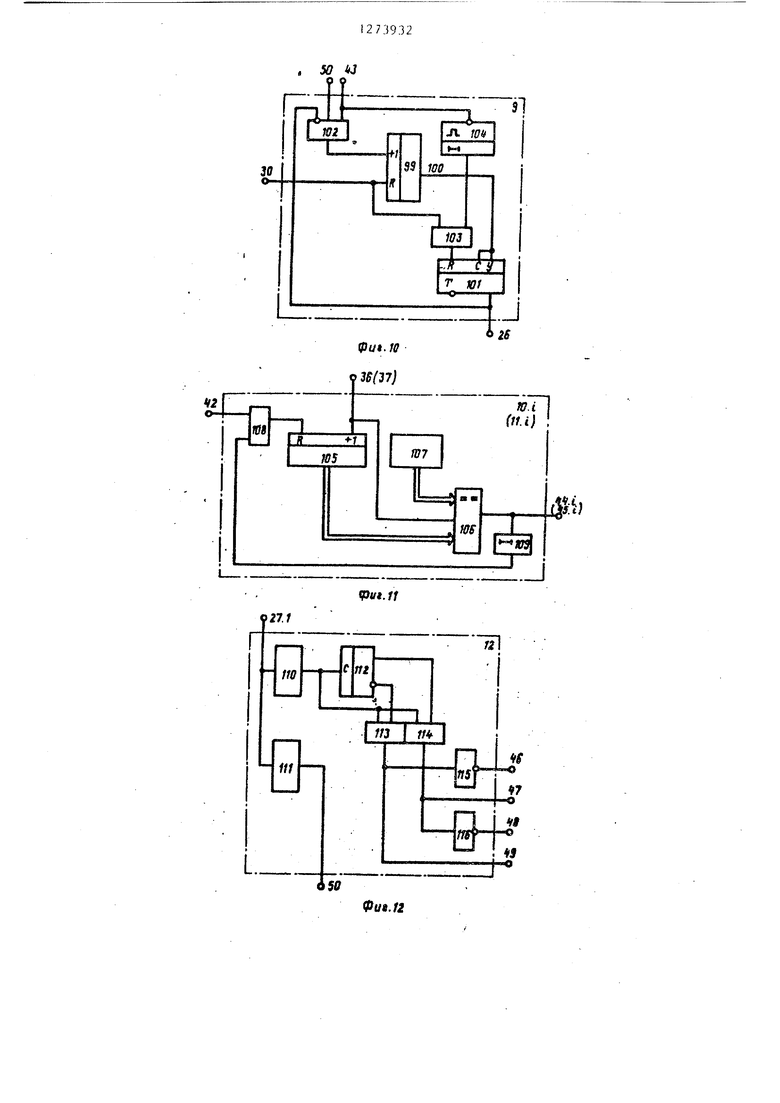

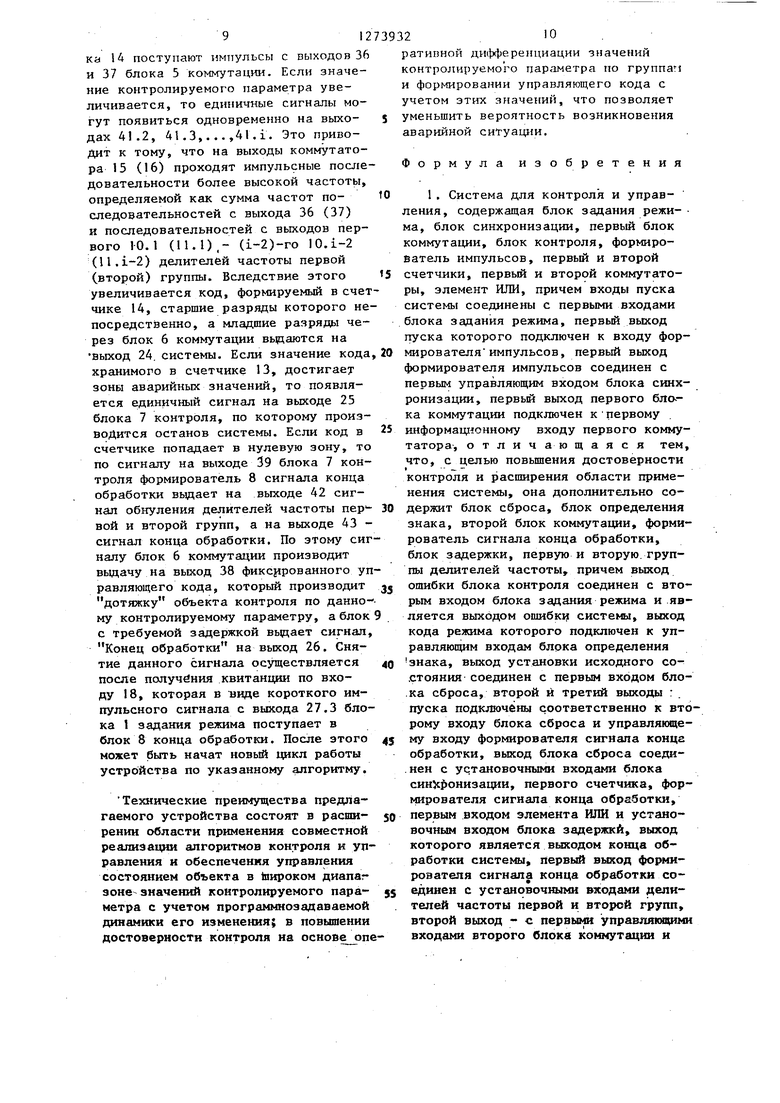

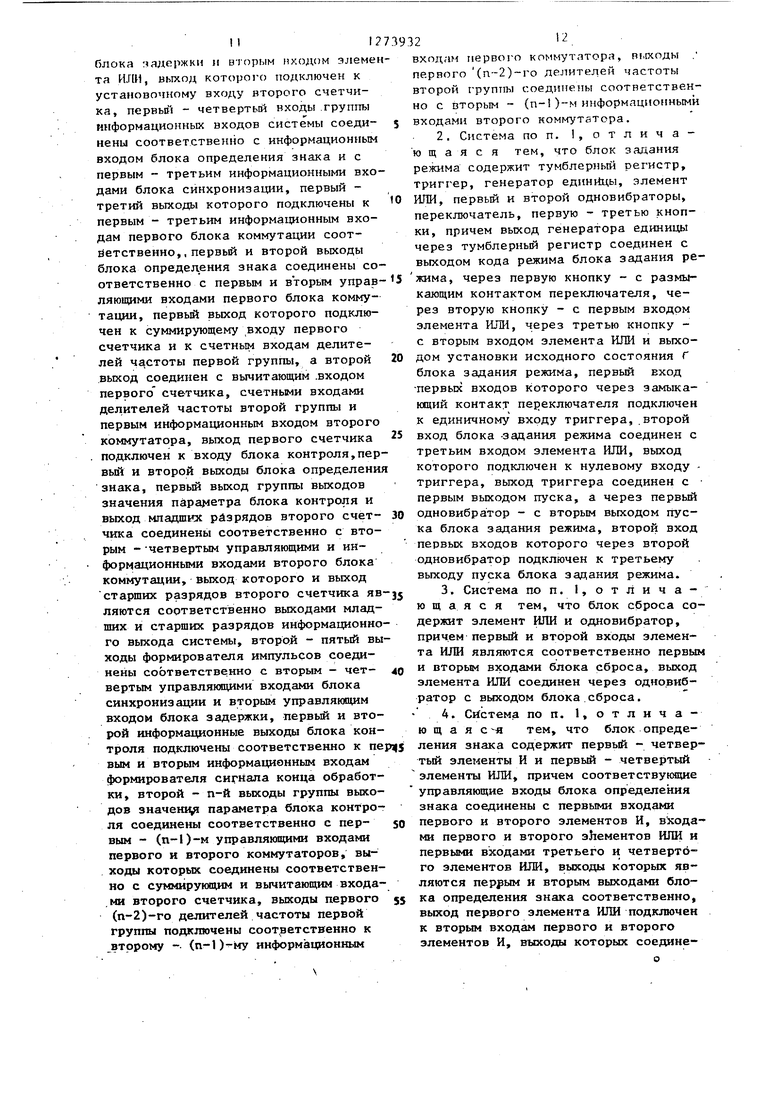

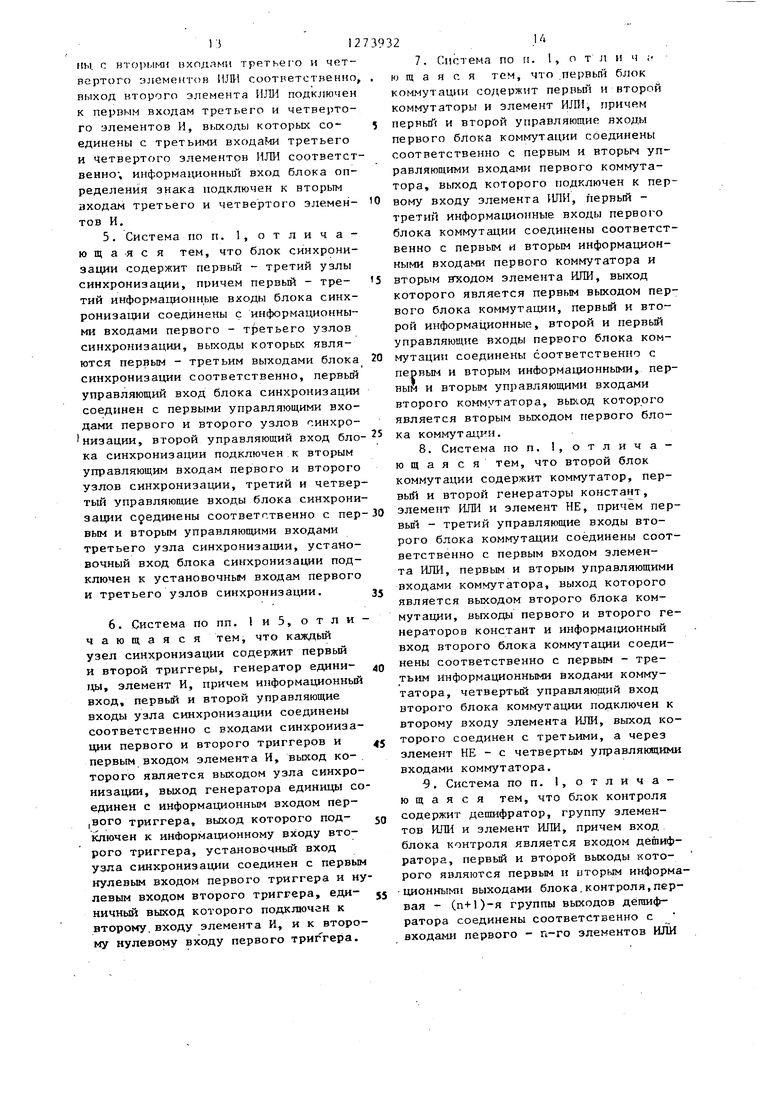

12 Изобретение относится к вычислительной технике и автоматике и может быть использовано при построении ав-. томатизированных систем контроля и управления тexнoлoгичecки и процессами в качестве локальной управляющей подсистемы. Цель изобретения - повышение достоверности контроля и расширение области применения. На фиг. 1 приведена функциональная схема системы;, на фиг. 2 - схема блока задания режима; иа фиг. 3 схема блока сброса; на фиг. 4 - схемаблока определения знака; на фиг.5 схема блока синхронизации; на фиг.6 схема первого блока коммутации; на фиг. 7 - схема второго блока коммутации; на фиг..8 - схема блока конт роля; на фиг. 9 - схема формирователя сигнала конца обработки; на фиг. 10 - схема блока задержки; на фиг.11 пример выполнения функциональной схе мы делителей частоты первой и второй группы; на фиг. 12 - формирователь импульсов; на фиг. 13 - схема генера торов констант, содержащихся во втором блоке коммутации и делителях час тоты; на фиг. 14 - временная диаграмма работы формирователя импульсов и блока синхронизации (а), а также временная диаграмма работы блока задержки (б) . Сиетема для контроля и управления содержит блок задания режима блок сброса, блок 3 определения знака и блок 4 синхронизации, первьв 5 и вто рой 6 блоки коммутации, блок 7 контроля, формирователь 8 сигнала конца обработки, блок 9 задержки, первую 10.1-10.(п-2) и вторую 11.1-П.(п-2) группы делителей частоты, формирователь 12 импульсов, первый 13 и второй 14 счетчики, первый 15 и второй 16 коммутаторы, элемент ИЛИ 17, входы 18 пуска системы, группу 19 ин форма(ионных входов системы, состоящую из первого 20 - четвертого 23 входов, информационный выход 24, выходы 25 ошибки и конца обработки 26 системы, первый 27.1 - третий 27.3 выходы пуска, выходы установки исход ного 28 и кода режима 29 блока 1 задания режима выход 30 блока 2 сброса, первый 31 и второй 32 выходы бло ка 3 определения знака, первый 33 третий 35 выходы блока 4 синхронизации, первый 36.и второй 37 выходы 2 пер1и.)го блока 5 коммутации, пыхещ 38 второго блока 6 коммутации, пе рвьгй 39 второй 40 информационные выходы и первьпЧ 41.1 - п-й 4 1 .п выходы группы выходов значения параметра блока 7 контроля, первьй .42 и второй 43 выходы блока 8 конца обработки, выходы 44.1 - 44.(п-2) делителей 10.1 10.(п-2) частоты первой г.руппы, выходы 45.1 - 45. (п-2) делителей 11..Г11.(п-2) частоты второй группы, первый 46 - пятьп1 50 выходы формирователя 12 импульсов, выходы младших 51 и старших 52 разрядов счетчика 14. Блок 1 задания режима содержит тумблерньй регистр 53, триггер 54, генератор 55 единицы, элемент ИЛИ 56, первый 57.1 и второй 57.2 одновибраторы, переключатель 58, первую 59 третью 6Г кнопки. Блок 2 сброса содержит элемент ИЛ- 62 и одновибратор 63. Блок 3 определения знака содержит первый 64 -. четвертый 67 элементы И и первый 68 - четвертый 71. элементы ИЛИ. Блок 4 синхронизации содержит первьй 72 - третий 74 узлы синхронизации. Узел 72 (73, 74) синхронизации содержит первый 75 и второй 76 триггеры, генератор 77 единицы, элемент И 78. Первый блок 5 коммутации содержит первый 79 и второй 80 коммутаторы и элемент ИШ 81. Второй блок 6 коммутации содержит коммутатор 82, первый 83 и второй 84 генераторы констант, элемент ИЖ 85 и элемент НЕ 86. Блок 7 контроля содержит дешифратор 87, элемент ИЛИ 8,8 и группу элементов ИЛИ 89.1 - 89.п. Формирователь 8 сигнала конца обработки содержит первый 90 и второй 91 триггеры, первый 92 и второй 93 ,, элементы И, первый 94 и второй 95 элементы Ш1И генератор 96 единицы, нулевой выход 97 первого 90 и единичный выход 98 второго триггера 91. Блок 9 задержки содержит счетчик 99 с выходом 100 переполнения, триггер 101, элемент И 102, элемент ИШ1 103, одновибратор 104. Делитель 10.i (ll.i) частоты первой и второй групп содержит счетчик 105, элемент 106 сравнения, генератор 107 констант, элемент ИШ 108, элемент 09 задержки. Формирователь 12 импульсов содержит первый 11Й и второй-111 генераторы импульсов, триггер 112, йервый 113 и второй 114 элементы И, перВ1 й П 5 и второй 116 элементы НЕ. 31 Генераторы констант 83 (84, 107) содержат генератор 17 едннццы, груп пу элементов НЕ 118. - 118.К. Блок 1 задания, режима предназначен для управления пуском, остановом системы, установкой ее исходного состояния и задания режима функционирования. Пуск системы может быть осу ществлен с помощью кнопки 59 (фиг.2) или по команде, поступающей на входы 18, в зависимости от положения пе реключателя 58. При этом устанавлива ется в единичное состояние триггер 54 и формируются потенциальный (на выходе 27.1) и импульсный (на выходе 27.2 с помощью одновибратора 57. сигналы пуска. Сигнал останова на триггер 54 поступает через элемент ИЛИ 56 с входа 25 при нажатии кнопки 60 останова или кнопки 61 устаНОНКИ исходного. При нажатии кнопки 61 сигнал сброса вьщается также на выход 28 блока 1. С помощью тумблерного регистра 53 задается код режима работы системы, поступающий на выход 29 блока 1. Код, набираемый на тумблерном регистре 53, может использоваться и для задания режимов работы других систем (устройств), к.оторые на фиг. , 1 не показаны. Одновибратор 57.2 формирует короткий импульс после прихода сигнала по входу 18. Блок 2 сброса служит для формирования сигнала установки исходного состояния системы заданной длительноети, что обеспечивается одновибратором 63 (фиг. 3). Установка исходного осуществляется при подаче сигнала пуска устройства и по сигналу общего сброса, поступающим на входы элемента ИЛИ 62. Блок 3 определения знака осуществляет выбор знака контролируемого параметра (его приращения) с учетом заданного кода режима работы, поступающего на вход 29, и сигналом- знака (например, направления вращения), поступающим на вход 20 от объекта или системы верхнего уровня (фиг. 4).

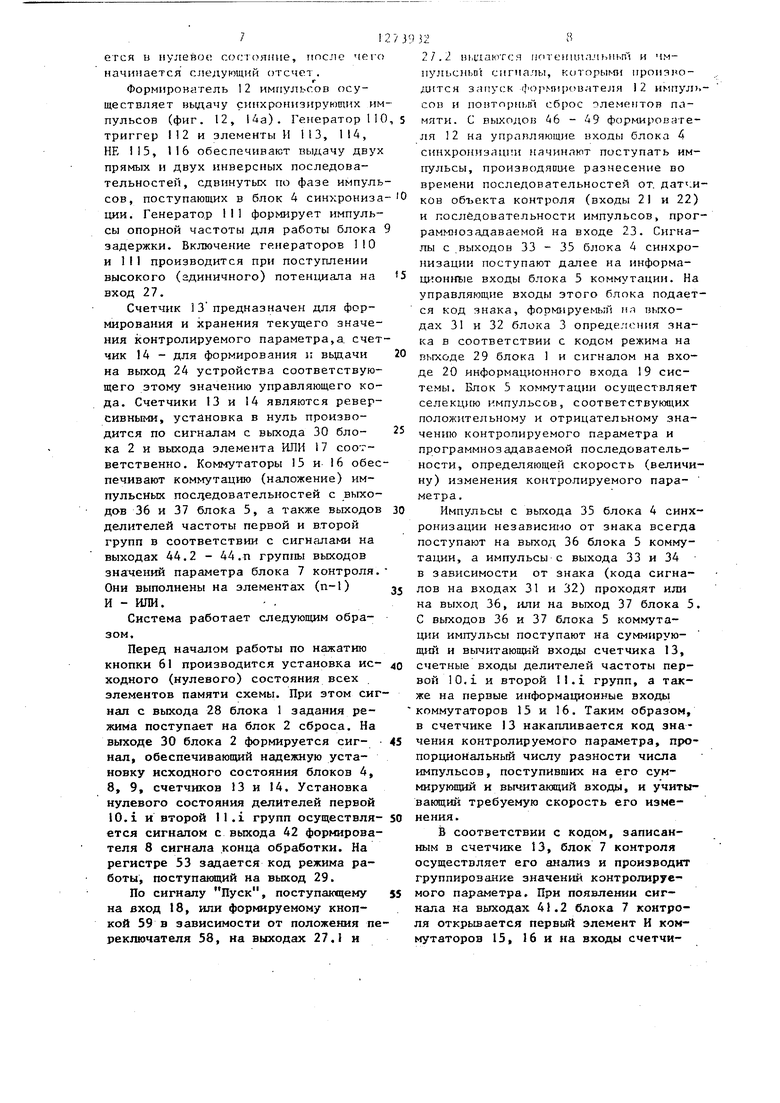

При появлении кода режима, содержащего единичные сигналы на входах элемента ИЛИ 68 (69), знак определяется сигналами, поступающими на вторые входы элементов И 64 (66) и 65 (67) по входу 29 (20). Результирующий код знака 10 и 01 формируется элементами ИЛИ 70 н 71. Блок 4 синхронизации предназначен для разнесе80 и элементом ИЛИ 81 (фиг. 6). Второй блок 6 коммутации предназначен для коммутации младших разрядов управляющего кода, поступающего на объект. При наличии сигналов на входах 43 и 41.1 (в области малых значений контролируемого параметра) информация на выход 38 блока 6 подается от генераторов 83 или 84 констант через коммутатор 82 в зависимости от сигналов на входах 31 и 32 (фиг. 7). Если сигнал на выходе элемента ИЛИ 85 равен нулю, то информация на выход 3d :52 1П1Я по премеш импульсных послс донательностей от датчиков объекта контроля (входы 21 и 22) и прогр«тbtMJioзадаваемой последовательности (вход 23) с помощью тактовых импульсов от формирователя 12 на входах 46-49 (фиг.5 и 14а). Первый триггер 75, входягдий в узлы 72-74 синхронизации,устанавлигается в единичное состояние по переднеьгу фронту сигнала на выходе С, по- скольку на информационном входе присутствует единичный сигнал от генератора 77. Установка в нуль триггера 75 производится при подаче единичных сигналов на один из его нулевых входов. Второй триггер 76 устанавливается в eдини шoe состояние после прихода на вход С переднего ф зонта сигнала с входа 46. При этом триггер 75 пер еходит в нулевое состояние. Выдача выходного сигнала узлов 72 и 73 синхронизируется .импульсами на входе 47, а узла 74 - импульсами на входе А9 с помощью элемента И 78, что обеспечивает разнесение во времени сигналов по входам 21-23 (выдача сигналов на входах 21 и 22 разнесена во времени на датчиках объекта контроля, поэтому они синхронизируются различными импульсами на входе 47). Первый блок 5 коммутации служит для управления подачей синхроимпульсов на счетчик 13, делители lO.i, ll.i и через коммутаторы 15 и 16 на счетчик 14. Его работа по выходам 36 и 37 представлена следующими логичес кимн функциями: S,, v S,,4 V S,f,,, где S f-j-f ,c сигнахл на « 15 ах 31-35 соответственно. Функции дзб Kifjj реализуются элеентами 2И-ИЛИ (коммутаторами) 79 и 512 коммутатора 82 поступает с входа 51 (от счетчика 14). Такой алгоритм работы блока 6 коммутации позволяет производить маскирование младпшх раз рядов управляю1цих кодов, формируемых системой в зависимости от значения контролируемого параметра и условий эксплуатации объекта. Генераторы 83 и 84 констант (а также 107) выполнены по единой схеме, представленной на фиг .13 Задание единичных и нулевых значений разрядов кода константы осуществляется выбором числа элементов НЕ .i и соотве гствутощим подключением их выходов и выходов генератора 117 единицы. Блок 7 контроля служит для осуществления оперативного определения зоны, в которой находится значение контролируемого параметра (или его рассогласования). Всего ньщелено п+2 зоны значений: первая зона иулевого или единичного значения илл зона кон ца обработки - ей соответствуют нулевой и единичный выходы дешифратора 87 (фиг. 8); вторая (п+1)-я зоны допустимых значений контролируемого параметра - им соответствуют единичные сигналы на выходах дешифратора, подключенных к входам элементов ИЛИ 89.1 - 89.п, причем единичный сигнал на выходе элемента ИЛИ 89.1 приводит к появлению единичного сигнала на выходах элементов ИЛИ 89.,...,89.п и выходах 4l.i-41.n блока 7 контроля; (п+2)-я зона недопустимых аварийных значений контролируемого параметра. При его попадании в эту зону появляется единичный сигнал на выходе-элемента ИЛИ 88 (выходе 25 блока 7). Формирователь 8 сигнала конца обработки предназначен для формирования сигнала Конец обработки. при по падании кода контролируемого параметра в область нулевых или отрицательных значений, а также сигнала установки исходного состояния делителей частоты первой и второй группы Триггер 90 (фиг. 9, 14 б) устанав ливается в единичное состояние при появлении нулевого кода счетчика 13 Па фиг. 14 б цифрами 2, 1, О и т.д. обозначены коды чисел, записанных в счетчике 13. Одновременно с триггером 90 устанавливается в еди ничное состояние триггер 91 ввиду то го, что отрицательный перепад сигна6ла с иул.вого выхода 97 тригтера 90 проходит через э;1емент ИЛИ 94 на вход С триггера 91. Триггер 90 обнуляется, после перехода счетчика 13 в единичное.состояние и появления сигнала на входе 40 (элементы И 92 и 93 исключают ложное срабатьшание триггера 90 при переходных процессах на входах 39 и 40). Установка в нуль триггера 91 производится по сигналу на входе 27 вследствие того, что Квход этого триггера подключен к выходу генератора 96 единицы. Кроме того, триггеры 90 и 91 могут быть установлены в нуль .по сигналу общего сброса на входе 30. Этот сигнал через элемент ИЛИ 95 проходит также на выход 42 блока 8. Блок 9 задержки обеспечивает задержку выдачи сигнала конца обработки на заданную величину. Время задержки определяется коэффициентом пеpec4eia счетчика 99 (фиг. 10). При поступлении сигнала на входе 43 счет чик 99 начинает заполняться импульсами, проходящими с входа 50 через элемент И 102. После прихода К-го импульса на счетный вход счетчика 9.9 (К - коэффициент пересчета) появляется сигнал переполнения на его выходе 100. Этим сигналом устанавливается в единичное состояние триггер 101, который формирует на выходе 26 блока 2 задержанный на требуемое время сигнал конца обработки. После окончания действия сигнал на входе 43 по ; отрицательному перепаду срабатывает : одновибратор 104, который производит обнуление триггера 101. Делители частоты lO.i, ll.i первой и второй групп выполнены по общей схеме (фиг. 41) и предназначены для деления частоты импульсов на заданный коэффициент. Первая (втора) группа делителей 10.i (11.i)o6ecneчивает коррекцию частоты импульсных последовательностей, поступающих на суммирующий (вычитающий) входы счетчика 14. Коэффициент деления задается генератором 107 константы. При достижении кода счетчика 105 величины, равной заданной константе, импульс с входа 36 (37) проходит на выход схемы 106 сравнения и далее на выход 44.1 (45.1) делителя 10.1 (11.1) частоты. Этим импульсом, за держанным элементом 109, через элемент ШШ 108 счетчик 105 устанавлива/

ется ь нулевое состояние, после чего начинается следующий отсчет.

г

Формиронатель 12 импульсов осуществляет выдачу синхронизирующих импульсов (фиг. 12, lia). Генератор П триггер 112 и элементы И 113, 114, НЕ 115, 116 обеспечивают выдачу двух прямых и двух инверсных последовательностей, сдвинутых по фазе импульсов, поступающих в блок 4 синхрониза ции. Генерато.р 111 формирует импульсы опорной частоты для работы блока задержки. Включение генераторов ПО и П1 производится при поступлении высокого (адиничного) потен1у1ала на вход 2 7.

Счетчик 1 3предназначе для формирования и хранения текущего значения контролируемого параметра,а. счетчик 14 - для формирования и вьщачи на выход 24 устройства соответствующего этому значению управляющего кода. Счетчики 13 и 14 являются реверсивными, установка в нуль производится по сигналам с выхода 30 блока 2 и выхода элемента ИЛИ 17 соответственно. Коммутаторы 15 и 16 обеспечивают коммутацию (наложение) импульсных последовательностей с выходов 36 и 37 блока 5, а также выходов делителей частоты первой и в.торой групп в соответствии с сигналами на выходах 44.2 - 44.п группы выходов значений параметра блока 7 контроля. Они выполнены на элементах (п-1) И - ИЛИ.

Система работает следующим образом.

Перед началом работы по нажатию кнопки 61 производится установка исходного (нулевого) состояния всех элементов памяти схемы. При этом сигнал с выхода 28 блока 1 задания режима поступает на блок 2 сброса. На выходе 30 блока 2 формируется сигнал, обеспечивающий надежную установку исходного состояния блоков 4, 8, 9, счетчиков 13 и 14. Установка нулевого состояния делителей первой 10.i и второй ll.i групп осуществляется сигналом с выхода 42 формирователя 8 сигнала конца обработки. На регистре 53 задается код режима работы, поступающий на выход 29.

По сигналу Пуск, поступающему на вход 18, или формируемому кнопкой 59 в зависимости от положения переключателя 58, на выходах 27.1 и

9 32В

27.2 ш.иаются иотеии.плльиьт и чмпульс}1ьп1 сигналы, KuTopbihni произпоДО1ТСЯ зяпуск фop иpoвлтeJlя 12 импульсов и понтпряьп сброс олемонтов памяти. С выходов 46 - 49 формирователя 12 на управляющие нходы блока 4 синхро}{изации начинают поступать импульсы, производяпше разнесение во времени последовательностей от. датчиков объекта контроля (входы 21 и 22) и последовательности импульсов, npoi- раммнозадаваемой на входе 23. Сигналы с выходов 33 - 35 блока 4 синхронизащш поступают далее на информационные входы блока 5 коммутации. На управляющие входы этого блока подается код знака, формируемый ил выходах 31 и 32 блока 3 опреде/юния знака в соответствии с кодом режима на выходе 29 блока 1 и сигналом на входе 20 информационного входа 19 системы. Блок 5 коммутации осуществляет селекцию импульсов, соответствующих положительному и отрицательному значению контролируемого параметра и программнозадаваемой последовательности, определяющей скорость (величину) изменения контролируемого параметра.

Импульсы с выхода 35 блока 4 синхронизации независимо от знака всегда поступают на выход 36 блока 5 коммутации, а импульсы с выхода 33 и 34 в зависимости от знака (кода сигналов на входах 31 и 32) проходят или на выход 36, или на выход 37 блока 5. С выходов 36 и 37 блока 5 коммутации импульсы поступают на суммирующий и вычитающий входы счетчика 13, счетные входы делителей частоты первой 10,1 и второй ll.i групп, а также на первые информационные входы коммутаторов 15 и 16. Таким образом, в счетчике 13 накапливается код значения контролируемого параметра, прюпорциональный числу разности числа импульсов, поступивших на его суммирующий и вычитающий входы, и учитывающий требуемую скорость его изменения.

В соответствии с кодом, записанным в счетчике 13, блок 7 контроля осуществляет его анализ и производит группирование значений контролируемого параметра. При появлении сигнала на выходах 41.2 блока 7 контроля открьшается первый элемент И коммутаторов 15, 16 и иа входы счетчика 14 поступают импульсы с выходов 36 и 37 блока 5 коммутации. Если значение контролируемого параметра увеличивается, то единичные сигналы могут появиться одновременно на выходах 41.2, 41.3,..,,41.1. Это приводит к тому, что на выходы коммутатора 15 (16) проходят импульсные последовательности более высокой частоты, определяемой как сумма частот последовательностей с выхода 36 (37) и последовательностей с выходов первого 10.1 (11.1).- (i-2)-ro IO.i-2 (ll.i-2) делителей частоты первой (второй) группы. Вследствие этого увеличивается код, формируемый в счетчике 14, старшие разряды которого непосредственно, а младшие разряды через блок 6 коммутации вьщаются на выход 24. системы. Если значение кода хранимого в счетчике 13, достигае7 зоны аварийных значений, то появляется единичный сигнал на выходе 25 блока 7 контроля, по которому производится останов системы. Если код в счетчике попадает в нулевую зону, то по сигналу на выходе 39 блока 7 контроля формирователь 8 сигнала конца обработки вьщает на выходе 42 сигнал обнуления делителей частоты первой и второй групп, а на выходе 43 сигнал конца обработки. По этому сигналу блок 6 коммутации производит вьщачу на выход 38 фикс 1рованного управляющего кода, который производит дотяжку объекта контроля по данному контролируемому параметру, а блок с требуемой задержкой вьдает сигнал, Конец обработки на выход 26. Снятие данного сигнала осуществляется после получения квитанции по входу 18, которая в тзиде короткого импульсного сигнала с выхода 27.3 блока 1 задания режима поступает в блок 8 конца обработки. После этого может быть начат новый цикл работы устройства по указанному алгоритму.

Технические преимущества предлагаемого устройства состоят в расширении области применения совместной реализации алгоритмов контроля и управления и обеспечения управления состояпием объекта в Ьироком диапаг зоне-значений контролируемого параметра с учетом программнозадаваемой динамики его изменения; в повышении достоверности контроля на основе оперативной ди1{х})еренциации значений KOHTpojtHpyeMoro параметра по группап и формировании управляющего кода с учетом этих значений, что позволяет уменьшить вероятность возникновения аварийной ситуации.

Формула изобретения

1 . Система для контроля и управления, содержащая блок задания режима, блок синхронизации, первый блок коммутации, блок контроля, формирователь импульсов, первый и второй счетчики, первый и второй коммутаторы, элемент ИЛИ, причем входы пуска системы соединены с первыми входами блока задания режима, первый выход пуска которого подключен к входу формирователя импульсов, первый выход формирователя импульсов соединен с первым управляющим входом блока синхронизации, первьй выход первого бло-ка коммутации подключен к первому информационному входу первого коммутатора, отличающаяся тем, что, с целью повьшения достоверности контроля и расширения области применения системы, она дополнительно содержит блок сброса, блок определения знака, второй блок коммутации, формирователь сигнала конца обработки, блок задержки, первую и вторую.группы делителей частоты причем выход ошибки блока контроля соединен с вторым входом блока задания режима и является выходом ошибки системы, выход кода режима которого подключен к управляющим входам блока определения знака, выход установки исходного состояния соединен с первым входом бло.ка сброса, второй и третий выходы : пуска подключены соответственно к второму входу блока сброса и управляющему входу формирователя сигнала конце обработки, выход блока сброса соеди.нен с установочными входами блока синхронизации, первого счетчика, формирователя сигнала конца обработки, первым входом элемента ШШ и установочным входом блока задержки, выход которого является выходом конца обработки системы. Первый выход формирователя сигнала конца обработки соединен с установочными входами делителей частоты первой и второй групп, второй выход - с первыми управляющими входами второго блока коммутации и

блока : ядержкн л вторым нходом элемета ИЛИ, выход которого подключен к установочному входу второго счетчика, nepBbrfi - четвертый входы .группы информационных входов системы соедийены соответственно с информационным входом блока определения знака и с первым - третьим информационными входами блока синхронизации, первый третий выходы которого подключены к первым - третьим информационным входам первого блока коммутации соотйетственно,, первый и второй выходы блока определ.ения знака соединены соответственно с первым и вторым управ ляющими входами первого блока коммутации, первый выход которого подключен к суммирующему входу первого счетчика и к счетным входам делителей частоты первой группы, а второй выход соединен с вычитающим .входом первого счетчика, счетными входами делителей частоты второй группы и первым информационным входом второго коммутатора, выход первого счетчика подключен к входу блока контроля,первьй и второй выходы блока определени знака, первый выход группы выходов значения блока контроля и выход младших разрядов второго счетчика соединены соответственно с вторым --четвертым управляющими и информационными входами второго блока коммутации, выход которого и выход старших разрядов второго счетчика яв ляются соответственно выходами младших и старших разрядов информационного выхода системы, второй - пятый выходы формирователя импульсов соединены соответственно с вторым - четвертым управляющими входами блока синхронизации и вторым управляющим входом блока задержки, первый и второй информационные выходы блока контроля подключены соответственно к пе вым и вторым информационным входам формирователя сигнала конца обработки, второй - п-й выходы группы выходов значен1у1 параметра блока контроля соединены соответственно с первым - (n-l)-M управлякицими входами первого и второго коммутаторов, выходы которых соединены соответственно с суммирующим и вьмитающим входами второго счетчика, выходы первого (п-2)-го делителей частоты первой группы подключены соответственно к второму -. (п-1)му информационным

вхоцаи iiepBOi-o коммутатор;, В1.ходы . первого (п-2)го делителей частоты второй группы соединены соответственно с вторым (п- )-м информационными входами второго коммутатора.

2.Система по п. , отличающая с я тем, что блок задания режима содержит тумблерньй регистр, триггер, генератор единицы, элемент ИЛИ, первьй и второй одновибраторы, переключатель, первую - третью кнопки, причем выход генератора единицы через тумблерный регистр соединен с выходом кода режима блока задания режима, через первую кнопку - с размыкающим контактом переключателя, через вторую кнопку - с первым входом злемента ИЛИ, через третью кнопку с вторым входом элемента ИЛИ и выходом установки исходного состояния Г блока задания режима, первый вход -первых входов которого через замыкающий контакт переключателя подключен к единичному входу триггера, .второй вход блока -задания режима соединен с третьим входом элемента ИЛИ, выход которого подключен к нулевому входу триггера, выход триггера соединен с первым выходом пуска, а через первый одновибратор - с вторым выходом пуска блока задания режима, второй вход первых входов которого через второй одновибратор подключен к третьему выходу пуска блока задания режима.

3.Система по п. I, отличающая с я тем, что блок сброса содержит элемент ИЛИ и одновибратор, причем- первый и второй входы злемента ИЛИ являются соответственно первым и вторым входами блока сброса, выход элемента ИЛИ соединен через одновибратор с выходом блока сброса.

4.Система по п. 1,отличаю щ а я тем, что блок определения знака содержит первый - четвертый элементы И и первый - четвертый элементы ИЛИ, причем соответствующие управляющие входы блока определения знака соединены с первыми входами первого и второго элементов И, входами первого и второго эЬементов ШШ и первыми входами третьего и четвертого элементов ИЛИ, выходы которых являются перрым и вторым выходами блока определения знака соответственно, выход первого элемента ИЛИ подключен к вторым входам первого и второго элементов И, выходы которых соединео

. С BTOpi,iMH входами третьего и четвертого :)лемент(в lUttl соответственно выход второго элемента ЯШ подключен к первым входам третьего и четвертого элементов И, выходы которых со единены с третьими вxoдa IИ третьего и Четвертого элементов ИЛИ соответственно, информационный вход блока определения знака подключен к вторым входам третьего и четвертого эле.ментов И.

5.Система по п. 1, о т л и ч а ю щ а -я с я тем, что блок синхронизации содержит первый - третий узлы синхронизации, причем первый - третий информационные входы блока синхронизации соединены с информационными входами первого - третьего узлов синхронизации, выходы которых являются первым - третьим выходами блока синхронизации соответственно, первый управляющий вход блока синхронизации соединен с первыми управляющими входами первого и второго узлов синхронизации, второй управляющий вход блока синхронизации подключен к вторым управляющим входам первого и второго узлов синхронизации, третий и четвертьй управляющие входы блока синхронизации С9единены соответственно с пер вым и вторым управляющими входами третьего узла синхронизации, установочный вход блока синхронизации подключен к установочным входам первого и третьего узлов синхронизации.

6.Система попп. 1и5, отличающаяся тем, что каждый узел синхронизации содержит первый

и второй триггеры, генератор едини), элемент И, причем информационный вход, первый и второй управляющие входы узла синхронизации соединены соответственно с входами синхронизации первого и второго триггеров и первым входом элемента И, выход ко-, торого является выходом узла синхронизации, выход генератора единицы соединен с информационным входом пер|ВОГО триггера, выход которого подключен к информационному входу второго триггера, установочный вход узла синхронизации соединен с первым нулевым входом первого триггера и нулевым входом второго триггера, едяничный выход которого подключен к второму,входу элемента И, и к второму нулевому входу первого .

7.Система по и. 1, о т л и ч ; ю щ а я с я тем, что первьш блок коммутации содержит периьв и второй коммутаторы и элемент ШШ, причем парный и второй управляющие входы первого блока коммутации соединены соответственно с первым и вторым управляющими входами первого коммутатора, выход которого подключен к первому входу элемента ИЛИ, первый третий информационные входы первого блока коммутации соединены соответственно с первым и вторым информационными входами первого коммутатора и вторым вгходом элемента ИЛИ, выход которого является первым выходом первого блока коммутации, первый и второй информационные, второй и первый управляющие входы первого блока коммутации соединены соответственно с первым и вторым информационными, первым и вторым управляющими входами второго коммутатора, выход которого является вторым выходом первого блока коммутации.

8.Система по п. , отличающая с я тем, что второй блок коммутации содержит коммутатор, первый и второй генераторы констант, элемент ИЛИ и элемент НЕ, причем первьй - третий управляющие входы второго блока коммутации соединены соответственно с первым входом элемента ИЛИ, первым и вторым управляющими входами коммутатора, выход которого является выходом второго блока коммутации, выходы первого и второго генераторов констант и информа1Ц1онный вход второго блока коммутации соединены соответственно с первым - третьим информационными входами коммутатора, четвертый управляющий вход второго блока коммутации подключен к второму входу элемента ИЛИ, выход которого соединен с третьими, а через элемент НЕ - с четвертым управляющими входами коммутатора.

9.Система по п. 1, отличающая с я тем, что блок контроля содержит дешифратор, группу элементов ИЛИ и элемент ИЛИ, причем вход блока контроля является входом дейифратора, первый и второй выходы которого являются первым и вторым информационными выходами блока.контроля,первая - (п+1)-я группы выходов дешифратора соединены соответственно с входами первого - Г4-го элементов ИЛИ 151 группы и элемента ИЛИ, выход которого является выходом ошибки блока кон троля, выходы группы элементов ИЛИ являются.выходами гРУПпы выходов зна чения параметров блока контроля и все, кроме последнего, соединены с входами последующих элементов ИЛИ группы. 10. Система по п. 1, отличающаяся тем, что формирователь сигнала конца обработки содержит пер вый и второй триггеры, первый и второй элементы И, первый и второй элементы ИЛИ, генератор единицы, причем первый информационный вход блока кон ца обработки соединен с инверсным входом первого и прямьм входом второ го элементов И, выходы которых подключены соответственно к. первому нулевому и единичному входам первого триггера, второй информационный вход блока конца обработки соединен с пря мым входом первого и инверсным входом второго элементов И, а управляющий вход блока подключен к первому входу первого элемента ИЛИ, выход ко торого соединен с входом синхронизации второго триггера, выход генерато ра единиц подключен к нулевому инфор мационному входу второго триггера, выход которого соединен с первым вхо дом в.торого элемента ИЛИ, выход кото рого является первым выхрдом блока конца обработки, установочный вход блока конца обработки соединен с нулевым входом второго триггера, первым входом второго элемента ИЛИ и вторым нулевым входом первого триггера, нулевой выход которого подключен к единичному информационному вхо ду второго триггера и второму входу первого элемента ИЛИ, а единичный вы 35од является вторым выходом блока конца обработки. 11. Система по п. 1, о т ли ч а ю щ а я с я тем, что блок задержки содержит счетчик, триггер, элемент И, элемент ИЛИ, одновйбратор, причем первый управляющий вход блока задерж ки соединен с первым входом элемента И, а через одновйбратор - с первым входом элемента ШШ выход которого подключен к нулевому входу триг гера, второй управляющий вход, блока задержки соединен с вторым входом эле 32 мента И, ныход которого подключен к счетному входу счетчика, )зочный вход блока задержки соединен с вторым входом элемента ШВ{ и установочным входом счетчика, выход переполнения которого подключен к информационному входу и входу синхронизации триггера, выход триггера является выходом блока задержки и соединен с третьим входом элемента И. 12. Система по п. 15Отличаю щ а я с я тем, что каждый делитель частоты первой и второй групп содержит счетчик, элемент сравнения, генератор констант, элемент ИЛИ, элемент задержки, причем счетный вход делителя частоты соединен со счетным входом счетчика и управляющим входом элемента сравнения, выход которого является выходом делителя частоты и через элемент задержки соединен с первым входом элемента ИЛИ,установочньй вход делителя частоты подключен к второму входу элемента ИЛИ, выход которого соединен с установочным входом счетчика, выходы счетчика и генератора констант подключены к первому и второму информационным входам элемента сравнения соответственно. 3. Система по п. 1, о т л и ч а-, ю щ а я с я тем, что формирователь импульсов содержит первый и второй генераторы импульсов., триггер, первьп1 и второй элементы И, первый и второй элементы НЕ, причем вход формирователя импульсов соединен с входами цервого и второго генераторов импульсов, вьпсод первого генератора импульсов подключен к первым входам первого и второго элементов Инк входу триггера, нулевой и единичный выходы которого соединены с вторыми входами первого и второго элементов И соответственно, выход первого элемента И через первый элемент НЕ и выход второго элемента И подключены соответственно к первому и второму выходам формирователя импульсов, выход второго элемента И через второй элемент НЕ, выход первого элемента И и выход второго генератора импульсов соединены соответственно с третьим пятым выходами формирователя импульсов .

. 2

(put. 5

Фи9. 6

OmCT J3

-ЦгГг-fi

3t зг w .r

rz

151 I

14

f

uu

i1

i2

-lh ji

Фи. 7

iZd

г5

о о

41 о о

ntmiff.s w./T

tS3i

0ut,t

W39

27.3

50 4J

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для программного управления | 1985 |

|

SU1325409A1 |

| Система для контроля и управления | 1985 |

|

SU1270767A1 |

| Устройство для измерения параметра динамического процесса и управления им с самоконтролем | 1986 |

|

SU1423985A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Цифровая система для программного управления двигателем | 1986 |

|

SU1320793A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Система для контроля и управления | 1985 |

|

SU1269154A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для контроля полупроводниковой памяти | 1985 |

|

SU1319079A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении автоматизированных систем контроля и управления технологическими процессами в качестве локальной управлшощей подсистемы. Целью изобретения является повьшение достоверности контроля и расширение области применения. Система для контроля и управления содержит блок задания режима, блок сброса, блок определения знака и блок синхронизадин, первый и второй блоки коммутации, блок контроля, блок конца обработки,блок задержки, первую и вторую группы делителей частоты, формирователь импульсов, первьй и второй счетчики, первый и второй коммутаторы, элемент ИЛИ. Сущность изобретения состоит в повышении достоверности контроля н расширении области применения путем совместной реализации алгоритмов контроля и управления. Формирование кода контролируемого параметра в виде двух последовательностей импульсов производится с учетом программнозадаваемого значения скорости его изменения. Дифференцирование контроли(Л руемого параметра по величине путем группирования кодов позволяет дифференцировать процесс вьщачи управ- . ляющих сигналов на объект. Формирование управляюпшх сигналов в соответствии с ии})ормацией о действительfc ном состоянии объекта контроля путем изменения их частоты позволяет увеличивать (уменьшать) код, подаваемый на объект. Маскирование в зоне малых значений контролируемого параметра младших разрядов управляющих кодов, поступающих на объект, фиксировакными кодами позволяет учитывать процесс старения объекта. 12 з.п. ф-лы, 14 ил.

9ut.f2

Л

т ад

47 46 49 22 75 715

и & 13

9ff 27 91

Фиг.З

| Микропроцессорные комплекты БИС на основе интегральной инжекционной логики./Подред | |||

| Э.П | |||

| Калошкина | |||

| М.: Радио и связь, 1984, с | |||

| Контрольный стрелочный замок | 1920 |

|

SU71A1 |

| Устройство для контроля дискретных объектов управления | 1977 |

|

SU690499A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-11-30—Публикация

1985-06-04—Подача