ю -vi ел

4 «

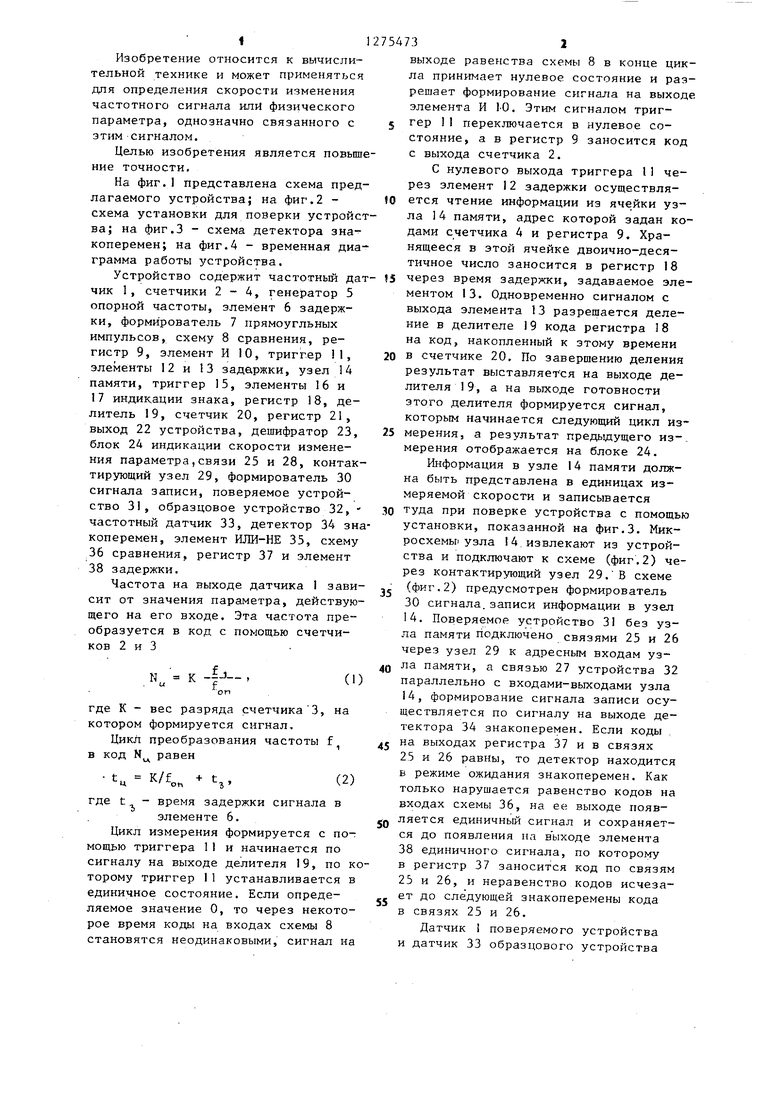

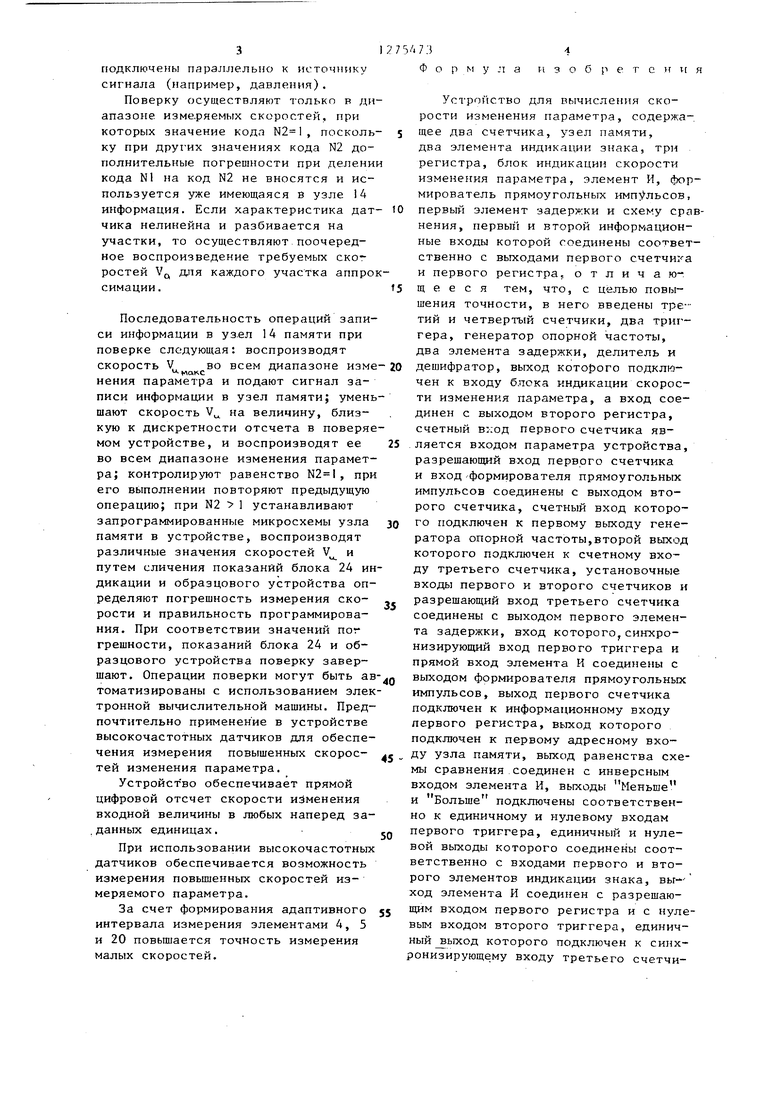

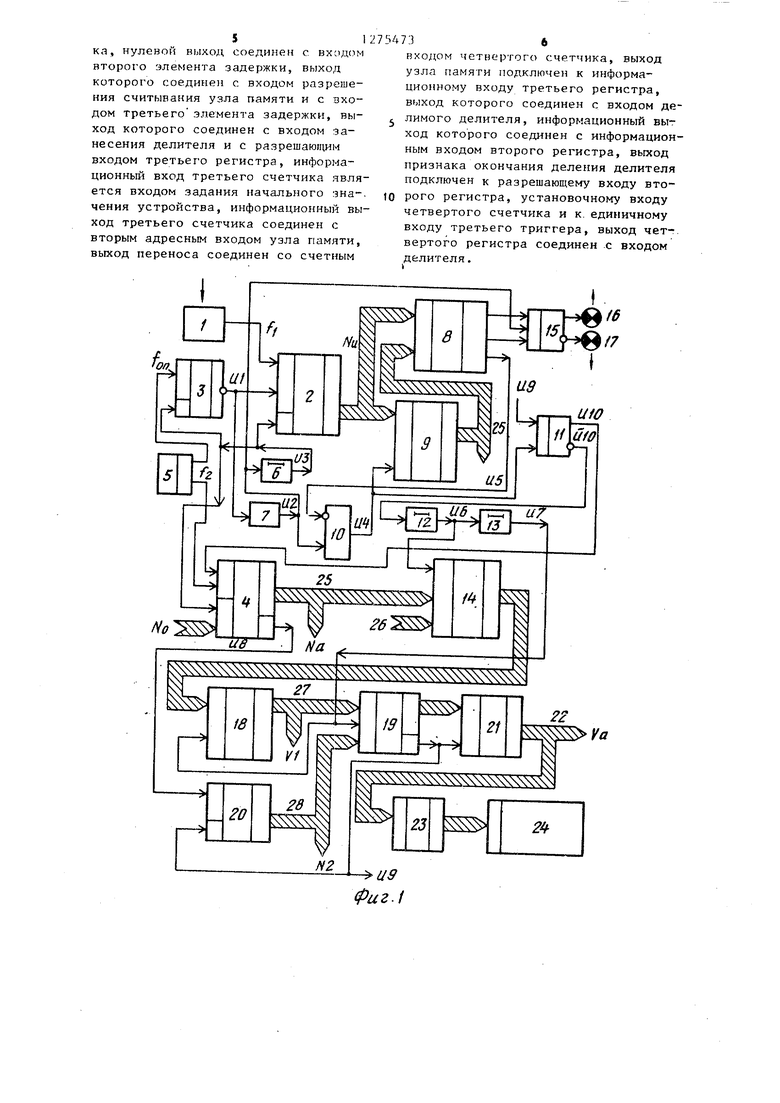

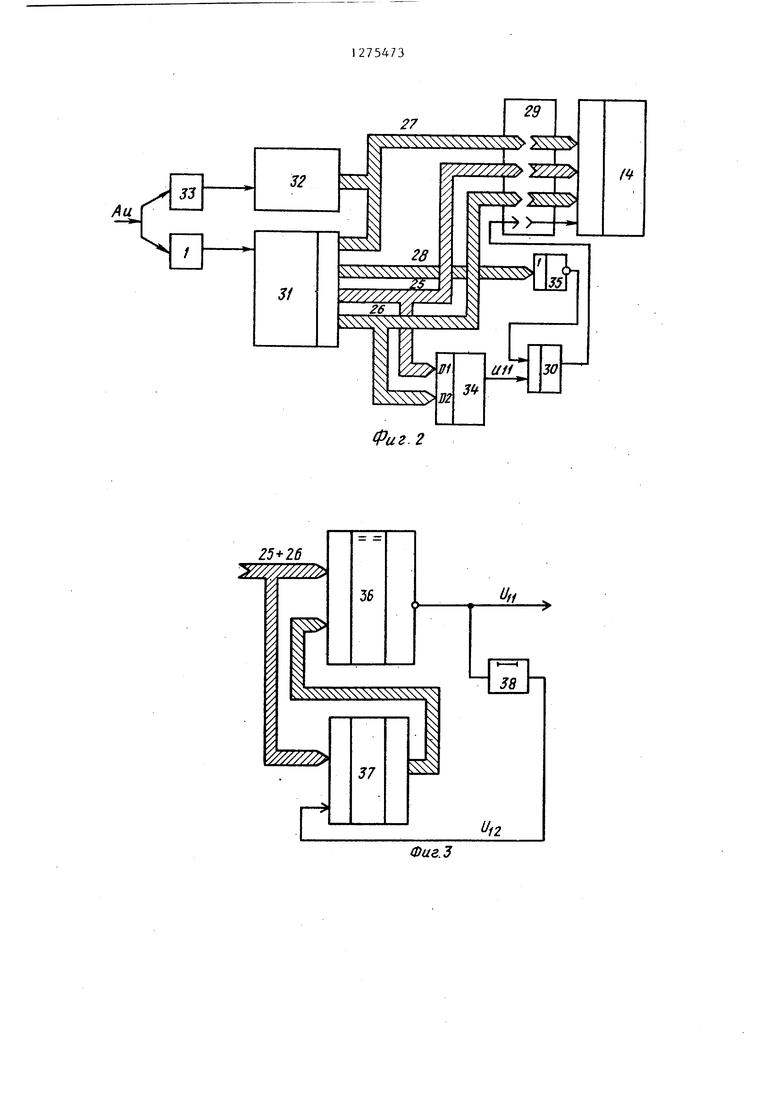

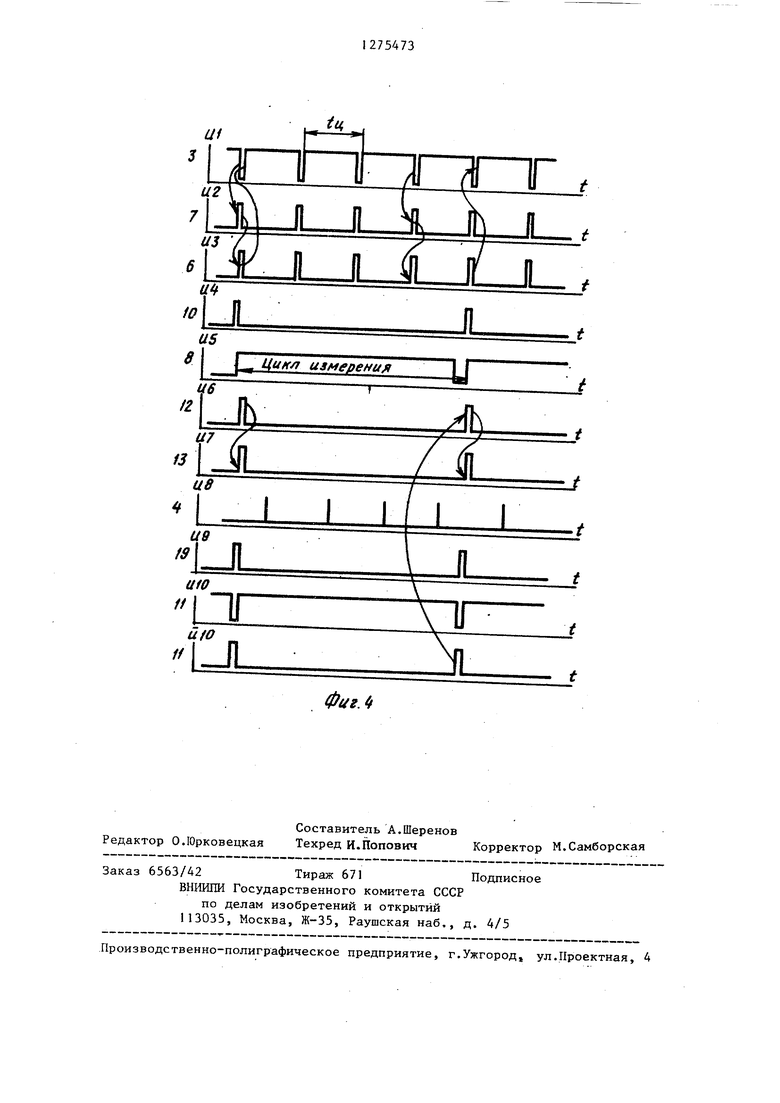

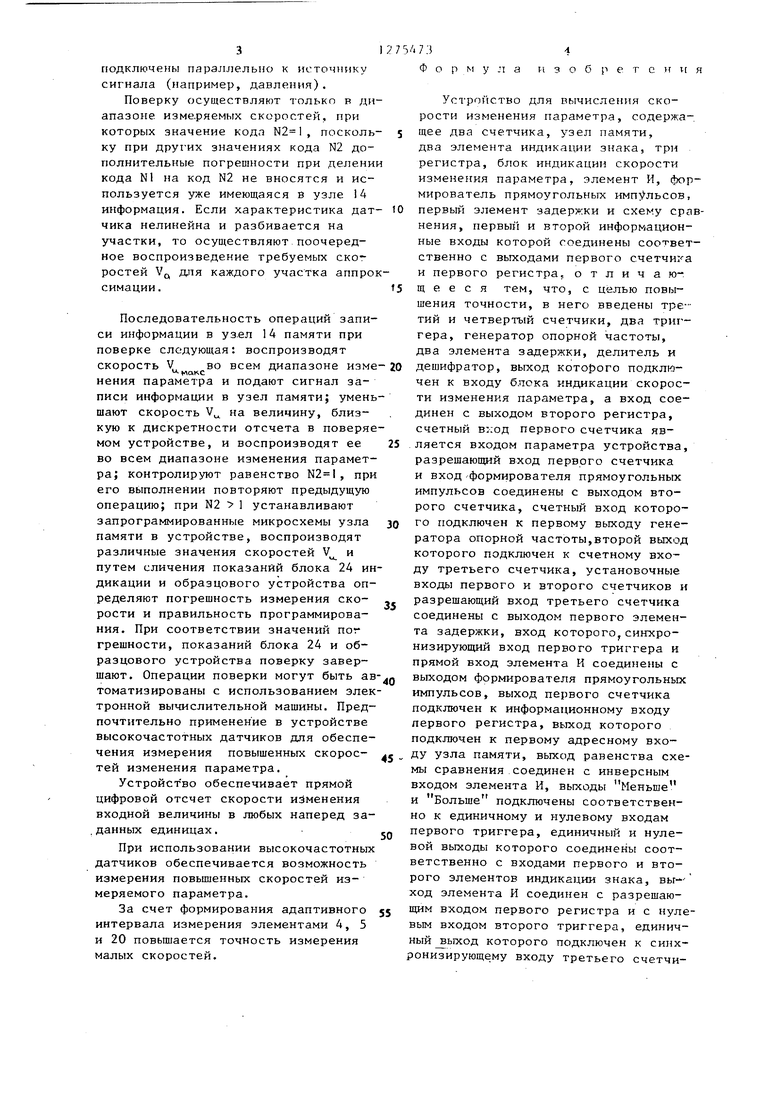

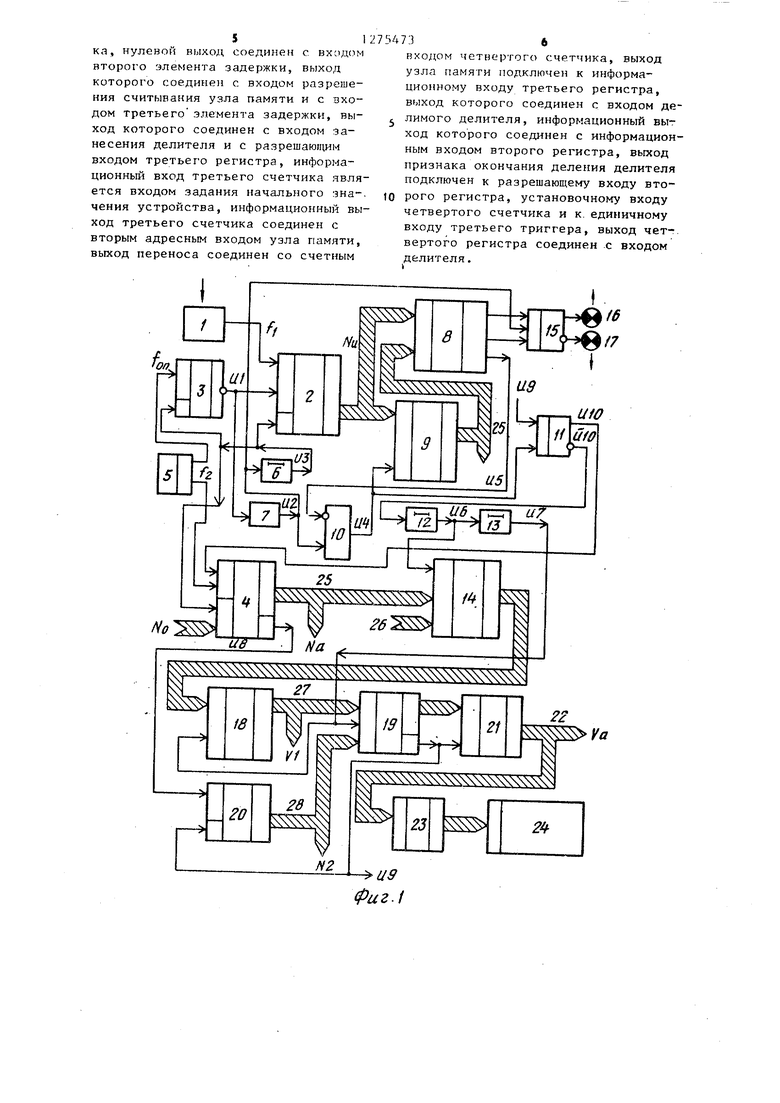

со Изобретение относится к вычислительной технике и может применяться для определения скорости изменения частотного сигнала или физического параметра, однозначно связанного с этим сигналом. Целью изобретения является повьппе ние точности. На фиг.1 представлена схема предлагаемого устройства; на фиг.2 схема установки для поверки устройст ва; на фиг.З - схема детектора знакоперемен; на фиг.4 - временная диаграмма работы устройства. Устройство содержит частотный дат- 3 через чик 1, счетчики 2-4, генератор 5 опорной частоты, элемент 6 задержки, формирователь 7 прямоугльных импульсов, схему 8 сравнения, регистр 9, элемент И 10, триггер 11, элементы 12 и 13 задержки, узел 14 памяти, триггер 15, элементы 16 и 17 индикации знака, регистр 18, делитель 19, счетчик 20, регистр 21, выход 22 устройства, дешифратор 23, блок 24 индикации скорости изменения параметра,связи 25 и 28, контак тирующий узел 29, формирователь 30 сигнала записи, поверяемое устройство 31, образцовое устройство 32, частотный датчик 33, детектор 34 зн коперемен, элемент ИЛИ-НЕ 35, схему 36 сравнения, регистр 37 и элемент 38 задержки. Частота на выходе датчика 1 зави сит от значения параметра, действую щего на его входе. Эта частота преобразуется в код с помощью счетчиков 2 и 3 к -Yгде К - вес разряда счетчика3, на котором формируется сигнал. Цикл преобразования частоты f в код Nj равен K/f -ь t, ,(2 ц оп - время задержки сигнала в элементе 6. Цикл измерения формируется с по мощью триггера 11 и начинается по сигналу на выходе делителя 19, по торому триггер 11 устанавливается единичное состояние. Если определяемое значение О, то через некото рое время коды на входах схемы 8 становятся неодинаковыми, сигнал н 32 выходе равенства схемы 8 в конце цикла принимает нулевое состояние и разрешает формирование сигнала на выходе элемента И ЬО. Этим сигналом триггер 1I переключается в нулевое состояние, а в регистр 9 заносится код с выхода счетчика 2. С нулевого выхода триггера 11 через элемент 12 задержки осуществляется чтение информации из ячейки узла 14 памяти, адрес которой задан кодами счетчика 4 и регистра 9. Хранящееся в этой ячейке двоично-десятичное число заносится в регистр 18 время задержки, задаваемое элементом 13. Одновременно сигналом с выхода элемента 13 разрешается деление в делителе 19 кода регистра 18 на код, накопленный к этому времени в счетчике 20, По завершению деления результат выставляется на выходе делителя 19, а на выходе готовности этого делителя формируется сигнал, которым начинается следующий цикл измерения, а результат предыдущего из-. мерения отображается на блоке 24. Информация в узле 14 памяти должна быть представлена в единицах измеряемой скорости и записывается туда при поверке устройства с помощью установки, показанной на фиг.З. Микросхемы узла 14 извлекают из устройства и подключают к схеме (фиг.2) через контактирующий узел 29.В схеме (фиг.2) предусмотрен формирователь 30 сигнала.записи информации в узел 14. Поверяемое устройство 31 без узла памяти подключено связями 25 и 26 через узел 29 к адресным входам узла памяти, а связью 27 устройства 32 параллельно с входами-выходами узла 14, формирование сигнала записи осуществляется по сигналу на выходе детектора 34 знакоперемен. Если коды на выходах регистра 37 и в связях 25 и 26 равны, то детектор находится в режиме ожидания знакоперемен. Как только нарушается равенство кодов на входах схемы 36, на ее выходе появляется единичный сигнал и сохраняется до появления на выходе элемента 38 единичного сигнала, по которому в регистр 37 заносится код по связям 25 и 26, и неравенство кодов исчезает до следующей знакоперемены кода в связях 25 и 26. Датчик поверяемого устройства и датчик 33 образцового устройства 3 подключены параллельно к источтижу сигнала (например, давления). Поверку осуществляют только в ди апазоне измеряемых скоростей, при которых значение кода , посколь ку при других значениях кода N2 дополнительные погрешности при делени кода N1 на код N2 не вносятся и используется уже имеющаяся S узле 14 информация. Если характеристика дат чика нелинейна и разбивается на участки, то осуществляют поочередное воспроизведение требуемых скоростей VQ для каждого участка аппро симации. Последовательность операций записи информации в уз.ел 14 памяти при поверке следующая: воспроизводят скорость У во всем диапазоне изме нения параметра и подают сигнал записи информации в узел памяти; умень шают скорость V на величину, близкую к дискретности отсчета в поверяе мом устройстве, и воспроизводят ее во всем диапазоне изменения параметра; контролируют равенство , при его выполнении повторяют предыдущую операцию; при N2 1 устанавливают запрограммированные микросхемы узла памяти в устройстве, воспроизводят различные значения скоростей V и путем сличения показаний блока 24 ин дикации и образцового устройства определяют погрешность измерения скорости и правильность программирования. При соответствии значений nor грешности, показаний блока 24 и образцового устройства поверку завершают. Операции поверки могут быть ав томатизированы с использованием элек тронной вычислительной машины. Предпочтительно применение в устройстве высокочастотных датчиков для обеспечения измерения повышенных скороетей изменения параметра. Устройство обеспечивает прямой цифровой отсчет скорости изменения входной величины в любых наперед за,данных единицах. При использовании высокочастотных датчиков обеспечивается возможность измерения повышенных скоростей измеряемого параметра. За счет формирования адаптивного интервала измерения элементами 4, 5 и 20 повышается точность измерения малых скоростей. 7 34 Форм у л а и 3 о б р е т с ff и я Устройство для вычисления скорости изменения параметра, содержащее два счетчика, узел памяти, два элемента индикации знака, три регистра, блок индикации скорости изменения параметра, элемент И, формирователь прямоугольных импульсов, первый элемент задержки и схему сравнения, первый и второй информационные входы которой соединены соответственно с выходами первого счетчиг а и первого регистра, отличающееся тем, что, с целью повышения точности, в него введены третий и четвертый счетчики, два триггера, генератор опорной частоты, два элемента задержки, делитель и дешифратор, выход которого подключен к входу блока индикации скорости изменения параметра, а вход соединен с выходом второго регистра, счетный вход первого счетчика является входом параметра устройства, разрешающий вход первого счетчика и вход формирователя прямоугольных импульсов соединены с выходом второго счетчика, счетный вход которого подключен к первому выходу генератора опорной частоты,второй выход которого подключен к счетному входу третьего счетчика, установочные входы первого и второго счетчиков и разрещающий вход третьего счетчика соединены с выходом первого элемента задержки, вход которого,синхронизирующий вход первого триггера и прямой вход элемента И соединены с выходом формирователя прямоугольных импульсов, выход цервого счетчика подключен к информационному входу первого регистра, выход которого подключен к первому адресному входу узла памяти, выход равенства схемы сравнения соединен с инверсным входом элемента И, выходы Меньше и Больше подключены соответственно к единичному и нулевому входам первого триггера, единичный и нулевой выходы которого соединены соответственно с входами первого и второго элементов индикации знака, выход элемента И соединен с разрешающим входом первого регистра и с нулевым входом второго триггера, единичный ыход которого подключен к синхонизирующему входу третьего счетчика, нулевой В1лход соединен с входсж второго элемента задержки, выход которого соединен с входом разрешения считывания узла памяти и с входом третьегоэлемента задержки, выход которого соединен с входом занесения делителя и с разрешающим входом третьего регистра, информационный вход третьего счетчика явля ется входом задания начального :значения устройства, информационный вы ход третьего счетчика соединен с вторым адресным входом узла памяти, выход переноса соединен со счетным входом четвертого счетчика, выход узла памяти подключен к информационному входу третьего регистра, в)1ход которого соединен с входом делимого делителя, информационный выход которого соединен с информационным входом второго регистра, выход признака окончания деления делителя подключен к разрешающему входу второго регистра, установочному входу четвертого счетчика и к. еди1гичному входу третьего триггера, выход четвертого регистра соединен с входом делителя,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для метрологической поверки цифровых вольтметров | 1982 |

|

SU1049847A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Система для передачи хронометрической информации | 1984 |

|

SU1251152A1 |

| Устройство для автоматической поверки электроизмерительных приборов | 1985 |

|

SU1307420A1 |

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Устройство поверки приборов на затирание | 1984 |

|

SU1180822A1 |

| Устройство для вычисления производной частотно-импульсных сигналов | 1976 |

|

SU734729A1 |

| Устройство для поверки ваттметров | 1985 |

|

SU1267312A1 |

| Тренажер радиотелеграфиста | 1983 |

|

SU1124369A1 |

Изобретение относится к области вычислительной техники и позволяет определять скорость изменения частотного сигнала или физического параметра, однозначно Связанного с этим сигналом. Цель изобретения повышение точности. Устройство со держит частотный датчик, счетчики, генератор опорной частоты, элементы задержки,.формирователь прямоугольных импульсовi схему сравнения, узел памяти, триггер, регистры, дешифратор, блок индикации, контактирующий узел, Элемент И, формирователь сигнала записи, детектор знакоперемен, элемент ШШ-НЕ. Точность повышается за счет формирования адаптив-т него интервала измерения. 4 ил. с S

Фиг.З

Авторы

Даты

1986-12-07—Публикация

1984-10-10—Подача