1

kJ3o6peTeHHe относится к автоматике и вычислительной технике, в частности, к устройствам формирования цифрового кода производной частотно-импульсного сигнала.

Известно частотно-импульсное дифференцирующее устройство, содержащее блок приращения периода, блок возведения в куб, элемент И и счетчик результата l|.

Недостаток устройства - пониженная точность измерения производной.

Известно также частотно-импульсное дифференцирующее устройство, содержащее блок управления, генератор опорной частоты, частотомер мгновенных значений, блок измерения периодов, управляемый делитель частоты, счетчик импульсов, элементы и группы элементов И и ИЛИ 2.

Недостаток устройства - сложность конструктивной реализации.

Наиболее близким к изобретению является устройство для вычисления произч водной частотно-импульсного сигнала.

содержащее блок приращения периода, соединенный первым входом с входом устройства, первым выходом - с первым входом элемента И, а вторым выходом - с входом .обнуления счетчика результата, подключенного счетным входом к выходу элемента И, соединенного вторым входом, с выходом первого управляемого делите- . ля частоты, счетный вход которого подключен к выходу второго управляемого

10 делителя частоты, а управляющий вход соединен с выходом первого регистра памяти, подключенного первым информационным входом к выходу первого блока элементов И, соединенного первым вхо15дом с выходом второго регистра памяти и с управляющим входом второго управляемого делителя частоты,подключенного счетным входом к выходу третьего управляемого делителя астоты, счетный

20 вход которого соединен с выходом генератора опорной частоты и подключен через делитель частоты к счетному входу счетчика периода, соединенного выходом с перпьгм входом второго блока элементов , подключенного выходом к информационному входу второго регистра памяти, причем вторые входы обоих блоков элементов И и входы обнуления регистров, памяти и счетчика периодов соединены с соответствующими выходами блока управления, подключенного входом к выходу устройства, причем управляющи вход третьего управляемого делителя

частоты подключен через третий регистр памяти к выходу второй группы элементов И З.

Недостаток устройства - сложность конструктивной реализации.

Цель изобретения - упрощение устройства.

С этой целью в устройстве для вычисления производной частотно-импульсных сигналов, содержащем блок прираще- ния периода, соединенный первым входом с входом устройства, первым выходом с первым входом элемента И, а вторым выходом с входом обнуления счетчика результата, подключенного счетным входом к выходу элемента И,

соединенгюго вто- выходом первого упрЬвляе- рым входом с мого делителя частоты, счетный вход которого подключен к выходу второго управляемого делителя частоты, а управ- ляющий вход соединен с выходом первого регистра памяти, подключенного информационным входом к выходу первого блока элементов И, соединенного первым входом с выходом второго регистра памя ти и с управляющим входом второго управляемого делителя частот, подключённого счетным входом к выходу третьего управляемого делителя частоты, счетнь1й вход которого соединен с выходом генератора опорной частоты и подключен через делитель частоты к счетному входу счетчика периода, соединенного выходом с первым входом второго блока элементов И, подключенного выходом к информационному входу второго регистра памяти, причем -вторые входы обоих блоков элементов И и входы обнуления регистров памяти и счетчика периода соединены с соответствующим выходами бло ка управления, подключеного входом к входу устройства, дополнительно выход делителя частоты подключен к второму входу блока гсриращения периода, соединенного третьим входом с выходом второге регистра памяти и управляющим входом т),)етьего управляемого делителя частоты.

Кроме этого, блок приращения периода выполнен содержащим узел управления, триггоры, формирователи, элемент задержки, элементы И и ИЛИ, группу элементов И, и счетчик, подключенный выходом к входу первого формирователя, первому входу первого элементов И, первому входу первого элемента ИЛИ и пер Бому входу узла управления, второй вход которого через второй формирователь соединен с первым выходом первого триггера, соединенного счетным входом с первым входом блока приращения периода и подключенного вторым выходом через третий формирователь к первому входу второго элемента И, второму входу первого элемента ИЛИ и первому входу третьего элемента И, соединенного вторым входом с выходом первого формирователя и подключенного выходом, к шине индикации нулевых значений производной и первому входу второго элемента ИЛИ, второй вход которого соединен с шиной запуска, а выход второго элемента ИЛИ подключен к установочному входу первого триггера и через элемент задержки соединен с первым входом второго триггера и установочным входом третьего триггера, подключенного счетны входом к выходу первого элемента ИЛИ, первым выходом - к первому выходу блока приращения периода, а вторым выходом - к входу четвертого формирователя, соединенного выходом с вторым выходом блока приращения периода, причем второй вход второго триггера, подключенного выходом к второму входам первого и второго элементов И, соединен с выходом третьего элемента ИЛИ, входы которого соответственно подключены к выходам первого и второго элементов И и входам четвертого триггера, выходыкоторого соединены с шинами индикации знака производной, а счетный вход счетчика подключен к выходу четвертого элемента И, соединенного первым входом со вторым входом блока приращения периода и подключенного вторым входом к первому выходу узла управления, второй и третий выходы которого соединены соответственно с первым входом группы элементов И и входом обнуления счетчика, подключенного установочным входом к выходу группы элементов И, соединенной вторым входом с третьим входом блока приращения периода;

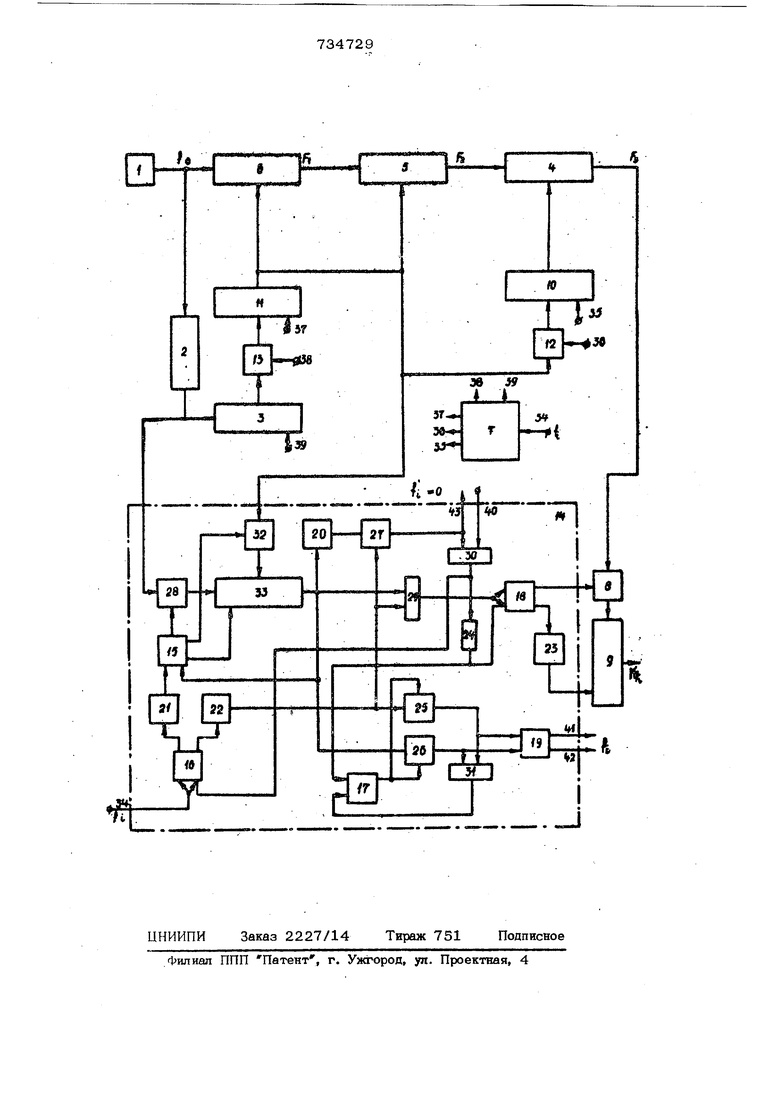

На чертеже изображена блок-схема устройства. Устройство содержит генератор 1 опорной частоты, делитель 2 частоты, счетчик 3 периода, первый, второй и третий управляемые делители 4, 5 и 6, частоты, блок 7 управления, элементы 8 И, счетчик 9 результата, первый и второй регистры Ю и 11 памяти, первый и второй блоки 12 к 13 элементов И и блок 14 приращения периода. Блок приращения периода содержит уаел 15 управления первый, второй, третий и чет вертый триггеры 16, 17, 18 и 19, первый, второй, третий и четвертый формирователи 20, 21, 22 и 23, элемент 24 задержки, первый, второй, третий и чет- вертый элементы 25, 26, 27 и 28 И, первый, второй и третий элементы 29, 30 и 31 ИЛИ, группу элементов 32 И, и счетчик 33, соответствующие входные и выходные шины 34-43. Каждый из управляемых делителей частоты 4, 5 и 6 выполнен на счетчике и группе элемен тов И. Устройство работает следующим обра зом. В блоке 7 из последовательности импульсов входного сигнала f. , поступающего на шину 34, формируются управляющие сигналы, определяющие по выкод ным шинам 35 - 39 последовательность работы узлов устройства. С выхода гене ратора 1 импульсы опорной частоты поступают на, счетный вход управляемого делителя 6 и вход делителя 2. В целите ле 2 опорная частота делителя на пос- тоинный коэффициент К. В управляемых делителях 4-6 входная частота делитс на коэффициенты, записанные в виде параллельного кода в регистры памяти 10 и 11. С выхода делителя 2 импульсы поступают на счетный вход счетчика 3 периода, где они суммируются в проме жутках времени, равных текущим периодам входного сигнала, формируемым пут подачи на вход обнуления счетчика 3 сигнала с щины 39 блока 7 управления. На выходе счетчика 3 в момент предшес вующий обнулению образуется код Ч- -Ir-T. Т - текущий 1 -и период вхо ного сигнала f . Этот код через блок 13 элементов И по сигналу управления с шины 38 блока 7 переписывается в регистр памяти 11 предварительно очищенный от предыдуще информации сигналом с щины 38 блока 7 Перед обнулением регистра 11 памя- тя информация о коде N, предыдущего ( i - 1)-го периода входного сигнала переписывается., с шины 36 через открытый сигналом блок 12 элементов И в регистр 1О памяти, предварительно обнуленный сигналом с шины 35. В управляемом делителе 6 опорная частота делится на коэффициент деления Nf; V -к.,. Полученная выходная частота F повторно делится; на коэффициент NT-- в управляемом делителе 5, на выходе которого образуется частота р П 2- о 1 Частота F делиггся в управляемом делителе 4 на коэффициент Nyj . пропорциональный предыдущему ( 1 -l).4viy периоду входной частоты. Частота FT, на выходе делителя 4 соответственно равна. .-х „ с - Jil- Е г Ъ i.,-H М - частота, соответствующая ( 1-1)-му периоду входного сигнала. Эта частота в промежутке времени, на который открывается элемент 8 И, суммируется в счетчике 9 результата. Время отпускания элемента И определяет блок 14 приращения периода. Блок 14 работает следующим образом. По сигналу пуск, поступающему с шины 40 через элемент 30 ИЛИ на установочный вход триггера 16, последний устанавливается в единичное состояние. Этот же входной сигнал, пройдя через элемент 24 задержки, устанавл1шает триггер 18 в единичное состояние, а триггер 17 в нулевое состояние. Задержка необходима для того, чтобы импульс с формирователя 22 по перепаду напряжения триггера 16, не установил триггеры 18 и 17 в противоположные начальные состояния. Первый импульс входной частоты - переводит триггер 16 в состояние, при котором на входе формирователя 21 образуется импульс по перепаду напряжения ,на выходе триггера 16. Этот импульс запускает узел управления, 15 по его второму входу. Сначала выходным сигналом узла 15 обнуляется счетчик 33, затем окутывается группа элементов 32 И, через которую в счетчик 33 из регистра 11 записывается код Ny , пропорциональный ( 1 -.1)-му периоду входного сигнала, после чего открывается элемент 28 И, через который на счетный вход счетчика 33, работающего в режиме вычитания входных импульсов, начинают поступать импульсы с выхода делителя 2. Обнуление счетчика 33 произойдет через интервал времени, равный . Появив- шийся на выходе счетчика 33 импульс, сдвинутый относительно первого импульса входной частоты { на предыдущий ( 1-1)-ый период, поступает на первый вход узла 15 управления через элемент 29 ИЛИ на счетный вход триггера 18. При этом узлом 15 управления снимается сигнал, отпирающий элемент 28 И, 51 импульсы с выхода делителя 2 не поступают на вход счетчика 33. Второй импульс частоты f; перебрасывает триггер 16 в положение, при котором на выходе формирователя 22 образуется импульс, поступающий на второй вход элемента 29 ИЛИ. Интервал времени между двумя входными импульсами { равен периоду входной частоты { . Если входная частота увеличивается во времени, то ( 1 -1)-ый период больше 1 -го периода f - и импульс с выхода формирователя 22 поступает на элемент 29 ИЛИ раньше импульса с выхода счетчика 33. Если же входная частота уменьшается, то первым на элемент 29 ИЛИ приходит импульс с выхо- да счетчика. 33. По первомуимпульсу, поступившему на элемент 29, ИЛИ, триг гер 18 устанавливается в положение пр котором открывается элемент 8 И и на счетный вход счетчика результата 9 начинают поступать импульсы с делите ля 4. По второму импульсу, поступивше му на элемент 29 ИЛИ, триггер 18 воз вращается в исходное положение, при ко тором элемент 8 И запирается, а по перепаду напряжения в формирователе 23 образуется импульс, переписывающий код из счетчика 9 в выходной регистр (на блок-схеме не показан) и обнуляющий счетчик 9. Время, в течение которого элемент 8 И открыт, равно абсолютной величине приращении 1 -го периода входной частоты - относительно { 1-1)-го периода { . . Следовательно, в момент запирания элемента 8 И в счетчике 9 образуется код Т, Т пропорциональный первой производной входной частоты по времени. По приходу следующего (третьего) импульса цикл изменения повторяется. Знак производной определяется с помощью триггеров 17 и 19, элементов 25 и 26 И и элемента 31 ИЛИ. После установки по сигналу пуск триггера 17 в нулевое состояние, открываются элементы 25 и 26 И и в зависимости от того, какой из импульсов (с выхода счетчика 33 или выхода формирователя 22) придет первым, триггер 19 установится в соответствующее положение, характеризующее знак приращения периода, а следовательно, и знак производной по шинам 41 и 42 индикации знака. . Импульсом, первым прошедшим через один из элеметов 25 и 26 И и затем через элемент 31 ИЛИ, триггер 17 устанавливается в единичное состояние, при этом элементы 25 и 26 И закрываются, и второй импульс через них не проходит, а триггер 19 сохраняет положение, соответствующее первому импуль су. Поменяться знак производной может лишь после того, как производная пройдет через нулевое значение. В этот момент блок 14-устанавливается в исходное положение. Сигнал - О соответствует моменту ЛТ{ О, т. е. когда импульсы на элемент 29 ИЛИ приходят одновременно. Учитывая динамику изменения входного сигнала, выходной импульс с выхода счетчика 33, расширяясь в формирователе 20 (который удлиняет импульсы), сравнивается на элементе 27 И с импульсом с выхода формирователя 22. При совпадении этих импульсов, на выходе элемента 27 И и, соответственно, на шине 43 индикации нулевых значений появляется сигнал, который через элемент 30 ИЛИ устанавливает блок 14 в начальное положение. , Предлагаемое устройство для измерения производной частотно-импульсного ; сигнала отличается от известного простотой, реализации (в частности, упрощения блока приращения периода, отсугствием третьего регистра памяти) при сохранении на прежнем уровне метпрологических характеристик. Формула изобретения 1. Устройство для вычисления производной частотно-импульсных сигналов, содержащее блок приращения периода, сое диненный первым вкодом с входом устрой ства, первым выходом с первым входом элемента И, а вторым выходом - с входом обнуления счетчика результата, подключенного счетным входом к выходу эле мента И, соединенного вторым входом с выходом первого управляемого делитед частоты, счетный вход которого подключен к выходу второго управляемого делителя частоты, а управляющий вход соеди- ней с выходом первого регистра памяти, подключенного информационным входом к выходу первого блока элементов И, соединенного первым входом с выходом второго регистра памяти и с управляющим входом второго втравляемого делителя частоты, подключенного счетным входом к выходу третьего управляемого делитедя частоты, счетный вкод которого соединен с выходом генератора опорной час тоты и подключен через делитель частоты к счетному входу счетчика периода, соединенного выходом с первым входом второго блока элементов И, подключенного выходом к информационному входу второго регистра памяти, причем вторые входы обоих блоков элементов И и входы обнуления регистров памяти и сче чика периода соединены с соответствующими выходами блока управления, подюио ченного входом к входу устройства, отличающееся тем, что, с целью упрощения устройства, выход дели теля частоты подключен к второму входу блока приращения периода, соединенного третьим входом с выходом второго регистра памяти и управляющим входом третьего управляемого делителя частоты 2. Устройство по п. 1, отлича ющееся тем, что блок приращения периода содержит узел управления, триггеры, формирователи, элемент задержки, элемент И и ИЛИ, группу элементов И и счетчик, подключенный выходом ко входу первого формирователя, первому входу первого элемента И, первому входу первого элемента ИЛИ и первому вхо .ду узла управления, второй вход которого через второй формирователь соединен с первым выходом первого триггера, со- 2910 едяненного счетным входом с первым входом блока приращения периода и подключенного вторым выходом через третий формирователь к первому входу второго элемента И, второму входу первого элемента ИЛИ и первому входу третьего элемента И, соединенного вторым входом с выходом первого формирователя и подключенного выходом к шине индикации нунулевых значений производной и первому входу второго элемента ИЛИ, второй вход которого соединен с шиной запуска, а выход второго элемента ИЛИ подключен к установочному входу первого триггера и через элемент задержки соединен с первым входом второго триггера и установочным входом третьего триггера, подключенного счетным входом к выходу первого элемента-ИЛИ, первым выходом - : к первому выходу блока приращения периода, а вторым ьыходом - ко входу четвертого формирователя, соединенного выходом со вторым выходом блока приращения периода, причем второй вход второго триггера, подключенного выходом ко вторым входам первого и второго элементов И, соединен с выходом третьего элемента ИЛИ, входы которого соответственно подключены к выходам первого и второго элементов И и входам четвертого триггера, выходы которого соединены с шинами индикации знака производной, а счетный вход счетчика подключен к выходу четвертого элемента И, соединенного первым входом с, вторым входом блока приращения периода и подключенного вторым входом к третьему выходу узла управления, второй и третий выходы которого соединены соответственно с первым входом группы элементов И и входом обнуления сметчика, подключенного установочным входом к выходу группы элементов И, соединенной вторым входом с третьим входом блока приращения периода. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР Ns 39986О, кл. О 06 F 7/38, 1971. 2.Авторское свидетельство СССР по заявке К 2119484/24, кл. Q Об G 7/18; 1975. 3.Авторское- свидетельство СССР по заявке № 2395060, кл. C3i 06 I 3/00, 11.О8.76 (прототип)

Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дифференцирования частотно-импульсных сигналов | 1978 |

|

SU742967A1 |

| Устройство для преобразования разности частотно-импульсных сигналов в код | 1976 |

|

SU750728A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1976 |

|

SU624244A1 |

| Дискретный умножитель частоты | 1977 |

|

SU736099A1 |

| Устройство для дифференцирова-Ния чАСТОТы СлЕдОВАНия иМпульСОВ | 1978 |

|

SU798881A1 |

| Часточно-импульсное дифференцирующее устройство | 1977 |

|

SU691891A1 |

| Умножитель частоты импульсов | 1978 |

|

SU780175A1 |

| Устройство для преобразования частоты в код | 1977 |

|

SU696604A1 |

| Цифровой частотомер | 1975 |

|

SU783701A1 |

| Управляемый делитель частоты | 1982 |

|

SU1046936A1 |

Авторы

Даты

1980-05-15—Публикация

1976-08-18—Подача