Изобретение относится к вычислительной технике, в частности к устройствам для обработки данных, и может быть использовано в различных информационно-измерительных и управляющих системах, в системах моделирования с аппаратурной реализацией. 1)ункциЙ5 в устройствах дискретной обработки сигналов, везде, где необходимо вычислять значение полинома при заданном значении аргумента.

Цель изобрелгения - повьшение быстродействия при вычислении значений степенного ряда от с овокупности чисел, представляющих собой детерминированную функцию, квантованную по уровню и по времени.

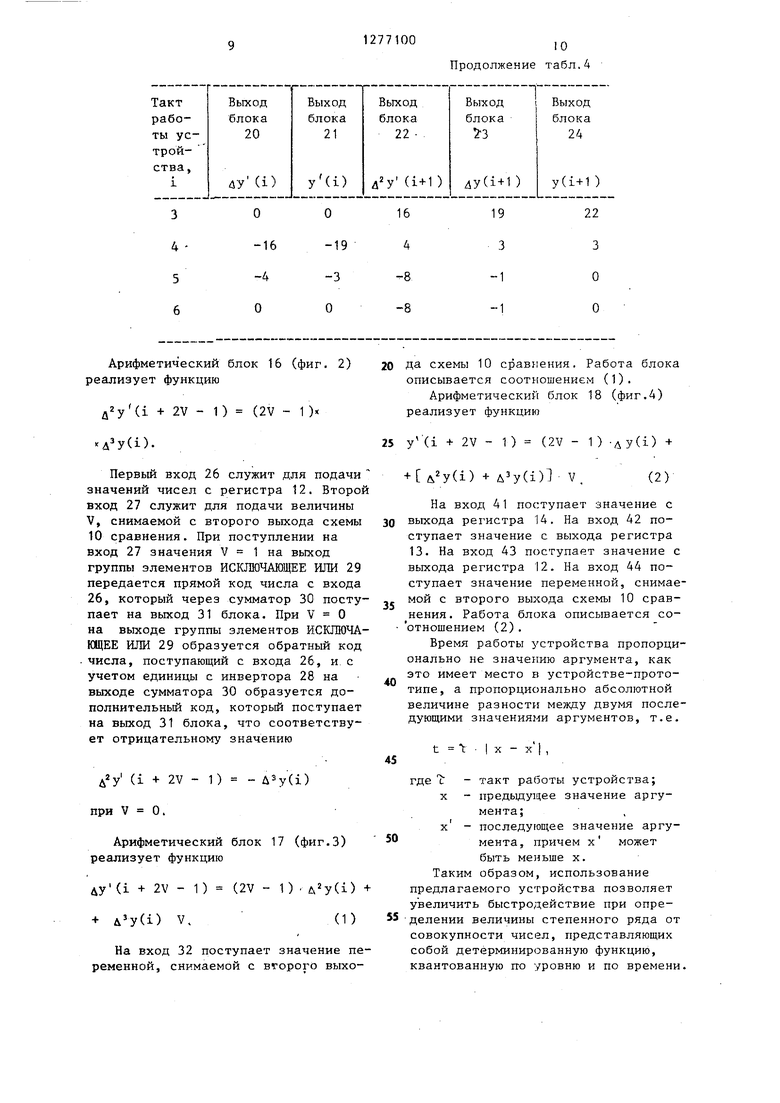

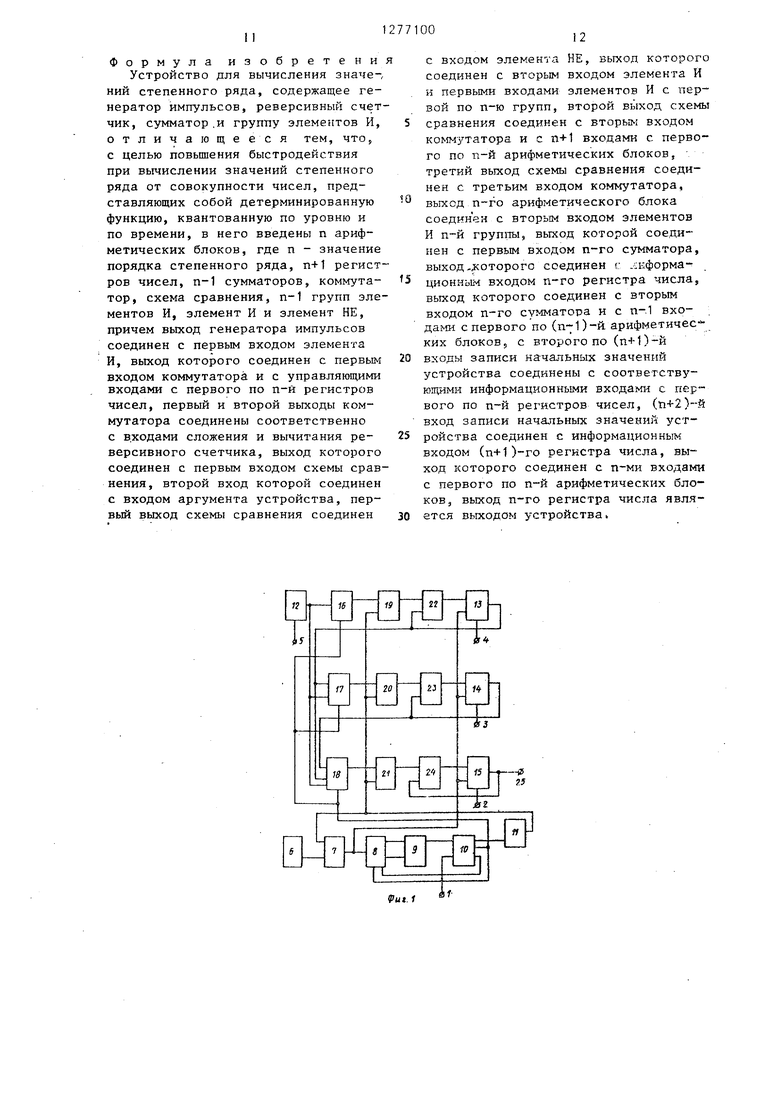

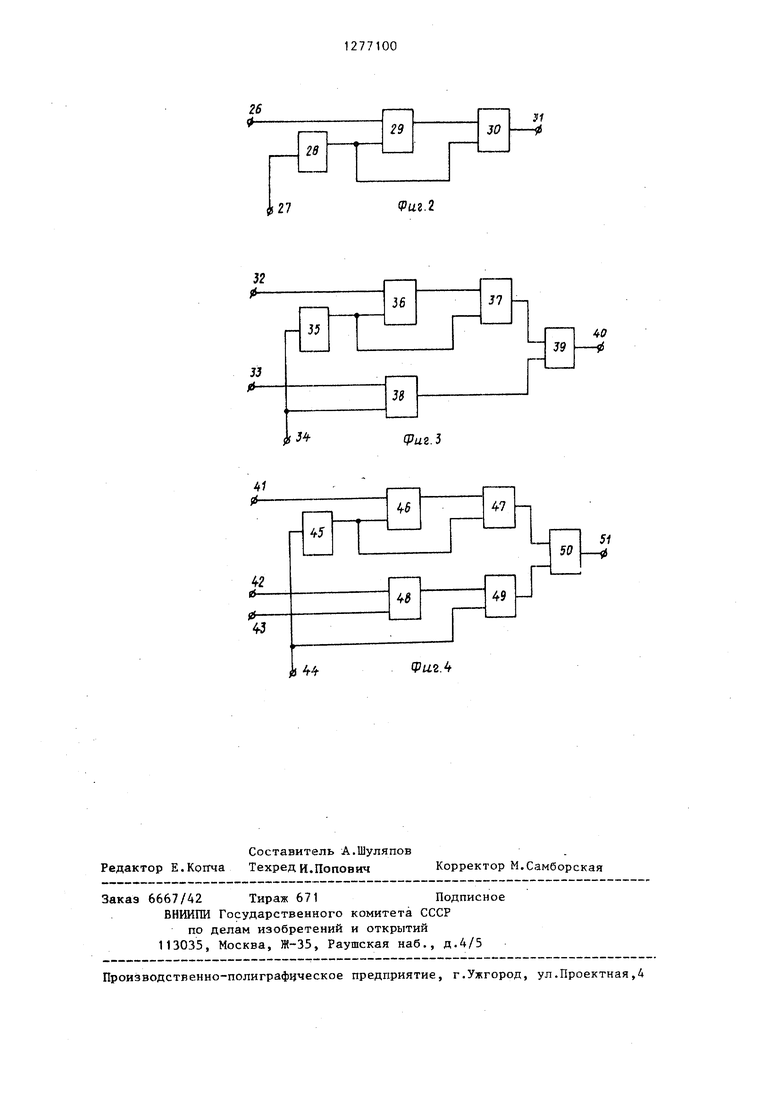

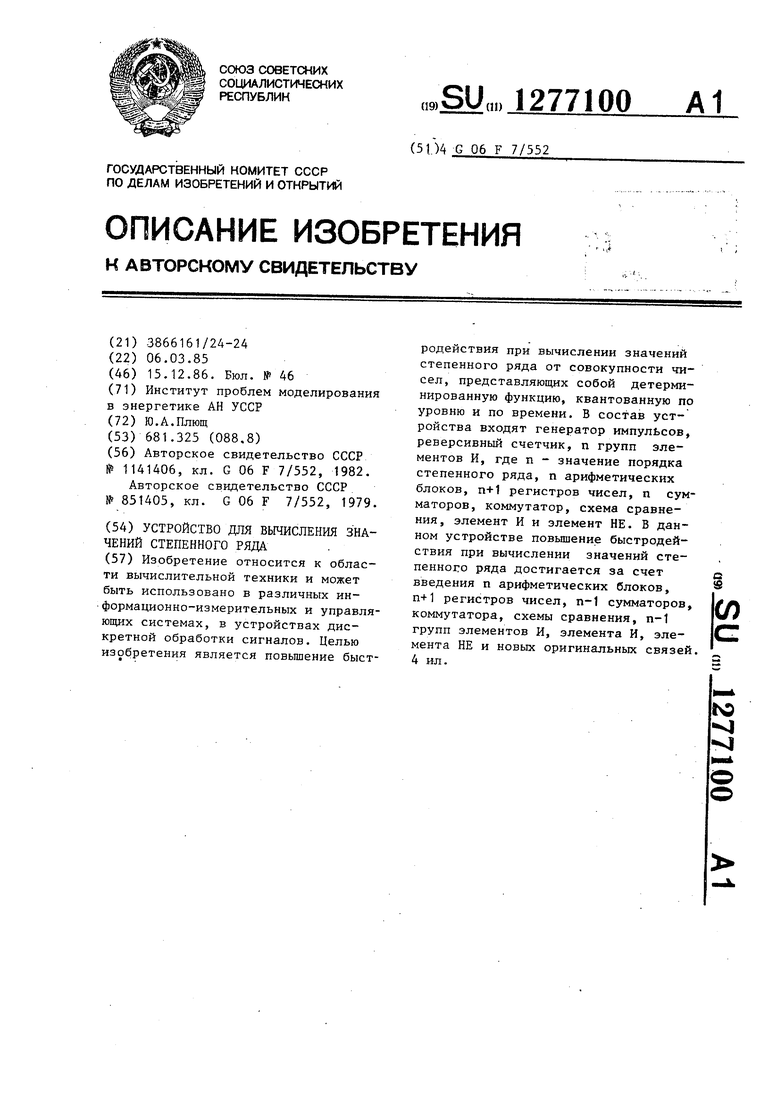

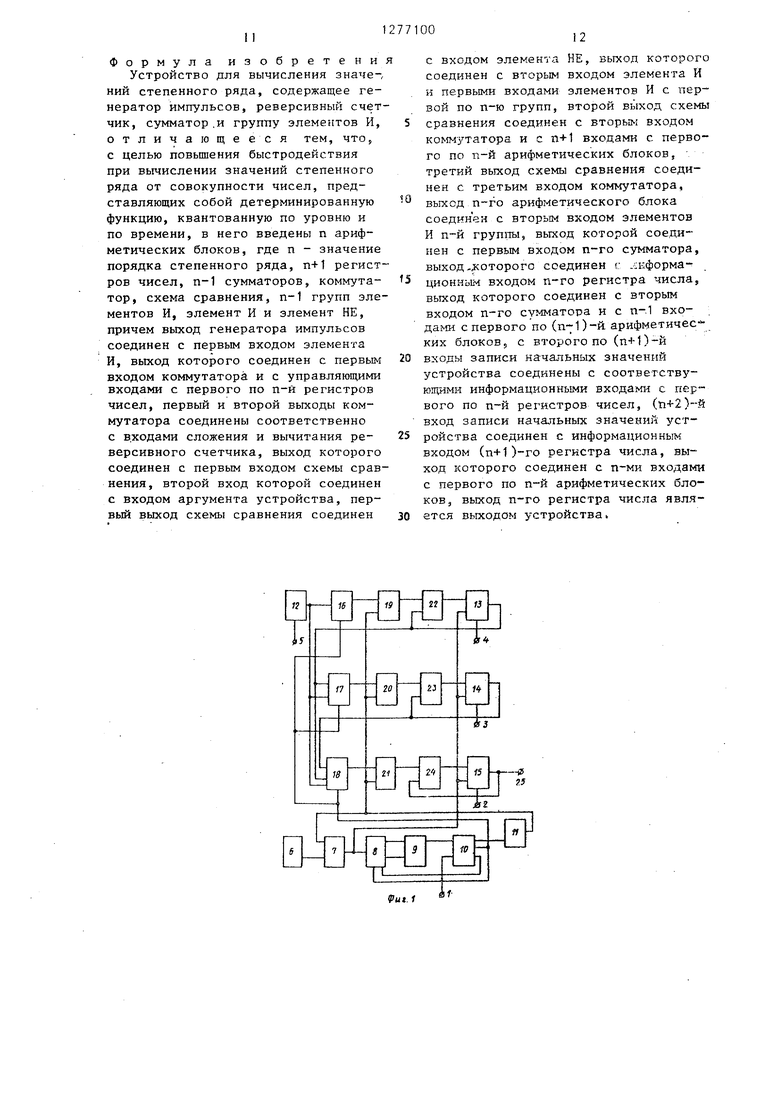

На фиг. 1 изображена функциональная схема устройства для вычисления значений степенного ряда; на фиг. 2- функциональная схема первого арифметического блока на фиг. 3 - функциональная схема второго арифметического блокаI на фиг, 4 - функциональная схема третьего арифметического блока.

Устройство для вычисления значений степенного ряда (фиг. 1) содержит первый t, четвертый 2, третий З второй 4 и пятый 5 установочные входы устройства, генератор 6 импульсов, -элемент И 7, коммутатор В, реверсивный счетчик 9, схему 10 сравнения, элемент НЕ 11, четвертый 12, первый 13, второй 14 и третий 15 регистры чисел, первый 16s второй 17 и третий 18 арифметические блоки, первую 19, вторую 20 и третью 21 труппы элементов И, первый 22, второй 23s третий 24 сумматоры и выход 25 устройства.

Первый арифметический блок 16 (фиг. 2) содержит информационные входы 26 и 27, инвертор 28, группу элементов ИСКЛЮЧ УОЩЕЕ ИЛИ 29, сумматор 30 и выход 31 блока.

Второй арифметический блок 17 (фиг. 3) содержит информационные входы 32, 33 и 34, инвертор 35, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 36,пер- вьй сумматор 37, группу элементов И 38, BTopoii сумматор 39 и выход 40 блока.

Третий арифметический блок 18 (фиг. 4) содержит информационные входы 41-44, инвертор 45, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 46, первьш 47 и второй 48 сумматоры., группу элментов И 49, третий сумматор 50 и выход 51 блока.

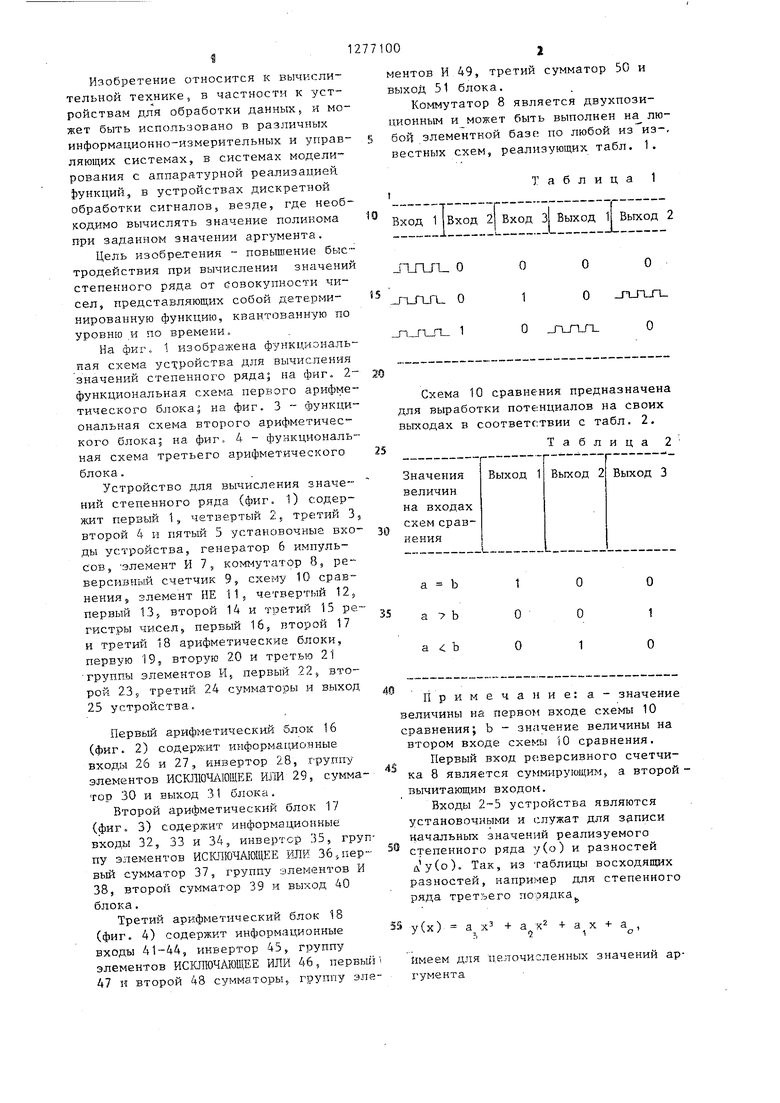

Коммутатор 8 является двухпози- ционным и может быть выполнен на лю- бой элементной базе цо любой из из-, вестных схем, реализующих табл. 1.

Таблица 1

10

Вход 1 Вход 2 Вход 3 Выход It Выход 2 ..«.«. Л,. . .. 1-«-«.«.«.. -L.«.-V м.-. «Д-... W. «..

0оо

1о

О ги-1Л о

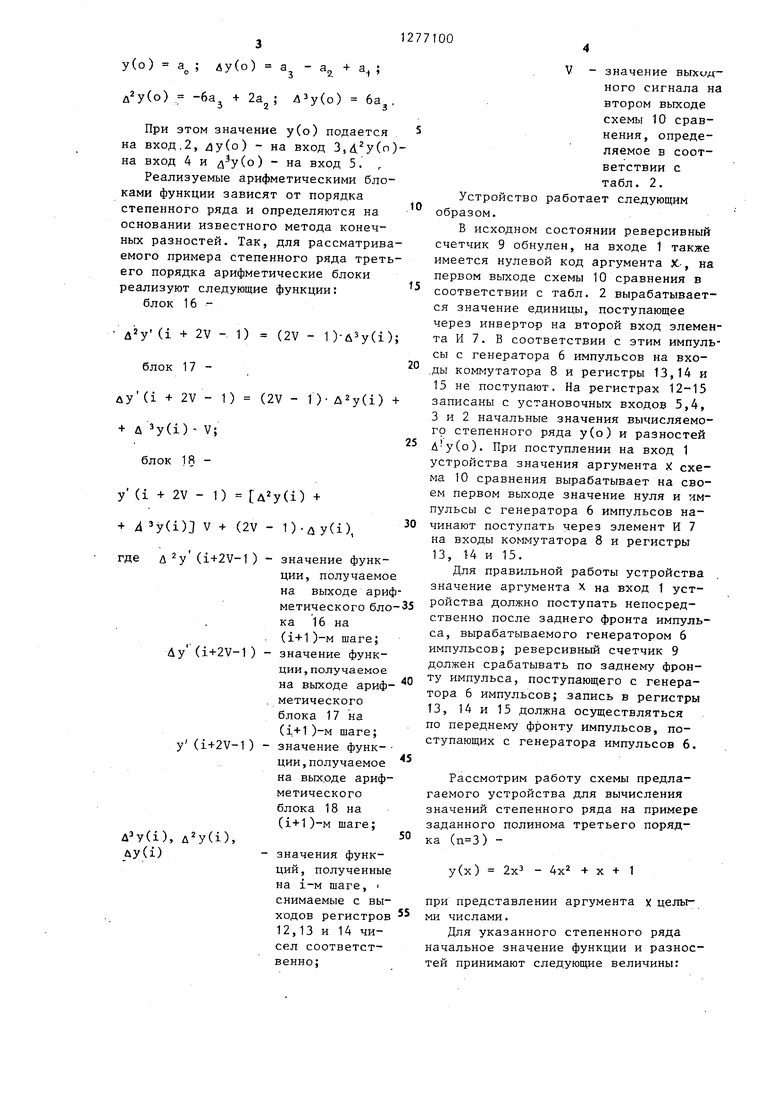

Схема 10 сравнения предназначена для выработки потенциалов на своих выходах в соответствии с табл. 2.

Таблица 2

а b

а 7 b а Ъ

1 О О

о о 1

о 1 о

S

Примечание: а- значение величины на первом входе схемы 10 сравнения; b - значение величины на втором входе схемы 10 сравнения.

Первый вход реверсивного счетчика 8 является суммирующим, а второй вычитающим входом.

Входы 2-5 устройства являются установочными и служат для записи н;ачальных значений реализуемого ® степенного ряда у(о) и разностей и у(о). Так, из таблицы восходящих разностей, например для степенного ряда третьего порядка

у(х) а х +

а х + а X + а . 5 1 о

Имеем для целочисленных значений аргумента

У(о)

лу(о)

а - а + а ;

д2у(о) -6а + ЛЗу(о) ба ,

При этом значение у(о) подается на вход.2, ду(о) - на вход 3,(n)- на вход 4 и (о) - на вход 5.

Реализуемые арифметическими блоками функции зависят от порядка степенного ряда и определяются на основании известного метода конечных разностей. Так, для рассматриваемого примера степенного ряда третьего порядка арифметические блоки реализуют следующие функции:

блок 16 д2у (1 + 2V - 1) (2V - 1)-u3y(i);

блок 17 у (1 + 2V - 1) (2V - 1)- Д2у(1) + + (1) - V;

блок 16 у (i + 2V - 1) (1) + + /4 y(i)J V + (2V - 1)-лу(1),

где Л у (i+2V-1 ) - значение функции, получаемое на выходе арифметического блока 16 на . (i+1)-м шаге; 4у (i+2V-1 ) - значение функции ,получаемое на выходе ариф- . метического блока 17 на (i+1 )-м шаге;

у (i+2V-1 ) - значение функ- ции,получаемое на вьпх.оде арифметическогоблока 18 на (i+1 )-м шаге;

(i), (i), Ay(i)

- значения функций, полученные на i-M шаге, снимаемые с выходов регистров 12,13 и 14 чисел соответственно;

10

15

20

5

0

5

0

5

0

5

V - значение выхид- ного сигнала на втором выходе схемы 10 сравнения, определяемое в соответствии с табл. 2.

Устройство работает следующим образом.

В исходном состоянии реверсивный счетчик 9 обнулен, на входе 1 также имеется нулевой код аргумента Х-, на первом выходе схемы 10 сравнения в соответствии с табл. 2 вырабатывается значение единицы, поступающее через инвертор на второй вход элемента И 7. В соответствии с этим импульсы с генератора 6 импульсов на вхо- .ды коммутатора 8 и регистры 13,14 и 15 не поступают. На регистрах 12-15 записаны с установочных входов 5,4, 3 и 2 начальные значения вычисляемого степенного ряда у(о) и разностей А у(о). При поступлении на вход 1 устройства значения аргумента X схема 10 сравнения вырабатывает на своем первом выходе значение нуля и импульсы с генератора 6 импульсов начинают поступать через элемент И 7 на входы коммутатора 8 и регистры 13, 4 и 15.

Для правильной работы устройства значение аргумента х на вход 1 устройства должно поступать непосредственно после заднего фронта импульса, вырабатываемого генератором 6 импульсов; реверсивный счетчик 9 должен срабатывать по заднему фронту импульса, поступающего с генератора 6 импульсов; запись в регистры 13, 14 и 15 должна осуществляться по переднему фронту импульсов, поступающих с генератора импульсов 6.

Рассмотрим работу схемы предлагаемого устройства для вычисления значений степенного ряда на примере заданного полинома третьего порядка () у(х) 2x3 - 4x2 + X + 1

при представлении аргумента х целы- ми числами.

Для указанного степенного ряда начальное значение функции и разностей принимают следующие величины:

У(о)

1 ; А у(о) а - а.

+ а

7;

(о) -6а + 2а 20; ) 6а 12.,

(1) л у(1) +

При поступлении на вход 1 устрой-, to ства аргумента схема 10 сравне 2 - 20 -8 ния в соответствии с табл 2 вьфабатывает на своих первом и третьем на .выхЗДе сумматора 23 - выходах значение нуля, а на втором выходе - значение единицы, т.е. V. 1. 15 Ду(1) л у ( 1) + Д у(о)

Арифметический блок 16 вычисляет

значение функции

-8 + 7 -П

(2У -О (о) (2 - 1)«

-М 2 12.

Арифметический блок 17 вычисляет Полученные на выходах сумматоров

значение функции22, 23 и 24 значения по переднему

I / фронту синхроимпульса, поступающего

ду- (1) (2V - 1) л уСо) + (о)JJ3 вторые входы регистров 13, 14 и

15, записываются в эти регистры. По заднему фронту имп:;льса в соответствии с табл. 1 и 2 реверсивный счет- Арифметический блок 18 вычисляет 30 чик 9 устанавливается в значение

единицы.

На этом первый такт работы устройства закончен.

Дальнейшая работа устройства по+ (2V 1)-ду(о) -20 + -i- 35 Ясняется табл. 3, где нулевой такт

устройства служит для задания у(о) .и д у(о).

(2 - 1) (-20) -1- 12 1

.значение функции у (1) U y(o) -ь А у(о)3 V +

+ (2 - 1) 7 -1.

Указанные значения через группы 19з 20 и 21 элементов И поступают на входы сумматоров 22, 23 и 24 соответственно и на. выходы их с учетом поступления на вторые входы значений (о), uy(o), у(о).

На выходе сумматора 22 (1) л у(1) + )

2 - 20 -8

20

-8 + 7 -П

на выходе сумматора 24 - у(1) у (1 ) + у(о) -I + 1 О .

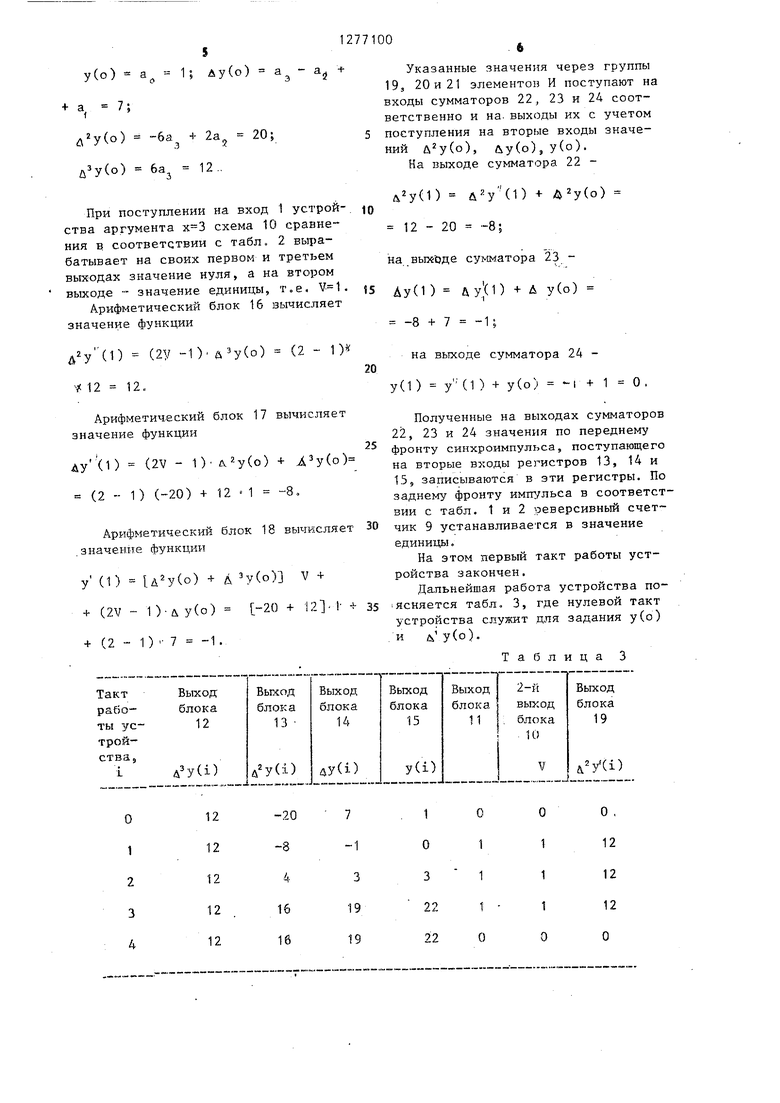

Таблица 3

Таким образом, после третьего .такта работы устройства с выхода 25 снимается значение у(3) 22.

При поступлении на вход 1 устройства нового значения аргумента х схема будет работать в соответствии с описанным алгоритмом ее функт ционирования.

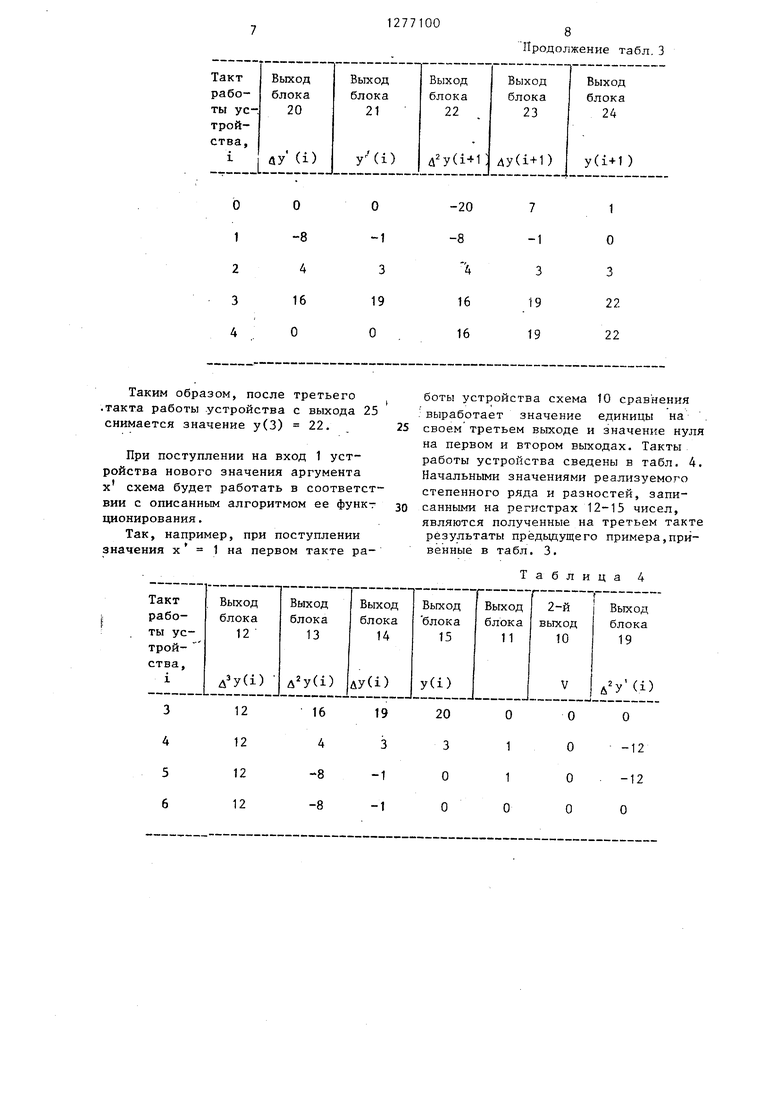

Так, например, при поступлении значения х 1 на первом такте раПродолжение табл.3

боты устройства схема 10 сравнения . выработает значение единицы на . своем третьем выходе и значение нуля на первом и втором выходах. Такты работы устройства сведены в табл. 4. Начальными значениями реализуемого степенного ряда и разностей, записанными на регртстрах 12-15 чисел, являются полученные на третьем такте результаты предыдущего примера,при- венные в табл. 3.

Таблица 4

1 1 о

о - -12 О -12 О О

Арифметический блок 16 (фиг. 2) еализует функцию

+ 2V - 1) (2V Г)«

(i).

Первый вход 26 служит для подачи значений чисел с регистра 12. Второй ход 27 служит для подачи величины , снимаемой с второго выхода схемы 10 сравнения. При поступлении на вход 27 значения V 1 на выход группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 29 передается прямой код числа с входа 26, который через сумматор 30 поступает на выход 31 блока. При V О на выходе группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 29 образуется обратн:ый код числа, поступающий с входа 26, и с учетом единицы с инвертора 28 на выходе сумматора 30 образуется дополнительный код, который поступает на выход 31 блока, что соответствует отрицательному значению

д2у (i + 2V - 1) - Д3у()

при V 0.

Арифметический блок 17 (фиг.З) реализует функцию

ду (1 + 2V - 1) (2V - 1) . ) + + Л у(1) V,(1)

На вход 32 поступает значение переменной, снимаемой с вгорого выхо1277100

10

Продолжение табл.4

да схемы 10 сравнения. Работа блока описывается соотиошение1М (1).

Арифметический блок 18 (фиг.4) реализует функцию

y (i + 2V - 1) (2V - 1 ) -AYd) +

+ & y(i) + Д3у(1)1 V

(2)

На вход 41 поступает значение с выхода регистра 14. На вход 42 поступает значение с выхода регистра 13. На вход 43 поступает значение с выхода регистра 12. На вход 44 поступает значение переменной, снимаемой с второго выхода схемы 10 сравнения. Работа блока описывается со- отношением (2) .

Время работы устройства пропорционально не значению аргумента, как это имеет место в устройстве-прототипе, а пропорционально абсолютной величине разности между двумя последующими значениями аргументов, т.е.

45

t

X - X

где 7: - такт работы устройства; X - предьщуцее значение аргумента;

х - последующее значение аргумента, причем х может быть меньше х.

Таким образом, использование предлагаемого устройства позволяет увеличить быстродействие при определении величины степенного ряда от совокупности чисел, представляющих собой детерминированную функцию, квантованную по уровню и по времени.

Формула изобретени

Устройство для вычисления значений степенного ряда, содержащее генератор импульсов, реверсивный счетчик, сумматор,и группу элементов И, отличающееся тем, что, с целью повьппения быстродействия при вычислении значений степенного ряда от совокупности чисел, представляющих собой детерминированную функцию, квантованную по уровню и по времени, в него введены п арифметических блоков, где п - значение порядка степенного ряда, п+1 регистров чисел, п-1 сумматоров, коммута- тор, схема сравнения, п-1 групп элементов И, элемент И и элемент НЕ, причем выход генератора импульсов соединен с первым входом элемента И, вьпсод которого соединен с первым входом коммутатора и с управляющими входами с первого по п-й регистров чисел, первый и второй выходы коммутатора соединены соответственно с входами сложения и вычитания ре- версивного счетчика, выход которого соединен с первым входом схемы сравнения, второй вход которой соединен с входом аргумента устройства, первый выход схемы сравнения соединен

с входом элемента НЕ, выход которого соединен с вторым входом элемента И и первыми входами элементов И с первой по п-ю групп, второй выход схемы сравнения соединен с вторым входом коммутатора и с п+1 входами с первого по и-й арифметических блоков, третий выход схемы сравнения соединен с третьим входом коммутатора, выход п-го арифметического блока соедин ен с вторым входом элементов И п-й группы, выход которой соединен с первым входом п-го сумматора, выход-которого соединен с .нформа- ционным входом п-го регистра числа, выход которого соединен с вторым входом п-го сумматора и с п-.1 вхо- . дами с первого по (n-D-ft арифметичес-- ких блоков 5 с второго по (п+1)-и входы записи начальных значений устройства соединены с соответствующими информационными вxoдaмli с первого по п-й регистров чисел, (п+2)-й вход записи начальньпс значений устройства соединен с информационным входом (п+1)-го регистра числа, выход которого соединен с п-ми входами с первого по арифметических блоков, выход п-го регистра числа является выходом устройства ь

i27

k 4(Риг.2

ФаеЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления полиномов | 1985 |

|

SU1277098A1 |

| Устройство для решения уравнений | 1986 |

|

SU1432555A1 |

| Устройство для вычисления полинома | 1982 |

|

SU1098003A1 |

| Коррелометр | 1983 |

|

SU1091173A1 |

| Устройство для воспроизведения кардиоиды | 1981 |

|

SU1007102A1 |

| Устройство для логарифмирования | 1981 |

|

SU962926A1 |

| Устройство для вычисления степенных функций | 1985 |

|

SU1282120A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления полинома @ -ой степени | 1983 |

|

SU1140115A1 |

| Цифровой генератор функций | 1987 |

|

SU1413613A1 |

Изобретение относится к области вычислительной техники и может быть использовано в различных информационно-измерительных и управляющих системах, в устройствах дискретной обработки сигналов. Целью изобретения является повьшение быстродействия при вычислении значений степенного ряда от совокупности чисел, представляюощх собой детерминированную функцию, квантованную по уровню и по времени. В состав устройства входят генератор импульсов, реверсивный счетчик, п групп элементов И, где п - значение порядка степенного ряда, п арифметических блоков, п+1 регистров чисел, п сумматоров, коммутатор, схема сравнения, элемент И и элемент НЕ. В данном устройстве повышение быстродействия при вычислении значений степенного ряда достигается за счет введения п арифметических блоков, п+ регистров чисел, п-1 сумматоров, коммутатора, схемы сравнения, п-1 групп элементов И, элемента И, элемента НЕ и новых оригинальных связей. 4 ил. (Л 1C -j

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1141406A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для воспроизведения квадратичныхпОлиНОМОВ | 1979 |

|

SU851405A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-15—Публикация

1985-03-06—Подача