коммутатора, вторая группа управляющих входов схемы сравнения соединена соответственно с разрядными выходами второго регистра,информационные входы которого являются входами установки показателя степени устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Устройство для вычисления полинома | 1980 |

|

SU885997A1 |

| Устройство для вычисления значений многомерного полинома | 1990 |

|

SU1742829A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| Устройство для возведения в п-ую степень | 1982 |

|

SU1132287A1 |

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Устройство для вычисления @ -функций | 1983 |

|

SU1124321A1 |

| Устройство для сжатия информации | 1986 |

|

SU1324047A1 |

| Устройство для вычисления коэффициентов интерполирующего полинома | 1990 |

|

SU1748158A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ПОЛИНОМА п-Й СТЕПЕНИ, содержащее первый блок памяти, счетчик адреса, первый и второй коммутаторы, первый и второй регистры, первый сумматор, элемент задержки, генератор импульсов и элемент И, причем первый вькод первого коммутатора соединен с пер- , вым входом первого сумматора, первые управляющие входы первого и второго коммутаторов объединены и соединены с выходом элемента задержки, вьтод первого регистра соединен с первым информационным входом первого коммутатора, отличающееся тем, что, с целью сокращения аппаратурньк затрат, оно содержит дешифратор, схему сравнения, второй блок памяти, второй сумматор и два умножителя, причем вход пуска генератора импульсов является управляющим входом устройства, выход генератора импульсов соединен с первым входом элемента И, второй вход которого соединен с выходом схемы сравнения и входом элемента задержки, выход элемента И соединен со счетным входом счетчика адреса, разрядные выходы которого соединены соответственно с первой группой управляющих входов схемы сравнения и входами де1пифратора, первый выход которого соединен с вторым управляющим входом второго коммутатора и управляющими входами первого и второго блоков памяти, выход второго блока памяти соединен с первым и вторым информационными входами соответственно второго и первого коммутаторов, выход первого блока памяти соединен с третьим информационный входом первого коммутатора, первый и второй выходы которого соединены соответственно с первым и вторым информационными входами первого умножителя, выход которого соединен с вторым вхоСЛ дом первого сумматора и первым информационным входом первого регистра, второй информационный вход которого соединен с выходом первого сумматора и информационным входом первого блока памяти, первый и второй вьпсоды второго коммутатора соединены соответственно с первым и вторым информационными входами второго умножителя, выход которого соединен с первым входом второго сумматора, второй вход ел которого соединен с третьим выходом второго коммутатора, четвертый выход которого соединен с третьим вхо-дом первого сумматора, второй информационный вход второго комм татора соединен с выходом первого регистра,, вход записи которого соединен с выходом элемента - адержки, выход второго суммато| а соединен с информационным входом второго блока памяти, второй выход дешифратора соединен с вторым управляющим входом первого

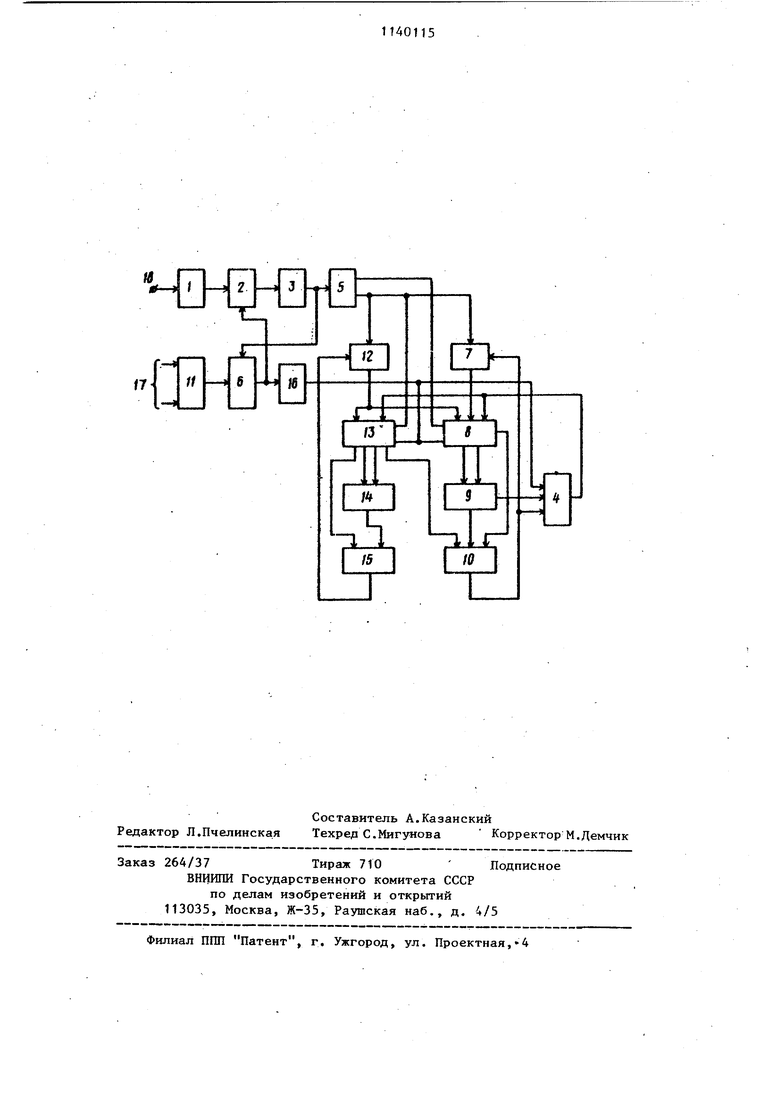

Изобретение относится к вычислительной технике и может быть использовано в измерительно-вычислительных системах, а также в АСУ, работаю щих в реальном масштабе времени. Известно арифметическое уртройствр, позволяющее вычислить значения полиномов п-й степени, содержащее регистры, одноразрядные сумматоры, элементы задержки и элементы И СП. Однако данное устройство не позволяет вычислять полиномы с коэффициентами различных знаков и имеет низкое быстродействие, обусловленное последовательным вьшолнением шагов итераций,Наиболее близким к предлагаемому по технической сущности является уст ройство ДЛЯ вычисления полинома, содержащее блок памяти, два коммутатора, входной коммутатор, два выходных коммутатора, три регистра, сумматор, регистр результата, блок управления, первый и второй преобра зователи кода частичных произведений в двуразрядный код, первую и вторую группы элементов И, первую, вторую и третью группы входных и пер вую и вторую группы выходных регист ров. Выход блока памяти соединен с первым входом входного коммутатора, первый выход которого соединен с управляющим входом первого регистра второй выход входного коммутатора с единен с информационными входами второго и третьего регистров, выходы первого и второго регистров соединены соответственно с первым и вторым входами, первого коммутатора, выход третьего регистра соединен с первым входом второго коммутатора, первый выход второго выходного коммутатора соединен с входом сумматора, выход которого соединен с инфор мационным входом регистра результат Недостатком известного устройства являются большие аппаратурные затраты. Цель изобретения - сокращение аппаратурных затрат. Поставленная цель достигается тем, что устройство для вычисления полинома п-й степени, содержащее первый блок памяти, счетчик адреса, первый и второй коммутаторы, первый и второй регистры, первый сумматор, элемент задержки, генератор импульсов и элемент И, причем первый выход первого коммутатора соединен с первым входом первого сумматора, первые управляющие входы первого и второго коммутаторов объединены и соединены с выходом элемента задержки, вькод первого регистра соединен с первым информационным входом первого коммутатора, дополнительно содержит дешифратор, схему сравнения, второй блок памяти, второй сумматор и два умножителя, причем вход пуска генератора импульсов является управляющим входом устройства, выход генератора импульсов соединен с первым входом элемента И, второй вход которого соединен с выходом схемы сравнения и входом элемента задержки, выход элемента И соединен со счетным входом счетчика адреса , разрядные выходы которого соединены соответственно с первой группой управляющих входов схемы сравнения и входами дешифратора, первый выход которого соединен с вторым управляющим входом второго коммутатора и управляющими.входами первого и второго блоков памяти, выход второго блока памяти соединен с первым и вторым информационными входами соответстьенно второго и первого коммутаторов, выход первого блока памяти соединен с третьим информационным входом первого коммутатора, первый и второй вькоды которого соединены соответственно с первым и вторым информационными входами первого умножителя, выход которого соединен с вторым-входом первого сумматора и первым информационным входом первого регистра, второй информационный вход которого соединен с выходом первого сумматора и информационным входом первого блока памяти, первый и второй выходы второго коммутатора соед нены соответственно с первым и вторым информационными входами второго умножителя, вькод которого соединен с первым входом второго сумматора, второй вход которого соединен с третьим выходом второго коммутатора четвертый выход которого соединен с третьим входом первого сумматора, второй информационный вход второго коммутатора соединен с выходом первого регистра, вход записи которого соединен с выходом элемента задержки, выход второго сумматора соединен с информационным входом второго блока памяти, второй выход дешифратора соединен с вторым управляющим входом первого коммутатора, вторая группа управляющих входов схемы сра нения соединена соответственно с ра рядными выходами второго регистра, информационные входы которого являются входами установки показателя степени устройства. На чертеже изображена блок-схема устройства для вычисления полино ма П-й степени. Устройство содержит генератор 1 импульсов, элемент И 2, счетчик 3, регистр 4, дешифратор 5, схему 6 .сравнения, первый блок 7 памяти, коммутатор 8, первый умножитель 9, первый сумматор 10, регистр 11, второй блок 12 памяти, второй коммутатор 13, второй умножитель 14, второй сумматор 15, элемент .16 задержки, вход 17 показателя степени устройства и управляющий вход 18 устройства. Устройство вычисляет полином где i- номер члена полинома, показатель степени аргумента,с действительными аргументом и коэффици ентами я; по схеме Горнера :(((...(.о(.,),),....4с,;) : U Устройство реализует алгоритм вычисления полинома по формуле (-(,).JxV...c..J. 4(-((.,)..s)x....c,J, полученной преобразованием исходной формулы (2). На вход 17 устройства заносится степень вычисляемого полинома, а на вход 18 поступает сигнал запуска устройства. Устройство работает следующим образом. В исходном состоянии в блоке 7 памяти размещены значения коэффициентов с(, а j...,c, npifqeM коэффициенты с индексами i п, h -4,...,11,7, 3 размещены по четным адресам памяти, а коэффициенты с индексами i n-2, п-6, ... ,9, 5,1 размещены по нечетным адресам. По нулевому адресу блока 7 памяти размещен аргумент х, В блоке 12 памяти размещены значения коэффициентов а.,, а J ,...,4,2, О, причем по нулевому адресу находится ноль, коэффициенты с индексами ,п-5,...,10,6,2 размещены по четным адресам памяти, коэффициенты с индексами ,h-7,...,8,4,0 размещены по Нечетйым адресам. В регистре 4 находится константа, зави сящая от степени вычисляемого полинома, равная п-1/2 . Все разряды счетчика 3 находятся в единичном состоянии. По сигналу Пуск импульсы, вырабатываемые генератором 1, поступают на элемент И 2. Первый импульс с генератора поступает на вход счетчика 3 и устанавливает его в нулевое состояние . При этом по сигналу с дешифратора 5 из блока 7 памяти через коммутатор 8 на оба входа умножителя 9 поступают значения аргумента к. Результат х поступает в регистр 4. Далее генератор 1 импульсов вырабатывает очередной импульс, содержимое .счетчика 3 увеличивается на единицу и из блока 7 памяти пс сигналу с дешифратора 5 считывается коэффициент е, который поступает на вход умножителя 9, на второй вход.которого через коммутатор 8 поступает мноитель х из регистра 4. Одновременно по сигналу с дешифратора 5 из блока 12 памяти считывается коэффици51

ент (1лч , который поступает через коммутатор 13 на вход умножителя 14, на второй вход которого поступает множитель х с регистра 4. Результаты умножения из умножителя 9 поступают на сумматор 10, а из умножителя 14 -на сумматор 15. На второй вход сумматора 10 поступает коэффициент ч ,,2 из блока 7 памяти через коммутатор 8, на второй вход сумматора 15 - коэффициент «я.через коммутатор 13. Результаты из сумматоров 10 и 15 переписываются соответственно в блок 7 памяти по адресу размещения коэффициента eH.jH в блок 12 памяти по адресу размещения коэффициента Nfl.j. Далее генератор 1 вырабатывает очередной импульс и итерационньй процесс вычисления значения полинома по формуле (3) повторяется

- раз, Когда содержимое счетчика 3

п-1

сигнал со схемы

станет, равным

6 сравнения через элемент задержки, который осуществляет задержку сигнала на время выполнения одной итерации, сбросит счетчик 3 в нулевое состояние и результат с выхода сумматора 15 запишется по первому адресу блока 12 памяти, а результат с выхода сумматора 10 запишется в регистр 11. Сигнал с выхода схемы 6 сравнения запрещает прохождение импульсов с выхода генератора 1 на вход счетчика 3. В очередном цикле по сигналу с дешифратора 5 из бло15

ка 7 памяти прочитьтается значение аргумента х, которое через коммутатор 8 поступает на вход умножителя

9,на второй вход которого поступает множитель с регистра 4. Результат умножения поступает на сумматор

10,на второй вход которого из блок 12 памяти через коммутатор 8 поступает результат, записанный по первому адресу. Значение полинома записывается в блок 7 памяти по первому адресу.

Через коммутаторы 8 и 13 в различные итерационные циклы может передаваться информация с выходов регистра 4, блоков 7 и 12 памяти на входы умножителей 9 и 14 и сумматоров 10 и 15. Управляющими сигналами для коммутаторов 8 и 13 являются сигналы с выходов дешифратора 5 и элемента 16 задержки, последний кроме того, разрешает заносить информацию с выхода сумматора 10 на регистр 4.

Таким образом, в предлагаемом устройстве значительно сокращен объем оборудования. Кроме того, устройство позволяет отыскивать значения полиномов с действительными коэффициентами. В результате применения для вычисления полинома измененной схемы и соответствующего расположения коэффициентов и промежуточных результатов в блоках памяти время отыскания значения полинома уменьшается, т.е. повьш1ается быстродействие.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления значения полинома -й степени | 1978 |

|

SU769536A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления полинома | 1980 |

|

SU885997A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-02-15—Публикация

1983-09-16—Подача