Изобретение относится к вычислительной технике и предназначено для использс5вания в универсальных и специализированных ЦВМ при обработке больших массивов данных.

Известно устройство для логарифмирования двоичных чисел,, содержащее .регистры старших и младших разрядов аргумента, три блока памяти, блок управления, коммутатор, сумматор, выходной регистр, триггер, сдвигатель, блок управления сдвигателем 1.

Недостатком известного устройства является низкое быстродействие.

Наиболее близким к предлагаемому является устройство для логарифмирования массивов двоичных чисел, содержащее входной регистр, три блока памяти, два сумматора, семь регистров, блок для возведения в КЕЭдрат, блок умножения, блок управления. Известное устройство работает по конвейерному принципу и реализует операцию логарифмирования над массивами чисел с быстродействием, равным времени возведения в квсщрат (при реализации на элементах 155 серии зто время равно 165 не). Производительность данного устройства выше, чем в известных устройствах для

логарифмирования, разработанных в СССР и за рубежом 2.

Однако его производительность можно еще более повысить, если уменьшить задержку в наиболее медленной ступени конвейера, которой является ступень, содержащая квадратор. Задержка в этой ступени более, чем вдвое превосходит задерж10ку в остальных ступенях конвейера, поэтому половину такта работы конвейера они простаивают.

Цель изобретения - увеличение быстродействия устройства.

15

Поставленная цель достигается тем, что в известное устройство содержащее два сумматора, три бло ка памяти,входной регистр,выходной ре гистр, шесть промежуточных регист20ров, первый блок возведения в квадрат и блок управления, первый выход которого соединен с управляющим входом первого промежуточного регистра, второй выход блока управ25ления соединен с управляющими входами входного регистра, с второго по шестой промежуточных регистров и выходного регистра, информационный вход входного регистра соединен с

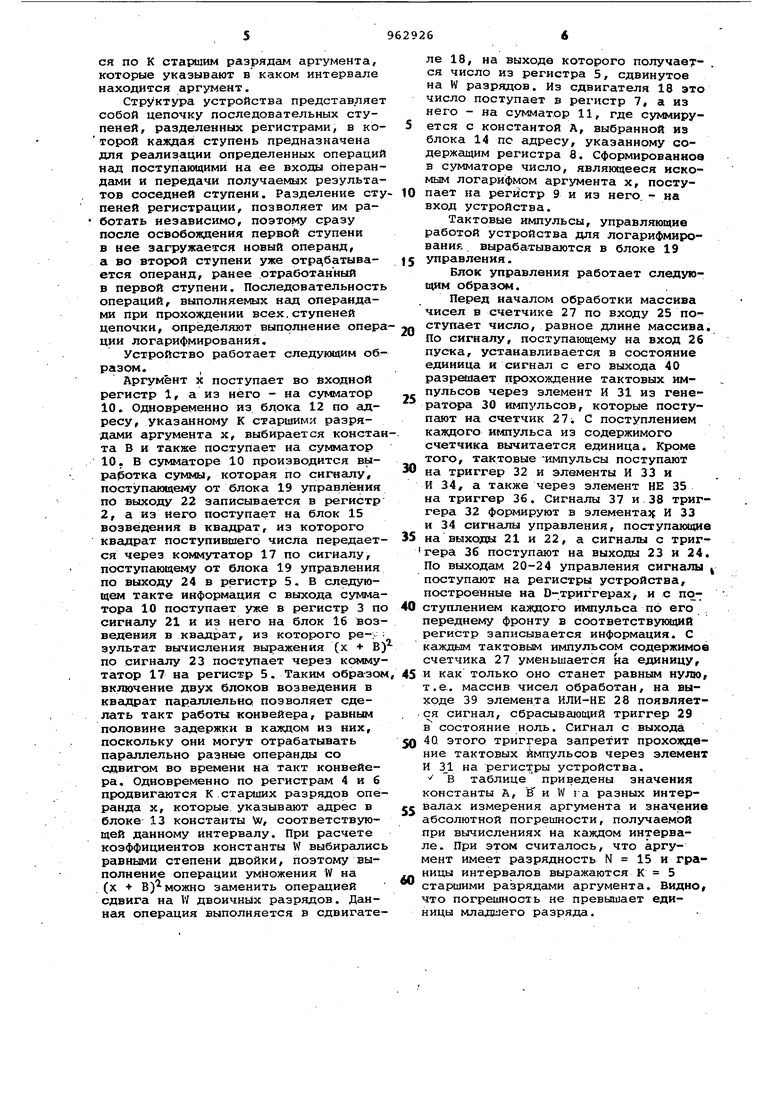

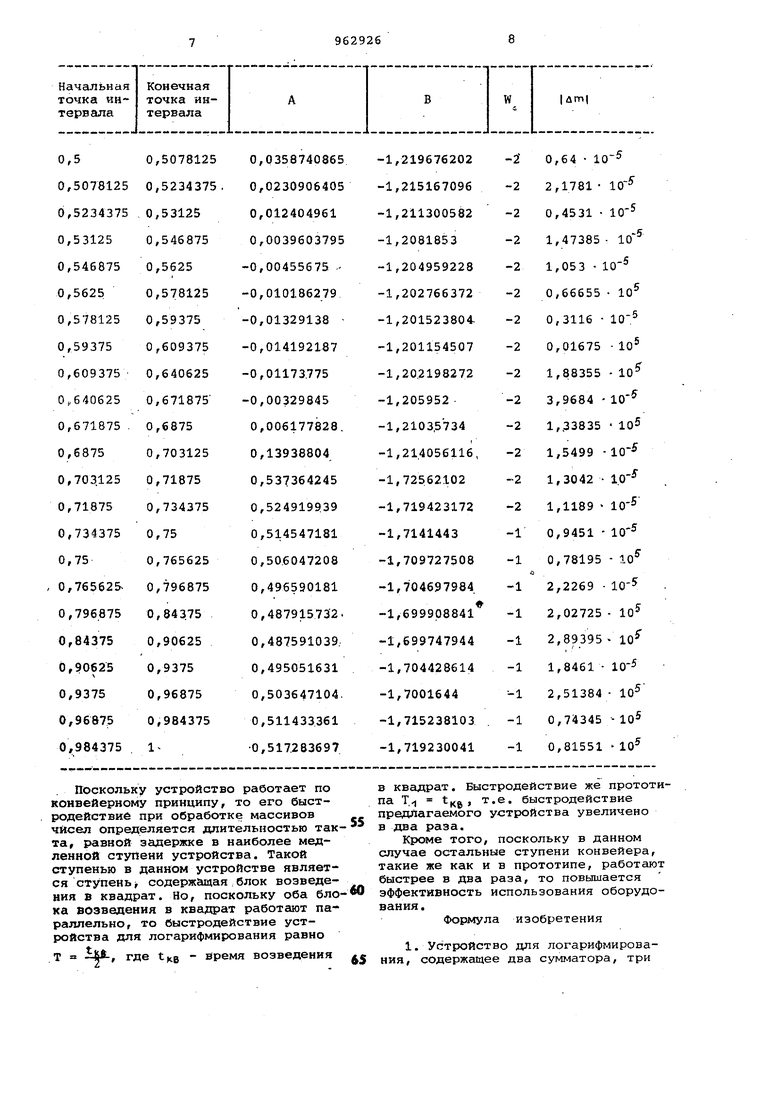

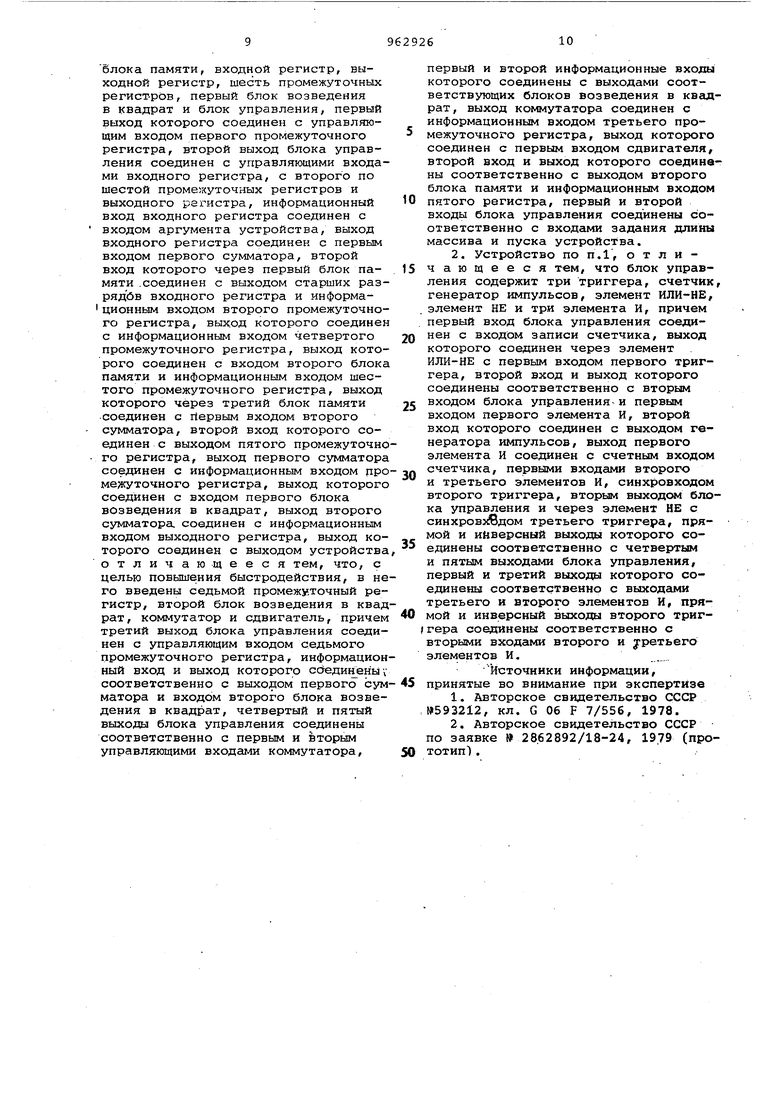

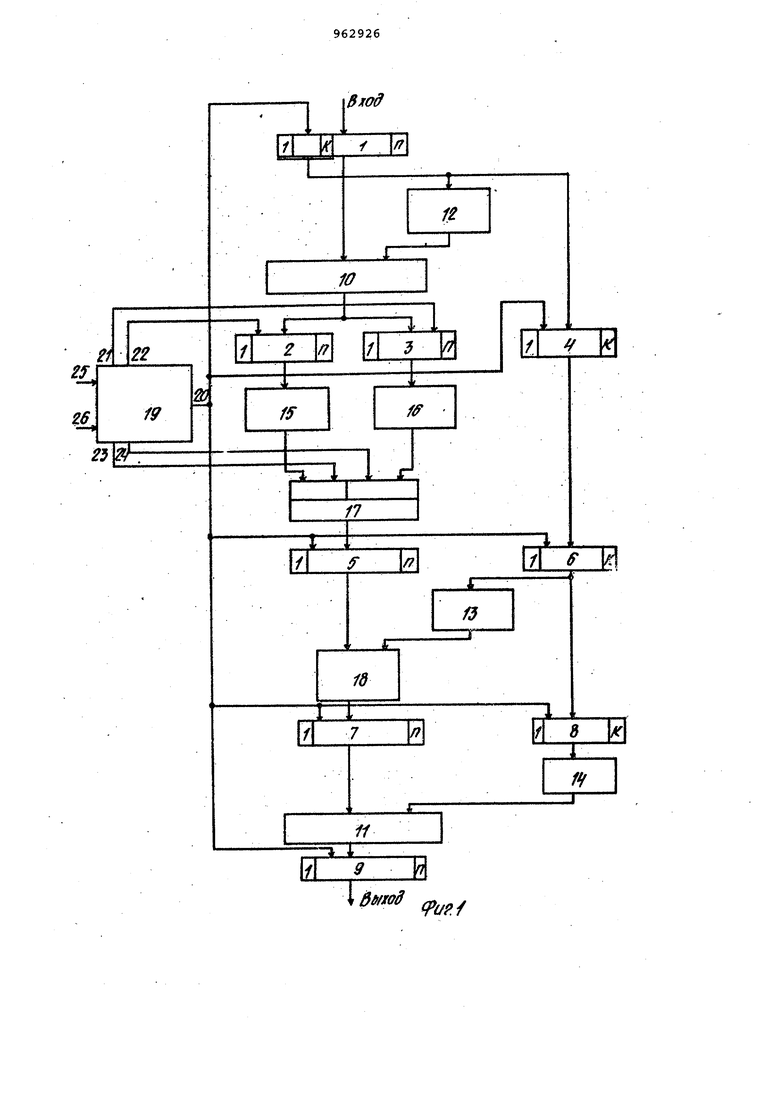

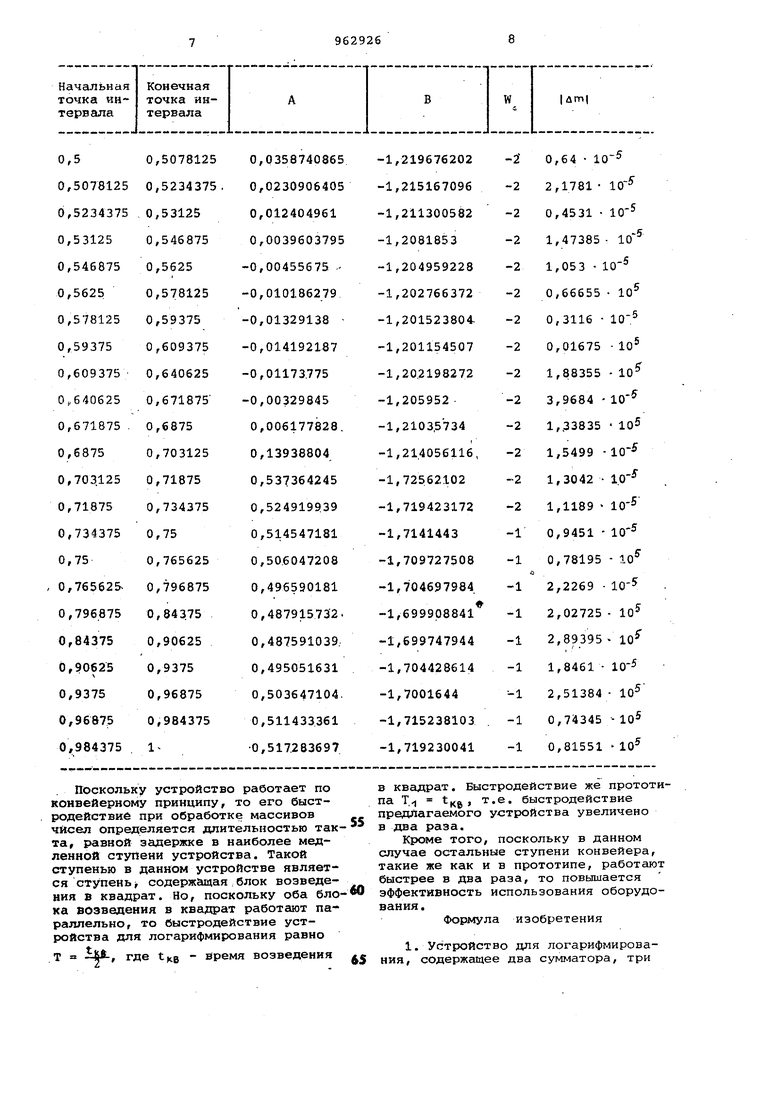

30 входом аргумента устройства, выход Входного регистра соединен с первым входом первого сумматора, второй вход которого через первый блок памяти соединен с выходом старших разрядов входного регистра и информационным входом второго промежуточного регистра, выход которого соединен с информационным входом четвертого промежуточного регистра, выход которого соединен с входом второго блока памяти и информационным. входом шестого промежуточного регистра, выход которого через третий блок памяти соединен с первым входом второго сумматора, второй вход которого соединен с выходом пятбго промежуточного регистра, выход первого cy Iмaтopa соединен с информационным входом первого промежуточного регистра, выход которого .соединен с входом первого блока возведеник в квадрат, выход второго сумматора соединен с информационным входом выходного регистра, выход которо го соединен с выходом устройства, дополнительно введены седьмой промежуточный регистр, второй блок возведения в квадрат, коммутатор и сдвигатель, причем третий выход блока управления соединен с управляющим входом седьмого промежуточного регистра, информационный вход и выход которого соединены соответственно с выходом первого сумматора и входом второго блока возведения в квадрат, четвертый и пятый выходы блока управления соединены соответственно с первыгл и вторязил управляющими входами коммутатора, первый и второй информационные входы которого соединены с выходами соответствующих блоков возведения в квадрат, выход коммутатора соединен с информационным входом третьего промежуточного регистра, выход которого соединен с первым входом сдвигателя, второй вход и выход которого соединены соот ветстйенно с выходом второго блока памяти и информационным входом пятого регистра, первый и второй входы блока управления соединены соответственно с входа;ми задания длины маесива и пуска.устройства. При этом блок управления содержит три триггера, счетчик, генератор им пульсов, элемент ИЛИ-НЕ, элемент НЕ и три элемента И, приче.м первый г вход блока управления соединен с вхо дом записи счетчика, выход которого соединен через элемент ИЛИ-НЕ с пер ВЫ1Л входом первого триггера, второй вход и выход которого соединены соответственно-с вторым входом блока управления и первым входом первого элемента И, второй вход которого со единен свыходом генератора импульс выход первого элемента И соединен с счетным входом счетчика, первыми входами второго и третьего элементов И, синхровходом второго триггера и вторам выходом блока управления и через элемента НЕ с синхровходом третьего триггера, прямой и инверсный выходы которого соединены соответственно с четвертым и пятым выходами блока управления, первый и третий выходы которого соединены соответственно с выходами третьего и второго элементов И, прямой и инверсный выходы второго триггера соединены соответственно с вторыми входами второго и третьего элементов И. На фиг.1 дана блок-схема устройства для логарифмирования; на фиг. 2 - схема блока управления. Устройство для логарифмирования содержит регистр 1 входной, регистры 2-8 промежуточные, регистр 9 выходной, сумматоры 10 и 11, блоки 12-14 памяти, блоки 15 и 16 возведения в квадрат, коммутатор 17, сдвигатель 18, блок 19 управления, выходы 20-24 и входы 25 я 26 блока управленияi Блок 19 управления содержит счетчик 27, элемент ИЛИ-НЕ 28, триггер 29, генератор 30 импульсов, элемент И 31, триггер 32, элементы И 33 и 34, элемент НЕ 35, триггер 36, выходы 37 и 38 триггера 32, выход 39 элемента ИЛИ-НЕ 28 и выход 40 триггера 29. Устройство предназначено для обработки нормализованных данных, представленных в формате с фиксированной запятой. Вычисление функции у EogjX производится в устройстве таблично-алгоритмическиь методом путем хранения сжатыхтаблиц, данных в паЕ1яти и их восстановления-при помощи арифметического устройства на основе соотношенияу А -I- WCx В), где константы А, В и W выбираится из условия минимизации абсолютной погрешности. Диапазон изменения аргумента 1/2, 1 разбивается на интервалы, количество которых определяется требуемой точностью, причем границы интервалов выражаются К старшими двоичными раэрядсми аргумента. Как показал вычислительный эксперимент, проведенный на ЭВМ, для 15-разрягиых двоичных чисел использование вышеуказанного алгоритма при разбиении диапазона изменения аргумента на 24 интервала позволяет достичь точности . На разных интервалах константы имеют различные значения. КОНСТЕШТЫ В хранятся в блоке 12 памяти, константы W в блоке 13 памяти и константы А в блоке 14 памяти. Адресация к ка)к;дому блоку памяти осуществляет-. ся по к старшим разрядам аргумента, которые указывают в каком интервале находится аргумент. Структура устройства представляет собой цепочку последовательных ступеней, разделенных регистрами, в которой каждая ступень предназначена для реализации определенных операций над поступающими на ее входы операндами и передачи получаемых результатов соседней ступени. Разделение сту пеней регистрации, позволяет им работать независимо, поэтому сразу после освобождения первой ступени в нее загружается новый операнд, а во второй ступени уже отрг батывается операнд, ранее отработанный в первой ступени. Последовательность операций, выполняемых нал операндами при прохождении всех.ступеней цепочки, определяют выполнение опера ции логарифмирования. Устройство работает следующим образом. , Аргумент X поступает во входной регистр 1, а из него - на сумматор 10. Одновременно из блока 12 по адресу, указанному К старшими разрядами аргумента х, выбирается конста та В и также поступает на сумматор 10. В сумматоре 10 производится выработка суммы, которая по сигналу, поступакмцему от блока 19 управления по выходу 22 записывается в регистр 2, а из наго поступает на блок 15 возведения в квадрат, из которого квсшрат поступившего числа передается через коммутатор 17 по сигналу, поступающему от блока 19 управления по выходу 24 в регистр 5. В следующем такте информация с выхода сумматора 10 поступает уже в регистр 3 по сигналу 21 и из него на блок 16 возведения в квадрат, из которого ре-у зультат вычисления выражения (х + В) по сигналу 23 поступает через коммутатор 17 на регистр 5. Таким обра-зом включение двух блоков возведения в квадрат параллельно позволяет сделать такт работы конвейера, равным половине зёщержки в каждом из них, поскольку они могут отрабатывать параллельно разные операнды со сдвигом во времени на такт конвейера. Одновременно по регистрам 4 и 6 продвигсцотся К .старших разрядов операнда X, которые, указывают адрес в блоке 13 константы х/, соответствующей данному интервалу. При расчете коэффициентов константы W выбирались равными степени двойки, поэтому выполнение операции умножения W на (х В) можно заменить операцией сдвига на V/ двоичных разрядов. Данная операция выполняется в сдвигателе 18, на выходе которого получается число из регистра 5, сдвинутое на W разрядов. Из сдвигателя 18 это число поступает в регистр 7, а из него - на сумматор 11, где суммируется с константой А, выбранной из блока 14 ПС адресу, указанному содержащим регистра 8. Сформированное в сумматоре число, являняцееся искомым логарифмом аргумента х, поступает на регистр 9 и из него - на вход устройства. Тактовые импульсы, управляющие работой устройства для логарифмирования вырабатываются в блоке 19 управления. Блок управления работает следующим образом. Перед началом обработки массива чисел в счетчике 27 по входу 25 поступает число, равное длине массива. По сигналу, поступающему на вход 26 пуска, устанавливается в состояние единица и сигнал с его выхода 40 разрешает прохождение тактовых импульсов через элемент И 31 из генератОра 30 импульсов, которые поступают на счетчик 27i С поступлением каждого импульса из содержимого счетчика вычитается единица. Кроме того, тактовые импульсы поступают на триггер 32 и элементы И 33 и И 34, а также через элемент НЕ 35 на триггер 36. Сигналы 37 и 38 триггера 32 форхмируют в элемента И 33 и 34 сигналы управления, поступающие на выходы 21 и 22, а сигнешы с триггера 36 поступают на выходы 23 и 24. По выходам 20-24 управления сигналы поступают на регистры устройства, построенные на 0-триггерах и с по-; отуплением каждого импульса по его переднему фронту в соответствующий регистр записывается информация. С каждым тактовым импульсом содержимое счетчика 27 уменьшается на единицу, и как только оно станет равным нулю, т.е. массив чисел обработан, на выходе 39 элемента ИЛИ-НЕ 28 появляет я сигнал, сбрасывающий триггер 29 в состояние ноль. Сигнал с выхода О этого триггера запретит прохождение тактовых импульсов через элемент И на регистры устройства. В таблице приведены значения константы А, в и W га разных интервалах измерения аргумента и значение абсолютной погрешности, получаемой при вычислениях на каждом интервае. При этом считалось, что аргуент имеет разрядность N 15 и границы интервалов выражаются К 5 старшими разрядами аргумента. Видно, то погрешность не превышает едиицы младшего разряда.

Поскольку устройство работает по конвейерному принципу, то его быстродействие при обработке массивов чисел определяется длительностью такта, равной задержке в наиболее медленной ступени устройства. Такой ступенью в данном устройстве является ступень содержащая:блок возведения в квадрат. Но, поскольку оба блока возведения в квадрат работают параллельно, то быстродействие устройства для логарифмирования равно

Т Ц где t.B - время возведения

в квадрат. Быстродействие же прототипа Т t,g , т.е. быстродействие предлагаемого устройства увеличено в два раза.

Кроме того, поскольку в данном случае остальные ступени конвейера, такие же как и в прототипе, работают быстрее в Два раза, то повышается эффективность использования оборудования .

Формула изобретения

1. Устройство для логарифмирования, содержащее два сутиматора, три

блока памяти, входной регистр, выходной регистр, шесть промежуточных регист-ров, первый блок возведения в квадрат и блок управления, первый выход которого соединен с управляющим входом первого промежуточного регистра, второй выход блока управления соединен с управляющими входами входного регистра, с второго по шестой промежуточных регистров и выходного рах-истра, информационный вход входного регистра соединен с входом аргумента устройства/ выход входного регистра соединен с первым входом первого сумматора, второй вход которого через первый блок памяти .соединен с выходом старших разрядбв входного регистра и информационным входом второго промежуточного регистра, выход которого соединен с информационным входом четвертого промежуточного регистра, выход которого соединен с входом второго блока памяти и информационным входом шестого промежуточного регистра, выход которого через третий блок памяти соединен с Первым входом второго сумматора, второй вход которого соединен с выходом пятого промежуточного регистра, выход первого сумматора соединен с информационным входом промежуточного регистра, выход которого соединен с входом первого блока возведения в квадрат, выход второго сумматора, соединен с информационным входом выходного регистра, выход которого соединен с выходом устройства отличающееся тем, что, с целью повышения быстродействия, в него введены седьмой промежуточный регистр, второй блок возведения в квадрат , коммутатор и сдвигатель, причем третий выход блока управления соединен с управляющим входом седьмого промежуточного регистра, информационный вход и выход которого сс единены соответственно с выходом первого сумматора и входом второго блока возведения в квадрат, четвертый и пятый выходы блока управления соединены соответственно с первым и вторым управляющими входс1ми коммутатора,

первый и второй информационные входы которого соединены с выходами соответствующих блоков возведения в квадрат, выход коммутатора соединен с информационным входом третьего промежуточного регистра, выход которого соединен с первым входом сдвигателя, второй вход и выход которого соединены соответственно с выходом второго блока памяти и информационным входом

пятого регистра, первый и второй

входы блока управления соединены соответственно с входами задания длины массива и пуска устройст ва.

2. Устройство по П.1, о т л и чающееся тем, что блок управления содержит три триггера, счетчик, генератор импульсов, элемент ИЛИ-НЕ, элемент НЕ и три элемента И, причем первый вход блока управления соединен с входом записи счетчика, выход которого соединен через элемент ИЛИ-НЕ с первым входом первого триггера, второй вход и выход которого соединены соответственно с вторым

входом блока управления-и первым входом первого элемента И, второй вход которого соединен с выходом генератора импульсов, выход первого элемента И соединен с счетным входом счетчика, первыми входами второго

и третьего элементов И, синхровходом второго триггера, вторым выходом блока управления и через элемент НЕ с синхровхбдом третьего триггера, прямой и ийверсный выходы которого соединены соответственно с четвертым

и пятым выходами блока управления, первый и третий выходы которого соединены соответственно с выходами третьего и второго элементов И, прямой и инверсный выходы второго триггера соединены соответственно с вторыми входами второго и уретьего элементов И.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР №593212, кл, G 06 F 7/556, 1978.

2.Авторское свидетельство СССР

по заявке № 28,62892/18-24, 1979 (прототип) .

I/I

I б мод

f/.f

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1983 |

|

SU1080135A1 |

| Устройство для логарифмирования массивов двоичных чисел | 1979 |

|

SU926654A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Устройство для деления | 1981 |

|

SU987621A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU922735A1 |

| Вычислительное устройство | 1990 |

|

SU1742814A1 |

| Цифровой генератор логарифмической функции | 1980 |

|

SU942006A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1976 |

|

SU593212A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

Авторы

Даты

1982-09-30—Публикация

1981-02-12—Подача